# COMPUTER MAINTENANCE COURSE

**VOLUME XVII**

HP2114B CENTRAL PROCESSOR UNIT

## **HEWLETT-PACKARD**

### **COMPUTER MAINTENANCE COURSE**

# VOLUME XVII STUDENTS MANUAL

### HP2114B CENTRAL PROCESSOR UNIT

(HP STOCK NO. 5951-1311)

#### -NOTICE-

The information contained in this manual is for training purposes only. Consult the Hewlett-Packard documentation supplied with the computer for current information concerning the specific computer system furnished.

The information contained in this publication may not be reproduced in any form without the expressed consent of the Hewlett-Packard Company.

#### **COPYRIGHT HEWLETT-PACKARD COMPANY 1969**

11000 Wolfe Road, Cupertino, California 95014 Area Code 408 257-7000 TWX 910-338-0221

#### **PREFACE**

This training manual has been prepared to acquaint a service technician with the rudiments of maintaining the Hewlett-Packard 2114B. It is assumed that the user possesses a basic understanding of programming and of digital computer service.

The document is intended to supplement the Operating and Service Manuals supplied with the computer. These manuals should be consulted for schematics and other technical information appropriate to the particular unit being maintained.

## **TABLE OF CONTENTS**

| Secti | on    |                                          | Page | Section | on           | Pa                                     | age |

|-------|-------|------------------------------------------|------|---------|--------------|----------------------------------------|-----|

| I     | INTRO | DUCTION                                  |      |         | 2-86.        | AC Input                               |     |

|       | 1-1.  | Purpose of 2114B Computer                | 1-1  |         | 2-88.        | Turn On Operation                      |     |

|       | 1-2.  | Physical Description of HP 2114B         |      |         | 2-91.        | Turn On Delay2-                        |     |

|       |       | Computer                                 | 1-1  |         | 2-93.        | Turn Off Mode2-                        | ·10 |

|       | 1-5.  | Options                                  | 1-2  |         | 2-96.        | Troubleshooting The Power Fail Detect  |     |

|       | 1-8.  | Software                                 |      |         |              | Circuit                                |     |

|       | 1-12. | Logical Troubleshooting                  |      |         | 2-99.        | Turn On Delay2-                        |     |

|       | 1-15. | Integrated Circuit Description           |      |         | 2-102.       | Maintenance Procedures2-               |     |

|       | 1-20. | Output                                   |      |         | 2-104.       | Cleaning                               | -11 |

|       | 1-23. | Circuit Operation                        |      |         | 2-105.       | Filters                                |     |

|       | 1-26. | Failure                                  |      |         | 2-106.       | Dusting                                |     |

|       | 1-28. | Or Tying                                 |      |         | 2-107.       | Inspection                             |     |

|       | 1-30. | CTL Comparison                           |      |         | 2-109.       | Supply Voltages2-                      |     |

|       | 1-33. | Type D FF                                |      |         | 2-112.       | Primary Regulator Adjustment 2-        |     |

|       | 1-36. | And-Or Expanders                         |      |         | 2-114.       | +20 Volt Memory Supply Adjustment 2-   |     |

|       | 1-38. | Binary Full Adder                        |      |         | 2-116.       | Power Failure Threshold Adjustment .2- | -11 |

|       | 1-43. | "D" Latch                                |      |         |              |                                        |     |

|       | 1-45. | IC Replacement                           | 1-6  | Ш       |              | PANEL                                  |     |

|       |       |                                          |      |         | 3-1.         | Introduction                           |     |

| II    |       | OWER SUPPLY                              |      |         | <b>3-4.</b>  | Equipment for Service                  |     |

|       | 2-1.  | Introduction                             |      |         | <b>3-5</b> . | Access for Service                     |     |

|       | 2-2.  | Physical Construction                    |      |         | 3-7.         | Circuit Description                    |     |

|       | 2-7.  | Equipment for Maintenance                |      |         | 3-8.         | Master Oscillator                      |     |

|       | 2-9.  | Safety Precautions                       |      |         | 3-10.        | Proximity Switch Circuit               |     |

|       | 2-12. | Circuit Description                      |      |         | 3-18.        | Adjustments                            |     |

|       | 2-13. | Primary Regulator                        | 2-2  |         | 3-26.        | Load Circuit                           |     |

|       | 2-18. | The AC Voltage Sense Circuit             |      |         | 3-30.        | Switch Register Lamps                  |     |

|       | 2-21. | Overcurrent Protection                   |      |         | 3-34.        | Run FF Buffer                          |     |

|       | 2-23. | Primarily Regulator — Troubleshooting    | 2-3  |         | 3-37.        | Front Panel Test Switches              |     |

|       | 2-24. | Isolation Transformer                    |      |         | 3-39.        | Console Lock                           |     |

|       | 2-26. | Regulator and Driver Shorts              |      |         | 3-42.        | Lamp Test                              |     |

|       | 2-29. | Regulator and Driver Open Circuit        |      |         | 3-45.        | Loader Enable                          |     |

|       | 2-31. | Waveshapes                               |      |         | 3-50.        | Single Instruction Loop                |     |

|       | 2-35. | Thermal Switches                         |      |         | 3-53.        | Phase Loop                             |     |

|       | 2-37. | Heat Dissipation                         |      |         | 3-57.        | Memory Off Switch                      |     |

|       | 2-40. | Transistor Insulators                    |      |         | 3-59.        | Halt Button                            |     |

|       | 2-44. | Unregulated Supplies                     |      |         | 3-62.        | Front Panel Operating Controls         |     |

|       | 2-48. | The +30V Supply                          |      |         | 3-64.        | Basic Binary Loader                    |     |

|       | 2-50. | +5V Supply                               |      |         | 3-66.        | Troubleshooting                        | 3-5 |

|       | 2-52. | -2V Supply                               |      |         | OF LAWS      | AT PROGRESS HAVE                       |     |

|       | 2-54. | ±12V Supply                              |      | IV      |              | AL PROCESSOR UNIT                      |     |

|       | 2-56. | +30V Lamp Supply                         | 2-7  |         | 4-1.         | Introduction                           |     |

|       | 2-58. | Troubleshooting the Unregulated          | 0.5  |         | 4-3.         | Bus Structure                          |     |

|       | 0.00  | Supplies                                 |      |         | 4-6.         | Registers and Buses                    |     |

|       | 2-60. | 60 Cycle Ripple                          |      |         | 4-8.         | Switch Register                        |     |

|       | 2-62. | Fuses                                    |      |         | 4-10.        | Overflow and Extend                    |     |

|       | 2-64. | +20 Volt Regulator                       |      |         | 4-12.        | Read - Store - Function                |     |

|       | 2-66. | Current Protection                       |      |         | 4-14.        | I/O Interface                          |     |

|       | 2-69. | +20 Volt Regulator Adjustment            |      |         | 4-17.        | Arithmetic Logic Assembly              |     |

|       | 2-76. | +20 Volt Regulated Bus - Troubleshooting |      |         | 4-19.        | Hardware Registers                     |     |

|       | 2-79. | Temperature Compensation                 |      |         | 4-21.        | S-R Bus                                |     |

|       | 2-81. | Compensation Resistors                   | 2-9  |         | 4-23.        | Logic Operations                       |     |

|       | 2-84. | Power Fail Detect Circuit                | 2-9  |         | 4-25.        | Shift — Rotate                         | 4-2 |

### TABLE OF CONTENTS (Continued)

| Secti | on             |                                                         | Page         | Section | on             | Page                                                     |

|-------|----------------|---------------------------------------------------------|--------------|---------|----------------|----------------------------------------------------------|

|       | 4-27.          | I/O Bus                                                 | 4-2          |         | 6-30.          | Power Failure Halt 6-3                                   |

|       | 4-29.          | Register Displays                                       | 4-3          |         | 6-32.          | Power On Circuit (PON) 6-3                               |

|       | 4-31.          | System Timing Generator                                 | 4-3          |         | 6-36.          | Power Down Operation Sequence 6-4                        |

|       | 4-33.          | Oscillator and Divider                                  |              |         | 6-39.          | Initial Power On                                         |

|       | 4-36.          | Timing Signals                                          |              |         | 6-45.          | Service Subroutine 6-6                                   |

|       | 4-41.          | Memory Timing Signals                                   |              |         | 6-50.          | Troubleshooting the I/O System 6-6                       |

|       | 4-44.          | Run — Step FF                                           | 4.7          |         | 6-67.          | DMA 6-7                                                  |

|       | 4-49.          | Phase Operation                                         |              |         | 6-68.          | General Description 6-7                                  |

|       | 4-56.          | Instruction Decoder                                     | 4.7          |         | 6-73.          | Major Advantages 6-8                                     |

|       | 4-58.          | Shift Logic Assembly                                    |              |         | 6-75.          | Installation 6-8                                         |

|       | 4-63.          | Overflow Register                                       | 1-10<br>1-10 |         | 6-77.          | Programming 6-8                                          |

|       | 4-69.          | Extend Register                                         |              |         | 6-78.          | Program Word Formats 6-8                                 |

|       | 1 00.          | Extend register                                         | 1-10         |         | 6-80.          | Typical DMA Program 6-9                                  |

| v     | MEMOR          | RV                                                      |              |         | 6-82.          | Theory of Operation 6-9                                  |

| •     | 5-1.           | Introduction                                            | 5-1          |         | 6-83.          | Functional Description 6-9                               |

|       | 5-4.           | Memory Timing                                           |              |         | 6-87.          | Detailed Circuit Description 6-9                         |

|       | 5-7.           | Ferrite Core Characteristics                            | 5 1          |         | 6-89.          | Initialization                                           |

|       | 5-11.          | Toroid                                                  |              |         | 6-96.          |                                                          |

|       | 5-11.<br>5-14. |                                                         |              |         |                | Generation of a Phase 5 Signal 6-16                      |

|       | 5-14.<br>5-18. | Core Arrays                                             |              |         | 6-99.          | Data Input Operation                                     |

|       | 5-16.<br>5-22. | Addressing                                              |              |         | 6-102.         | Data Output Operation                                    |

|       | 5-22.<br>5-26. | Diode Matrix                                            |              |         | 6-104.         | DMA Register Stepping and Device                         |

|       | 5-26.<br>5-32. | Driver-Switch Assembly                                  |              |         | C 110          | Turn-Off                                                 |

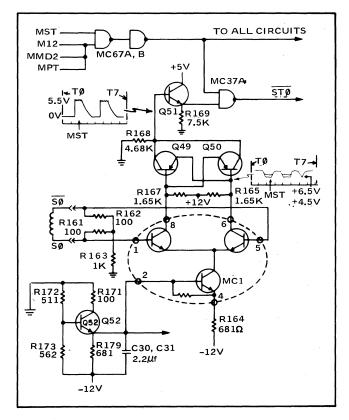

| •     |                | Driver Switch Timing                                    |              |         | 6-113.         | The Update Interrupt System 6-20                         |

|       | 5-37.          | Coincidence — Anti-Coincidence                          |              |         | 6-120.         | DMA Troubleshooting                                      |

|       | 5-39.          | Address Example                                         |              |         | 6-125.         | High-Speed Data Channel                                  |

|       | 5-45.          | Protection Diodes                                       |              |         | 6-130.         | Programming the High-Speed Data                          |

|       | 5-47.          | Current Boost                                           |              |         | 0.100          | Channel                                                  |

|       | 5-51.          | Power On                                                |              |         | 6-132.         | Functional Description                                   |

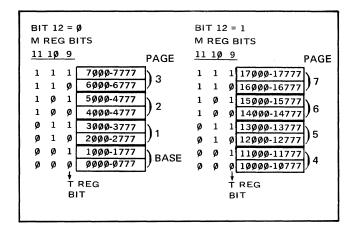

|       | 5-53.          | Page Addressing                                         |              | T 7TT   | MD O I ID      | AL EGILOOMING PROCEEDINES                                |

|       | 5-56.          | Memory Bit Information                                  |              | VII     |                | SLESHOOTING PROCEDURES                                   |

|       | 5-61.<br>5-67. | Sense Amplifier                                         |              |         | 7-1.<br>7-3.   | Introduction                                             |

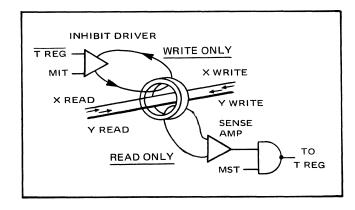

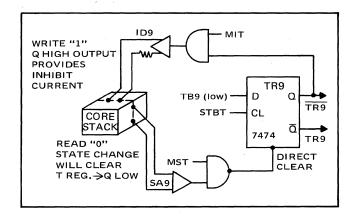

|       |                | Inhibit Driver                                          |              |         | 7-3.<br>7-4.   | Special Servicing Notes 7-1                              |

|       | 5-71.<br>5-74. | Memory Core Module Characteristics 8K Core Installation |              |         | 7-4.<br>7-6.   | Troubleshooting Aids 7-1 Abbreviations and Mnemonics 7-1 |

|       | 5-74.<br>5-76. | Parity Error                                            |              |         | 7-6.<br>7-14.  |                                                          |

|       | 5-76.<br>5-79. |                                                         |              |         | 7-14.<br>7-20. | Wiring Data                                              |

|       | 5-79.<br>5-84. | Bit Comparison Tree                                     |              |         |                | Schematic Diagrams 7-3                                   |

|       |                | Memory Error Address Register                           |              |         | 7-23.          | Maintenance and Repair Procedures 7-3                    |

|       | 5-86.          | Flag and Interrupt Circuitry                            |              |         | 7-28.          | Repair Procedures                                        |

|       | 5-88.          | Troubleshooting the Memory Section                      |              |         | 7-31.          | Pretest Checkout                                         |

|       | 5-93.          | General Troubleshooting Techniques.                     |              |         | 7-33.          |                                                          |

|       | 5-97.          | Troubleshooting Hints                                   |              |         | 7-35.          | Power On                                                 |

|       | 5-104.         | Troubleshooting the DR/SW Cards                         | 9-19         |         | 7-36.          | Power Supply Voltages 7-3                                |

|       | 5-115.         | Troubleshooting the Inhibit Driver                      | E 14         |         | 7-37.          | Lamp Test                                                |

|       | F 11F          | Cards                                                   |              |         | 7-38.          | Indicator Test 7-4                                       |

|       | 5-117.         | Troubleshooting the Sense Amp Cards                     | 5-14         |         | 7-39.          | Console Lock Test 7-4                                    |

| Y.    | Ta ibiim (     | O LIMBLID OLIOMELA                                      |              |         | 7-40.          | Switch Register Test                                     |

| VI    |                | OUTPUT SYSTEM                                           | 0.1          |         | 7-41.          | Load Address "Zeros" Test 7-4                            |

|       | 6-1.           | Introduction                                            |              |         | 7-42.          | Load Memory "Ones" Test 7-4                              |

|       | 6-3.           | I/O Control Assembly                                    |              |         | 7-43.          | Load Address "Ones" Test 7-5                             |

|       | 6-5.           | Interrupt Phase 4                                       | 6-1          |         | 7-44.          | Load Memory "Zeros" Test 7-5                             |

|       | 6-8.           | Interrupt Operation Following                           | 0.1          |         | 7-45.          | Load Memory Switch Test 7-5                              |

|       | 0.10           | Phase 4                                                 |              |         | 7-46.          | Display Memory Test 7-5                                  |

|       | 6-12.          | Conditions which Allow Phase 4                          |              |         | 7-47.          | Single Cycle Switch Test 7-5                             |

|       | 6-19.          | Select Code Generation                                  |              |         | 7-48.          | NOP Test                                                 |

|       | 6-21.          | Central Interrupt Register                              |              |         | <b>7-50.</b>   | Addressable A and B Test 7-5                             |

|       | 6-23.          | I/O Extender 2151A                                      |              |         | <b>7-55.</b>   | STA Test                                                 |

|       | 6-25.          | I/O Multiplex                                           |              |         | <b>7-58.</b>   | Extend and Indirect Indicator Test 7-6                   |

|       | 6-28.          | Power Failure - Automatic Restart                       | 6-3          |         | 7-60.          | Memory Test 7-6                                          |

### TABLE OF CONTENTS (Continued)

| Section | Page                            | Section | Page                             |

|---------|---------------------------------|---------|----------------------------------|

| 7-72.   | Memory Address Test 7-7         | 7-103.  | Alter-Skip Group Diagnostic 7-12 |

| 7-74.   | The Basic Binary Loader 7-8     | 7-104.  | Memory Reference Group           |

| 7-85.   | Entering Changes into the Basic |         | Diagnostic                       |

|         | Binary Loader 7-9               | 7-105.  | Shift/Rotate Group Test          |

| 7-88.   | Loading Absolute Tapes 7-9      | 7-106.  | Memory Address Test7-12          |

| 7-90.   | Punched Tape Reader 7-9         | 7-107.  | Memory Checkerboard Test7-12     |

| 7-92.   | Teleprinter                     | 7-108.  | Specific Problems Dealing With   |

| 7-94.   | Loading Halts                   |         | The Basic Binary Loader          |

| 7-96.   | The Long Diagnostic             |         | And the Loading of Absolute      |

| 7-100.  | Loading the Long Diagnostic     |         | Tapes                            |

|         | in the HP 2114B                 |         | •                                |

## LIST OF ILLUSTRATIONS

| Figure       | e Title                              | Page  | Figure | e Title P                                | age  |

|--------------|--------------------------------------|-------|--------|------------------------------------------|------|

| 1-1.         | HP 2114B                             | . 1-1 | 5-8.   | Memory Address Identification            | 5-3  |

| 1-2.         | TTL "NAND" Basic Building Block      | . 1-4 | 5-9.   | X-Y Diode Decoders                       |      |

| 1-3.         | Open Collector                       | . 1-5 | 5-10.  | Octal Input Lines to Core                |      |

| 1-4.         | CTL Typical Circuit (1820-0956)      |       | 5-11.  | Driver Switch Voltage Buses              | 5-5  |

| 1-5.         | D Type Flip Flop (+ Edge Trigger)    | . 1-5 |        | Driver/Switch                            |      |

| 1-6.         | AND-OR Expander                      | . 1-5 |        | Transistor Saturation                    |      |

| 1-7.         | Binary Full Adder                    |       |        | Memory Read Current Boost                |      |

| 1-8.         | D Latch (1820-0301)                  | . 1-6 |        | 8K Core Page Addressing                  |      |

| <b>2</b> -1. | Line Regulator Block Diagram         |       |        | Four Wires                               |      |

| 2-2.         | Primary Regulator                    | . 2-2 |        | Data Sense And Inhibit                   |      |

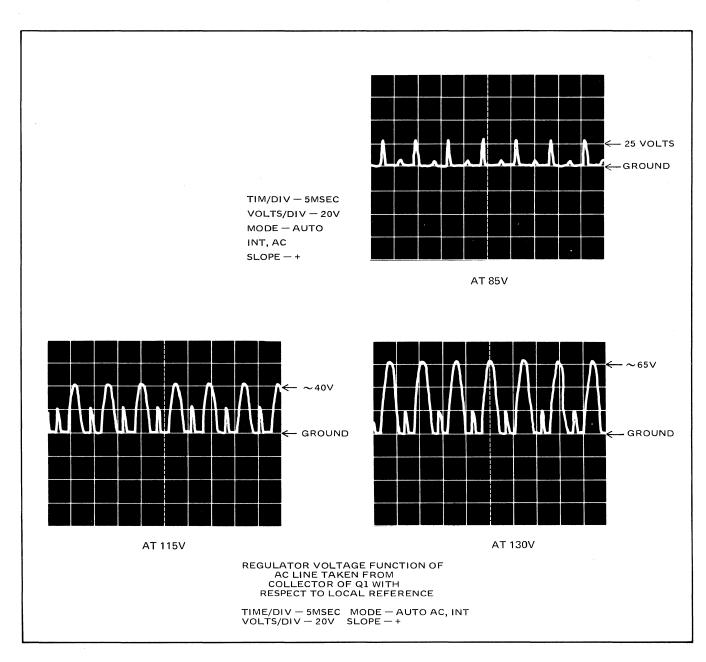

| 2-3.         | Q1 Collector Waveshapes              | . 2-4 |        | Sense Amplifier                          |      |

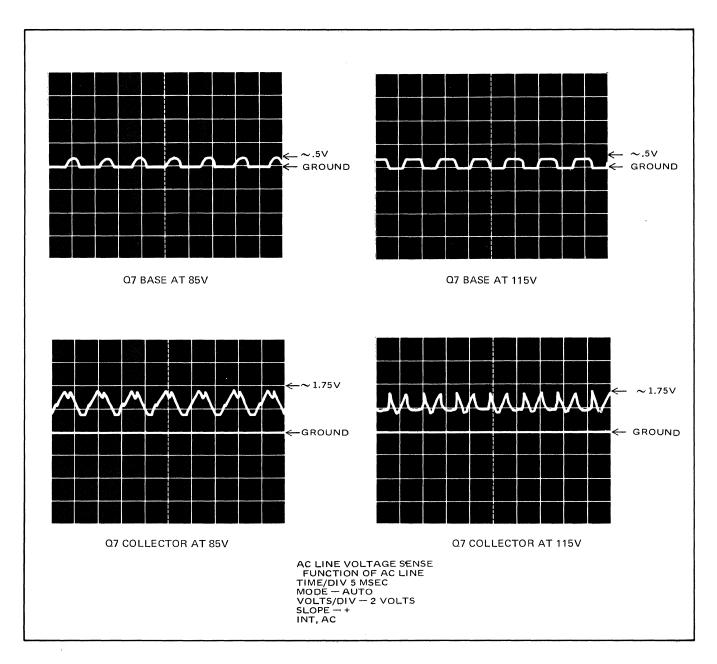

| 2-4.         | Q7 Base and Collector Waveshapes     |       |        | Inhibit Driver                           |      |

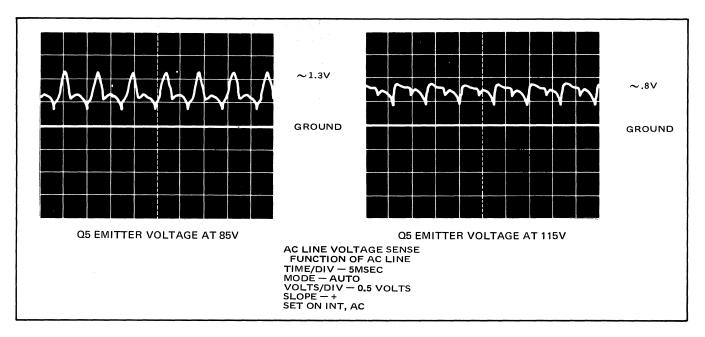

| <b>2-5</b> . | Q5 Emitter Waveshapes                |       |        | Driver/Switch Waveshape                  |      |

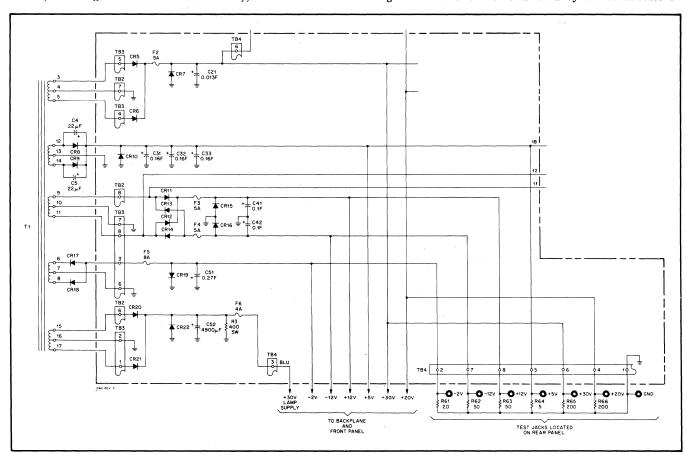

| 2-6.         | The Unregulated Bus                  |       |        | Inhibit Driver Waveshape                 |      |

| 2-7.         | 20 Volt Regulator Block Diagram      |       | 5-22.  | Sense AMP Output                         |      |

| <b>2-8</b> . | 20 Volt Regulator                    |       | 6-1.   | Interrupt Flow Chart                     |      |

| 2-9.         | Power Fail Block Diagram             |       | 6-2.   | Typical Interrupt Logic                  |      |

|              | Power Fail                           |       | 6-3.   | PON Circuit                              |      |

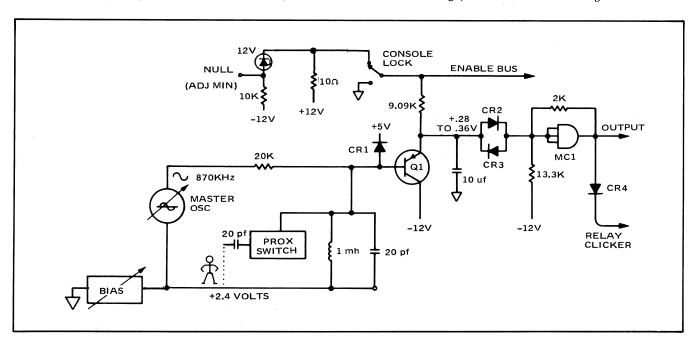

| 3-1.         | Proximity Switch Circuit             |       | 6-4.   | Simplified Power Fail Interrupt Circuit  |      |

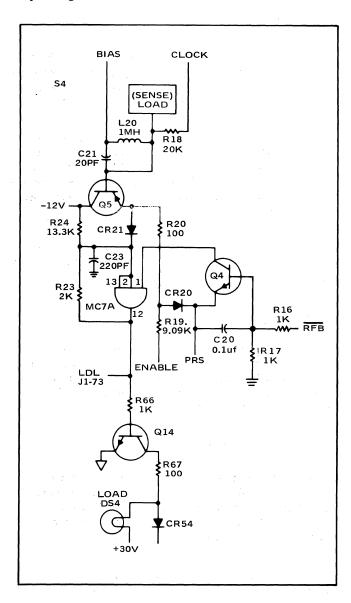

| 3-2.         | LOAD Proximity Switch                |       | 6-5.   | DMA Instruction and Control Word Formats |      |

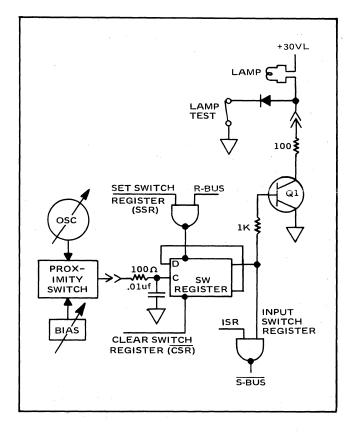

| 3-3.         | Switch Register Logic                | . 3-3 | 6-6.   | DMA Functional Block Diagram 6           | 5-11 |

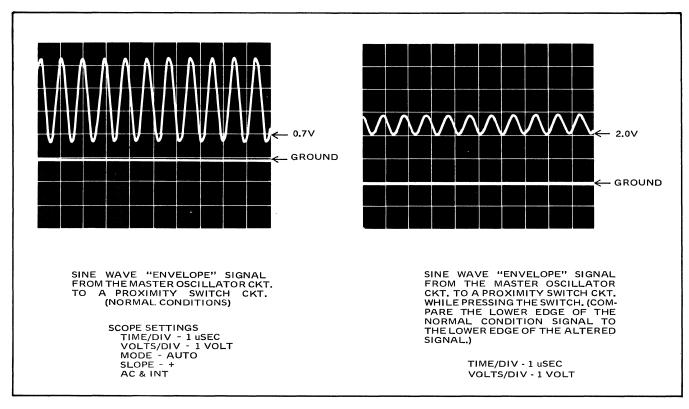

| 3-4.         | Envelope Signal to Base of Proximity |       | 6-7.   | Device Channel Select Logic at           |      |

|              | Switch Transistor                    |       |        | Initialization                           | 5-13 |

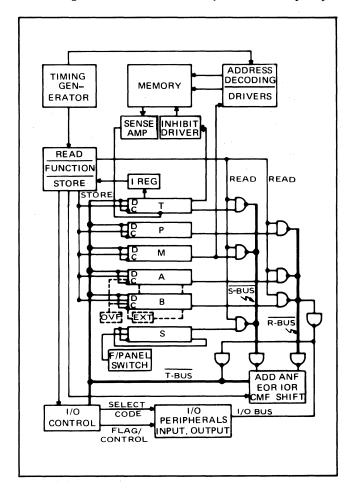

| 4-1.         | Bus Structure                        |       | 6-8.   | Initialization of Set Control and        |      |

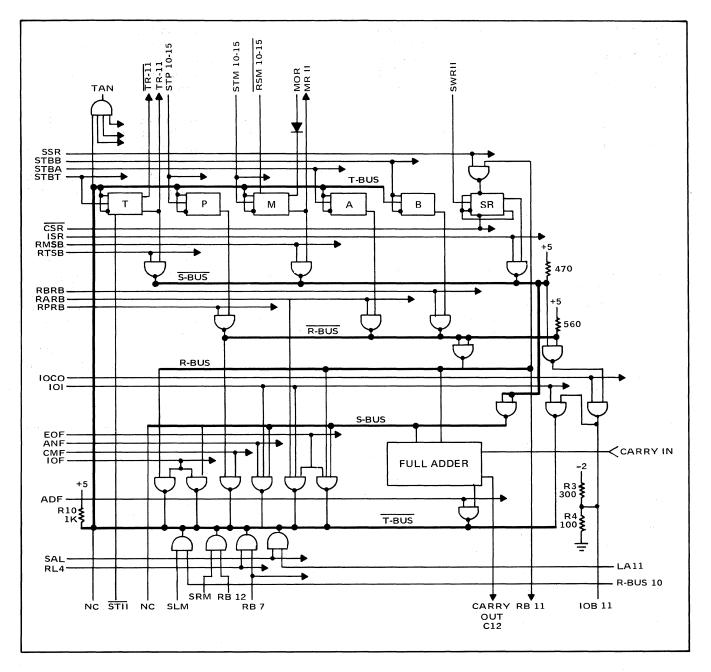

| 4-2.         | Arithmetic Logic                     | . 4-3 |        | Clear Control FFs                        |      |

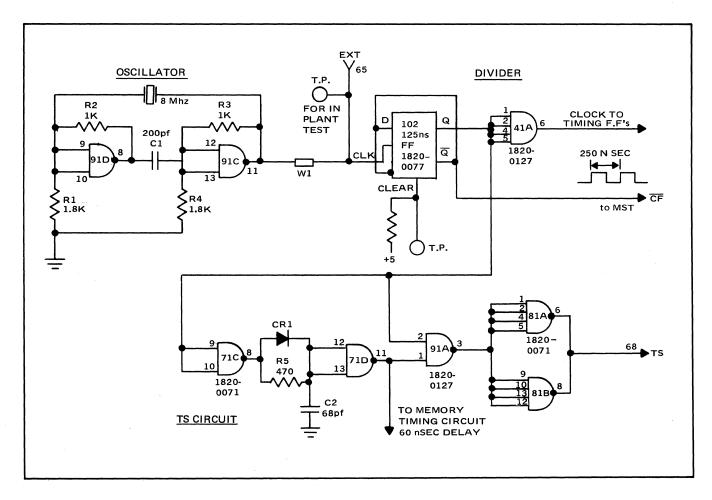

| 4-3.         | Oscillator and Divider               |       |        | Memory Address Register                  |      |

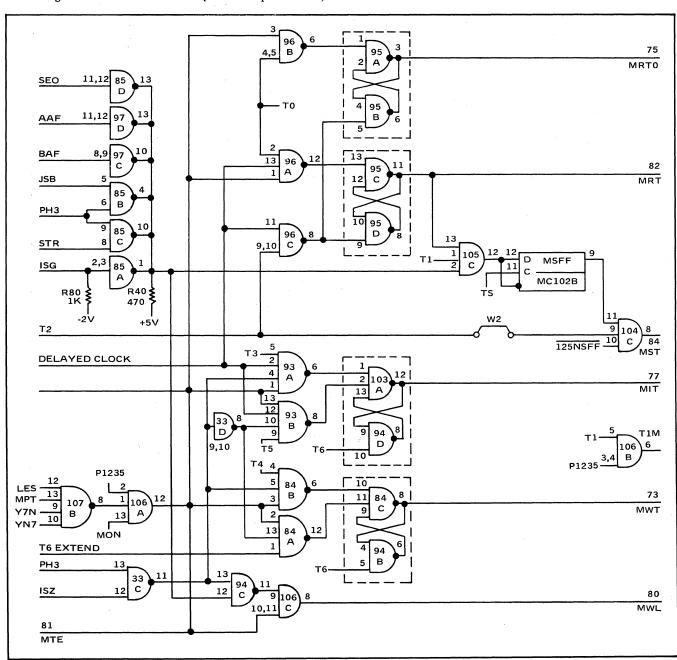

| 4-4.         | Timing Circuits                      |       |        | Word Count Register                      |      |

|              | Memory Timing Signals                |       |        | Turning DMA On                           |      |

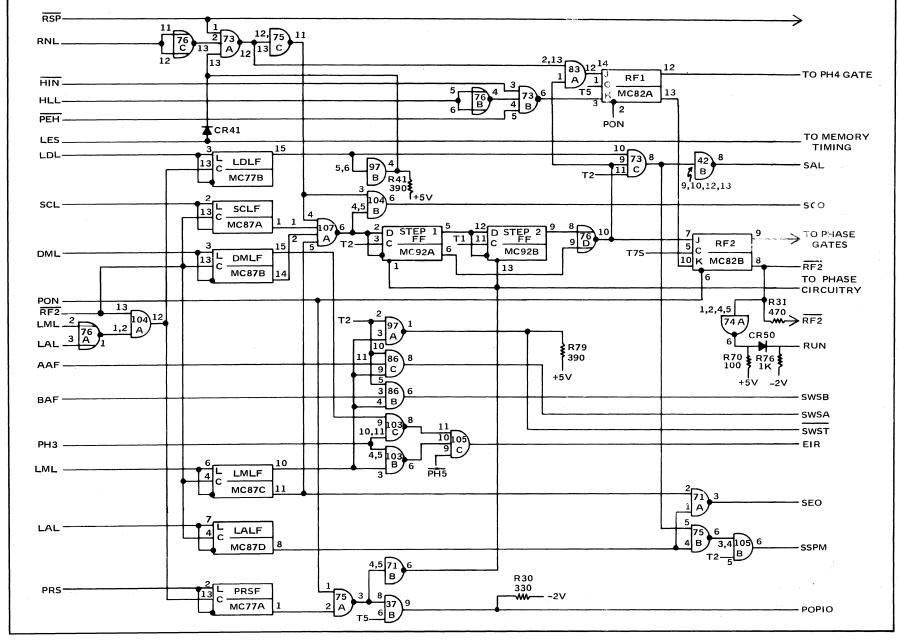

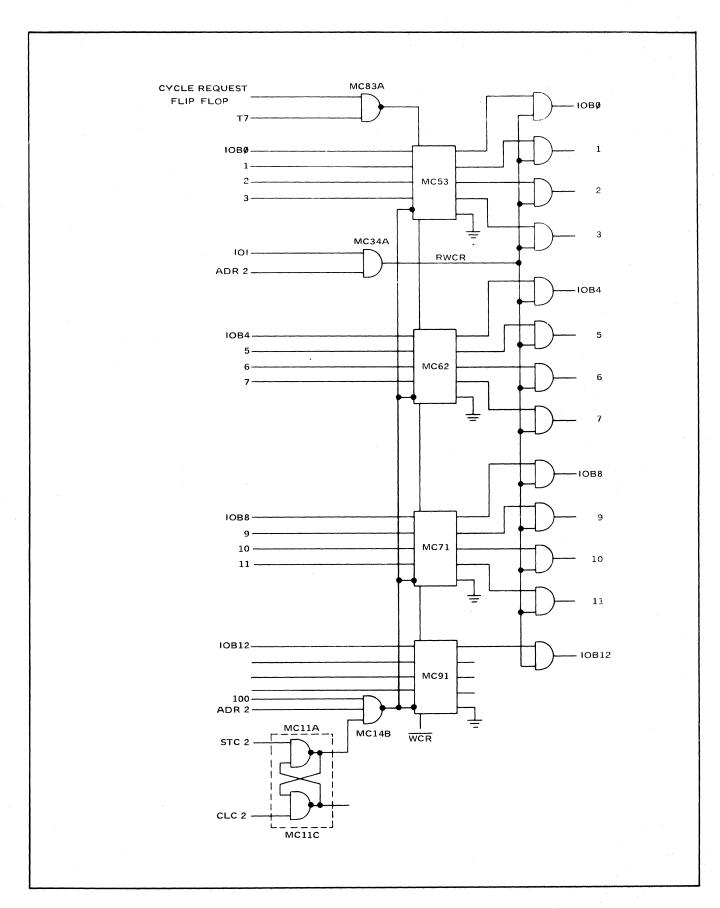

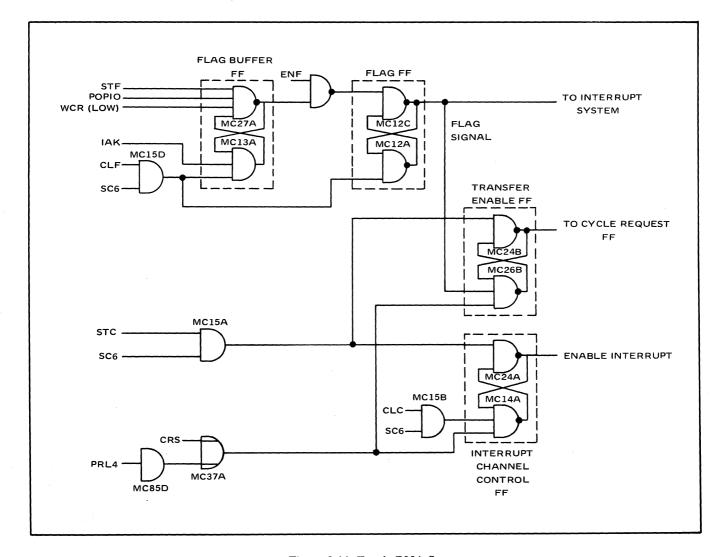

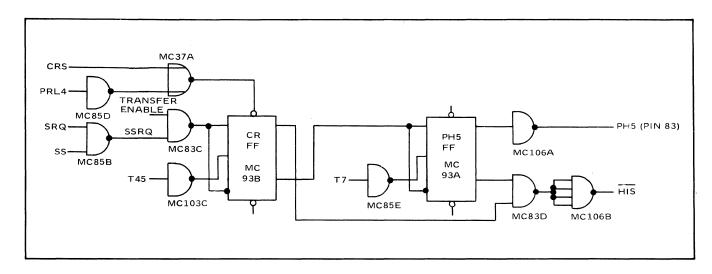

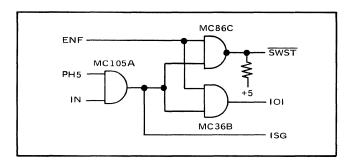

|              | Run-Step FFs and Panel Controls      |       |        | Cycle Request & PH5 Logic 6              |      |

| 4-7.         | Phase Operation                      |       |        | Circuits Unique to Input                 | 5-17 |

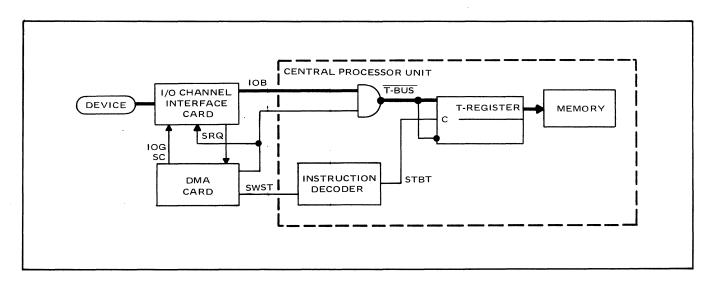

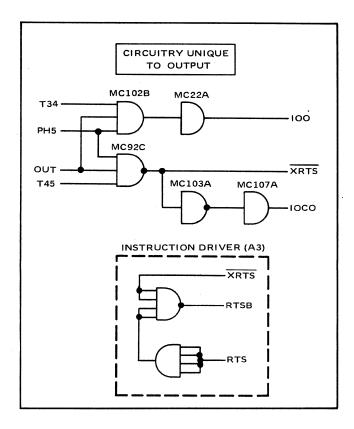

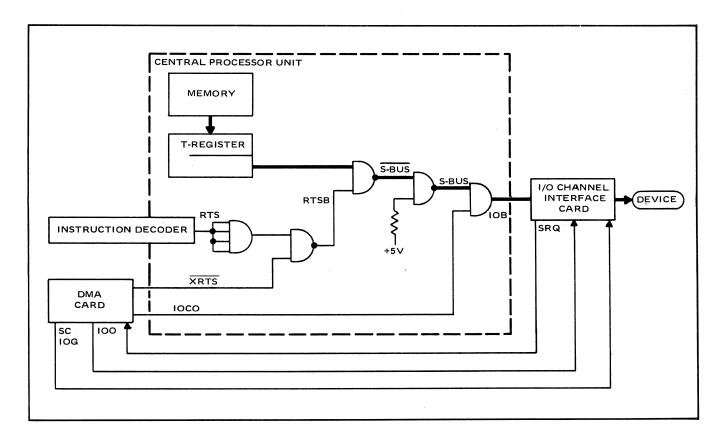

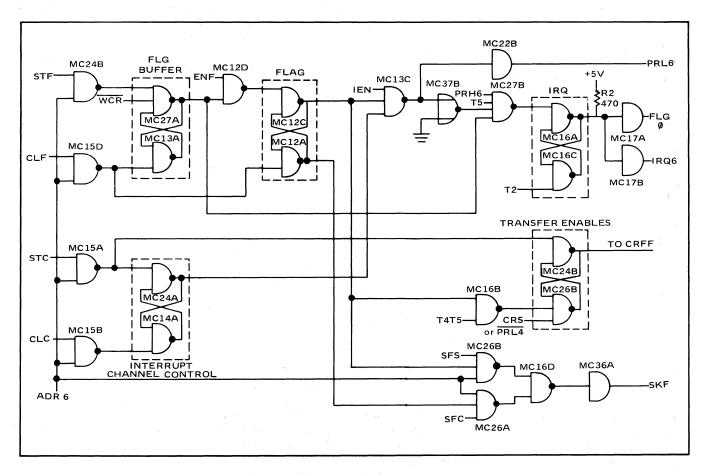

|              | Simplified Block Diagram             |       | 6-14.  | Transferring Data from an External       |      |

| 5-1.         | Memory Timing                        | . 5-1 |        | Device to Memory                         | 5-17 |

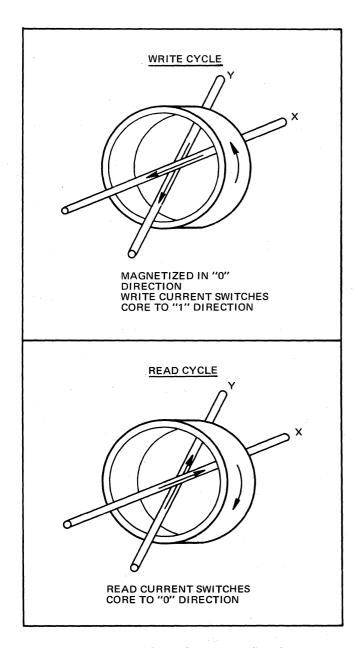

|              | Core Characteristics                 |       |        | Circuitry Unique to Output               | j-18 |

|              | Read Write Currents vs. Core Status  |       | 6-16.  | Transferring Data from Memory to an      |      |

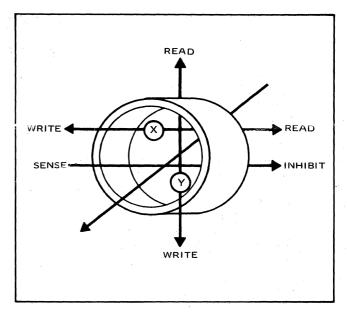

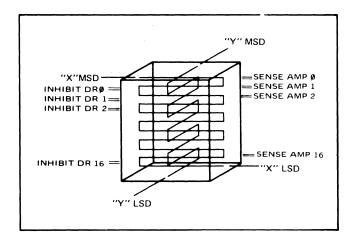

|              | The 4-Wire System                    | . 5-2 |        | External Device                          |      |

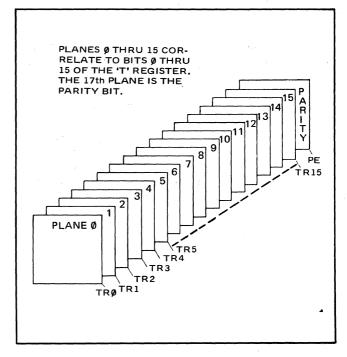

| 5-5.         | Each 4K Core Module has 17           |       |        | Flag & Interrupt Circuits                |      |

|              | 17 Core Planes                       |       |        | Update PH4 Circuitry                     | 5-20 |

|              | Core Module Addressing and Data      |       | 6-19.  | High-Speed Channel Card Functional       |      |

| 5-7.         | The Core Plane                       | . 5-3 |        | Block Diagram                            | 5-23 |

## LIST OF TABLES

| Table | Title                                | Page | Table | Title Page                                |

|-------|--------------------------------------|------|-------|-------------------------------------------|

| 1-1.  | Major Computer Assemblies            | 1-2  | 6-2.  | Basic Sequence for DMA Data Transfer 6-12 |

| 1-2.  | 2114B Integrated Circuit Components  | 1-3  | 7-1.  | Recommended Test Equipment 7-1            |

| 2-1.  | Computer Voltage Bus                 | 2-7  | 7-2.  | State of Front Panel Indicators After     |

| 3-1.  | Front Panel Operating Controls       | 3-5  |       | Power Turn-On                             |

| 4-1.  | Set Phase Conditions                 | 4-7  | 7-3.  | Basic Binary Loader Listing 7-9           |

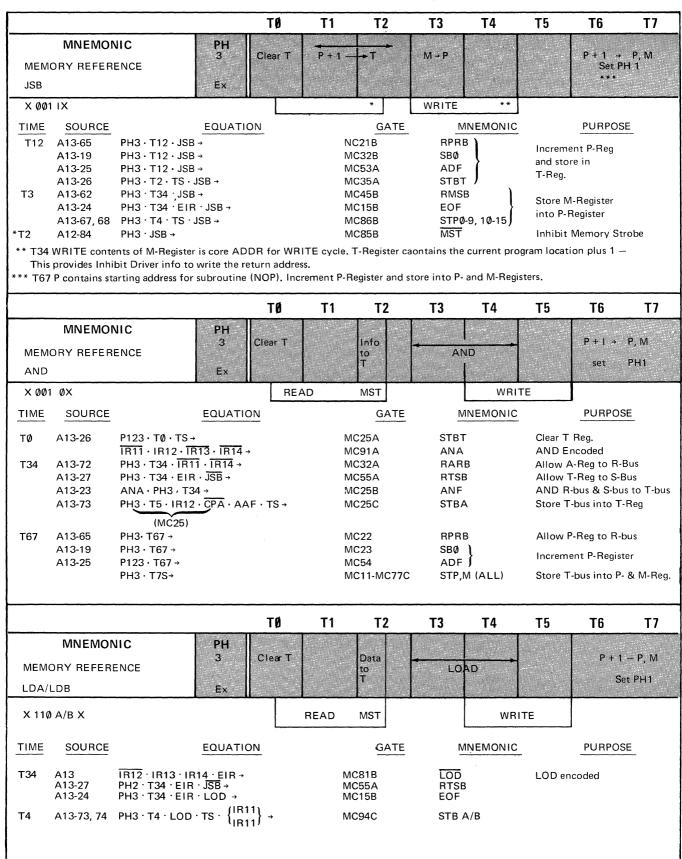

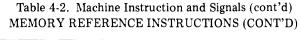

| 4-2.  | Machine Instruction Timing & Signals | 4-10 | 7-4.  | Punched Tape Reader Loading Options7-10   |

| 6-1.  | Typical DMA Program                  | 6-10 | 7-5.  | Loading Halts                             |

# SECTION INDEX

| INTRODUCTION                |    |

|-----------------------------|----|

|                             |    |

| THE POWER SUPPLY            |    |

|                             |    |

| FRONT PANEL                 |    |

|                             |    |

| CENTRAL PROCESSOR UNIT      | IV |

|                             |    |

| MEMORY                      |    |

|                             |    |

| INPUT/OUTPUT SYSTEM         | VI |

|                             |    |

| TROUBLE SHOOTING PROCEDURES |    |

## INTRODUCTION

# SECTION I

#### 1-1. PURPOSE OF 2114B COMPUTER.

1-2. The Hewlett-Packard Model 2114B Computer is a small general purpose digital computer which combines performance and economy with small size. The HP 2114B has full compatibility with HP data measuring and recording instruments as well as a wide range of input/output devices. The HP 2114B is subject to rigid operational and environmental specifications. The logic design and software follow conventional standards of computer usage and notation so that the HP 2114B may also be used as a free-standing device in other types of systems, such as process control, media conversion, data reduction or communication systems. The hardware and software are specifically designed to permit interfacing of real-time devices (i.e., devices running asynchronously with respect to a program being run). The word length is 16 bits. The basic HP 2114B computer includes the processor unit (main frame) with 4,096-word memory.

#### 1-3. PHYSICAL DESCRIPTION OF HP 2114B COM-PUTER.

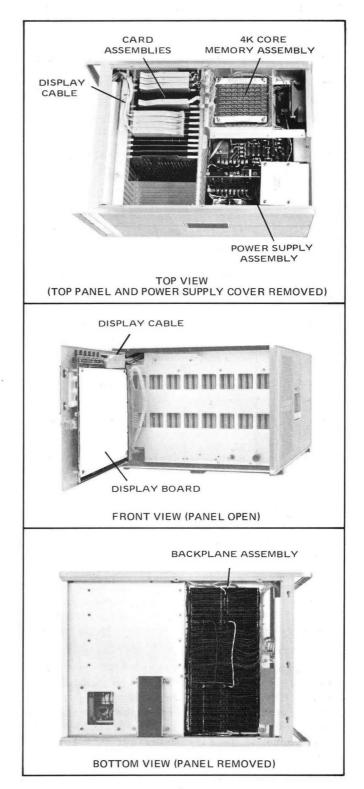

- 1-4. In detailing a physical description of the HP 2114B, the major assemblies that make up the computer are shown in Figure 1-1. The following assemblies will be emphasized as the course progresses.

- a. PLUG-IN CARD ASSEMBLY which contains Card assemblies A1 through A23 that make up the main portion of the Computer's Logic circuits. Each assembly is located on a separate printed circuit card which fits into the Computer's Card Cage.

- b. DISPLAY ASSEMBLIES The Display Board is directly connected to the back of the Front Panel Assembly. The display board contains driver circuits for the front panel lamps, and the sensing assemblies for the Switch Register. The display cable links the Display Board with the Computer's logic cards.

- c. BACKPLANE ASSEMBLY The Computer's Back Plane Assembly is located beneath the card cage and is directly accessed by removing the bottom protective cover. The Back Plane contains power supply buses and interconnecting circuitry for the plug-in cards in the card cage.

- d. POWER SUPPLY The Computer power supply provides regulated DC voltages to the logic circuits, indicator lamps and other computer circuitry.

- e. 4K CORE MEMORY ASSEMBLY The Core Memory Assembly is located behind the card cage on the left hand side of the computer. The core stack makes up the computer's memory storage.

Figure 1-1. HP2114B

f. FRONT PANEL ASSEMBLY — Contains the display registers, Switch Register and Control Switches for the HP 2114B.

Table 1-1. Major Computer Assemblies

| REFERENCE     | ASSEMBLY    | QUANTITY | NOMENCLATURE                |

|---------------|-------------|----------|-----------------------------|

| A1,A2         | 02114-60427 | 2        | Driver Switch Card          |

| A3            | 02114-60429 | 1        | Inhibit Driver Card         |

| A6            | 02114-6005  | 1        | Sense Amplifier<br>Card     |

| A8,A9,A10,A11 | 02114-60424 | 4        | Arithmetic Logic<br>Card    |

| A12           | 02114-60426 | 1        | Timing Generator<br>Card    |

| A13           | 02114-60425 | 1        | Instruction Decoder<br>Card |

| A14           | 02114-6003  | 1        | Shift Logic Control         |

| A15           | 02114-6007  | 1        | I/O Control Card            |

| A24           | 02114-6009  | 1        | Display Board               |

| A25           | 02114-6016  | 1        | Display Cable               |

| A400          | 02115-6042  | 1        | 4K Core Memory<br>Assembly  |

| -             | 02114-60391 | 1        | Backplane Assembly          |

| _             | 02114-6020  | 1        | Power Supply<br>Assembly    |

| A300          | . –         | 1        | Capacitor Board<br>Assembly |

| A301          | 02114-6013  | 1        | Heat Sink Assembly          |

#### 1-5. OPTIONS.

- 1-6. Options for the HP 2114B Computer are of two general types:

- a. Processor Options or options that allow for an increase in memory or in computation capabilities of the basic unit. Examples of such options are the additional 4K of memory or the Direct Memory Access Option now available with the HP 2114B.

- b. Input/Output Options which add input and/or output facilities to the basic HP 2114B Computer. The options, identified by Interface Kit Numbers, provide the circuitry, cabling, and software to enable the computer to operate with a specific input or output instrument (measuring reading, or recording device), or with a series of instruments.

- 1-7. A total of seven (7) available I/O Slots are present in the main frame of the HP 2114B, but this can be extended by seventeen (17) more available slots through the

use of the HP 2151A I/O Extender Option. A greater increase in the input/output capability of the HP 2114B can also be attained through the HP 12595A Multiplexed I/O option which provides for a possible fifty-six (56) extra I/O devices of customer design.

#### 1-8. SOFTWARE.

- 1-9. Software is the totality of programs, routines, manuals, diagrams and operating insturctions. In the case of the HP 2114B, the software consists of the routines and materials supplied by the Hewlett-Packard Company which enables the computer to operate. The owner of a computer has three principal sources of runable programs:

- a. The Manufacturer

- b. User's Group Library

- c. Proprietary, written by his own company.

- 1-10. When troubleshooting or repairing the HP 2114B all hardware problems should be solved first. Once the hardware confidence of the computer is high through hardware diagnostic testing and problems still exist in the computer a software check should be made. An attempt at the program conditions which initially failed to operate properly should be made, which, in turn, may prove to be the problem area. Unfortunately, it may prove to be the most difficult part for the technician because of the intimate marriage between the software and hardware. Trying to understand a strange program, which is probably not documented with flow charts and description, is difficult even for top notch technicians with wide experience. Solving a software problem like this is one of the highest compliments to a technician's expertise.

- 1-11. There are two methods of entering information into the HP 2114B Computer that the technician should know. Information can be entered into the computer either by toggling the routine into the computer with the use of the Switch Register and Control Switches on the Front Panel or through the use of peripheral Input devices such as the HP 2748A Tape Reader or the HP 2752A Teleprinter. The standard method for entering information into the HP 2114B is through the use of punched tapes since all standard HP Program Software is produced on punched tape for convenience to the customer.

#### 1-12. LOGICAL TROUBLESHOOTING.

- 1-13. The operating computer system is rather complicated. There are certain techniques that the technician can use to simplify the troubleshooting problem. These techniques are covered in Section VII, Troubleshooting Procedures. These techniques allow the isolation of possible faults to smaller functional blocks.

- 1-14. Try to determine the nature of the difficulty from the person reporting a malfunction. Try to outline briefly the software program being used. How was it expected to

function? What were the actual results? Hopefully, problems associated with the misuse of hardware or simple operating errors can be detected at this point.

#### 1-15. INTEGRATED CIRCUIT DESCRIPTION.

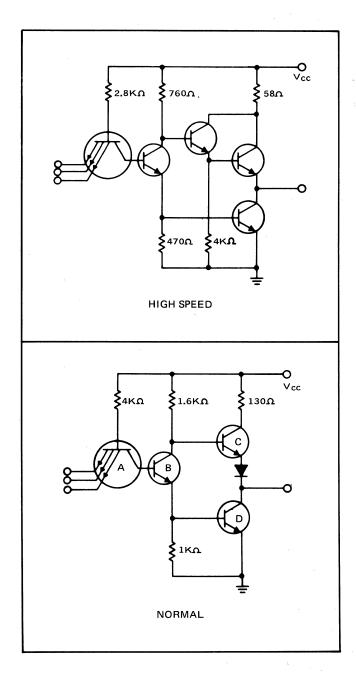

1-16. The logic type selected for use in the 2114B Computer is the TTL family. It requires only a +5.0 volt

power supply and ground. The HP 1820-0956 CTL (Complementary Transistor Logic AND gate is used to buffer input and output levels for compatibility with the HP family of I/O interface devices. Refer to Table 1-2 for stock number and description.

1-17. The TTL family is a high speed saturating logic. Characteristics for the normal family follow. Typical pro-

Table 1-2. 2114B Integrated Circuit Components

| HP STOCK NUMBER | DESCRIPTION                             | MFG. TYPE |

|-----------------|-----------------------------------------|-----------|

| 1820-0054       | *TTL Quad 2-input NAND                  | 7400N     |

| 1820-0063       | Dual 2-wide 2-input AND-OR-INV          | 7451N     |

| 1820-0065       | J-K FF                                  | 7470N     |

| 1820-0068       | Triple 3-input NAND                     | 7410N     |

| 1820-0070       | 8-input NAND                            | 7430N     |

| 1820-0071       | Dual 4-input NAND                       | 7440N     |

| 1820-0074       | 4-wide 2-input AND-OR-INV               | 7454N     |

| 1820-0075       | Dual J-K Master/Slave FF                | 7473N     |

| 1820-0077       | Dual D FF                               | 7474N     |

| 1820-0084       | 4-wide 2-input AND-OR-INV Exp           | 7453N     |

| 1820-0085       | Dual 4-input Exp                        | 7460N     |

| 1820-0105       | Linear Ckt Voltage Reg                  | SL6160    |

| 1820-0111       | 1 out of 10 Decoder                     | 930159X   |

| 1820-0127       | Quad 2-input NAND                       | 900259X   |

| 1820-0129       | Triple 3-input NAND                     | 900359X   |

| 1820-0130       | Dual 4-input NAND                       | 900459X   |

| 1820-0132       | Hex Inverter                            | 901659X   |

| 1820-0183       | Differential Amplifier                  | CA3028    |

| 1820-0233       | Up/Down Counter                         | SN10625   |

| 1820-0301       | Quad Latch Buffer (D FF)                | 7475N     |

| 1820-0305       | Full Adder                              | 7483N     |

| 1820-0310       | DTL Triple 3-input NAND                 | 15862N    |

| 1820-0327       | Quad 2-input NAND                       | 7401N     |

| 1820-0328       | Quad 2-input NOR                        | 7402N     |

| 1820-0370       | HS Quad 2-input NAND                    | 74H00N    |

| 1820-0371       | HS Triple 3-input NAND                  | 74H10N    |

| 1820-0372       | HS Triple 3-input AND                   | 74H11N    |

| 1820-0374       | HS Dual 4-input AND                     | 74H21N    |

| 1820-0377       | HS Dual 2-input AND-OR-INV Exp.         | 74H50N    |

| 1820-0378       | HS Dual 2-wide 2-input AND-OR-INV       | 74H51N    |

| 1820-0379       | HS 4-wide 2-2-2-3-input AND-OR Exp.     | 74H52N    |

| 1820-0380       | HS 4-wide 2-2-2-3-input AND-OR-INV Exp. | 74H53N    |

| 1820-0381       | HS 4-wide 2-2-2-3-input AND-OR-INV      | 74H54N    |

| 1820-0382       | HS 2-wide 4-input AND-OR-INV Exp.       | 74H55N    |

| 1820-0383       | HS Dual 4-input Expander                | 74H60N    |

| 1820-0384       | Triple Dual 4-input Expander            | 74H61N    |

| 1820-0956       | CTL Dual 2-input AND Buffer             | SL3459    |

<sup>\*</sup> Except DTL and CTL as noted.

pagation delay is 13nsec per gate and 40nsec per flip flop. Power dissipation is 10 MW per gate and 60 MW per flip flop. Operating temperature range is 0°C to 70°C which is more than adequate for the 2114B.

1-18. The logic is built around the NAND gate. Figure 1-2 is a sample of the circuit with approximate resistor values shown.

Figure 1-2. TTL "NAND" Basic Building Block

1-19. A high speed version is used in some applications where higher fan out or improved speed is necessary. The power requirement doubles and the propagation delay halves compared to the normal unit.

#### 1-20. OUTPUT.

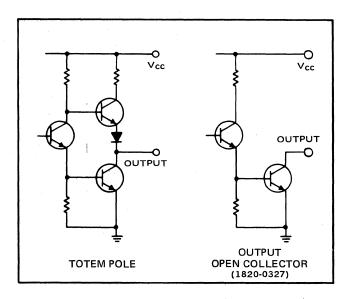

- 1-21. The totem pole output in the normal device gives a "one" output impedance of about 70 ohms. This helps provide good noise immunity. The logical "one" output has a guaranteed value of 2.4 volts minimum. Fan out, and drive criteria are based on a minimum of 2.0 volts which provides a noise immunity safety band.

- 1-22. The logical "zero" level is guaranteed at 0.4V maximum. Fan out and drive requirements are determined at 0.8V which provides a noise immunity safety band. An individual gate will normally change state as the input increases to about 1.4 volts.

#### 1-23. CIRCUIT OPERATION.

- 1-24. The TTL family is designed around the basic NAND circuit. Any number of emitters can be provided in the input transistor. Any one of the emitters pulled down to a logical "zero" will saturate transistor A pulling the collector voltage down. This holds off transistor B. The output is pulled high by the 1.6K resistor pulling up on the base of transistor C.

- 1-25. When all emitters are at the logical "one" level transistor B base to collector junction acts like a diode. It pulls up the base of transistor B, and both B and D are conducting. The output goes low through saturated transistor D.

#### 1-26. FAILURE.

1-27. The common failure modes include shorting in the output transistors which can hold the output either high or low. Failure in the input typically shorts emitter to emitter. This can pull an inter-connection bus high by virtue of the shorted emitters.

#### 1-28. OR TYING.

The totem-pole output precludes OR tying gates together because of the current limitations corresponding to each integrated circuit. Each TTL integrated circuit added through OR tying the outputs together produces an additional load in parallel to the other TTL integrated circuits. This additional load which is in parallel with the other loads provided by other integrated circuits reduces the total load of the circuit thus allowing an increase in current draw. This increase in current will exceed the limitations of each TTL integrated circuit and will begin to "blow" I.C. packs. Figure 1-3 shows the open collector output (alongside the normal output). One quad 2-input NAND gate is made this way - HP Stock No. 1820-0327. It allows OR tying for negative true signals. It is used extensively in the 2114B logic design, refer to the Bus structure design on the Arithmetic Logic assembly.

Figure 1-3. Open Collector

#### 1-30. CTL COMPARISON.

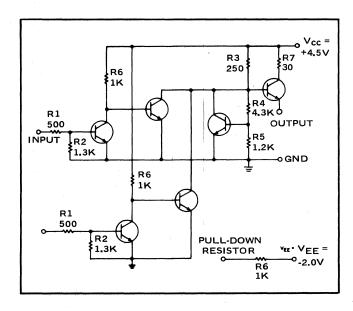

1-31. The CTL family used extensively in Hewlett-Packard computers differs somewhat in characteristics from the TTL logic. It requires a +4.5V supply and a -2.0V supply. The input circuit is a transistor base with the tie down resistors to -2.0V or ground. The output is an emitter follower and can be OR tied in positive true direction. A logical "zero" output is -0.3 volts. A logical "one" output is +2.3 volts. (Refer to Figure 1-4.)

Figure 1-4. CTL Typical Circuit (1820-0956)

1-32. The use of the CTL integrated circuits in the HP 2114B is to allow "OR" tying in the positive true sense and to amplify signals that are sent to other sections in the computer.

#### 1-33. TYPE D FF.

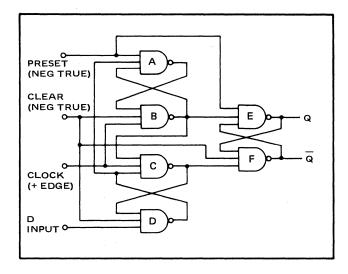

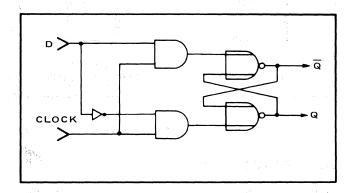

1-34. A commonly used TTL circuit is the 1820-0077 Dual D type positive edge triggered flip flop. The FF is made up of NAND gates as shown in Figure 1-5. The preset and clear signal inputs are both negative true. Either (or both) negative will inhibit the FF operation.

1-35. When preset and clear are both high the state of the D input establishes certain conditions. The change in the clock input from low to high state will complete the establishment of the FF state. A subsequent change of D input level (even with the clock remaining high) will not affect the FF output. Figure 1-5 shows the functional block diagram.

Figure 1-5. D Type Flip Flop (+ Edge Trigger)

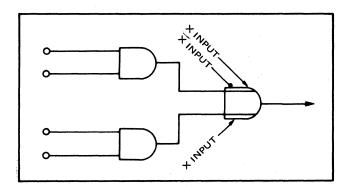

#### 1-36. AND-OR EXPANDERS.

1-37. Because of the OR tie limitations inherent in the totem pole output stage a family of expandable OR circuits was developed. The basic circuit is an AND-OR structure. The output may be true or inverting. The OR or NOR output stage may accept additional inputs. These are of two types. In one a single true input permits an additional OR, the other requires both true and complementary inputs for the additional OR input.

Figure 1-6. AND-OR Expander

#### 1-38. BINARY FULL ADDER.

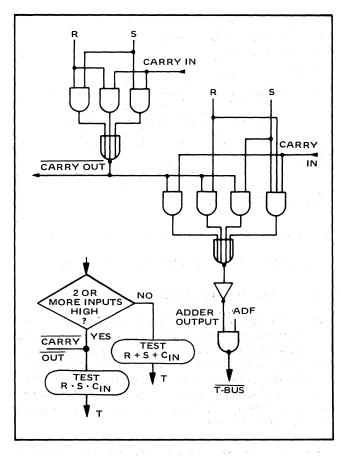

- 1-39. The Full Adder is used on the arithmetic logic assembly for arithmetic adding operations. The R and S buses and the carry in are compared two by two. If at least two are high a carry out (negative true) is generated.

- 1-40. If no carry out is generated either R, S, or Carry in can provide a T bus output. The presence of R, S, and Carry in will also generate a T bus output.

- 1-41. A glance at the adder circuit on the Arithmetic schematic will disclose that the R and S inputs are inverted in the second and fourth circuits, and the T bus output is inverted in the first and third. The polarity of the Carry out changes between each stage.

Figure 1-7. Binary Full Adder

1-42. The parallel add - serial carry requires a typical delay of 8 nsec per stage. Whenever the 2114B uses the full adder two timing cycles are used (500 nsec) to insure adequate time for completion.

#### 1-43. "D" LATCH.

1-44. The flip flop follows the D input so long as the clock input is positive. The current FF condition is retained as the clock goes negative. HP Stock No. 1820-0301. Refer to Figure 1-8.

Figure 1-8. D Latch (1820-0301)

#### 1-45. IC REPLACEMENT.

- 1-46. The replacement of Integrated Circuit packs on the Printed Circuit board requires care. Too much heat can "measle" the board ruining its appearance. Too much heat or aggressive mechanical manipulation can damage the plating around holes.

- 1-47. An effective way to replace an IC pack follows: Cut the body out. A sharp diagonal cutting pliers will allow cutting each leg individually. Remove each leg individually. Care must be exercised so that undue stress is not produced which might damage the plated hole. Use a light soldering iron with a tiny tip to remove each leg (from the component side). Each hole can be cleaned out with a round tapered toothpick (its size may have to be reduced to fit in the hole) or a vacuum device.

- 1-48. The new IC pack can be inserted, and carefully soldered. The rosin flux can be removed with Alpha cleaner (or other commercial product).

## THE POWER SUPPLY

# SECTION II THE POWER SUPPLY

#### 2-1. INTRODUCTION.

#### 2-2. PHYSICAL CONSTRUCTION.

- 2-3. The physical parts of the power supply assembly consist of the rear panel of the instrument which houses the line filter, the fans and the voltage bus test points. The heat sink assembly contains those elements which dissipate significant amounts of power. The transformer, capacitor board and the capacitor assembly are mounted to the deck. The regulator board is a plug-in board containing the small components associated with the primary regulator, +20 volt regulator, and power fail detect circuitry. The outputs of the power supply are the voltage buses with wiring attached to the computer back plane. All cabling associated with the primary regulator and AC line is physically separated from the DC voltage bus cabling. This is a precaution for personnel safety.

- 2-4. The 2114B power supply is a 50-60 Hz, 115 volt AC input only. A step down transformer is required for operation from a 230 volt line. It is a dissipative type power supply. Any line voltage in excess of the minimum required is dissipated in the form of heat. This heat is dissipated primarily by those components situated on the heat sink.

- 2-5. The power supply consists of four basic sections:

- a. The primary regulator establishes an input voltage of 83 volts to the primary of this transformer (T1).

- b. The DC voltage buses are simply full wave rectifier, capacitor filter buses, and depend on the transformer turns ratio to determine the actual voltage.

- c. The +20 volt regulator is a stable regulator with temperature compensation for the memory circuits.

- d. A power fail circuit senses power failure and also provides a turn-on delay.

- 2-6. The purpose of this lesson on the power supply will be to study the circuits and gain a familiarity with how they operate. It will discuss the safety precautions. A laboratory session will deal with wave shapes, trouble-shooting and actual fault analysis.

#### 2-7. EQUIPMENT FOR MAINTENANCE.

- 2-8. The equipment needed for the maintenance of the HP 2114B Power Supply is as follows:

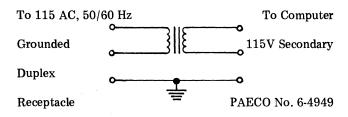

- a. Isolation Transformer 115V:115V 800 volt-amp capacity (For 60 Hz operation only, 550 volt-amp will be adequate)

- b. Variable AC Autotransformer 50/60 Hz, 7 amp.

- c. Oscilloscope HP 180A or equivalent HP 1801A Vert Amplifier HP 1720 Time Base HP 10004A Probes

- d. Multimeter HP 427A

For +20V bus improved accuracy is desired such as HP 412A or HP 3430A.

#### WARNING

Dangerous voltages are present in the computer even when the Power Switch S1 is in the OFF position. Do not attempt to remove the protective cover of the Power Supply, or attempt maintenance of any kind in area of the Power Supply, unless the power cord has first been removed from the power source. Do not energize the Power Supply during servicing unless an isolation transformer is connected between the main power source and J1 at the rear of the Computer. Use caution when making test measurements. Failure to heed this warning could result in death or injury.

#### 2-9. SAFETY PRECAUTIONS.

There are safety hazards associated with trouble-2-10. shooting and maintaining this power supply which differ from typical power supplies. The primary regulator determines the AC level to the primary winding on the transformer. All of the circuitry associated with the AC line thus is hot (i.e., connected electrically to the AC line). The series regulators, the regulator board, and the voltage and overload current protection circuits are all superimposed on the AC line voltage. Utmost care must be used in troubleshooting. Fault analysis and repair should not be performed without using an isolation transformer which allows this primary regulator circuit to float. Thus any single point can be grounded and become a reference node. Without this isolation transformer it is extremely difficult to troubleshoot the primary regulator circuit.

2-11. Periodic inspection of the insulation and cabling, especially following the replacement of components will establish that the insulation is still intact. Faulty insulation may result in serious danger to personnel, and to equipment. The routing of the cables must not be disturbed which may lead to contact between AC regulator circuitry and DC buses.

#### 2-12. CIRCUIT DESCRIPTION.

#### 2-13. PRIMARY REGULATOR.

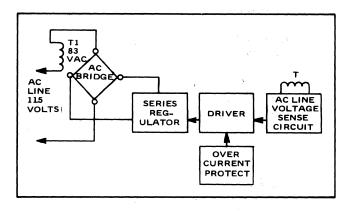

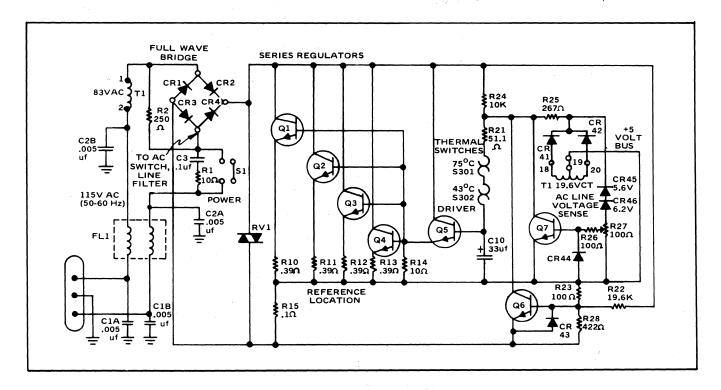

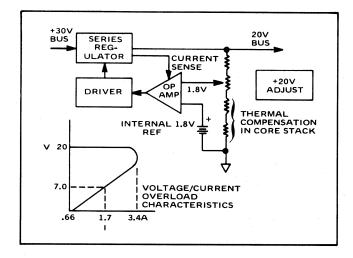

2-14. Figure 2-1, the block diagram of the Line Regulator, shows the 115 volt AC line supplying the transformer T1 winding and the series regulator circuitry. The winding design voltage is 83V AC. The series regulators

Figure 2-1. Line Regulator Block Diagram.

absorb the excess voltage. Because it is not convenient to work with AC voltage in semi-conductor circuits a full wave bridge converts to pulsating DC. This allows the series regulators to be DC circuits instead of bi-polar.

2-15. The series regulators require a driver for current amplification. The driver is controlled by two circuits: The AC line voltage circuit which establishes the 83 volts on the primary of the transformer, and the over-current protection circuit which prevents short circuits or other malfunctions from drawing excessive current through the series regulators.

2-16. A partial schematic of the primary regulator is shown in Figure 2-2. Capacitors C1 and C2 together with line filter FL1 provide noise filtering. Resistor R1 and capacitor C3, located in the Power Switch Turn-on Circuit, are used as an arc suppressor to prevent arcing caused by inductive kick-back from this primary of T1. This inductive kick-back from the primary windings will occur during turn-off and could possibly cause the Power Switch to burn up. R1 and C3 will protect against this burn up. Diodes CR1, CR2, CR3 and CR4 make up a full wave rectifier to convert the AC voltage to pulsating DC. The pulsating DC is applied to the series regulators made up of transistor Q1. Q2, Q3 and Q4. By controlling the current flow through the series regulator the voltage drop across the primary winding of transformer T1 is limited to a maximum of 83 volts. The series regulators are driven by Q5 which provides the required base current for regulation. The driver Q5 is in turn controlled by two circuits, the AC voltage sense circuit and the over current protection circuit.

Figure 2-2. Primary Regulator

2-17. The varistor RV1 across the full-wave rectifier, CR1, CR4, protects against high voltage spikes. At voltages in excess of 140V RMS the varistor breaks down, providing a low impedance to high noise spikes or an essential short to the high noise spikes. With respect to high frequency spikes, capacitor C10 is used in conjunction with R21 to filter out high frequency noise that may occur into the base of the driving transistor Q5. This will prevent the primary regulator circuit from operating in a sporadic fashion upon the occurence of these high frequency spikes.

#### 2-18. THE AC VOLTAGE SENSE CIRCUIT.

- 2-19. The AC Voltage Sense Circuit uses a separate transformer winding and diodes CR41 and CR42 provide full wave rectification for the sense voltage which is applied to the zener breakdown diodes CR45 and CR46.

- 2-20. The Zener diodes CR45 and CR46 will break down when 11.8V is sensed from the sense secondary. Transistor Q7 will begin to conduct at 12.4V causing a drop in the collector voltage. The voltage on the base of Q5 is reduced, reducing the base drive to the series regulators. The increased resistance of the series regulators causes the voltage applied to the primary to drop, maintaining the required 83 volts.

#### Note

The series regulators dissipate all power due to excess line voltage to the supply. This requires that the heat sink assembly and fan filters should be kept clean in order to allow propwer heat dissipation.

#### 2-21. OVERCURRENT PROTECTION.

2-22. The operation of the overcurrent protection circuit is as follows: All of the line current must flow through resistor R15. When the voltage drop across R15 increases sufficiently, transistor Q6 is turned on and the collector voltage drop reduces the base drive to Q5 so as to limit current at this level. It requires approximately 10 amps peak (4.1 RMS) to initiate this overcurrent action. Resistor R22 provides base current to Q6 depending on the AC line voltage. This reduces some what the critical current through R15 at elevated line voltages, and helps limit the peak dissipation of the regulators.

# 2-23. PRIMARY REGULATOR — TROUBLESHOOT-ING.

#### 2-24. ISOLATION TRANSFORMER.

2-25. It is necessary in troubleshooting the primary regulator that this circuit be isolated from the AC line. This is accomplished by using an isolation transformer. The isolation transformer should have a one to one ratio and be capable of handling 600 to 800 volt-amps. Such a large capacity is necessary because of the large peak to average

currents in this supply. A transformer and variable AC autotransformer with less capacity may cause poor operation.

#### 2-26. REGULATOR AND DRIVER SHORTS.

- 2-27. A convenient troubleshooting aid is to remove the primary regulator board. When this board is removed Q5 does not provide drive current and the line regulators remain off. There will be some voltage applied to the primary of the transformer because of the current path through resistor R2 (250 ohms). This provides sufficient primary current so that there will be 1.5 or 2 volts present on the 5 volt bus and proportional amounts on the other voltage buses.

- 2-28. There should be no current through the series elements Q1 to Q4. This can be determined by measuring the voltage drop across emitter resistors R10, 11, 12, and 13. (These are physically located on the Kingman board to the rear of the heat sink assembly.)

#### 2-29. REGULATOR AND DRIVER OPEN CIRCUIT.

2-30. Operation of the Regulator transistors can be checked without the regulator board by providing base drive. Use the isolation transformer and variable AC autotransformer in the line. Start with the AC autotransformer turned all the way down. Turn on Driver Q5 by connecting its base (+ terminal of C10 on Kingman Board) to the collector of Q1 or Q2 (on top side of heat sink) through a 1K resistor (1/4W ok). Use common node of R10-R15 for scope ground.

#### WARNING

This provides full line voltage to T1 primary. The line voltage should not exceed 85 to 90 volts. Now it is necessary to protect the power supply manually. You no longer have voltage or overcurrent protection. This requires that the input AC line slowly be increased with the variable AC autotransformer while carefully monitoring both voltage and current of the line. This procedure will establish that the regulators, driver, and AC bridge are capable of proper operation. Operation of the 5V bus should be an adequate indication. The above procedure will provide 5 volts DC with 0.3V P to P ripple at 85V AC Line.

#### 2-31. WAVESHAPES.

- 2-32. With the regulator board installed viewing waveshapes in the AC voltage sense and overcurrent circuits is a powerful troubleshooting aid. Specific changes take place as a function of line voltage. Use variable AC autotransformer and isolation transformers.

- 2-33. The regulator voltage (collector Q1 to R15) will have spikes as the AC line crosses zero voltage (figure 2-3). They are caused by the transformer flux decay as the diode bridge ceases to conduct. The voltage level is stable and they re-

peat each 8.3 milliseconds. As the voltage is increased to 85V the regulators will begin to show a voltage peak. This collector voltage increases to 60V peak-to-peak at high line.

2-34. The collector waveshape of Q7 increases until at 83V line voltage it develops a dip. (Refer to Figure 2-4.) The increased base drive to Q7 (with increasing line voltage) results in the collector dropping to a level which maintains the 83V input to T1.

#### 2-35. THERMAL SWITCHES.

2-36. The computer power supply could be damaged by an increase in ambient temperature. Thermal Switches S301

and S302 provide protection by shutting off the base drive to the series regulators and effectively turning the power supply off. Thermal Switch S302 is set to open at 43° centigrade and is located in the air stream directly behind fan B1. Thermal Switch S301 is set to open at 75° centigrade and is located on the heat sink assembly.

#### 2-37. HEAT DISSIPATION.

2-38. It is important that the filters on the fan assemblies be checked and cleaned as necessary at frequent intervals.

2-39. At high line and maximum current each transistor must dissipate over 100 watts peak. To accomplish this,

Figure 2-3. Q1 Collector Waveshapes

these transistors are mounted individually on each of the four vanes on the heat sink assembly. In addition to the four series regulators, the Q5 driver transistor, two regulators in the +20 volt circuit, and the 4 diodes in the AC bridge are also located on the heat sink assembly. It is not wise to leave the computer in the overload current mode for extended periods of time.

#### 2-40. TRANSISTOR INSULATORS.

2-41. Care must be exercised in working around the Heat Sink Assembly. The mica insulators for Q1 to Q5 are special insulators of larger physical size (HP 0340-0458). The high voltage noise spikes that may be on the AC line require insulators which will safely handly 1000 to 1500

volts. The mica protrudes over the edge of the heat sink. The mica edge must not be cracked, bent, or broken.

- 2-42. A thin uniform layer of silicon grease must be used on both surfaces of the insulator to insure adequate thermal conductivity.

- 2-43. When replacing the diodes do not allow them to rotate. Rotation will score and damage the mica insulators.

#### 2-44. UNREGULATED SUPPLIES.

2-45. The power supply contains several unregulated DC voltage supplies for the computer's logic circuits and in-

Figure 2-4. Q7 Base and Collector Waveshapes

Figure 2-5. Q5 Emitter Waveshapes

dicators. The supplies, +30V, +30 volt lamp supply,  $\pm 12V$ , +5V and -2V are shown in Figure 2-6.

2-46. The voltage buses of the power supply are brute force (no voltage control or current limit), full wave rec-

tifier, capacitor input lines. All cicruicts have fuse protection with the exeption of the +5 volt bus. The high current protection of the +5 volt bus is provided by the primary regulator overcurrent protection. The actual DC voltage of these buses is established by the turns ratio of

Figure 2-6. The Unregulated Buses

the transformer windings. Proper adjustment of the line regulator establishes the +5 volt bus. The other buses fall where they will.

2-47. An important troubleshooting aid on these voltage buses is the DC voltage as well as the AC ripple on each bus. It will be noted that each large capacitor has a protection diode across it which reduces the danger due to inadvertent reverse voltage connection. The plus 30 volt lamp supply is independent of the normal +30 volt supply. Its filtering requirements are minimal so the acceptable ripple is sub stantially higher. Otherwise, the supplies are similar. Refer to Table 2-1 for normal operating voltage levels.

Table 2-1. Computer Voltage Bus

| VOLTAGE   | MAXIMUM  | MINIMUM | AC RIPPLE    |

|-----------|----------|---------|--------------|

| BUS       | *        | **      | PEAK-TO-PEAK |

| + 5V      | 5.5V     | 4.3V    | 0.5V         |

| +12V      | 13.0V    | 11.8V   | 0.3V         |

| -12V      | -13.0V   | -11.9V  | 0.3V         |

| - 2V      | - 2.8V   | - 1.9V  | 0.4V         |

| +30V      | 32.0V    | 29.0V   | 0.5V         |

| +30V Lamp | 32.5V    | 28.0V   | 3.0V         |

| +20V      | 19.5V*** | 19.5V   | 0.01V        |

- \* High AC Line, minimum computer load.

- \*\* Low AC Line, maximum computer load.

- \*\*\* Depends upon ambient temperature. 19.5V dc nominal for 72°F to 80°F.

#### 2-48. THE +30V SUPPLY.

2-49. The voltage for the +30 volt logic supply is determined by the turns ratio of the transformer. Diodes CR5 and CR6 provide fullwave rectification. Diode CR7 protects the filter capacitor C21 from damage due to reverse voltages. The +30 volt supply also provides a lightly filtered input to the regulated +20 volt memory supply.

#### 2-50. +5V SUPPLY.

2-51. The voltage for the +5 volt logic supply is determined by the turns ratio of the transformer. Diodes CR8 and CR9 provide full wave rectification. Diode CR10 protects filter capacitors C31, C32, and C33 from damage due to reverse voltages.

#### 2-52. -2V SUPPLY.

2-53. The voltage for the -2 volt supply is determined by the turns ratio of the transformer. Diodes CR17 and CR18 provide full wave rectification. Diode CR19 protects filter capacitor C51 from damage due to reverse voltages.

#### 2-54. ±12V SUPPLY.

2-55. The voltage for the  $\pm 12$  volt supply is determined by the turn ratio of the transformer. Diodes CR11, CR12,

CR13, and CR14 provide fullwave rectification. Diodes CR15 and CR16 protect filter capacitors C41 and C42 from damage due to reverse voltages. The power failure detection circuits monitor the  $\pm 12$  volt supply windings.

#### 2-56. +30V LAMP SUPPLY.

257. The voltage for the +30 volt lamp supply is determined by the turns ratio of the transformer. Diodes CR20 and CR21 provide fullwave rectification. Diode CR22 protects filter capacitor C52 from damage due to reverse voltages. The +30 volt lamp supply is only lightly filtered.

# 2-58. TROUBLESHOOTING THE UNREGULATED SUPPLIES.

2-59. It is imperative that the high current carrying lines have good connections because of the extremely high peak currents. All of the mechanical connections in the 5V bus must be checked to determine that they make good contact. A poor connection in the 5 volt circuit compensated by raising the input regulator obviously will make all other voltage buses excessive. If error or fault occurs in only one or two of these nonregulated voltage buses the chances are good that it will be associated with either the rectifiers or transformer windings. Check that the diodes are installed and operating correctly and that the transformer center tap and voltage windings are properly connected.

#### 2-60. 60 CYCLE RIPPLE.

2-61. If analysis of all voltage buses indicates the presence of 60 cycle ripple rather than 120 cycle ripple it may indicate that one of the diodes in the AC diode bridge or that one of the diodes or transformer windings in the voltage sense circuit is open so that voltage regulation is accomplished each half cycle.

#### 2-62. FUSES.

2-63. It will be noted that the fuses are connected between the rectifier and capacitor in some cases. This means the fuses are subjected to RMS currents which are higher than the average DC output of the respective buses. This may account for fuse failure apparently below its rating. 60 cycle ripple present in one or two buses would indicate trouble in the transformer winding or rectifier associated with the specific voltage bus.

#### 2-64. +20 VOLT REGULATOR.

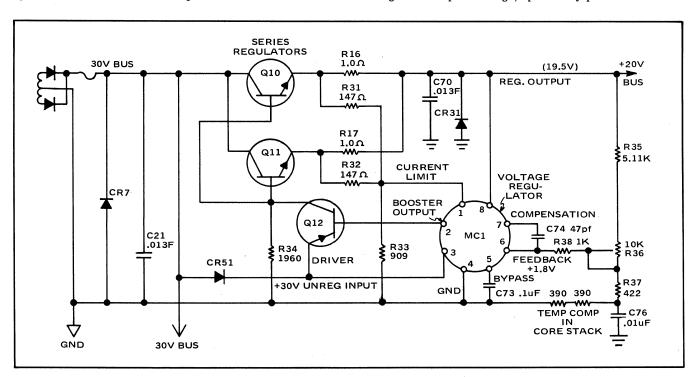

2-65. A glance at the block diagram (Figure 2-7) shows that this +20 volt regulator consists of series regulating elements with an appropriate driver, a complex integrated circuit, and the voltage adjustment potentiometer with several temperature compensation resistors. The sophisticated IC reduces the number of discrete components that are required.

Figure 2-7. 20 Volt Regulator Block Diagram

#### 2-66. CURRENT PROTECTION.

2-67. A look at the voltage overload graph shows that the output voltage is very stable up to its maximum established current (which in this case is about 3.5 amps). Above this level any further attempt to increase the current reduces the current delivering capability. This current fold back characteristic affords protection by reducing worse case dissipation.

2-68. Standard circuit operation delivers about 2.5 amps continuously. It is not necessary to measure the overload curve unless circuit failure has damaged components. To spot check the short current operation short out the +20

volt bus before power is applied to the computer. Then bring up AC voltage slowly. The regulator shall stay in the reduced current mode drawing about 0.8 amp with negligible output voltage.

#### 2-69. +20 VOLT REGULATOR ADJUSTMENT.

2-70. The proper DC level is 19.5 V at  $25^{\circ} \pm 2^{\circ} \text{C}$ . [The adjustment for other temperatures is 19.5 V -0.088/°C (Ambient Temp -  $25^{\circ} \text{C}$ .]

2-71. Referring to Figure 2-8, the +30 volt bus (consisting of a full wave rectifier and capacitor filter) is the unregulated power input. The series regulators are transistors Q10 and Q11. These transistors must be able to dissipate the power required at 2-1/2 amps. These transistors are located on the upper rear of the heat sink. The two emitter resistors R16, R17 are located directly behind on the left end of the Kingman card assembly. The bases are driven by the driver transistor Q12 located on the 2114-6010 Regulator assembly. Q12 gets its drive from the IC pin 2 booster output.

2-72. The +20 volt output bus is connected to pin 8. Output current goes through the series elements and the emitter resistors. The emitter resistors provide current balancing so that each transistor dissipates approximately half the load. If either of the transistors is destroyed or becomes inoperative the other is apt to become destroyed also. Check to insure both transistors are conducting. This can be done by measuring the voltage drop across the two emitter resistors.

2-73. The other inputs include: pin 4 ground, pin 3 unregulated input voltage, pin 5 by-pass for internal

Figure 2-8. 20 Volt Regulator

circuitry, pin 6 is the feedback point for voltage control, pin 7 allows frequency compensation to prevent oscillation.

- 2-74. Pin 6 is a voltage feedback node and compares the circuit voltage with an internal reference. The resistor sting consists of R35, R36, R37 and two temperature compensating resistors which are physically located in the core stack. The normal DC operating level for Pin 6 is about 1.8 volts.

- 2-75. Pin 1 senses the current being drawn through the regulating circuit and allows the overload characteristic for protection of the series elements. When the voltage between pins 1 and 8 exceeds about 0.7 volts it reduces the current pin 2 can provide.

#### 2-76. +20 VOLT REGULATED BUS — TROUBLE-SHOOTING.

- 2-77. An analysis of the DC levels is the most expedient way to troubleshoot the circuit. Check first that the +30 volt unregulated bus is normal. The input voltage level to pin 6 integrated circuit the feedback point should be approximately 1.8 volts when it is operating. As the +20 volt adjustment is made with potentiometer R36 the voltage change at pin 6 is negligible. The adjustment range of this circuit is from 2 volts to 30 volts.

- 2-78. The voltage relationship of pins 2 and 3 are stable regardless of actual adjustment of the 20 volt bus. Pin 3 is approximately 0.7V below the +30 volt unregulated bus. Pin 2 is about 0.7V below pin 3. Pin 1 to pin 8 voltage is a measure of the current being supplied by the regulator (voltage drop on emitter resistors of the regulators). When pin 1 exceeds pin 8 by 0.7 volts the booster output of pin 2 is reduced and the regulator enters the current fold back protection mode.

#### 2-79. TEMPERATURE COMPENSATION.

2-80. The temperature compensating resistors are located in the core stack. An allowance should be made of approximately 88 millivolts/degree C for voltage adjustment at temperatures other than 23-27°C (72-80°F) ambient. The voltage bus should be decreased by 88 millivolts per degree C. A decrease in temperature below normal ambient will require a voltage increase of 88mv/°C.

#### 2-81. COMPENSATION RESISTORS.

2-82. The only check of the temperature compensating resistors is a simple resistance measurement. A value of 675 to 900 ohms is an acceptable value. The component has a +7400 PPM/°C temperature coefficient. In case of component failure the computer can be brought up by substituting the closest resistor value available. Run Memory Checkerboard Program while slowly increasing voltage and note voltage at failure. Then restart the test and decrease the voltage to failure point. Set voltage at the middle of the range. This will result in a reduced temperature operating

range, but will suffice until the correct replacement can be obtained and installed.

2-83. The TC resistors are vendor supplied, and are not available through Hewlett-Packard. They are Texas Instruments sensistor TM 1/8W, 390 ohm  $\pm$  10%, +0.7% per  $^{\circ}$ C. The closest substitute available through HP stock is 0811-2031 815 ohm, +5900 PPM/ $^{\circ}$ C. Mount substitute on feedthrough insulators on memory bracket.

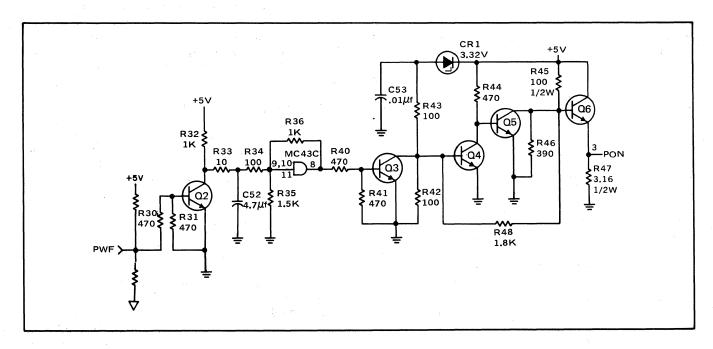

#### 2-84. POWER FAIL DETECT CIRCUIT.

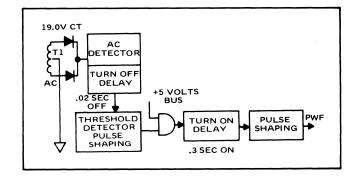

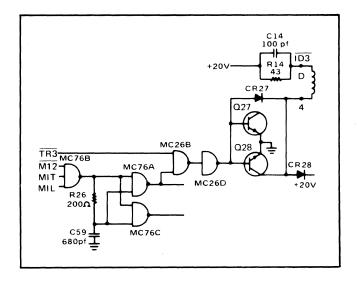

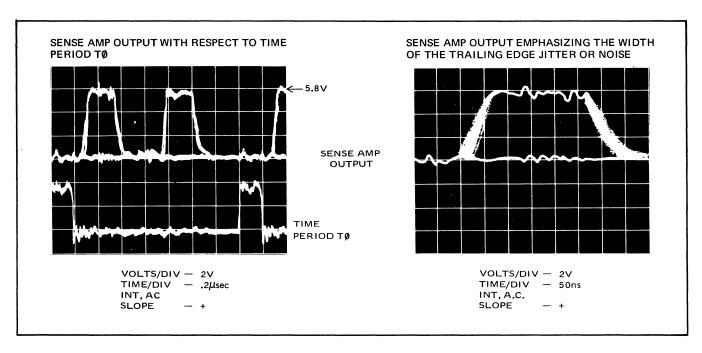

2-85. The purpose of this power fail detect circuit is to allow orderly turn on of power in the computer, and in case of power failure to allow proper turn off. A view of the block diagram indicated an AC detector which senses the voltage from the transformer winding. It utilizes the plus and minus 12 volt transformer windings although it is independent of the actual voltage buses. The circuit consists of an AC detector with a turn off delay, the threshold detector zener diode, the pulse shaping gates, and an effective AND gate with the 5 volt bus (Q24), a DC section with a turn-on delay network followed by a pulse shaping network.

Figure 2-9. Power Fail Block Diagram

#### 2-86. AC INPUT.

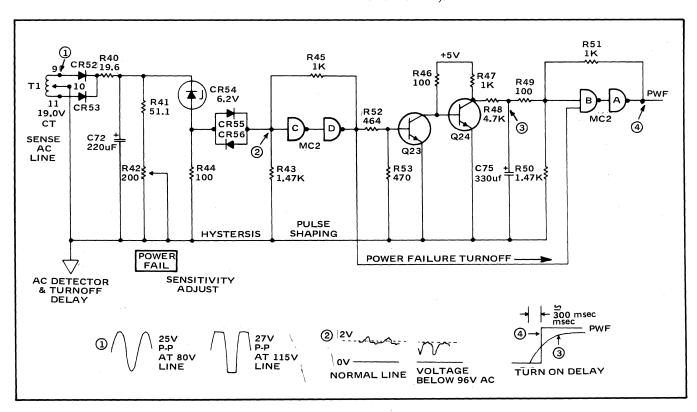

2-87. Referencing Figure 2-7, as the AC power comes up the full wave rectifiers CR52 and CR53 develop the voltage on C72. When the voltage has built up on this capacitor sufficiently high the zener diode CR54 begins to conduct at 6.2 volts and pulls up the input to the NAND gate MC2C. This voltage is pulled up through the forward biased diode CR55. Diodes CR55 and CR56 provide a hysteresis voltage level to the NAND gate inputs so that even if the voltage is somewhat near the turn on - turn off point for the NAND gates the output will not stutter. This provides an approximate 1.4 volt hysteresis range so that the operation will be stable even with minor variations in AC line.

#### 2-88. TURN ON OPERATION.

2-89. Now, let us follow the normal sequence as the AC power comes up. The voltage builds up on C72 until the voltage exceeds the level of CR54. This voltage build up on

C72 is based upon the RC time constant R40 and C72 during turn on. The voltage on the input gate MC2C rises until it switches the NAND gate MC2C. The output of the first section goes down so the output on the second section comes up. Resistors R45 and R43 provide a feedback network for speed up, and hold on purposes.

2-90. The true output from MC2D saturates Q23 and holds off Q24.

#### 2-91. TURN ON DELAY

2-92. The collector of Q24 goes high allowing C75 to charge up toward the +5V bus. The charging path is through R47 and R48. The time constant is about 300 milliseconds. When this voltage exceeds the threshold level on MC2B pin 5, MC2A and 2B switch providing a PWF high level output. The output of MC2D pin 8 is high and enables MC2B pin 4. R51 is a speed up resistor for pulse shaping.

#### 2-93. TURN OFF MODE.

2-94. When power failure reduces the AC line voltage the DC level on C72 discharges toward ground through R41 and R42. The time constant is about 20 milliseconds. Diode CR56 pulls the input to MC2C down until it falls below the turn on threshold. The output of MC2D drops disabling MC2B pin 4 which changes PWF to its negative true state.

2-95. Q24 turns on providing a discharge path for C75 to re-establish proper turn on time constant.

## 2-96. TROUBLESHOOTING THE POWER FAIL DETECT CIRCUIT.

2-97. A variable AC autotransformer on the computer AC line provides the best method for troubleshooting the circuit. The voltage on C72 will vary between approximately 7.7 to 8.3 volts DC (from 98 to 130 VAC line). The AC ripple will be 120 CPS with a 1.4V P.P. amplitude.

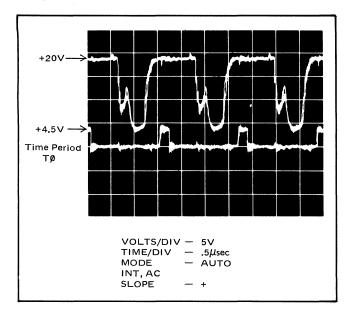

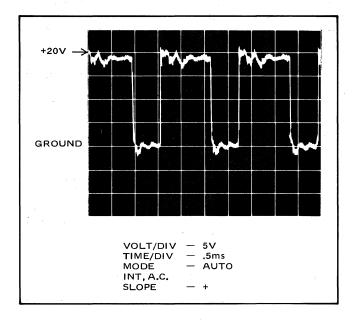

2-98. The input to MC2C will be 1.9 volts DC nominal. The AC waveshape at MC2C pin 12 will have a positive hump and a negative dip as CR55 and CR56 conduct. The relative size of the two will depend on the AC line voltage. When R42 is adjusted correctly the negative dip enlarges as the line voltage drops toward 98 VAC. At 98 to 100 VAC (96V minimum) the waveshape changes suddenly indicating that the states of MC2C and D have changed. (Refer to Figure 2-10). At this point the PWF output will go low initiating the power failure sequence.

#### 2-99. TURN ON DELAY.

2-100. The delay function during turn on can be checked in a rough way by observing the waveshape on C75 and the PWF output simultaneously. Set horizontal sweep to 100 msec/div, sync on AC line. Turn on the computer AC switch when the trace just begins a new sweep. The waveshapes can be seen after a couple of attempts. Leave switch off for a few seconds to insure all voltage buses have discharged fully before repeating. A delay of 300 to 500 milliseconds is typical (including reaction time in turning on the switch).

Figure 2-10. Power Fail

2-101. The PWF signal to the computer allows determining the status of the AC input voltage. This allows proper turn off for power failure. When Option 008 is installed the power failure option provides automatic restart when the power comes back on by interrupting to the software subroutine.

#### 2-102. MAINTENANCE PROCEDURES.

2-103. The HP 2114B Computer Power Supply requires a minimum of routine maintenance to ensure proper Computer operation. The routine maintenance, usually performed on a monthly basis, consists of cleaning, inspection and testing.

#### 2-104. CLEANING.

- 2-105. FILTERS. The Computer's two air filters, located on the Computer rear panel, should be cleaned as part of the routine maintenance procedure, or in extreme environments (high dust or oil content in the air), as needed. To clean filters perform the following:

- a. Remove the filters from the computer.

- b. Blow the filters clean with compressed air.

- c. If compressed air is not available, hot soapy water may be used as a substitute.

- d. Be sure the filters are completely dry and free of grease.

- e. Replace the filters.

- 2-106. DUSTING. Small particles may pass through filters and build up in the computer. Use a small vacuum or compressed air hose to remove excess dust. Pay particular attention to heat dissipating areas.

#### 2-107. INSPECTION.

2-108. Routine maintenance of the computer should include visual inspection of the mechanical parts of the computer. Dents, scratches, or poorly operating controls may indicate damage to the computer. Frayed, broken or burned insulation should be checked and corrected if necessary.

#### 2-109. SUPPLY VOLTAGES.

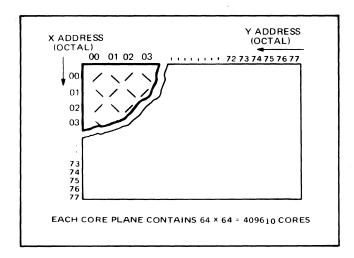

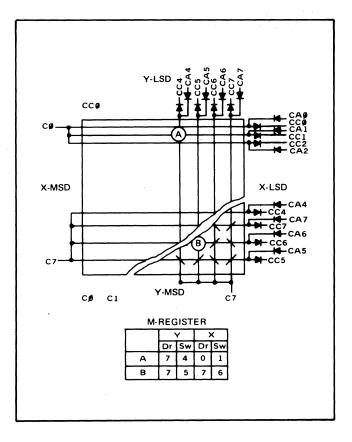

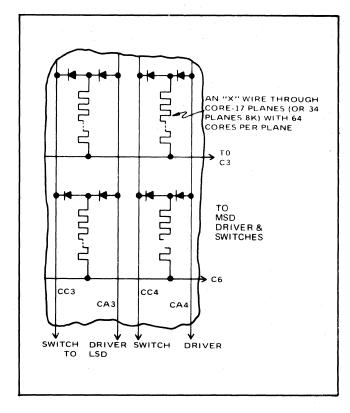

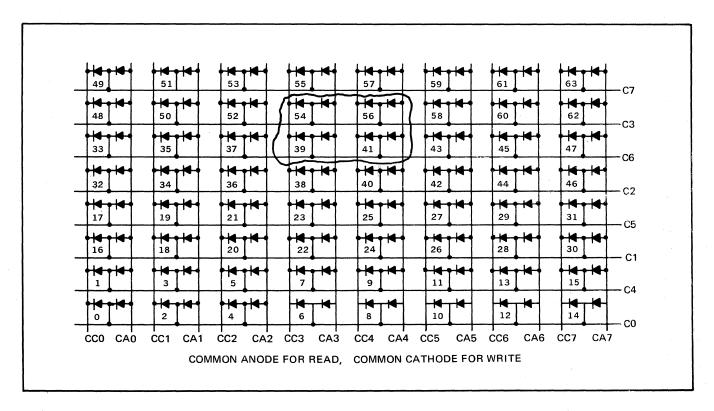

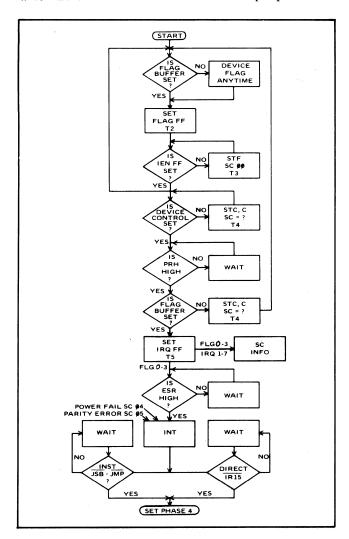

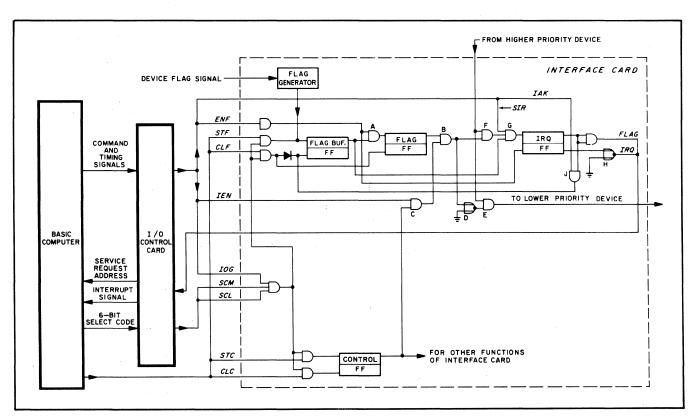

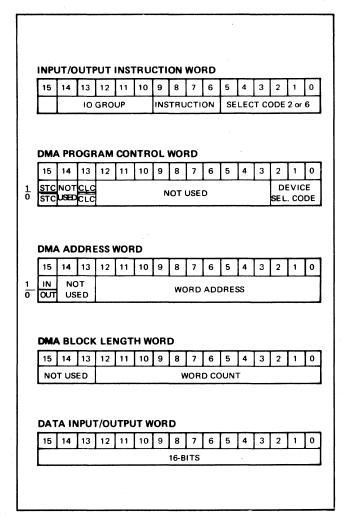

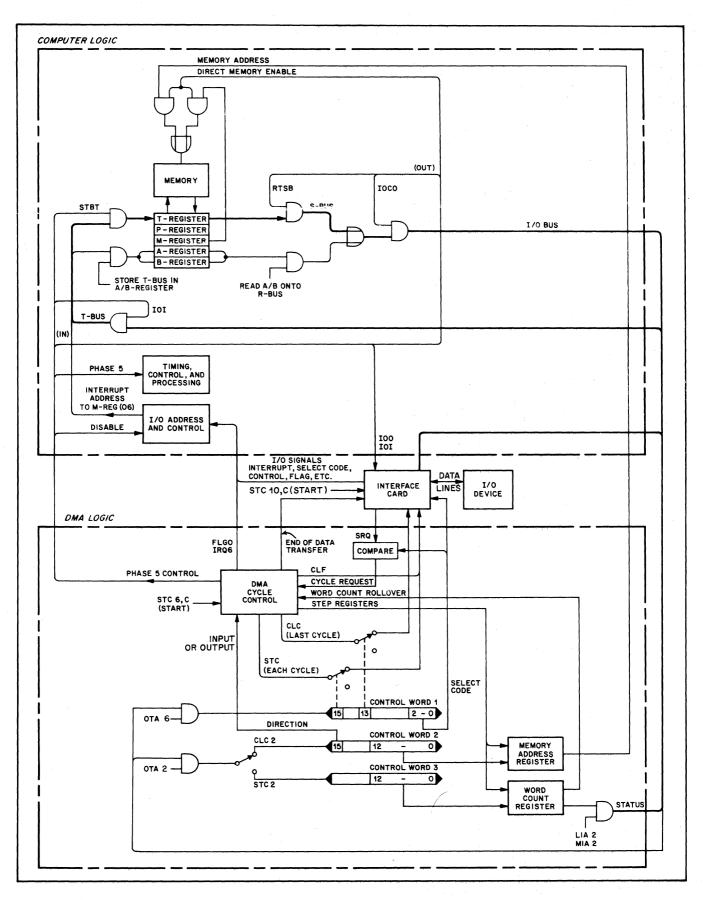

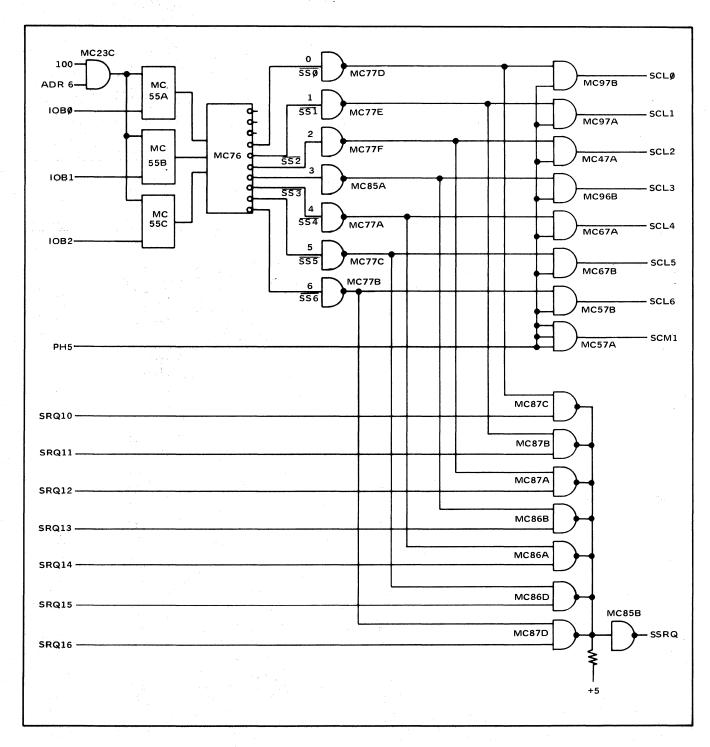

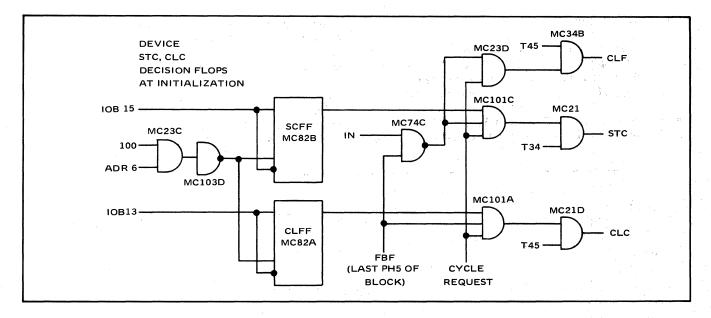

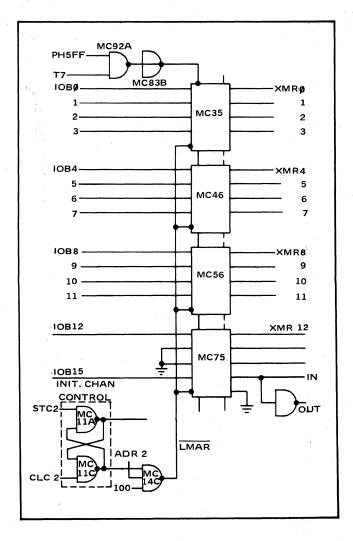

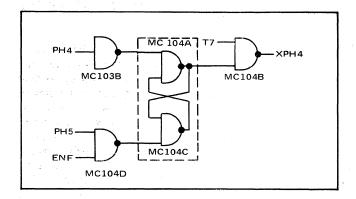

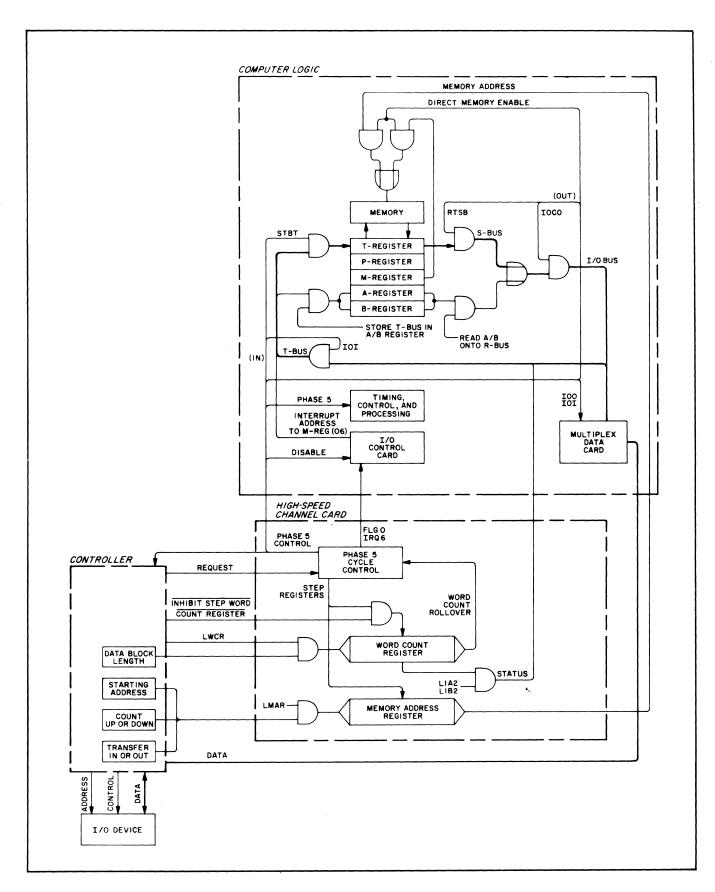

- 2-110. Check the computer's supply voltages at the test jacks on the computer's rear panel. The various supplies and the acceptable ranges for each are given in Table 2-1.