# 2100A computer

installation and maintenance manual

#### INSTALLATION AND MAINTENANCE MANUAL

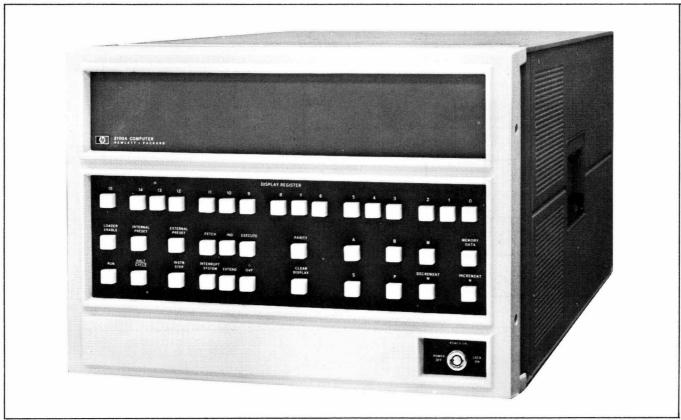

### MODEL 2100A COMPUTER

#### **SERIAL NUMBERS COVERED**

This manual applies directly to Model 2100A Computers having serial numbers prefixed 1136, 1140, 1145 through 1148, 1150, 1202, 1203, 1215, and 1217. Computers with higher prefix numbers will be covered in manual updating supplements.

#### **OPTIONS COVERED**

This manual covers options 001 and 015 as well as the basic computer.

#### **ACCESSORIES COVERED**

This manual covers the following accessory kits:

12884A, 12884A-001, and 12884A-002 Memory (4K Increments) Accessory Kits

12885 A, 12885 A-001, 12885 A-002, 12885 A-003, and 12885 A-004 Memory (8K Increments)

Accessory Kits

12895 A Direct Memory Access Accessory Kit

12899A Operator Panel Accessory Kit

12900A Maintenance Accessory Kit

12901 A Floating-Point Hardware Accessory Kit

Field installation of the above accessory kits is covered in separate manuals.

Printed: AUGUST 1972

### TABLE OF CONTENTS

| Secti | ion            | Page                                                               |

|-------|----------------|--------------------------------------------------------------------|

| I     | GENE           | RAL INFORMATION                                                    |

| •     | 1-1.           | Introduction                                                       |

|       | 1-3.           | Scope                                                              |

|       | 1-7.           | General Description                                                |

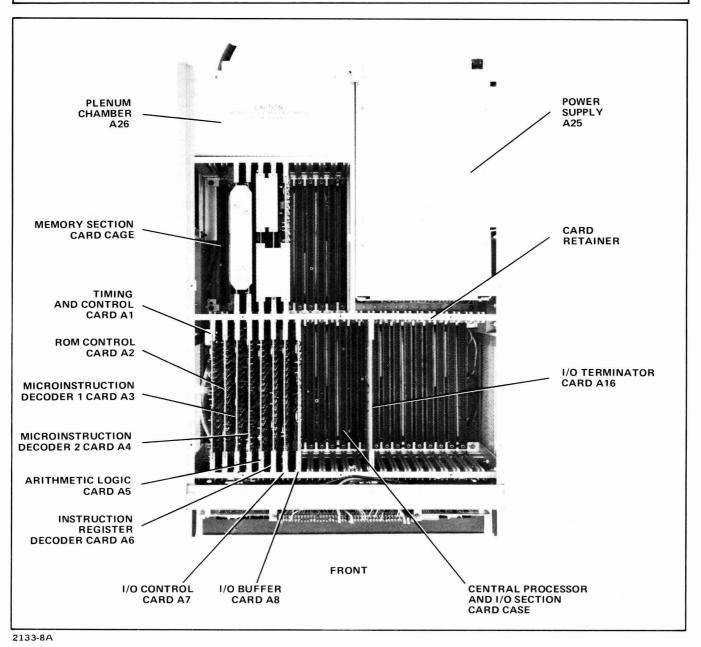

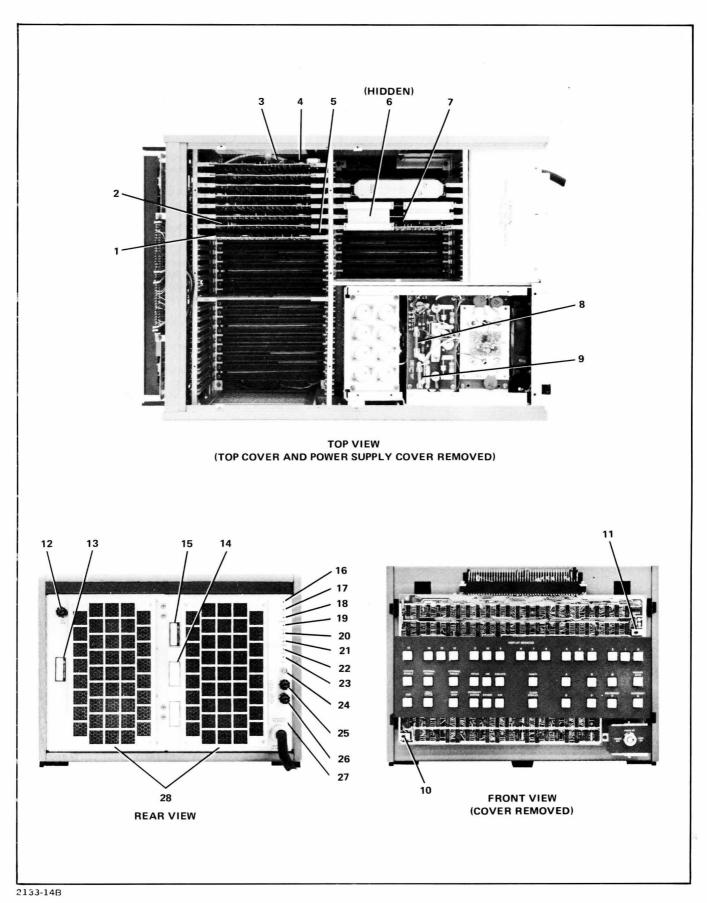

|       | 1-8.           | Computer Assemblies                                                |

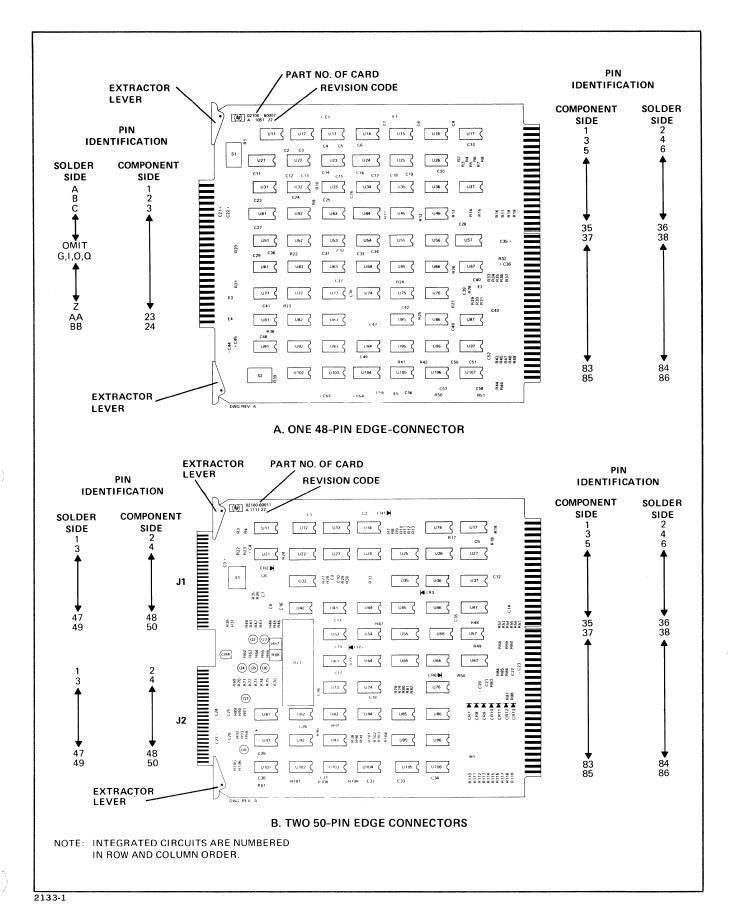

|       | 1-0.<br>1-10.  | Circuit Cards                                                      |

|       | 1-10.<br>1-14. | Operator Panel                                                     |

|       | 1-14.          | Power Supply Section                                               |

|       | 1-13.<br>1-17. | Backplane Assembly                                                 |

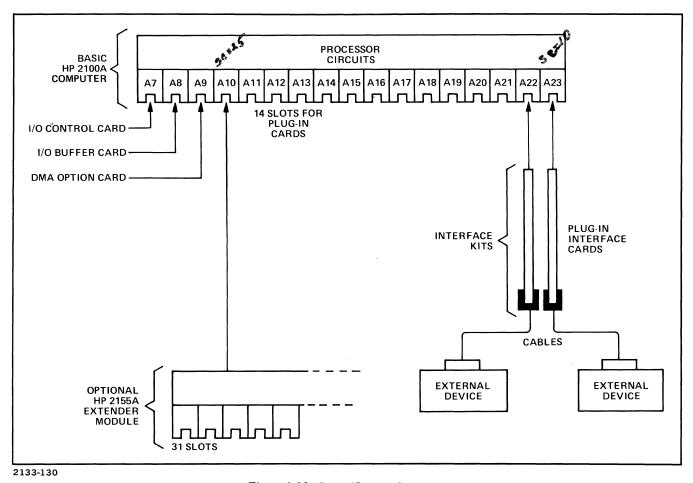

|       | 1-17.          | Processor Accessories                                              |

|       | 1-10.<br>1-19. | Memory Sizes                                                       |

|       | 1-19.<br>1-20. | 4K Memory Accessory Kits                                           |

|       | 1-20. 1-24.    | · · · · · · · · · · · · · · · · · · ·                              |

|       | 1-24.<br>1-30. | 8K Memory Accessory Kits                                           |

|       |                | Direct Memory Access Accessory Kit (12895A)                        |

|       | 1-35.          | Operator Panel Accessory Kit (12899 A)                             |

|       | 1-36.          | Processor Options                                                  |

|       | 1-37.          | Controller Panel (Option 001)                                      |

|       | 1-39.          | 230-Volt Operation (Option 015)                                    |

|       | 1-40.          | Input/Output Accessories                                           |

|       | 1-42.          | Panel Controls and Indicators                                      |

|       | 1-44.          | Specifications                                                     |

|       | 1-46.          | Identification                                                     |

|       | 1-47.          | Computer Model Number                                              |

|       | 1-49.          | Computer Serial Number                                             |

|       | 1-51.          | Option Numbers                                                     |

|       | 1-54.          | Assembly Part Numbers                                              |

|       | 1-57.          | Circuit-Card Revision Codes                                        |

|       | 1-59.          | Power Supply Date Code                                             |

|       | 1-61.          | Documentation of Equipment Improvements                            |

|       | 1-63.          | Maintenance Accessories and Service Items                          |

|       | 1-65.          | Maintenance Accessory Kit                                          |

|       | 1-67.          | Card Extenders                                                     |

|       | 1-68.          | Extension Cables                                                   |

|       | 1-69.          | Memory Current Sense Cable                                         |

|       | 1-70.          | Light Bulb Extractor                                               |

|       | 1-71.          | Rack Mounting Kit                                                  |

|       | 1-73.          | Manuals                                                            |

|       | 1-75.          | Maintenance Features                                               |

|       | 1-77.          | Recommended Maintenance Tools, Parts, Materials and Equipment 1-16 |

|       | 1-78.          | Tools                                                              |

|       | 1-83.          | Parts and Materials                                                |

|       | 1-86.          | Servicing Equipment                                                |

|       | 1-88.          | Field Office Assistance                                            |

|       | 1-00.          | Tien Office Assistance                                             |

| II    | INSTA          | LLATION                                                            |

|       | 2-1.           | Introduction                                                       |

|       | 2-4.           | Inspection of Shipment                                             |

|       | 2-11.          | Physical Inventory                                                 |

|       | 2-12.          | Manuals                                                            |

|       | 2-14.          | Equipment                                                          |

|       | 2-18.          | Program Tapes                                                      |

|       |                |                                                                    |

| Secti | ion            |                                     | Page  |

|-------|----------------|-------------------------------------|-------|

|       | 2-20.          | Installation Procedure              | . 2-1 |

|       | 2-21.          | Manual Updating                     | . 2-1 |

|       | 2-23.          | Environmental Requirements          | . 2-2 |

|       | 2-26.          | Power Requirements                  | . 2-2 |

|       | 2-29.          | AC Power Outlet and External Ground | . 2-2 |

|       | 2-36.          | AC Power Cable                      | . 2-3 |

|       | 2-39.          | Power Supply Checkout               | . 2-7 |

|       | 2-41.          | Mounting                            | . 2-7 |

|       | 2-45.          | Performance Check                   |       |

|       | 2-47.          | Claims                              |       |

|       | 2-49.          | Repackaging for Shipment            |       |

|       | 2-50.          | Shipment Using Original Packaging   |       |

|       | 2-52.          | Shipment Using New Packaging        | . 2-7 |

|       |                |                                     |       |

| III   |                | RY OF OPERATION                     |       |

|       | 3-1.           | Introduction                        |       |

|       | 3-3.           | Reference Information               |       |

|       | 3-5.           | Binary Signal Levels                | . 3-1 |

|       | 3-7.           | Logic Circuits                      | . 3-1 |

|       | 3-10.          | Signal Names                        |       |

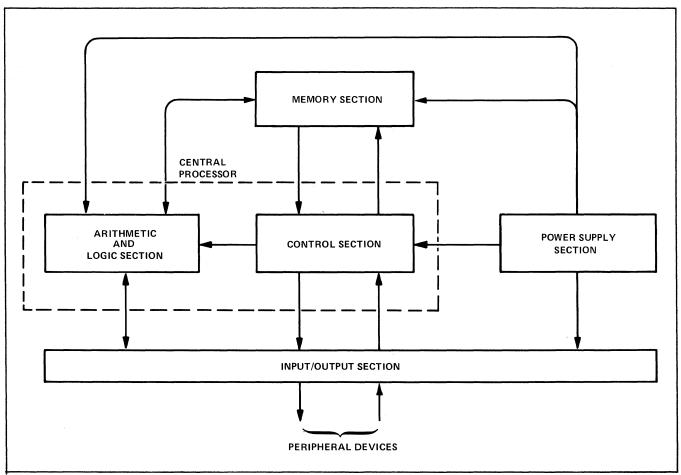

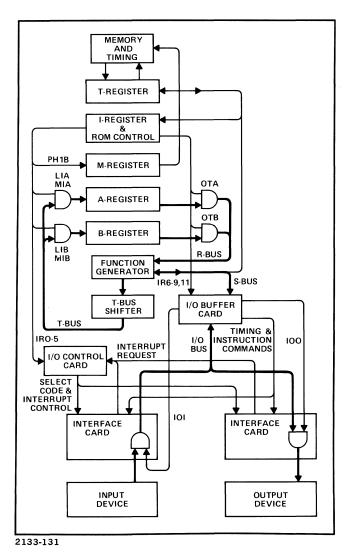

|       | 3-19.          | Computer Functional Sections        |       |

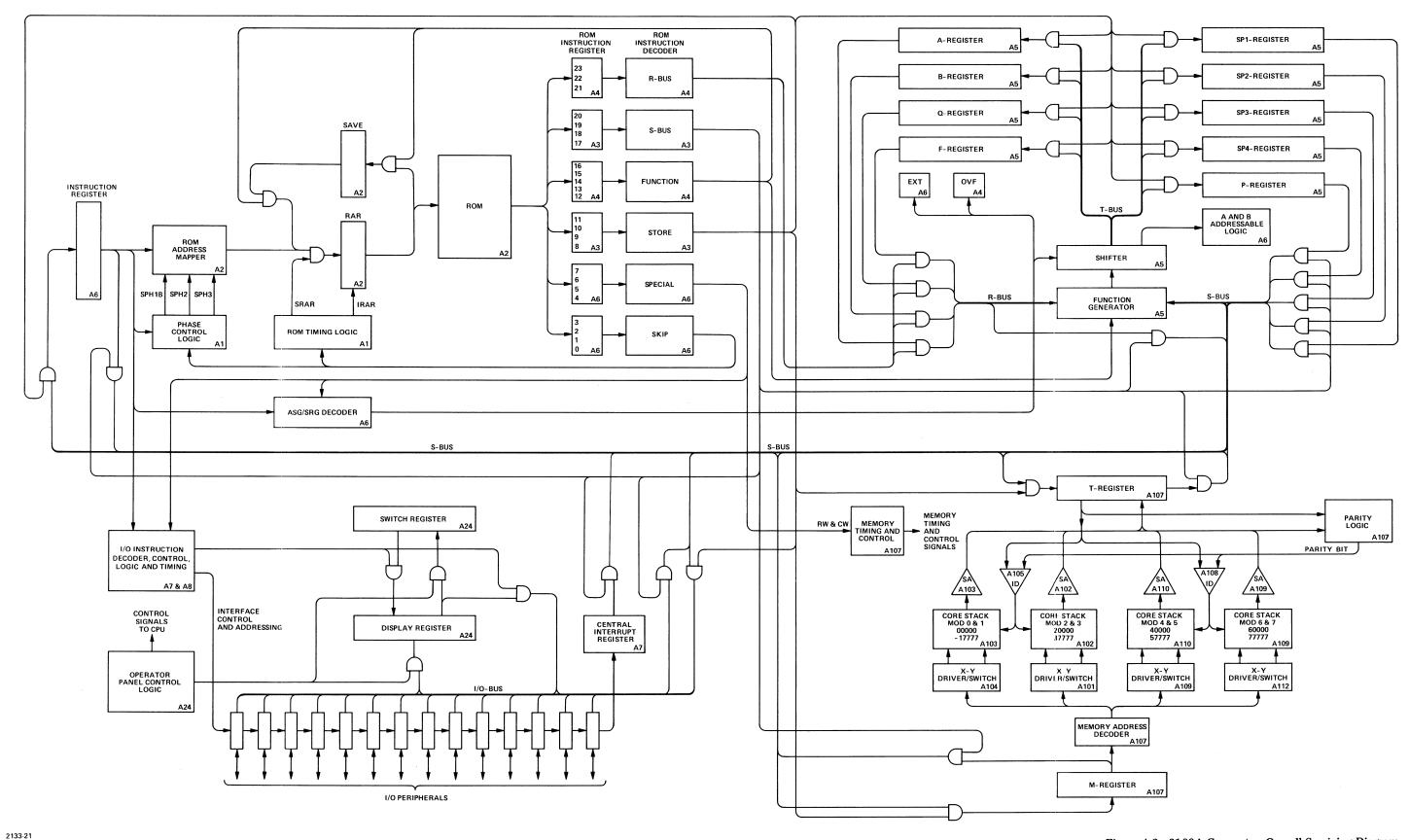

|       | 3-22.          | Overall Block Diagram Discussion    |       |

|       | 3-24.          | Bus System                          |       |

|       | 3-26.          | Memory Section                      |       |

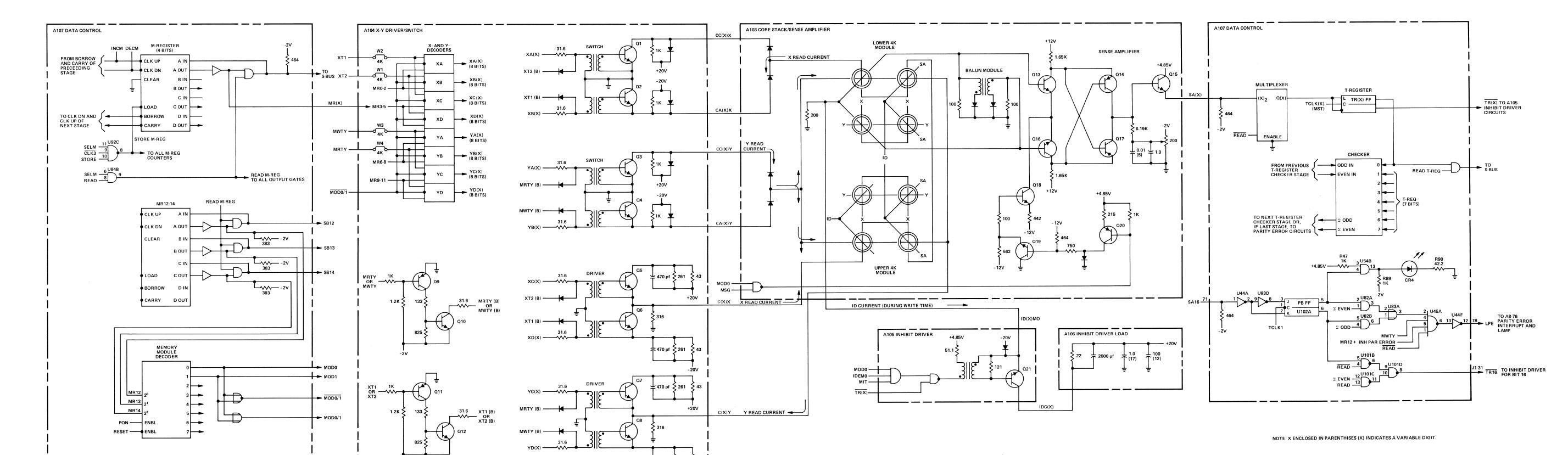

|       | 3-28.          | Core Stack                          |       |

|       | 3-30.          | Memory Timing and Control           |       |

|       | 3-31.          | Memory Section Registers            |       |

|       | 3-32.          | Memory Address Decoder              |       |

|       | 3-33.          | X/Y Driver/Switches                 |       |

|       | 3-34.          | Sense Amplifiers                    |       |

|       | 3-35.          | Inhibit Drivers                     |       |

|       | 3-36.          | Parity Logic                        |       |

|       | 3-37.          | Arithmetic and Logic Section        |       |

|       | 3-39.          | Registers                           |       |

|       | 3-40.          | R-Bus Registers                     |       |

|       | 3-41.          | S-Bus Registers                     |       |

|       | 3-42.          | Extend Register                     |       |

|       | 3-43.          | Overflow Register                   |       |

|       | 3-44.          | Function Generator                  |       |

|       | 3-45.          | Shifter                             |       |

|       | 3-46.          | A- and B-Addressable Logic FFs      |       |

|       | 3-47.<br>3-49. | Input/Output Section                |       |

|       |                | I/O Section Registers               |       |

|       | 3-50. $3-51.$  | Central Interrupt Register          |       |

|       | 3-51.<br>3-52. | S-Register                          |       |

|       | 3-52.<br>3-53. | Display Register                    | . J-1 |

|       | ა-აა.<br>3-55. |                                     |       |

|       |                |                                     |       |

|       | 3-58.<br>3-62. | Control Section                     |       |

|       |                | Instruction Register                |       |

|       | 3-63.          | Phase Control Logic                 |       |

|       | 3-64.          | ROM Address Mapper                  |       |

|       | 3-65.<br>3-66. | ROM Address Register                |       |

|       | 11-111.        | Dave register                       | . 0-0 |

| Section          |                                          | Page   |

|------------------|------------------------------------------|--------|

| 3-67.            | ROM                                      | 3-8    |

| 3-68.            | ROM Instruction Register                 |        |

| 3-69.            | ROM Instruction Decoder                  |        |

| 3-70.            | &RG/ASG Decoder                          |        |

| 3-70.<br>3-71.   | Computer Functional Operation            |        |

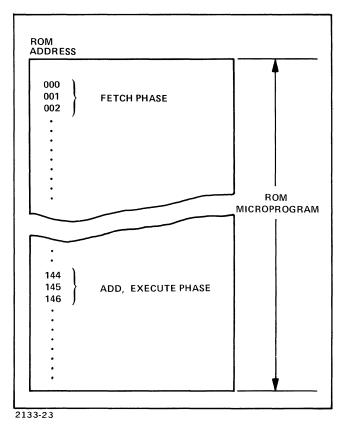

| 3-71.<br>3-73.   | ROM Microprogram Control                 |        |

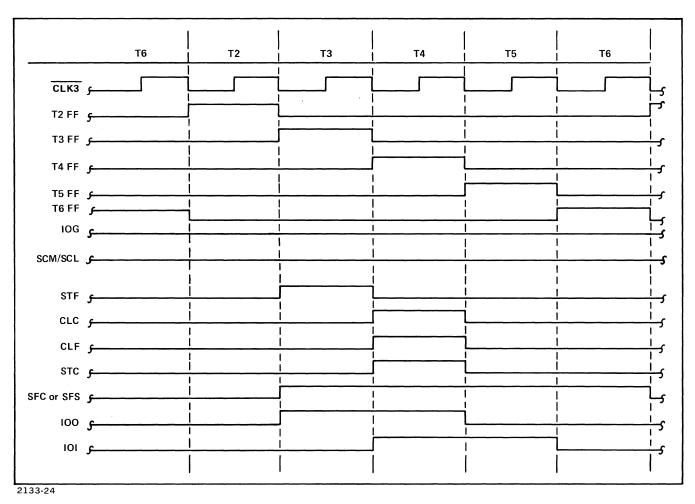

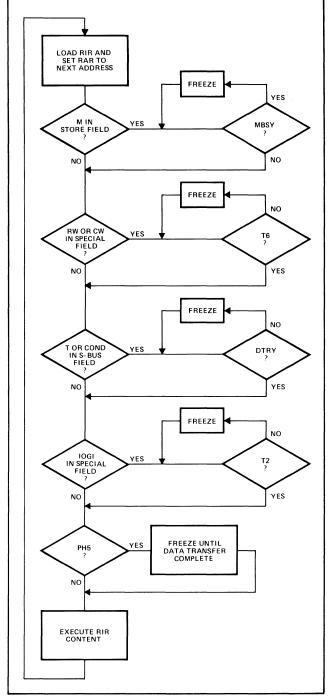

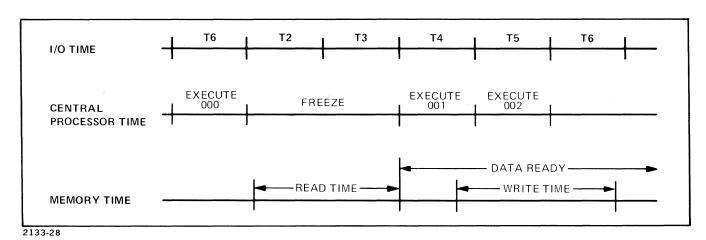

| 3-73.<br>3-85.   | Computer Timing                          |        |

| 3-88.            | I/O Section Timing                       |        |

| 3-90.            |                                          |        |

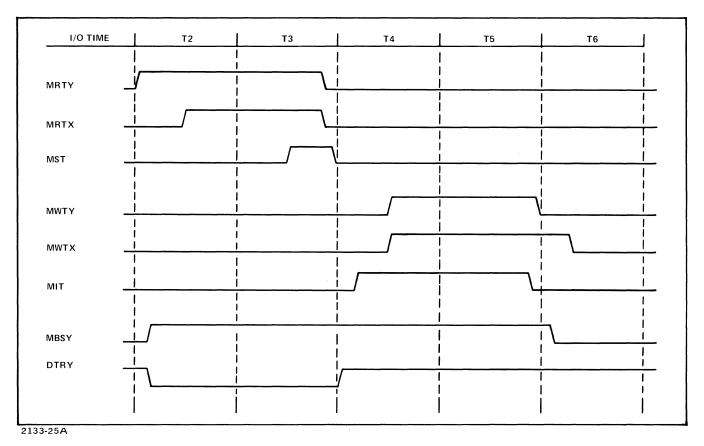

| 3-90.<br>3-91.   | Memory Section Timing                    |        |

| 3-91.<br>3-92.   | Memory Read Time                         |        |

| 3-92.<br>3-94.   |                                          |        |

|                  | Central Processor Timing                 |        |

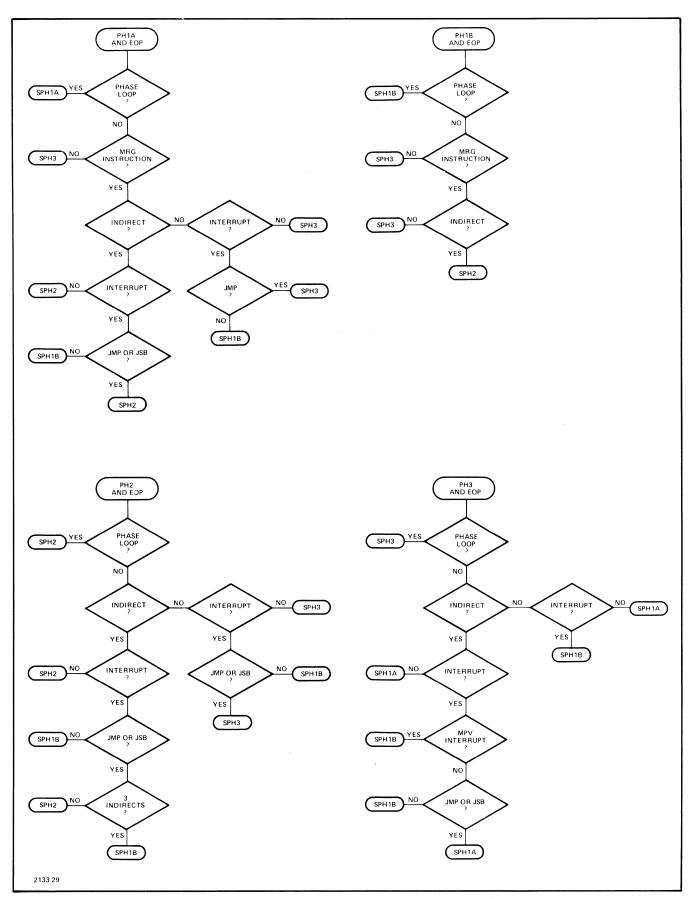

| 3-106.           | Phases of Operation                      |        |

| 3-108.           | Fetch Phase                              |        |

| 3-109.           | Indirect Phase                           |        |

| 3-110.           | Execute Phase                            |        |

| 3-111.           | Phase 5                                  |        |

| 3-112.           | Set Phase Logic                          |        |

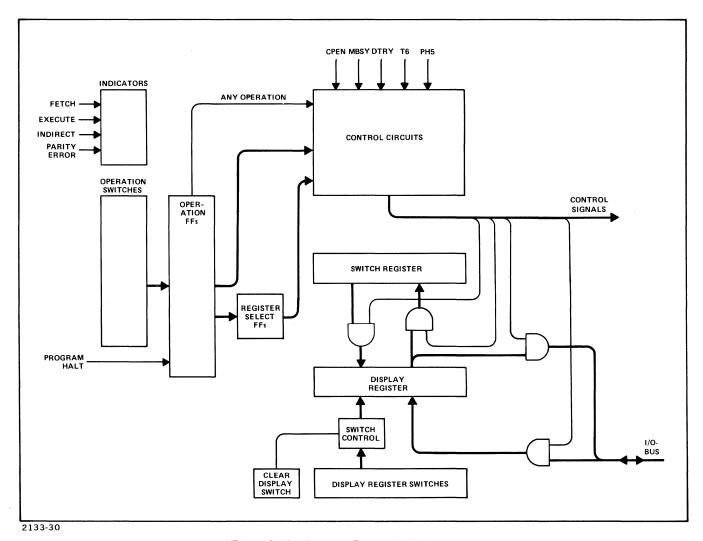

| 3-114.           | Operator Panel                           |        |

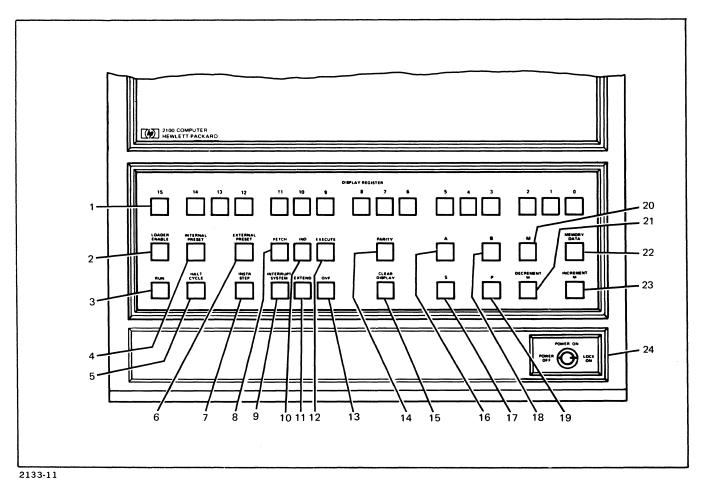

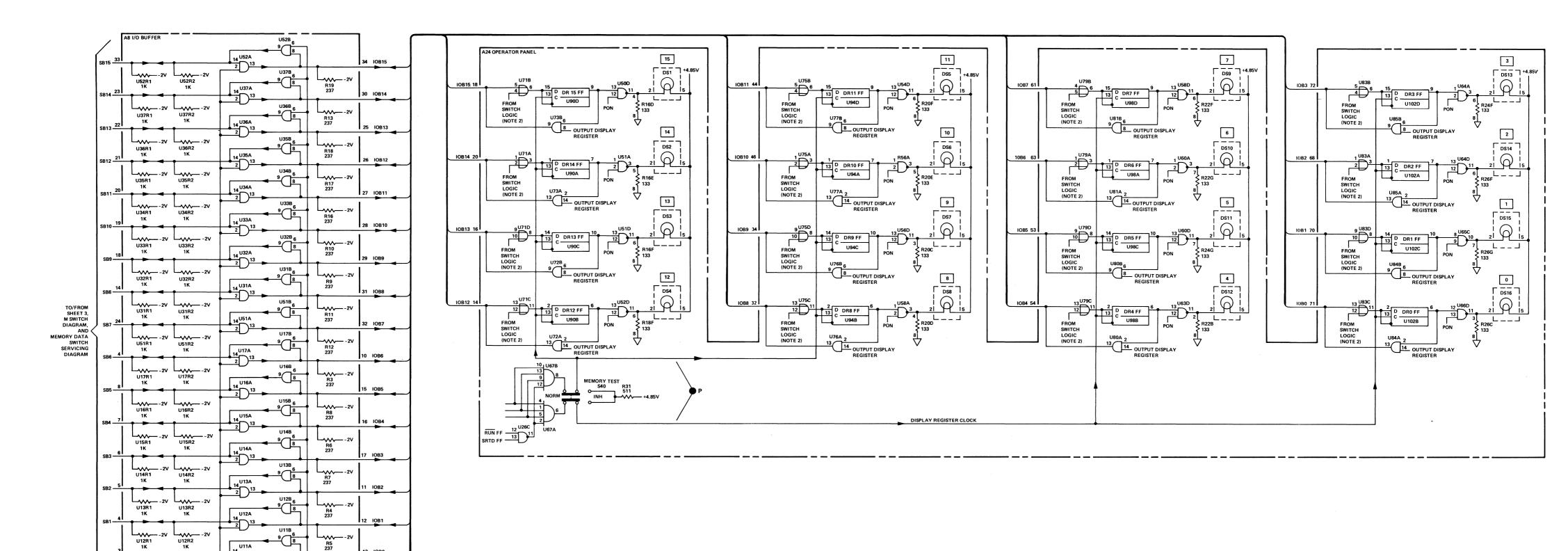

| 3-117.           | Panel Switches and Indicators            | 3-16   |

| 3-119.           | Computer Power Switch                    | 3-16   |

| 3-120.           | Display Register Switches                | 3-16   |

| 3-122.           | Operation Switches                       | 3-16   |

| 3-125.           | Special Maintenance Switches             | 3-17   |

| 3-128.           | Indicators                               |        |

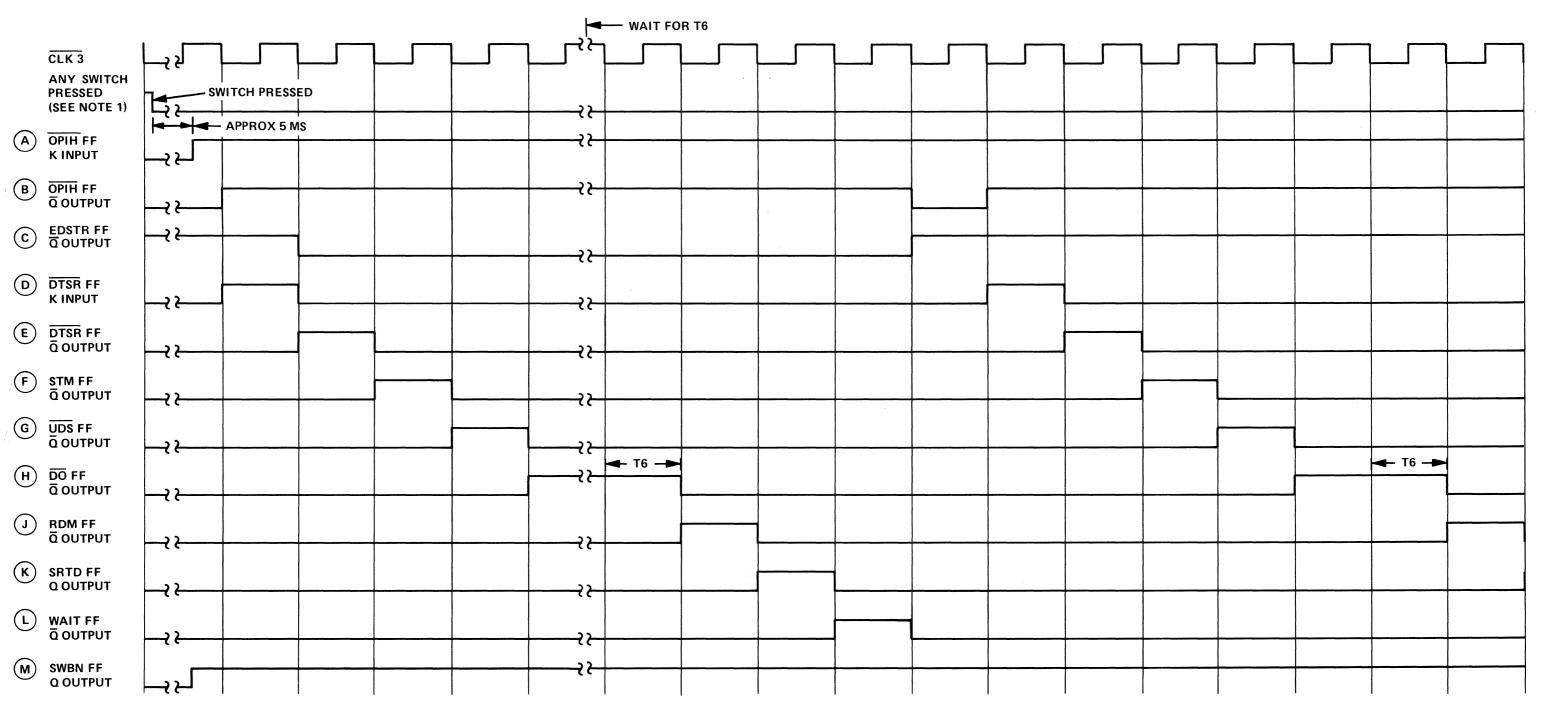

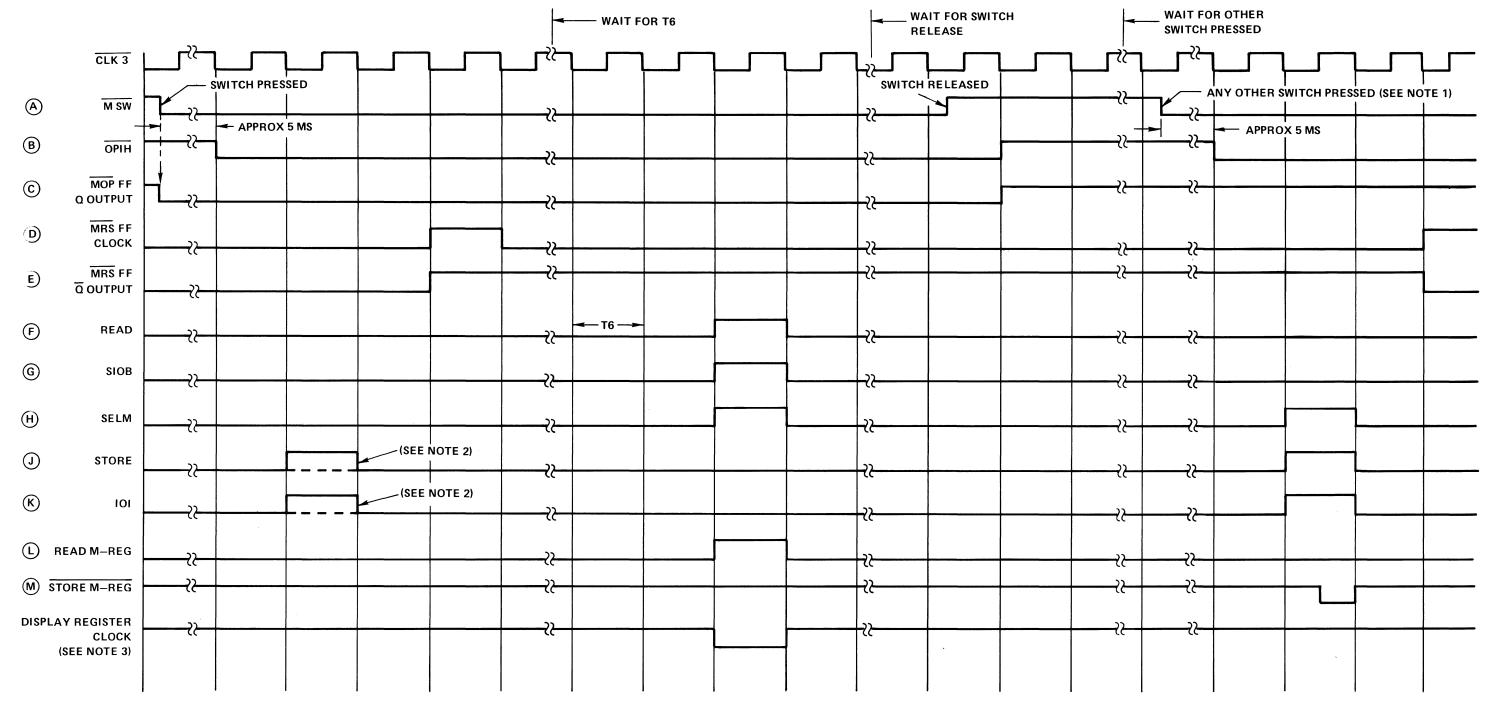

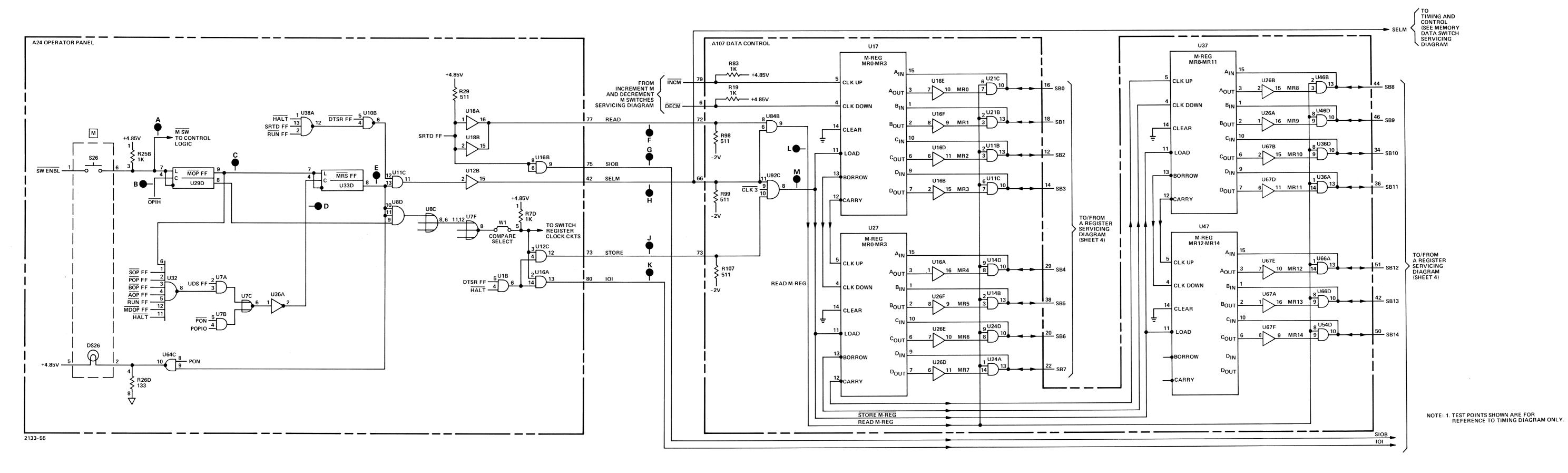

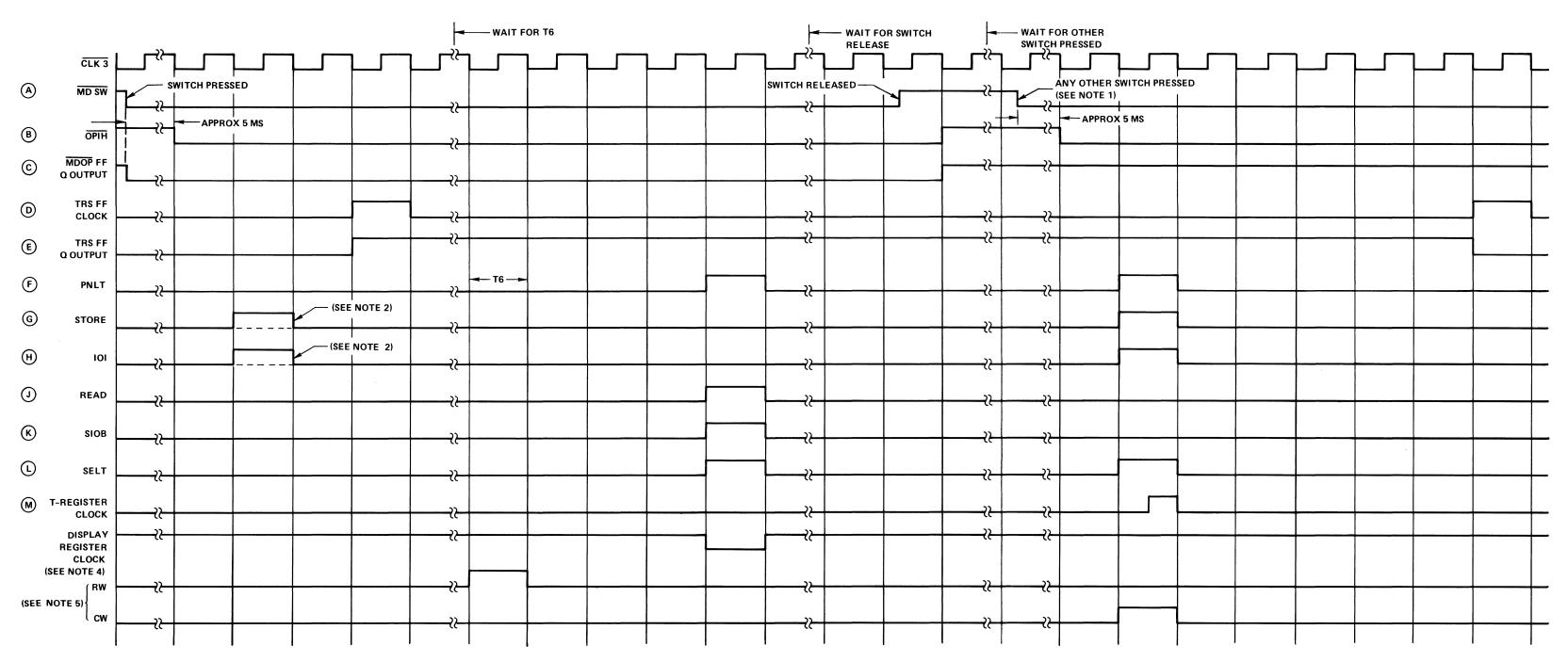

| 3-129.           | Operator Panel Functional Operation      | 3-17   |

| 3-130.           | General                                  |        |

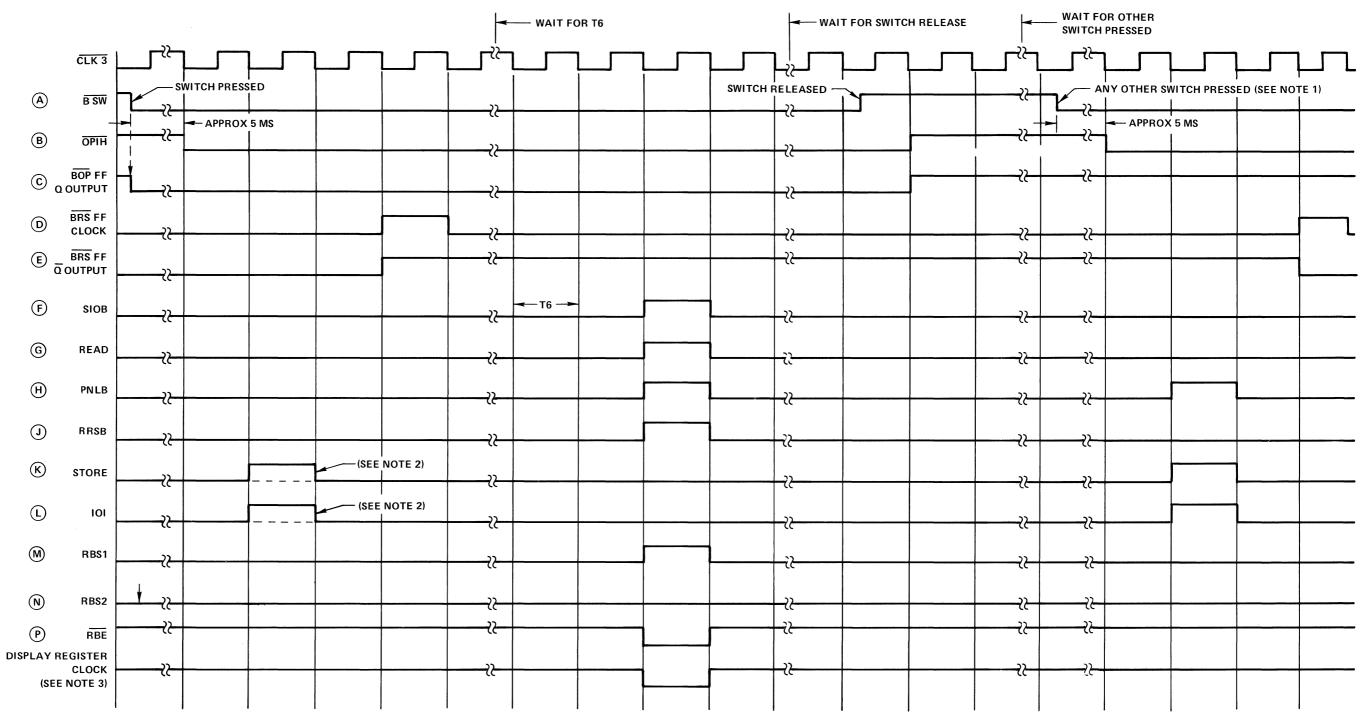

| 3-132.           | Operator Panel Cycle                     |        |

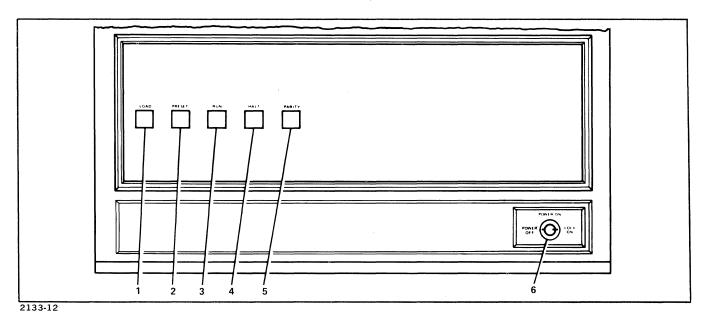

| 3-133.           | Controller Panel                         |        |

| 3-135.           | Controller Panel Jumpers                 |        |

| 3-137.           | Controller Panel Switches and Indicators |        |

| 3-140.           | Load Switch and Indicator                |        |

| 3-140.<br>3-141. | Preset Switch and Indicator              |        |

| 3-141.<br>3-142. | Halt Switch and Indicator                |        |

|                  |                                          |        |

| 3-143.<br>3-144. | Run Switch and Indicator                 |        |

|                  |                                          |        |

| 3-145.           | Special Computer Functions               |        |

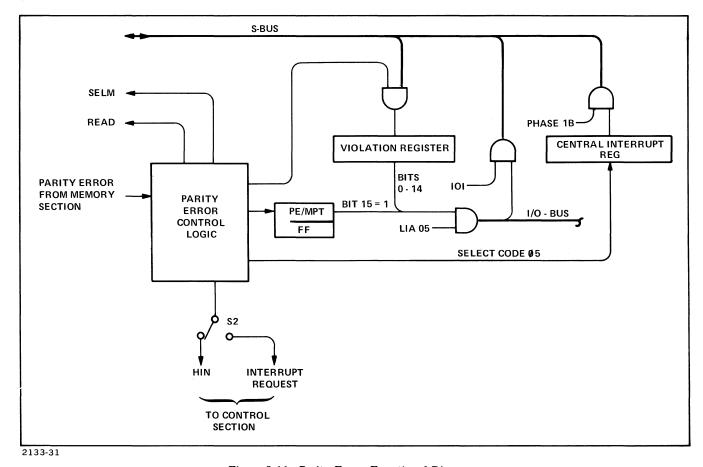

| 3-148.           | Parity Error                             |        |

| 3-149.           | General                                  |        |

| 3-151.           | Parity Error Halt                        |        |

| 3-152.           | Parity Error Interrupt                   |        |

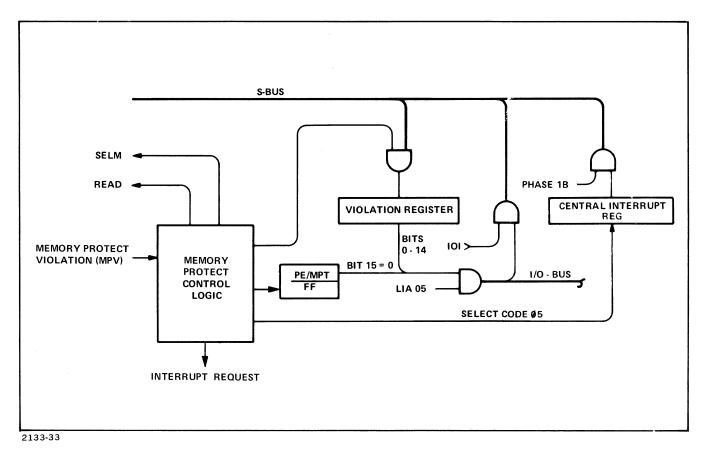

| 3-154.           | Memory Protect                           |        |

| 3-155.           | General                                  |        |

| 3-157.           | Detecting a Memory Protect Violation     |        |

| 3-159.           | Memory Protect Interrupt                 |        |

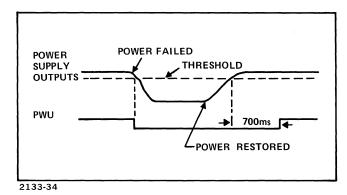

| 3-161.           | Power-Fail                               |        |

| 3-162.           | General                                  |        |

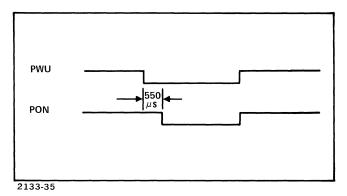

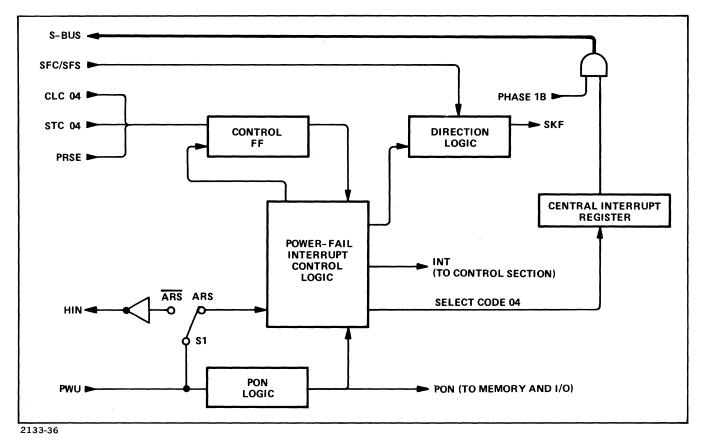

| 3-167.           | PWU Signal                               |        |

| 3-168.           | PON Signal                               |        |

| 3-169.           | Interrupt Operation                      |        |

| 3-172.           | Direct Memory Access                     |        |

| 3-173.           | General                                  |        |

| 3-175.           | DMA Initialization                       |        |

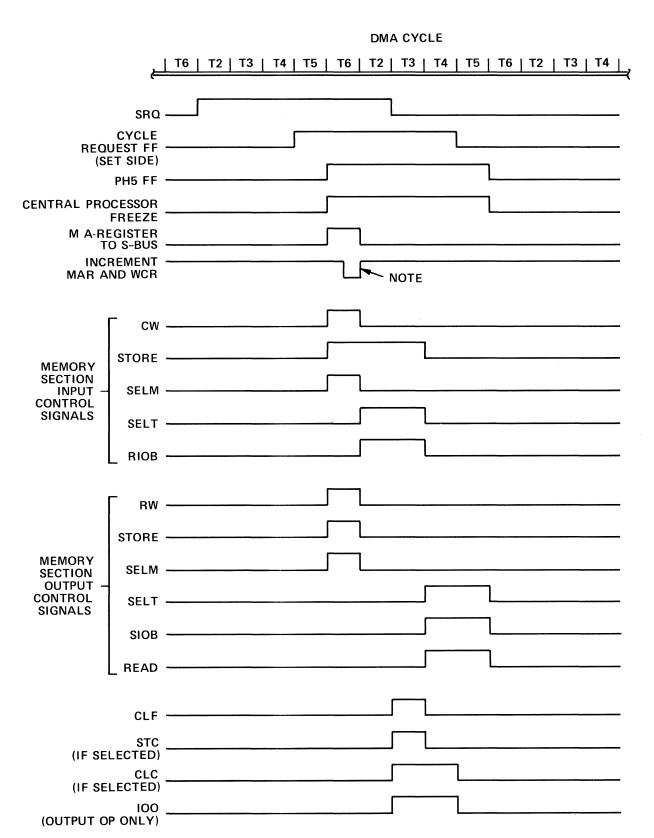

| 3-180.           | DMA Cycle                                |        |

| 3-183.           | Input Operation                          |        |

| 3-185            | Output Operation                         | . 3-27 |

| Section             | Pa                                       | age |

|---------------------|------------------------------------------|-----|

| 3-186.              | End Data Transfer                        |     |

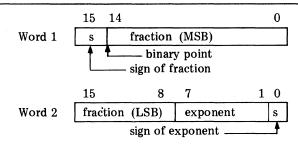

| 3-188.              | Floating Point                           | 27  |

| 3-189.              | General                                  | 27  |

| 3-190.              | Floating-Point Operation                 | 27  |

| 3-192.              | Floating-Point Instructions              | 28  |

| 3-194.              | Detailed Theory Introduction             |     |

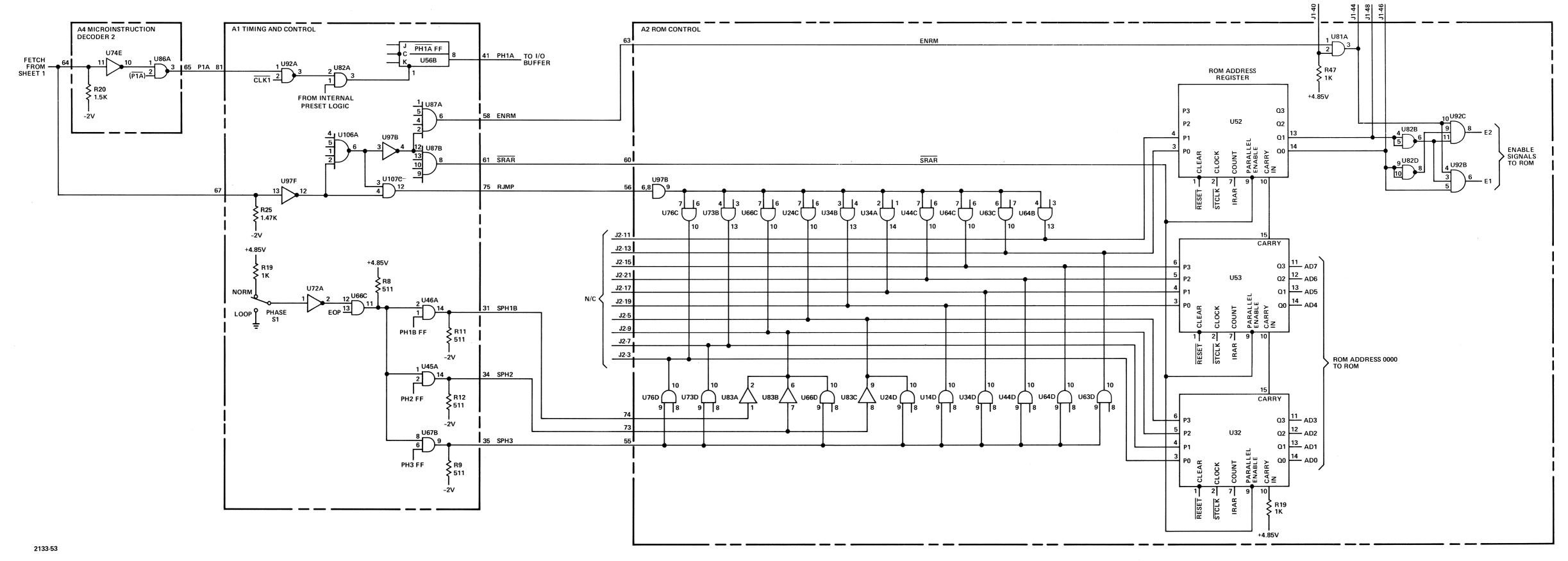

| 3-196. t            | Control Section Detailed Theory          |     |

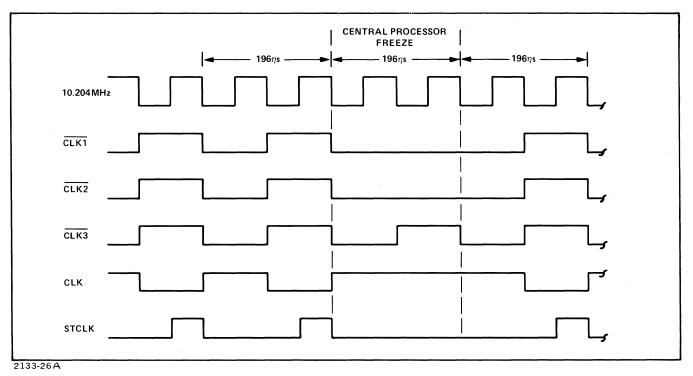

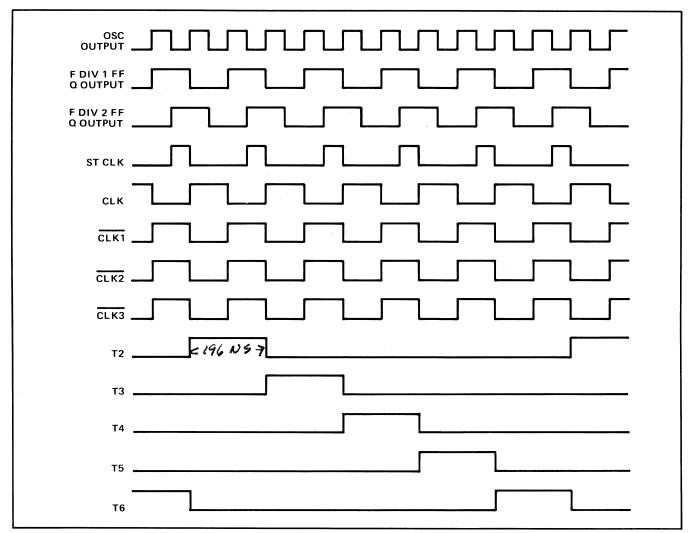

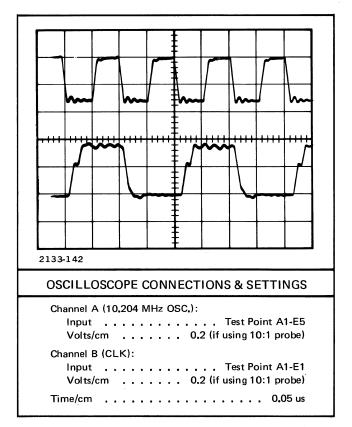

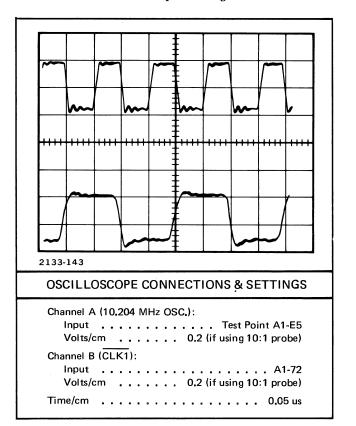

| 3-197.              | Clock Generator Circuits                 |     |

| 3-199.              | Oscillator                               |     |

| 3-200.              | Frequency Divider                        |     |

| 3-201.              | Clock Gating Circuits                    |     |

| 3-204.              | Parity Error Freeze                      |     |

| 3-20 <del>4</del> . | I/O Freeze                               |     |

| 3-206.              | Freeze Logic                             |     |

| 3-200.<br>3-211.    | Memory Protect or Parity Error Interrupt |     |

| 3-211.<br>3-212.    | DMA Cycle                                |     |

| 3-212.<br>3-213.    |                                          |     |

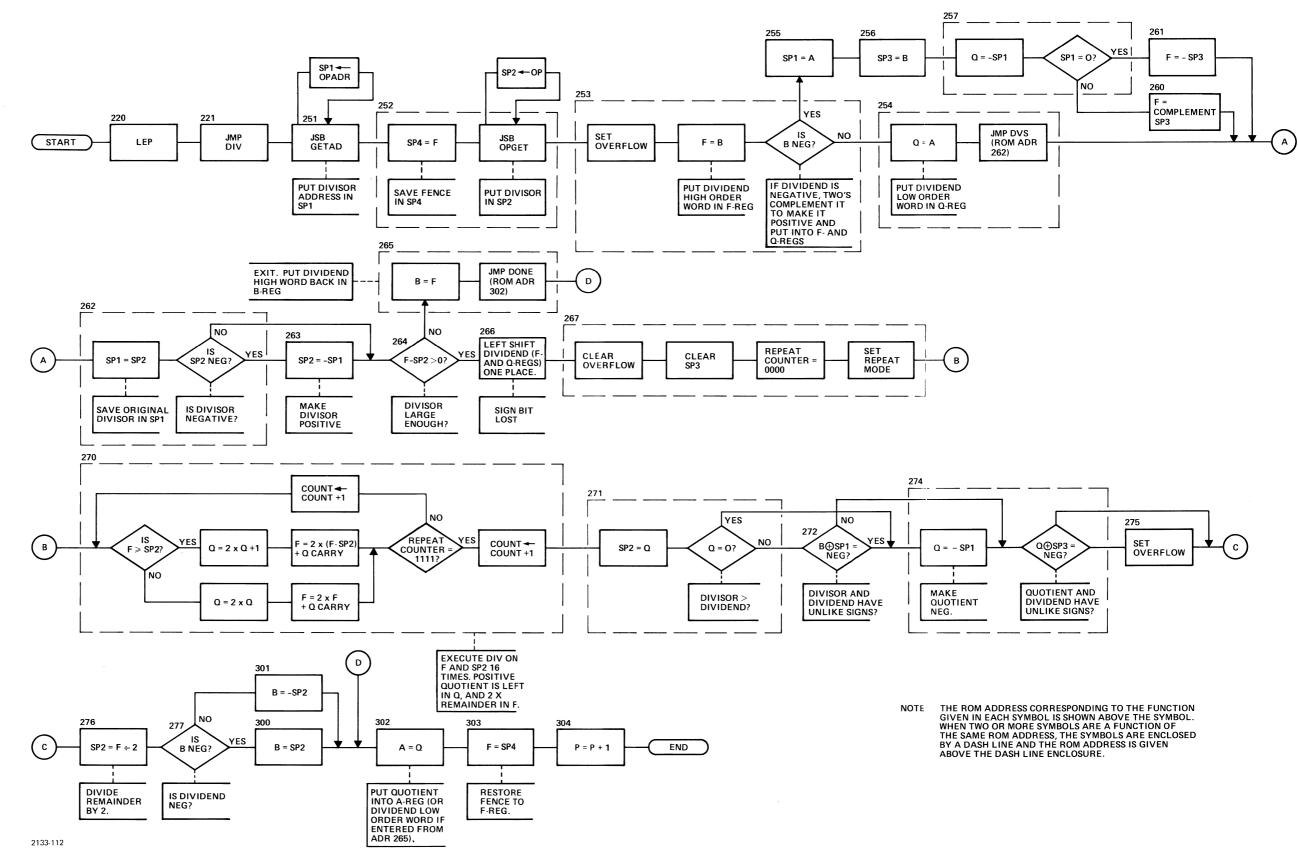

|                     | Divide Operation                         |     |

| 3-215.              | Memory Read/Write and Clear/Write        |     |

| 3-217.              | Read T-Register                          |     |

| 3-219.              | Store M-Register                         |     |

| 3-220.              | Step Generator Logic                     |     |

| 3-222.              | LRun Logic                               | -32 |

| 3-224.              | Run Mode                                 | -32 |

| 3-226.              | Single Instruction Mode                  | -32 |

| 3-230.              | Single Cycle Mode                        | -32 |

| 3-233.              | Halt Mode                                | -32 |

| 3-235.              | Automatic Restart                        | -33 |

| 3-237.              | Phase Control Logic                      |     |

| 3-240.              | Phase 1A                                 |     |

| 3-241.              | Phase 1B                                 |     |

| 3-245.              | Phase 2                                  |     |

| 3-249.              | Phase 3                                  |     |

| 3-253.              | Forcing Phase 1A                         |     |

| 3-254.              | Internal Preset                          |     |

| 3-254.<br>3-255.    | P-Switch                                 |     |

| 3-255.<br>3-256.    | Decoding P1A                             |     |

|                     |                                          |     |

| 3-257.              | Power On                                 |     |

| 3-258.              | Forcing Phase 1B                         |     |

| 3-259.              | Phase 1 Skip                             |     |

| 3-261.              |                                          | -35 |

| 3-263.              |                                          | -35 |

| 3-267.              | ROM Mapper                               |     |

| 3-269.              | Set Phase Signals                        |     |

| 3-270.              | I-Register Bit Decoding                  |     |

| 3-271.              | ROM Module Addressing                    |     |

| 3-273.              | ROM Jumps                                |     |

| 3-275.              | ROM Address Register                     |     |

| 3-277.              | Loading the RAR                          |     |

| 3-278.              | Incrementing the RAR                     |     |

| 3-279.              | Clearing the RAR                         |     |

| 3-280.              |                                          | -37 |

| 3-282.              | NER FF                                   |     |

| 3-284.              | LEP FF                                   | -37 |

| 3-285.              | Save Register                            |     |

| 3-292.              | ROM                                      |     |

| 3-298.              | The ROM Microprogram                     |     |

| Section          |                                     | Page |

|------------------|-------------------------------------|------|

| 3-300.           | Microcode                           | 3-38 |

| 3-301.           | Microinstruction                    | 3-38 |

| 3-302.           | Microroutine                        | 3-38 |

| 3-303.           | Subroutine                          | 3-39 |

| 3-304.           | Entry Point Labels                  |      |

| 3-305.           | Legal Entry Points                  |      |

| 3-306.           | End-of-Phase                        |      |

| 3-307.           | ROM Skip Mode                       |      |

| 3-309.           | ROM Jump Mode                       |      |

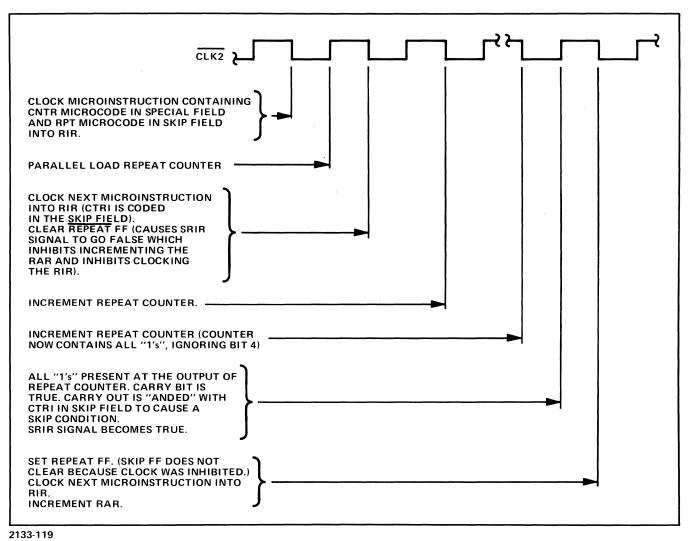

| 3-303.<br>3-311. | ROM Repeat Mode                     |      |

| 3-311.<br>3-312. | Synchronizing with I/O Time Periods |      |

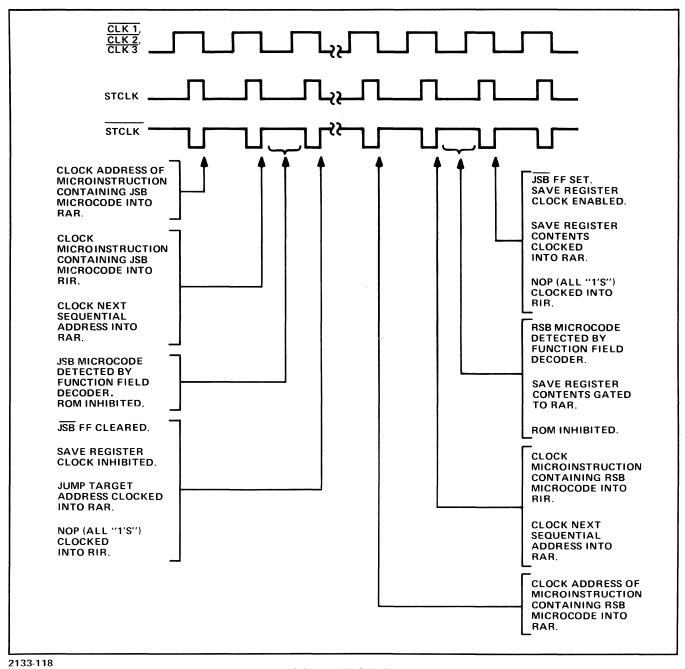

| 3-312.<br>3-314. | ROM Control Logic                   |      |

| 3-314.<br>3-316. | ROM Jump Control                    |      |

|                  |                                     |      |

| 3-320.           | Return from ROM Subroutines         |      |

| 3-321.           | End-of-Phase                        |      |

| 3-322.           | Halt Mode                           |      |

| 3-323.           | Automatic Restart                   |      |

| 3-324.           | ROM Instruction Register            |      |

| 3-326.           | Inputs                              |      |

| 3-327.           | Clocking                            |      |

| 3-330.           | Output Desitnations                 |      |

| 3-331.           | Instruction Register                | 3-41 |

| 3-333.           | Clocking                            |      |

| 3-334.           | S-Bus Data                          |      |

| 3-335.           | Function of I-Register Bits         | 3-41 |

| 3-336.           | ROM Microinstruction Decoder        |      |

| 3-338.           | R-Bus Field Decoder                 |      |

| 3-339.           | A (000)                             |      |

| 3-340.           | AAB (101)                           | 3-43 |

| 3-341.           | B (001)                             |      |

| 3-342.           | CAB (100)                           | 3-43 |

| 3-343.           | CQ (110)                            | 3-43 |

| 3-344.           | F (011)                             | 3-43 |

| 3-345.           | NOP (111)                           | 3-44 |

| 3-346.           | Q (010)                             | 3-44 |

| 3-347.           | S-Bus Field Decoder                 | 3-44 |

| 3-348.           | ADR (0110)                          | 3-44 |

| 3-349.           | CIR (0000)                          |      |

| 3-350.           | CL (1101)                           |      |

| 3-351.           | CNTR (0101)                         | 3-45 |

| 3-352.           | COND (0111)                         |      |

| 3-353.           | CR (1100)                           |      |

| 3-354.           | IOI (0001)                          |      |

| 3-355.           | M (0011)                            |      |

| 3-356.           | NOP (1111)                          |      |

| 3-357.           | P (1110)                            |      |

| 3-358.           | RRS (0100)                          |      |

| 3-359.           | S1 (1011)                           |      |

| 3-360.           | S2 (1010)                           |      |

| 3-361.           | S3 (1001)                           |      |

| 3-362.           | S4 (1000)                           |      |

| 3-363.           | T (0010)                            |      |

| 3-364.           | Function Field Decoder              |      |

| 3-364.<br>3-368. | ADD (01011)                         |      |

| 3-369.           | ADDO (01011)                        |      |

| 3-303.<br>3-370. | AND (01100)                         |      |

2100A Contents

| Section   |                       | Page   |

|-----------|-----------------------|--------|

| 3-371.    | ARS (11000)           | . 3-46 |

| 3-374.    | CFLG (11011)          | . 3-47 |

| 3-375.    | CJMP (10100)          | . 3-47 |

| 3-376.    | CLO (11101)           | . 3-47 |

| 3-377.    | CRS (10111)           |        |

| 3-379.    | DEC (00110)           |        |

| 3-380.    | DIV (00100)           | . 3-47 |

| 3-385.    | INC (01001)           | . 3-48 |

| 3-386.    | INCO (01000)          | . 3-48 |

| 3-387.    | IOR (11111)           | . 3-48 |

| 3-388.    | JMP (10010 or 10011)  | . 3-48 |

| 3-390.    | JSB (10000 or 10001)  |        |

| 3-391.    | LGS (10110)           |        |

| 3-393.    | LWF (11010)           | . 3-49 |

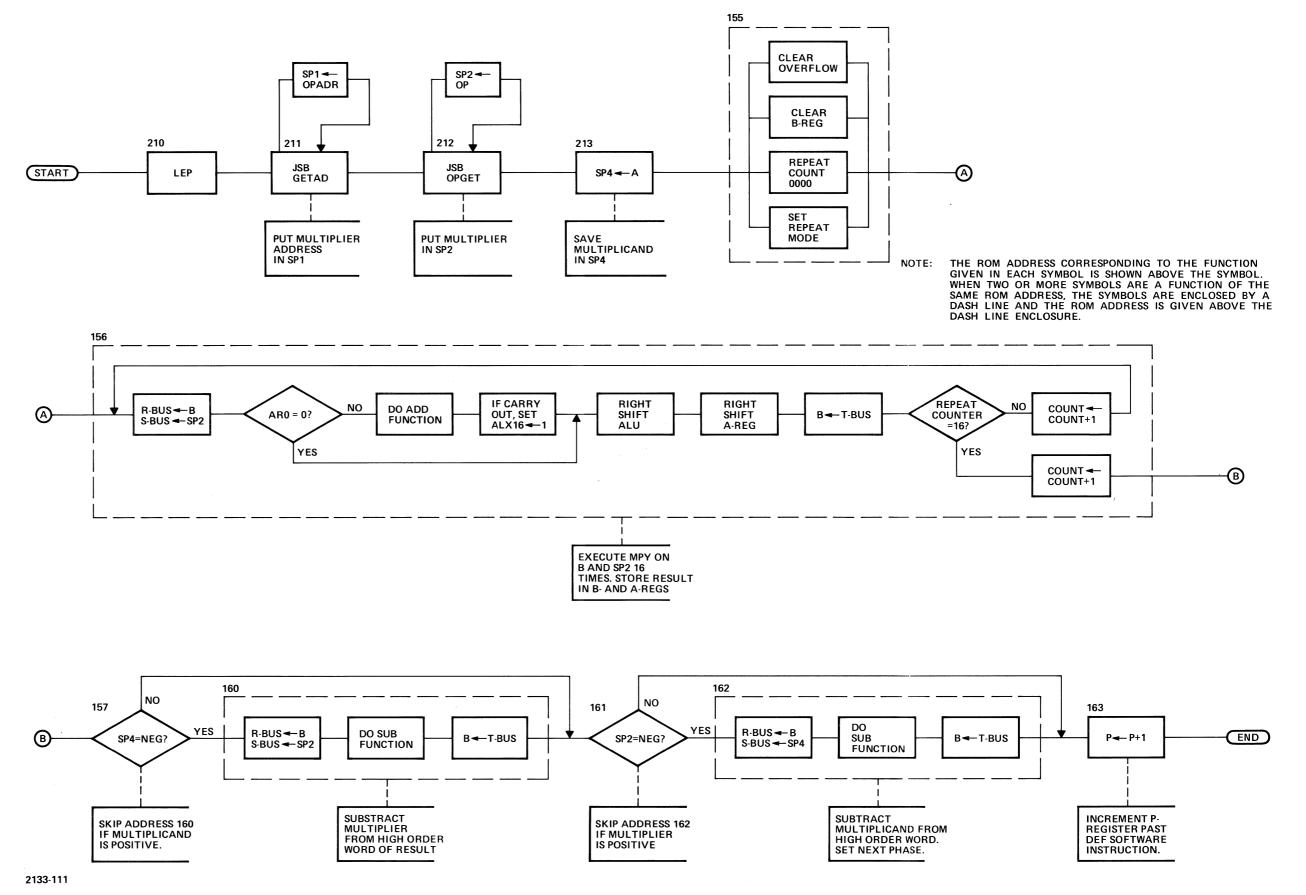

| 3-395.    | MPY (00011)           | . 3-49 |

| 3-397.    | NOR (01101)           |        |

| 3-398.    | P1A (00010)           |        |

| 3-399.    | RFE (00001)           |        |

| 3-400.    | RFI (00000)           | . 3-49 |

| 3-401.    | RSB (10101)           |        |

| 3-402.    | SFLG (11100)          |        |

| 3-403.    | SOV (11110)           |        |

| 3-404.    | SUB (00101)           |        |

| 3-405.    | XOR (01110)           |        |

| 3-406.    | Store Field Decoder   |        |

| 3-408.    | A (1110)              |        |

| 3-409.    | AAB (1100)            |        |

| 3-410.    | B (1101)              |        |

| 3-411.    | CAB (1011)            |        |

| 3-412.    | F (1001)              |        |

| 3-413.    | IOO (0000)            |        |

| 3-414.    | IR (0011)             |        |

| 3-415.    | M (0001)              |        |

| 3-416.    | P (1000)              |        |

| 3-417.    | Q (1010)              |        |

| 3-418.    | S1 (0111)             |        |

| 3-419.    | S2 (0110)             |        |

| 3-420.    | S3 (0101)             |        |

| 3-421.    | S4 (0100)             |        |

| 3-422.    | T (0010)              |        |

| 3-423.    | NOP (1111)            |        |

| 3-424.    | Special Field Decoder |        |

| 3-430.    | AAB (0110)            |        |

| 3-431.    | ASG1 (1010)           |        |

| 3-432.    | ASG2 (1011)           |        |

| 3-433.    | CNTR (0011)           |        |

| 3-434.    | CW (1100)             |        |

| 3-435.    | ECYN (1001)           | . 3-52 |

| 3-436.    | ECYZ (1000)           |        |

| 3-437.    | IOG1 (1101)           |        |

| 3-438.    | L1 (0001)             |        |

| 3-439.    | LEP (0111)            |        |

| 3-440.    | R1 (0010)             |        |

| 3-441.    | RSS (0000)            |        |

| 3-442.    | RW (1110)             |        |

| 3-443.    | SRG1 (0100)           |        |

| ~ ~ ~ ~ . |                       |        |

| Section          |                                              | Page  |

|------------------|----------------------------------------------|-------|

| 3-444.           | SRG2 (1011)                                  | 2 5 2 |

| 3-444.<br>3-445. | Skip Field Decoder                           |       |

| 3-443.<br>3-447. | AAB (1011)                                   |       |

| 3-447.<br>3-448. | COUT (0100)                                  |       |

| 3-446.<br>3-449. | CTR (1001)                                   |       |

| 3-449.<br>3-450. | CTRI (1000)                                  |       |

| 3-450.<br>3-451. | EOP (1101)                                   |       |

| 3-451.<br>3-452. |                                              |       |

|                  |                                              |       |

| 3-453.           | ICTR (0000)                                  |       |

| 3-454.           | NAAB (1100)                                  |       |

| 3-455.           | NEG (0011)                                   |       |

| 3-456.           | NMPV (1010)                                  |       |

| 3-457.           | ODD (0010)                                   |       |

| 3-458.           | OVF (0101)                                   |       |

| 3-459.           | RPT (0001)                                   |       |

| 3-460.           | TBZ (0111)                                   |       |

| 3-461.           | UNC (1110)                                   |       |

| 3-462.           | NOP (1111)                                   |       |

| 3-463.           | Repeat Counter                               |       |

| 3-466.           | Loading the Counter                          |       |

| 3-467.           | Incrementing the Counter                     |       |

| 3-470.           | Clearing the Counter                         |       |

| 3-471.           | Gating Onto the S-Bus                        |       |

| 3-472.           | EAG Doubleword Shifts and Rotates            |       |

| 3-473.           | EAG Multiply and Divide Operations           |       |

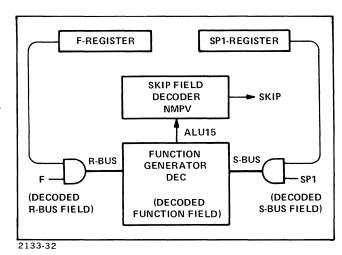

| 3-474.           | Arithmetic and Logic Section Detailed Theory |       |

| 3-477.           | A-Addressable and B-Addressable FF Logic     |       |

| 3-483.           | A/B Clear and A/B Select Flip-Flop Logic     |       |

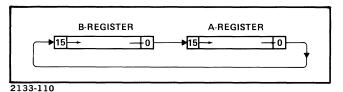

| 3-486.           | A- and B-Registers                           |       |

| 3-488.           | F- and Q-Registers                           |       |

| 3-490.           | P-Register                                   |       |

| 3-493.           | Scratch Pad Registers                        | 3-57  |

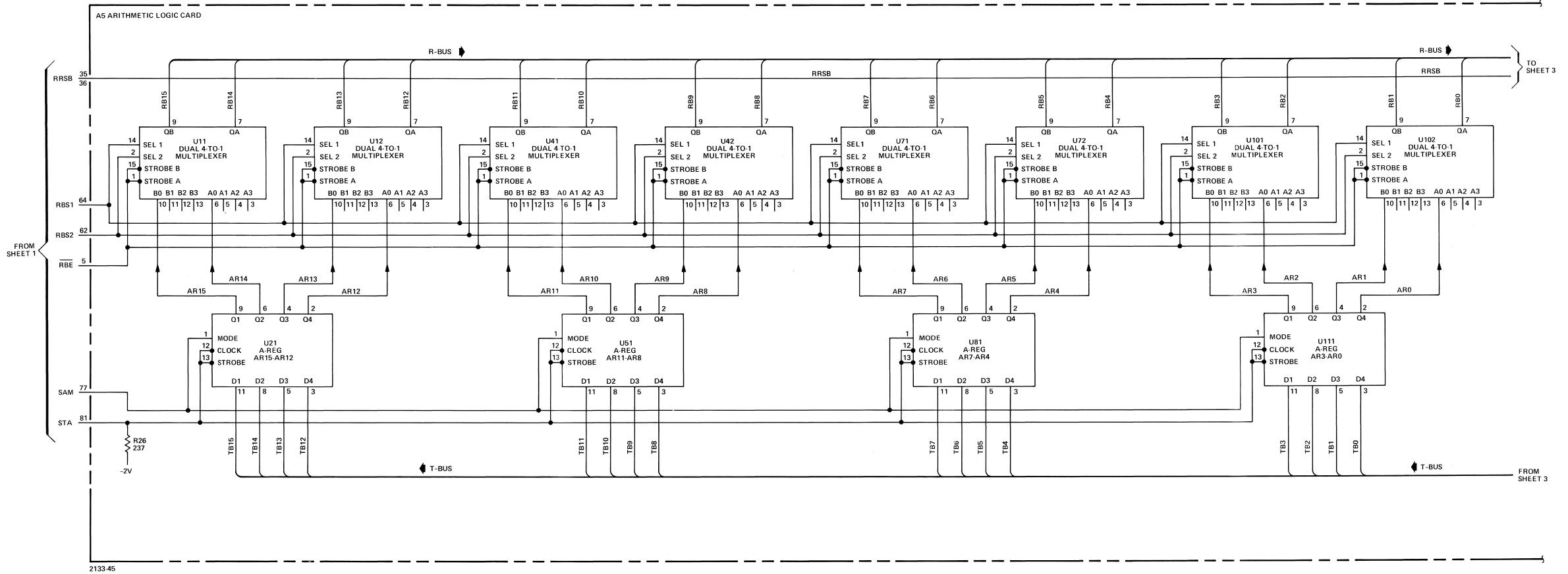

| 3-496.           | R-Bus Multiplexer                            | 3-57  |

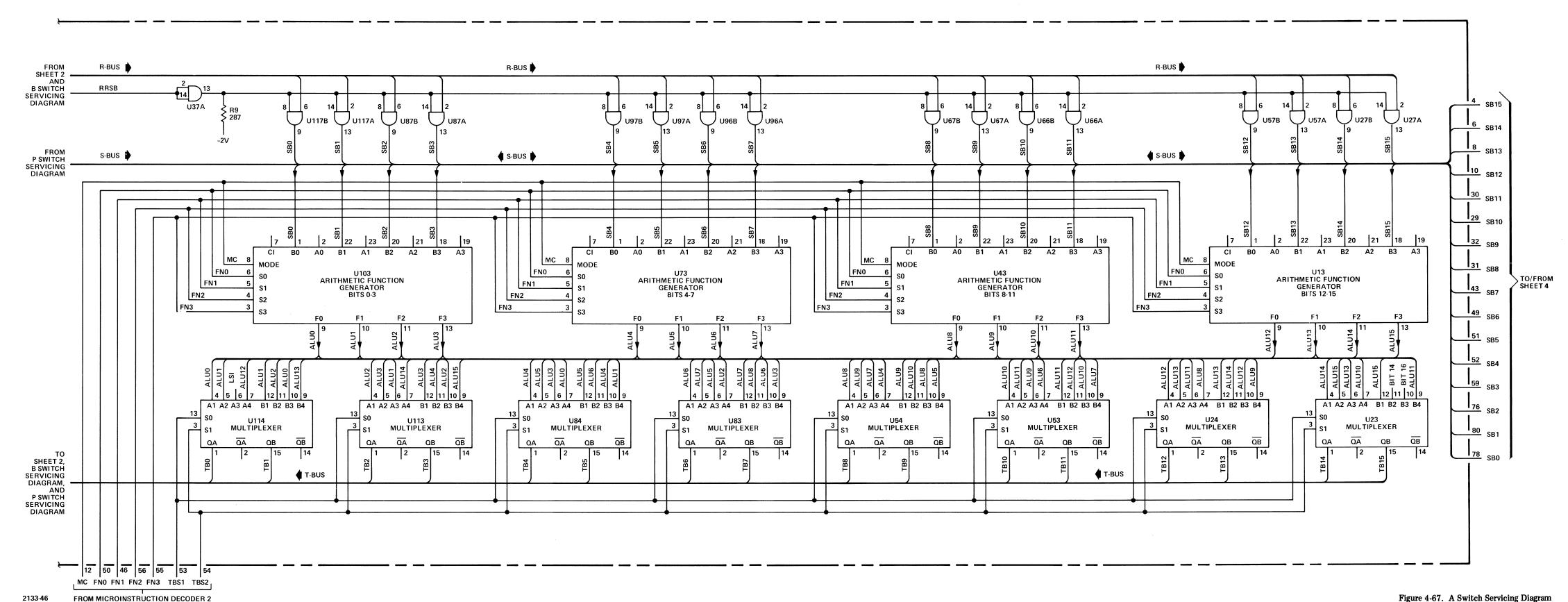

| 3-498.           | Arithmetic Function Generator                | 3-58  |

| 3-500.           | Shifter and Shift Linkage                    | 3-58  |

| 3-502.           | RFE Logic                                    | 3-58  |

| 3-504.           | CPU Flag Logic                               | 3-58  |

| 3-506.           | Extend Logic                                 |       |

| 3-508.           | Overflow Logic                               |       |

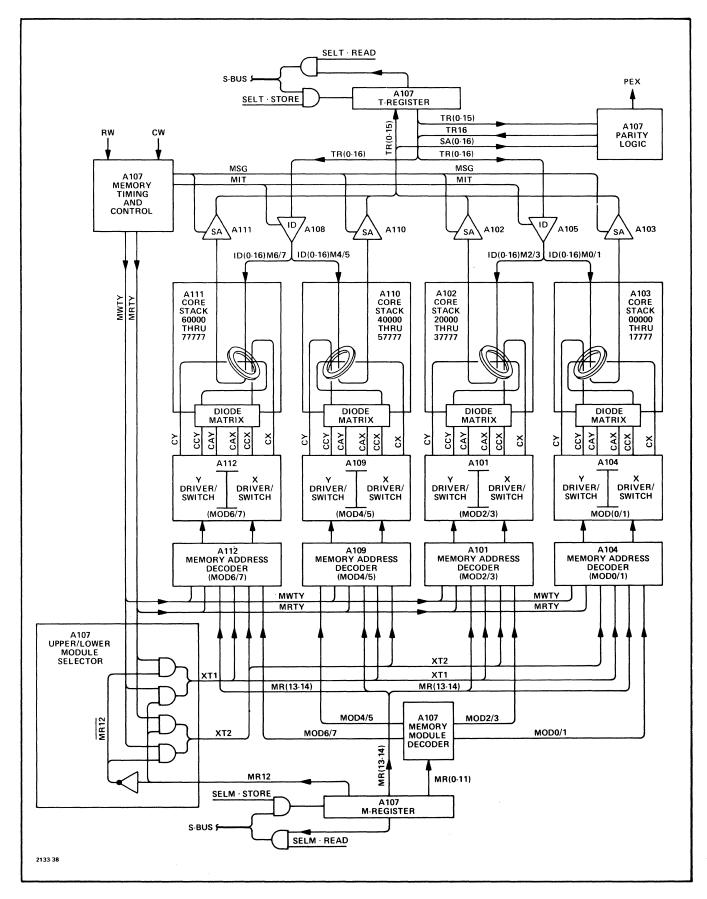

| 3-510.           | Memory Section, Detailed Theory              |       |

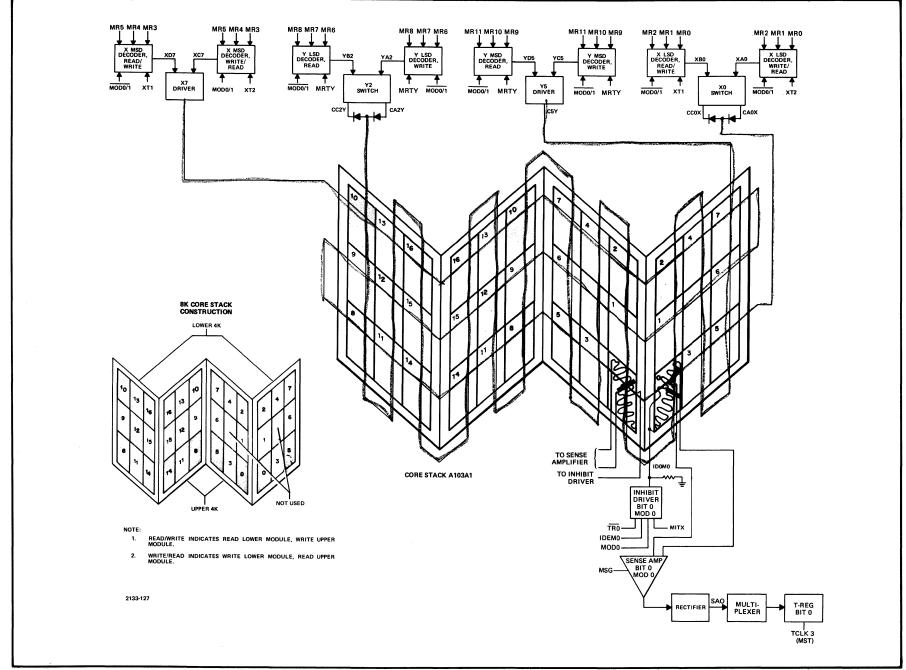

| 3-511.           | Functional Description                       |       |

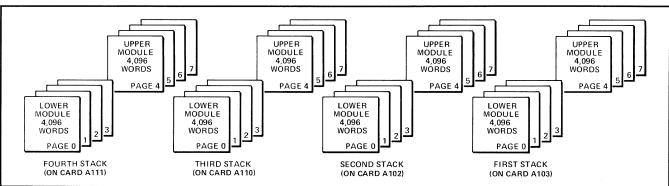

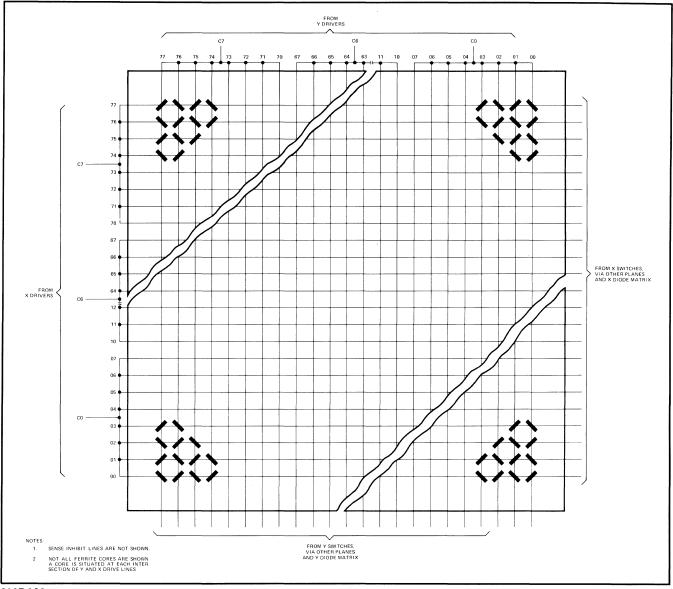

| 3-513.           | Core Stack Construction                      |       |

| 3-514.           | Organization of Data                         |       |

| 3-516.           | Addressing Method                            |       |

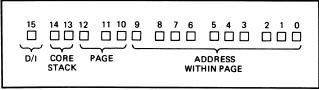

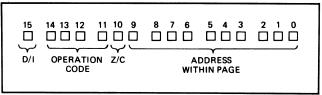

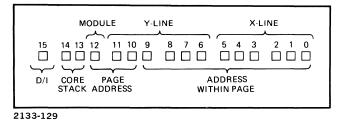

| 3-517.           | Full Address Word                            |       |

| 3-518.           | Addressing by Instruction Word               |       |

| 3-519.           | Memory Read Operations                       |       |

| 3-521.           | Readout for Display                          | 3-60  |

| 3-523.           | Instruction Word Readout                     |       |

| 3-525.           | Operand Readout                              |       |

| 3-533.           | Memory Write Operations                      |       |

| 3-535.           | Block Diagram Analysis                       |       |

| 3-536.           | Address Selection                            |       |

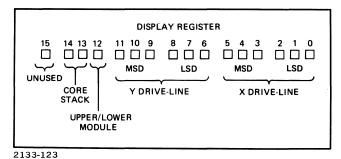

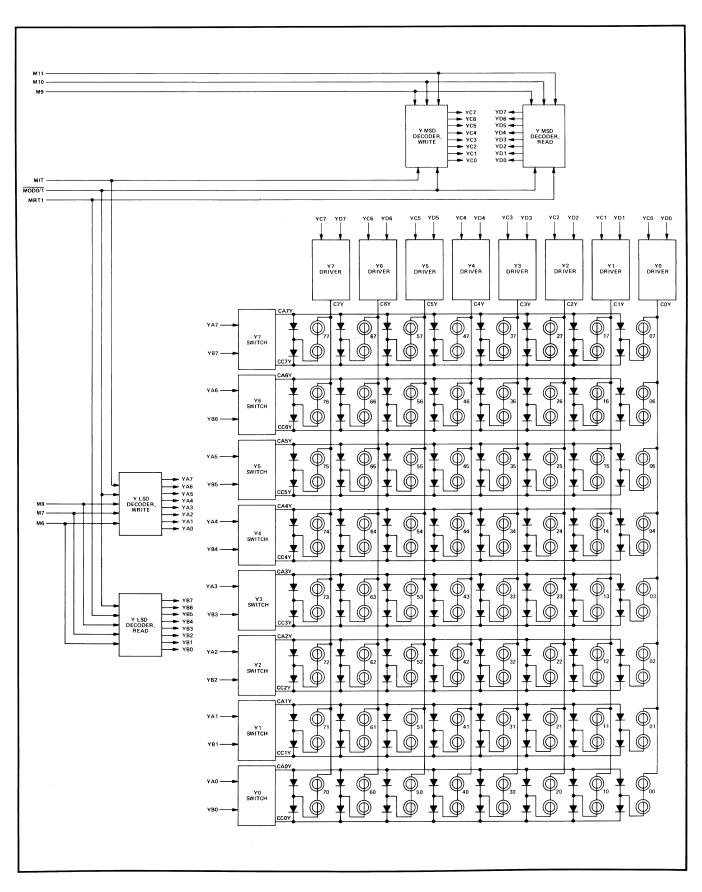

| 3-540.           | Y-Line Selection                             |       |

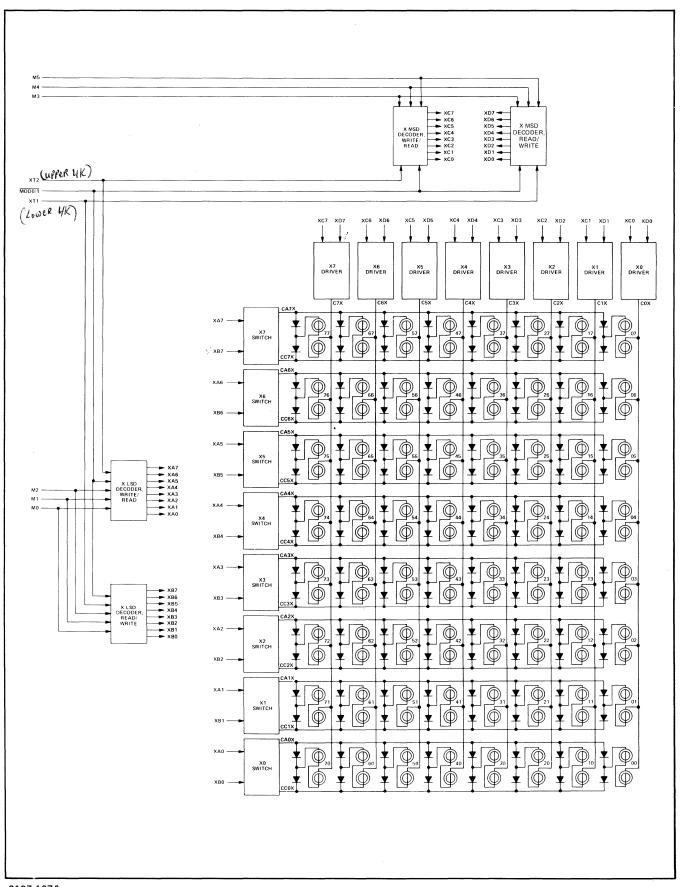

| 3-551.           | X-Line Selection                             |       |

| 3-555.           | Operation of Memory Section                  |       |

| Section             |                                 | Page |

|---------------------|---------------------------------|------|

| 3-556.              | Core Stack                      |      |

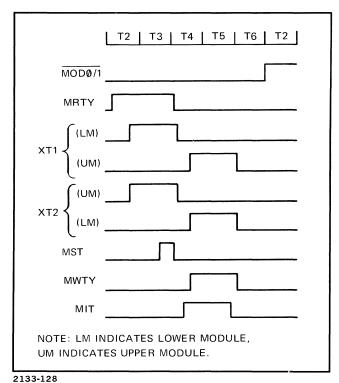

| 3-558.              | Lower Module Read Operations    |      |

| 3-568.              | Lower Module Write Operations   |      |

| 3-570.              | Upper Module Read Operations    |      |

| 3-571.              | Upper Module Write Operations   | 3-70 |

| 3-572.              | Logic Circuit Analysis          | 3-70 |

| 3-574.              | Addressing Circuits             | 3-70 |

| 3-582.              | Drivers and Switches            | 3-71 |

| 3-587.              | Sense Amplfiiers                | 3-72 |

| 3-593.              | Inhibit Drivers                 | 3-73 |

| 3-601.              | Parity                          | 3-74 |

| 3-605.              | Protective Circuits             |      |

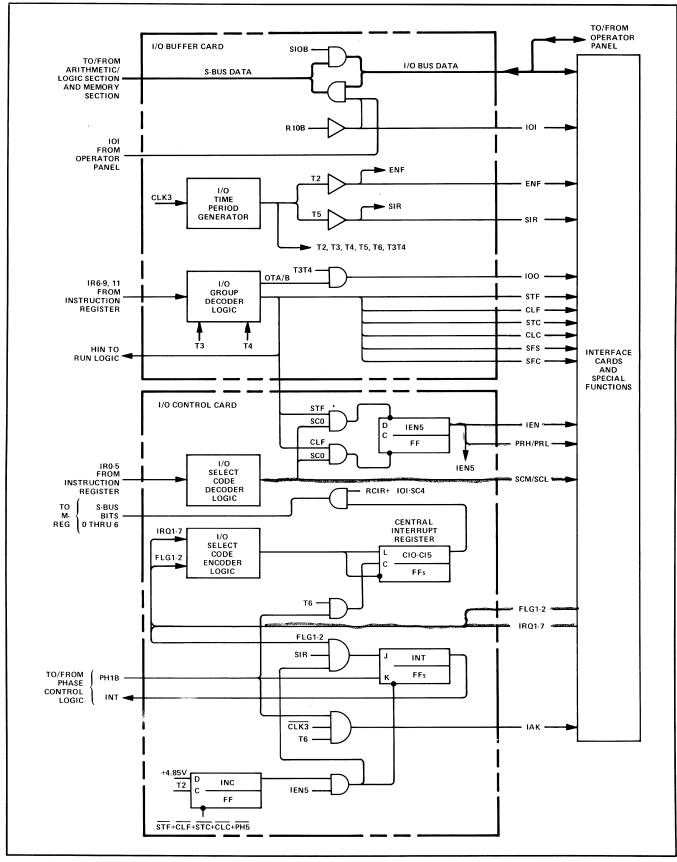

| 3-606.              | I/O Section Detailed Theory     |      |

| 3-607.              | General                         |      |

| 3-612.              | I/O Section Control Elements    |      |

| 3-613.              | General                         |      |

| 3-614.              | Input/Output Instructions       |      |

| 3-617.              | Interrupt Requests              |      |

| 3-618.              | Interface Cards                 |      |

| 3-619.              | Purpose                         |      |

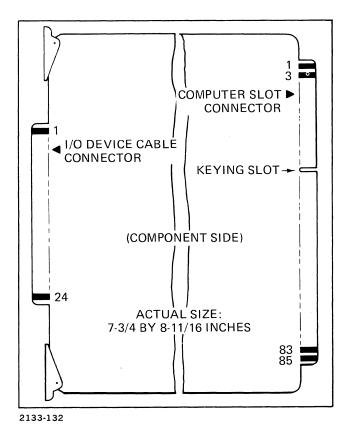

| 3-620.              | Logic Elements                  |      |

| 3-621.              | Pin Assignments                 |      |

| 3-624.              | I/O Terminator Card             |      |

| 3-62 <del>4</del> . | I/O Timing                      |      |

| 3-627.              | I/O Time Period Generator       |      |

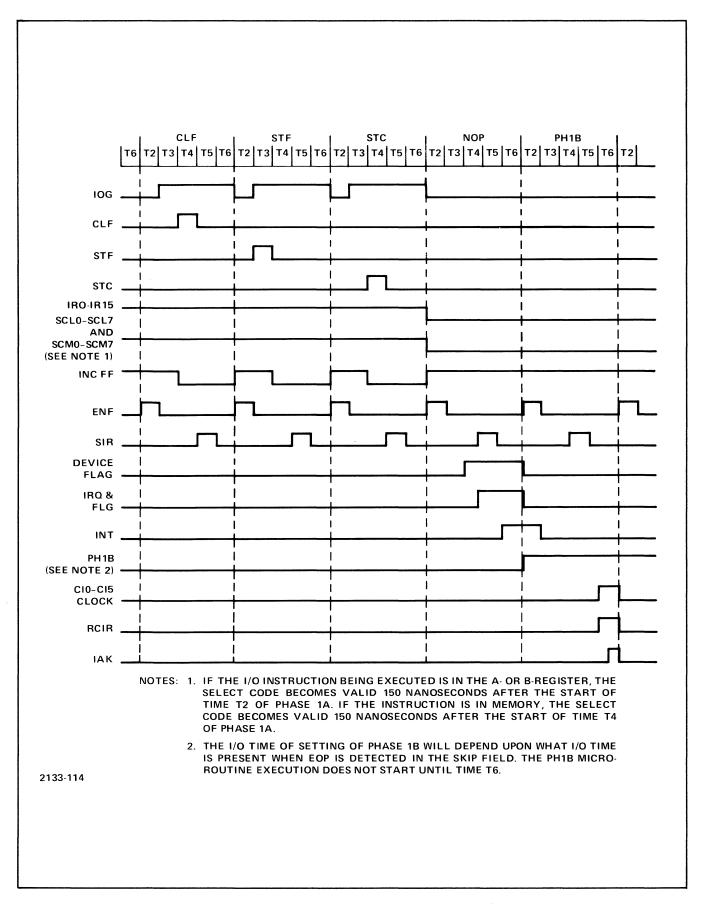

| 3-628.              | I/O Instruction Timing          |      |

| 3-630.              | I/O Control Signals Timing      |      |

| 3-631.              | ENF Signal                      |      |

| 3-632.              |                                 |      |

|                     | SIR Signal                      |      |

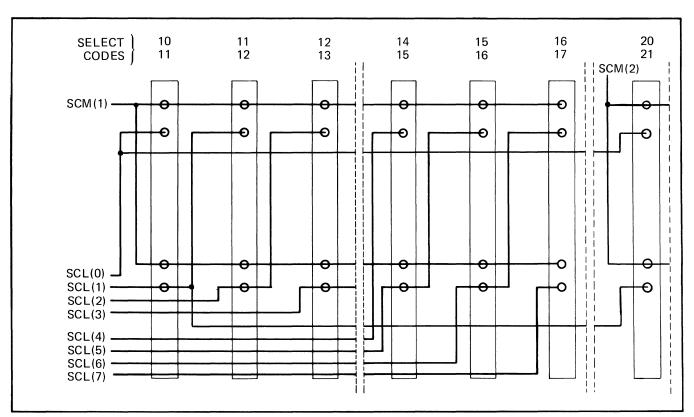

| 3-633.              | I/O Addressing                  |      |

| 3-637.              | Decoding Function               |      |

| 3-643.              | Encoding Function               |      |

| 3-644.              | Central Interrupt Register      |      |

| 3-645.              | Loading                         |      |

| 3-646.              | Clocking                        |      |

| 3-647.              | Output Gating                   |      |

| 3-649.              | I/O Instruction Processing      |      |

| 3-650.              | ROM Program Control             |      |

| 3-652.              | I/O Group Decoder Circuits      |      |

| 3-654.              | Data Transfer Instructions      |      |

| 3-655.              | MIA/B                           |      |

| 3-657.              | LIA/B                           |      |

| 3-658.              | OTA/B                           |      |

| 3-661.              | Control Instructions            |      |

| 3-662.              | Flag Instructions               |      |

| 3-663.              | Program Skip Instructions       |      |

| 3-664.              | Halt Instruction                |      |

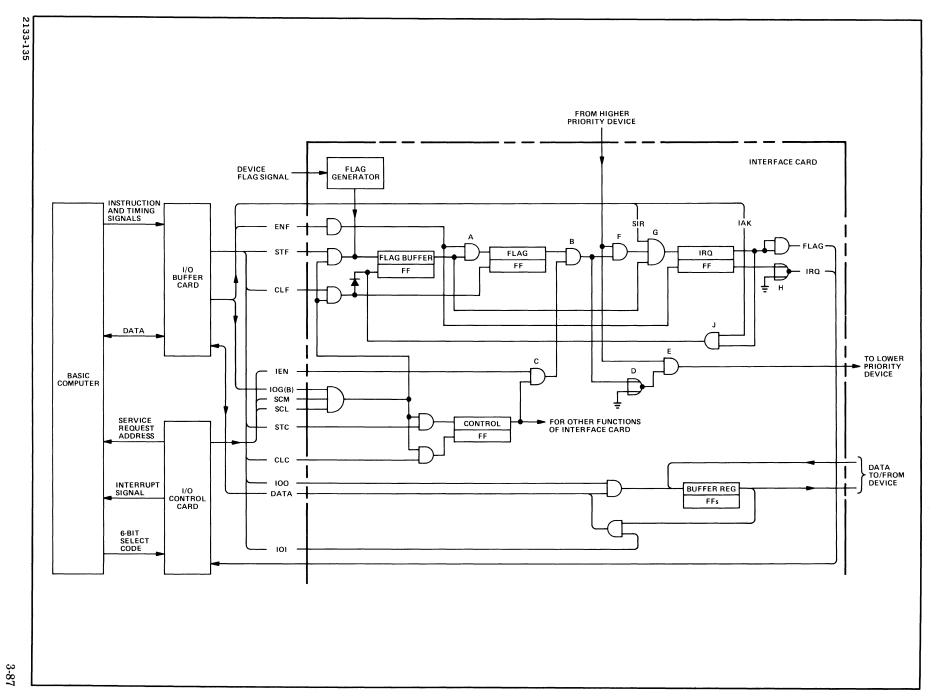

| 3-667.              | Interrupt System                |      |

| 3-670.              | Interrupt System Enable/Disable | 3-85 |

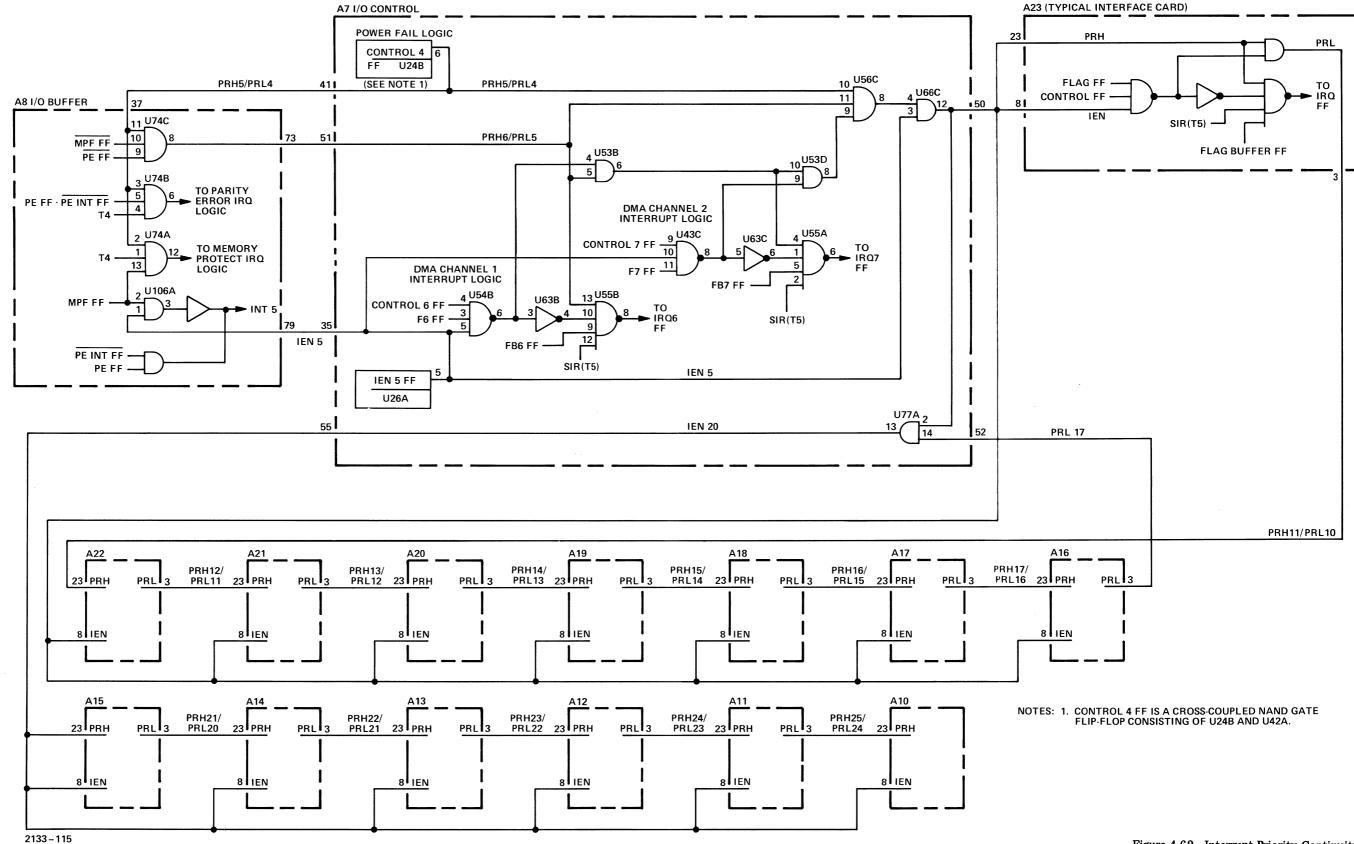

| 3-674.              | Interrupt Priority              | 3-88 |

| 3-675.              | Priority Assignments            |      |

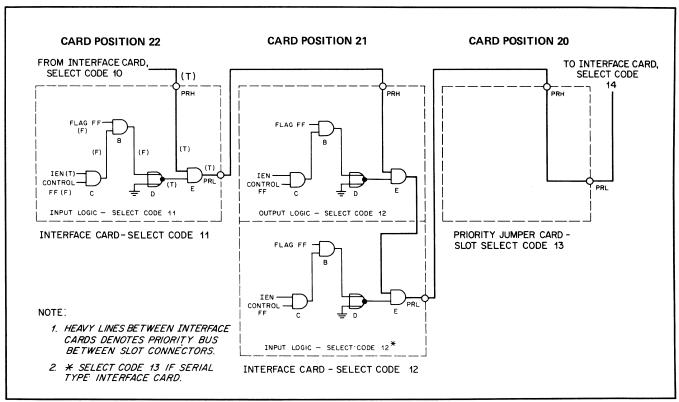

| 3-677.              | Priority Network Operation      |      |

| 3-682.              | Priority Continuity             |      |

| 3-684.              | Priority-Affecting Instructions |      |

| 3-686.              | Interrupt Generation            |      |

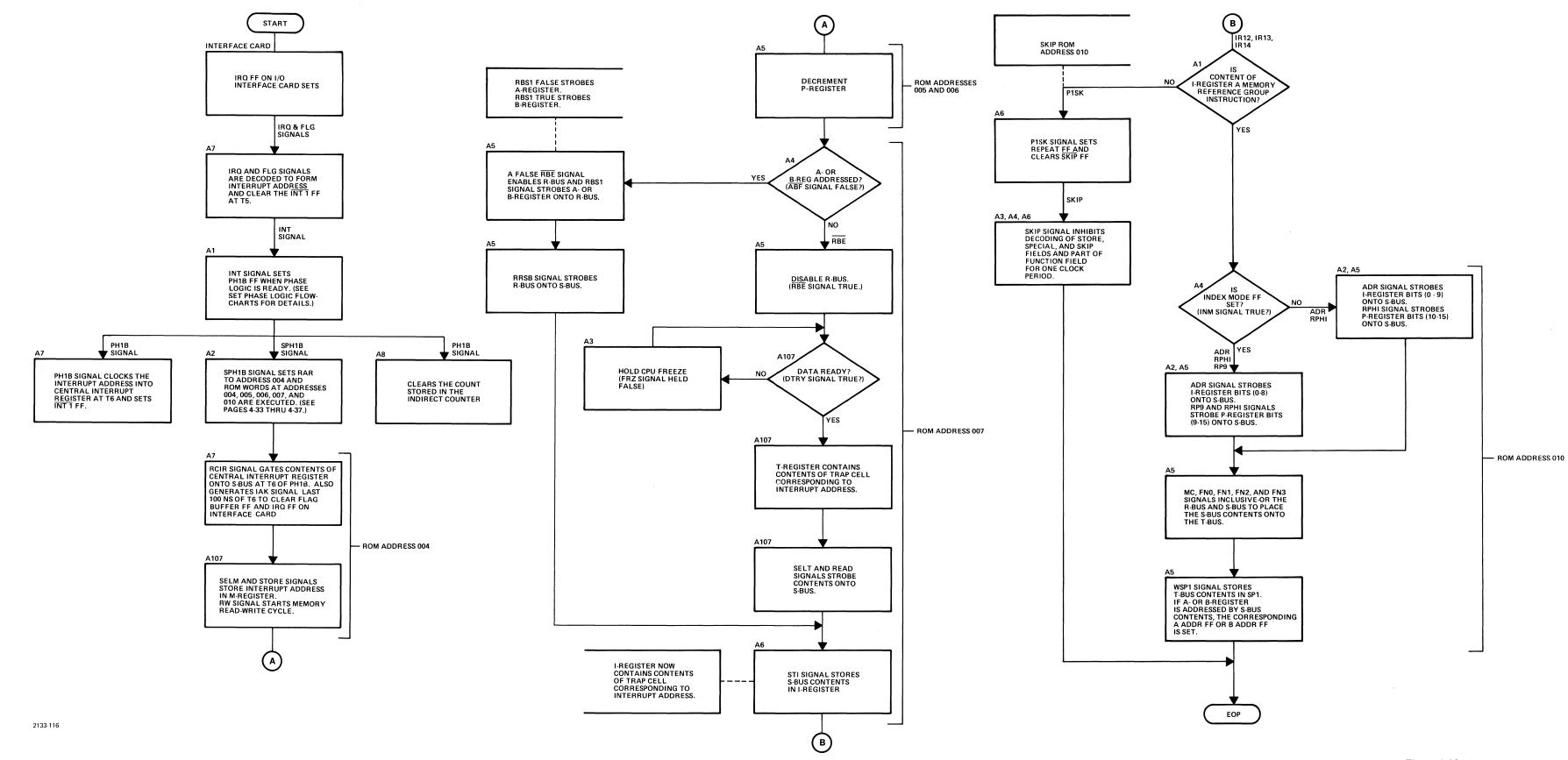

| 3-691.              | Interrupt Processing            |      |

| 3-692   Functional Description   3-90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Sect | ion                                  | P                                                                                                                   | age                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------|

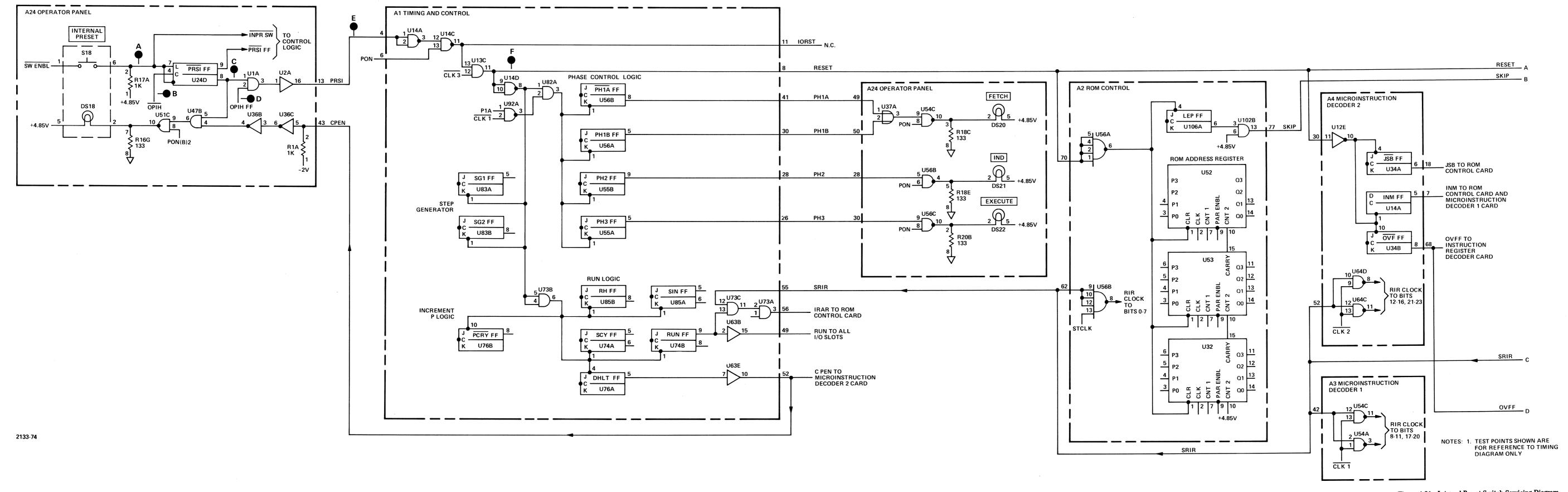

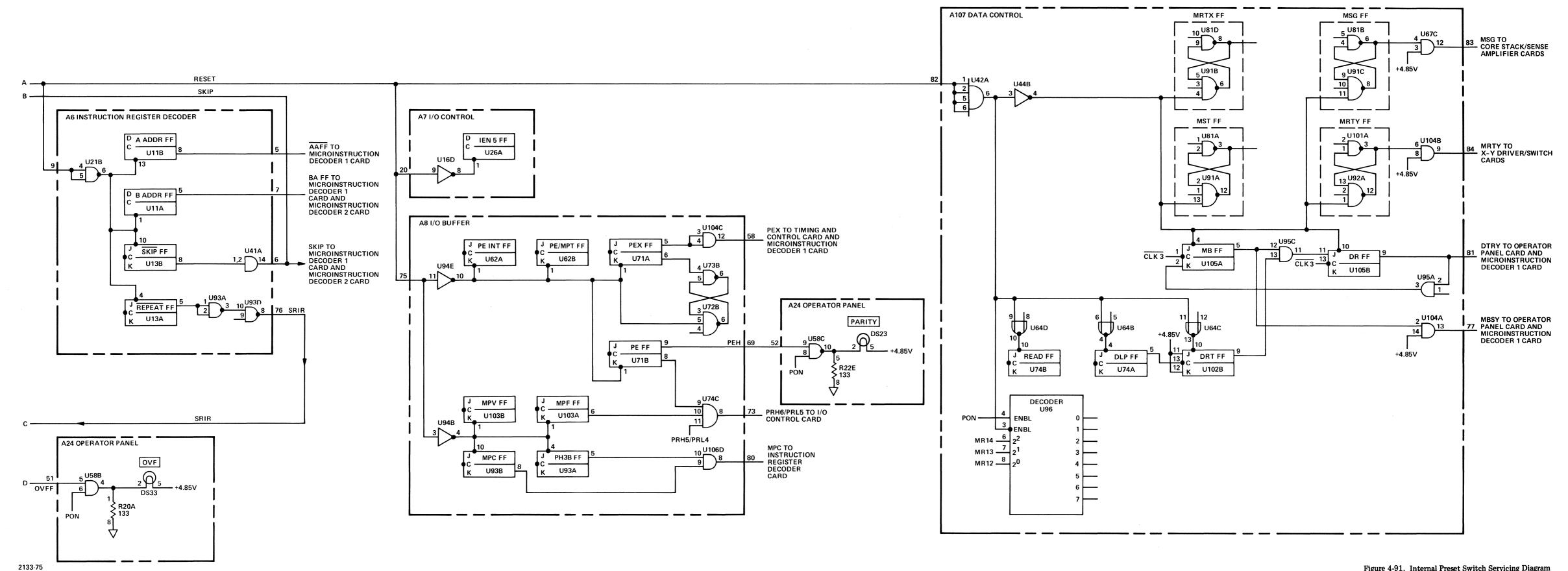

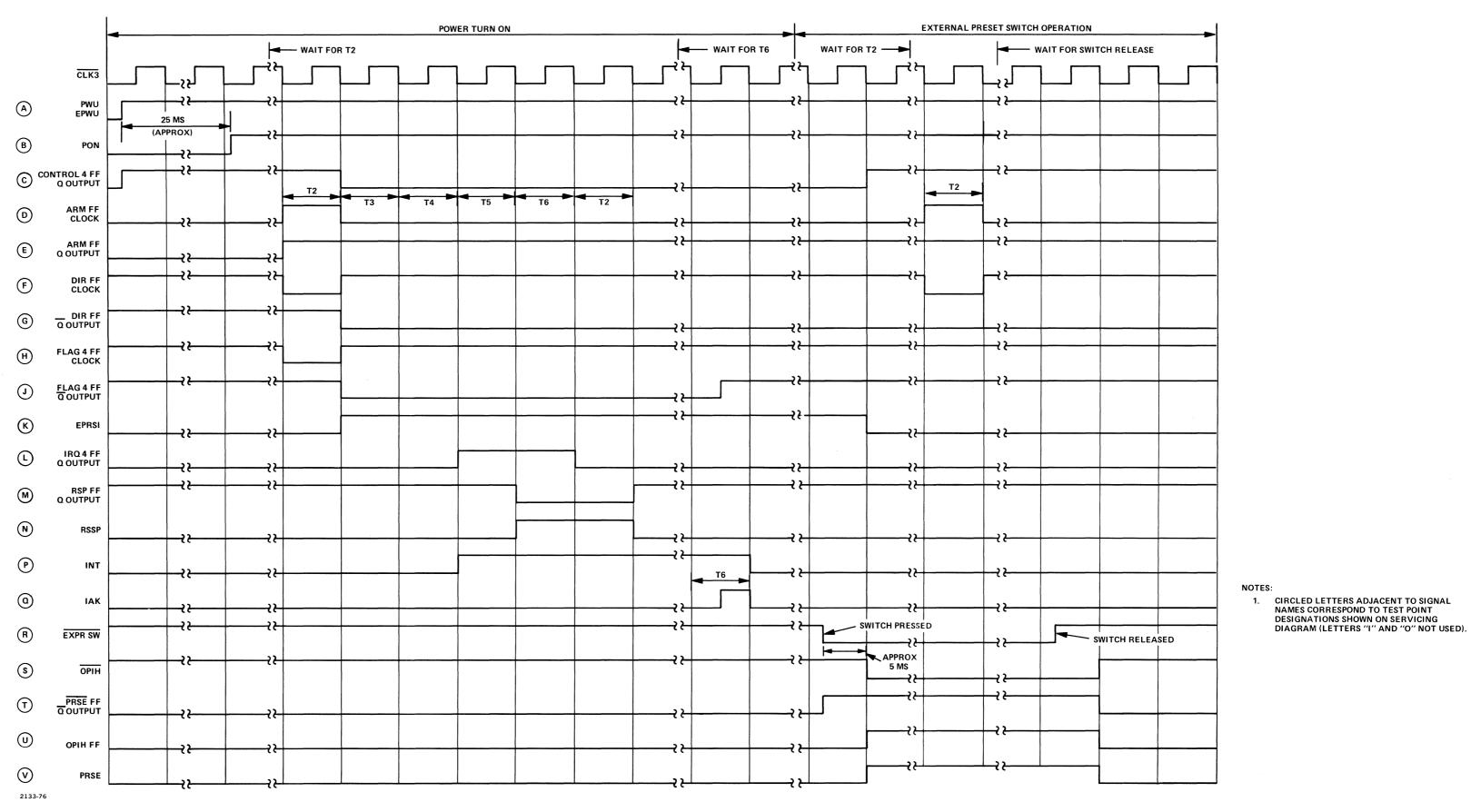

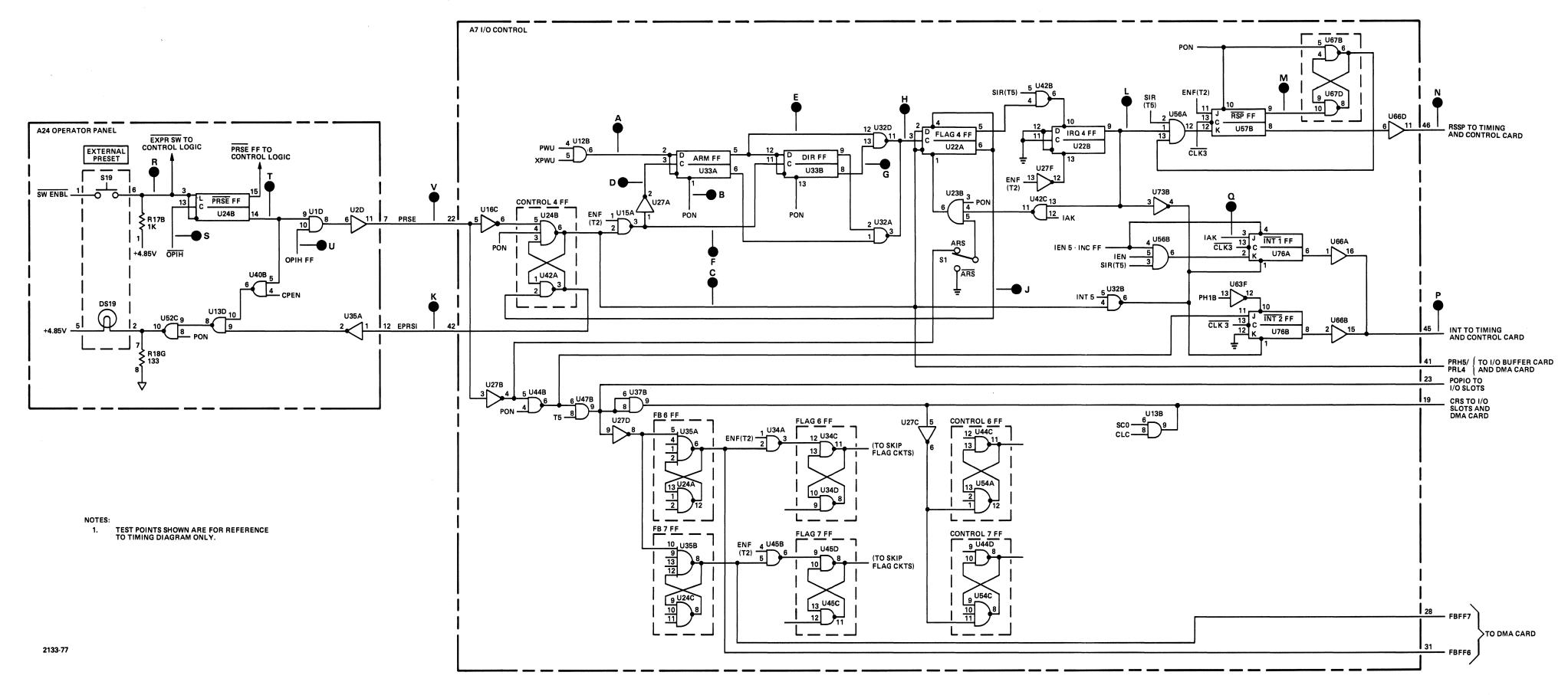

| 3-700. R OM Address 017 3-701. R OM Address 010 3-702. I/O System Reset 3-91 3-704. PON Signal 3-706. POPIO and CRS Signals 3-91 3-707. Reset Signal 3-708. I/O Violation Circuits  3-91 3-708. I/O Violation Circuits  3-91  3-708. I/O Violation Circuits  1V TROUBLESHOOTING 4-1. Introduction 4-1.4-3. General Servicing Information 4-1.4-4. Program Instruction Formats 4-1. Loading Absolute Loader Programs 4-1. Loading from Paper Tape 4-1. Loading from Paper Tape 4-1. Loading from Paper Tape 4-1. Diagnostic Operating Procedures 4-1. Sequence 4-1. Equipment of the Sequence 4-1. Error Halts 4-1. Test Sequence 4-3. Test Sequence 4-3. Loading Diagnostic Tapes using the HP 2748A Tape Reader 4-22. Loading Diagnostic Tapes with the HP 2752A Reader-Reroller 4-23. Loading Diagnostic Tapes with the HP 2752A Teleprinter 4-24. Loading Diagnostic Tapes with the HP 2752A Teleprinter 4-25. Loading Diagnostic Tapes with the HP 2752A Teleprinter 4-26. Maintenance Features 4-27. Loading Diagnostic Tapes with the HP 2752A Teleprinter 4-28. Basic Troubleshooting Procedures 4-30. Overall Computer Servicing Diagram 4-31. Set Phase Logic 4-32. Central Processor Servicing 4-33. Central Processor Servicing 4-34. Central Processor Servicing 4-35. God Maintenance Features 4-26. Maintenance Features 4-27. Loading Diagnostic Tapes with the HP 2752A Teleprinter 4-75. Loading Diagnostic Tapes with the HP 2752A Teleprinter 4-76. A-77. A-78. Basic Troubleshooting Procedures 4-98. Basic Troubleshooting Procedures 4-99. Central Processor Servicing Diagram 4-99. A-99.  |      | 3-694.<br>3-695.<br>3-697.<br>3-698. | Detailed Description       3         PH1B Signal       3         IAK Signal       3         ROM Address 004       3 | -90<br>-90<br>-91<br>-91 |

| 3-701. ROM Address 010 3-702. I/O System Reset 3-91 3-704. PON Signal 3-706. POPIO and CRS Signals 3-707. Reset Signal 3-708. I/O Violation Circuits 3-91 3-708. I/O Violation Circuits 3-91 3-708. I/O Violation Circuits 3-91  IV TROUBLESHOOTING 4-1. Introduction 4-1. Introduction 4-1. General Servicing Information 4-1. A-5. Program Instruction Formats 4-1. Loading from Paper Tape 4-1. Loading from the Operator Panel 4-1. Loading from the Operator Panel 4-1. Diagnostic Operating Procedures 4-1. Diagnostic Operating Procedures 4-1. General 4-1. General 4-1. Required Diagnostic Program Tapes and Procedures 4-1. Rest Sequence 4-1. Error Halts 4-2. Loading Diagnostic Tapes Using the HP 2748A Tape Reader 4-2. Loading Diagnostic Tapes Using the HP 2748A Reader-Reroller 4-2. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-2. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-2. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-2. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-2. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-2. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-2. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-2. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-2. Loading Diagnostic Tapes Using the HP 2758A Diagnostic 4-6 4-2. Loading Diagnostic Tapes Using the HP 2758A Diagnostic 4-6 4-2. Loading Diagnostic Tapes Using the HP 2758A Diagnostic 4-6 4-2. Restar Troubleshooting Procedures 4-3. Central Processor Servicing Diagnostic 4-6 4-3. Overall Computer Servicing Diagnostic 4-6 4-3. Overall Computer Servicing Diagnostic 4-8 4-3. Central Processor Servicing Diagnostic 4-8 4-3. Ann Instruction 4-4. Ann Instruction 4-5. Ann Instruction 4-6. Ann Instruction |      |                                      |                                                                                                                     |                          |

| 3-702. I/O System Reset 3-91 3-704. PON Signal 3-91 3-706. POPIO and CRS Signals 3-91 3-707. Reset Signal 3-91 3-708. I/O Violation Circuits 3-91 3-708. I/O Violation Circuits 3-91  TROUBLESHOOTING 4-1. Introduction 4-1 4-3. General Servicing Information 4-1 4-4. Loading Instruction Formats 4-1 4-8. Loading Absolute Loader Programs 4-1 4-10. Loading from Paper Tape 4-1 4-11. Loading from the Operator Panel 4-1 4-14. Diagnostic Operating Procedures 4-1 4-15. General 4-1 4-16. Required Diagnostic Program Tapes and Procedures 4-3 4-16. Required Diagnostic Program Tapes and Procedures 4-3 4-19. Error Halts 4-3 4-19. Error Halts 4-3 4-20. Procedures for Loading Diagnostic Tapes 4-5 4-22. Loading Diagnostic Tapes Using the HP 2748A Tape Reader 4-5 4-23. Loading Diagnostic Tapes Using the HP 2752A Teleprinter 4-7 4-25. Loading Halts 4-8 4-26. Maintenance Features 4-8 4-28. Basic Troubleshooting Procedures 4-8 4-28. Basic Troubleshooting Procedures 4-8 4-29. Overall Computer Servicing Diagram 4-9 4-30. Overall Computer Servicing Diagram 4-9 4-31. Central Processor Servicing Diagram 4-9 4-32. Central Processor Servicing Diagram 4-9 4-33. Hossel 1-1 4-34. Set Phase 1-1 4-35. AND Instruction 4-9 4-36. Memory Reference Group 4-4-1 4-45. Phase 1-1 4-47. Phase 2-1 4-48. AND Instruction 4-46 4-58. AD* Instruction 4-46 4-59. CP* Instruction 4-67 4-69. CP* Instruction 4-70 4-69. CP* Instruction 4-79 4-60. LD* Instruction 4-70                                                                                                                                                           |      |                                      |                                                                                                                     |                          |

| 3-704. PON Signal 3-706. POPIO and CRS Signals 3-91 3-707. Reset Signal 3-708. I/O Violation Circuits  3-91 3-708. I/O Violation Circuits  3-91 3-708. I/O Violation Circuits  3-91  IV TROUBLESHOOTING 4-1. Introduction 4-1. Introduction 4-1. Seneral Servicing Information 4-1. Loading Absolute Loader Programs 4-1. Loading Absolute Loader Programs 4-1. Loading from Paper Tape 4-1. Loading from Paper Tape 4-1. Loading from the Operator Panel 4-1. General 4-1. General 4-1. General 4-1. General 4-1. Est Sequence 4-1. Est Sequence 4-2. Loading Diagnostic Program Tapes and Procedures 4-1. Perror Halts 4-20. Procedures for Loading Diagnostic Tapes 4-21. Loading Diagnostic Tapes Using the HP 2748A Tape Reader 4-22. Loading Diagnostic Tapes Using the HP 2748A Tape Reader 4-24. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-24. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-24. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-26. Maintenance Features 4-28. Basic Troubleshooting Procedures 4-28. Basic Troubleshooting Procedures 4-29. Overall Computer Servicing Diagram 4-30. Overall Computer Servicing Diagram 4-30. Overall Computer Servicing Diagram 4-31. Central Processor Servicing 4-32. Central Processor Timing Specifications 4-33. And                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                                      |                                                                                                                     |                          |

| 3-706. POPIO and CRS Signals 3-91 3-707. Reset Signal 3-91 3-708. I/O Violation Circuits 3-91  IV TROUBLESHOOTING  4-1. Introduction 4-1 4-3. General Servicing Information 4-1 4-5. Program Instruction Formats 4-1 4-15. Program Instruction Formats 4-1 4-10. Loading Absolute Loader Programs 4-1 4-11. Loading from Paper Tape 4-1 4-13. Loading from Paper Tape 4-1 4-14. Diagnostic Operating Procedures 4-1 4-15. General 4-1 4-16. Required Diagnostic Program Tapes and Procedures 4-3 4-18. Test Sequence 4-3 4-19. Error Halts 4-3 4-19. Error Halts 4-3 4-20. Procedures for Loading Diagnostic Tapes 4-5 4-22. Loading Diagnostic Tapes Using the HP 2748A Tape Reader 4-5 4-23. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-6 4-24. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-6 4-25. Loading Halts 4-8 4-26. Maintenance Features 4-8 4-28. Basic Troubleshooting Procedures 4-8 4-28. Basic Troubleshooting Procedures 4-9 4-30. Overall Computer Servicing Diagram 4-9 4-31. Central Processor Servicing Data 4-9 4-32. Central Processor Servicing Data 4-9 4-34. Central Processor Servicing Data 4-9 4-35. ADM Instruction 4-9 4-45. Phase 1B 4-9 4-56. JMD Instruction 4-44 4-57. ISZ Instruction 4-45 4-58. AD* Instruction 4-67 4-66. LD* Instruction 4-70 4-70 4-70 4-70 4-70 4-70 4-70 4-70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |                                      | · · · ·                                                                                                             |                          |

| 3-707. Reset Signal 3-91 3-708. I/O Violation Circuits 3-91  IV TROUBLESHOOTING 4-1. Introduction 4-1 4-3. General Servicing Information 4-1 4-5. Program Instruction Formats 4-1 4-15. Program Instruction Formats 4-1 4-10. Loading from Paper Tape 4-1 4-11. Loading from Paper Tape 4-1 4-12. Loading from the Operator Panel 4-1 4-14. Diagnostic Operating Procedures 4-1 4-15. General 4-1 4-16. Required Diagnostic Program Tapes and Procedures 4-3 4-16. Required Diagnostic Program Tapes and Procedures 4-3 4-18. Test Sequence 4-3 4-19. Error Halts 4-3 4-20. Procedures for Loading Diagnostic Tapes 4-5 4-22. Loading Diagnostic Tapes Using the HP 2748A Tape Reader 4-5 4-23. Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller 4-6 4-24. Loading Diagnostic Tapes Using the HP 2752A Teleprinter 4-7 4-25. Loading Diagnostic Tapes Using the HP 2752A Teleprinter 4-7 4-26. Maintenance Features 4-8 4-28. Basic Troubleshooting Procedures 4-9 4-30. Overall Computer Servicing Diagram 4-9 4-31. Central Processor Servicing 4-9 4-32. Central Processor Servicing Diagram 4-9 4-33. Contral Processor Servicing Diagram 4-9 4-34. Central Processor Servicing Diagram 4-9 4-35. ROM Microprogram Servicing Data 4-28 4-41. Set Phase Logic 4-30 4-43. Phase 1A 4-30 4-45. Phase 1B 4-33 4-47. Phase 2 4-48. AND Instruction 4-49 4-55. JSB Instruction 4-44 4-55. JSB Instruction 4-45 4-56. JMP Instruction 4-45 4-57. ISZ Instruction 4-57 4-57. ISZ Instruction 4-57 4-58. AD* Instruction 4-70 4-59. CP* Instruction 4-70 4-61. LD* Instruction 4-79 4-61. LD* Instruction 4-79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                                      | · · · · · · · · · · · · · · · · · · ·                                                                               |                          |

| IV TROUBLESHOOTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      | 3-707.                               | · · · · · · · · · · · · · · · · · · ·                                                                               |                          |

| 4-1.       Introduction       4-1         4-3.       General Servicing Information       4-1         4-5.       Program Instruction Formats       4-1         4-8.       Loading Absolute Loader Programs       4-1         4-10.       Loading from Paper Tape       4-1         4-11.       Loading from the Operator Panel       4-1         4-14.       Diagnostic Operating Procedures       4-1         4-15.       General       4-3         4-16.       Required Diagnostic Program Tapes and Procedures       4-3         4-18.       Test Sequence       4-3         4-19.       Error Halts       4-3         4-20.       Procedures for Loading Diagnostic Tapes       4-5         4-22.       Loading Diagnostic Tapes Using the HP 2748A Tape Reader       4-5         4-22.       Loading Diagnostic Tapes with the HP 2755A Reader-Reroller       4-6         4-23.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-24.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-25.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-26.       Maintenance Features       4-8         4-28.       Basic Troubleshooting Procedures <td< td=""><td></td><td>3-708.</td><td>I/O Violation Circuits</td><td>-91</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      | 3-708.                               | I/O Violation Circuits                                                                                              | -91                      |

| 4-1.       Introduction       4-1         4-3.       General Servicing Information       4-1         4-5.       Program Instruction Formats       4-1         4-8.       Loading Absolute Loader Programs       4-1         4-10.       Loading from Paper Tape       4-1         4-13.       Loading from the Operator Panel       4-1         4-14.       Diagnostic Operating Procedures       4-1         4-15.       General       4-3         4-16.       Required Diagnostic Program Tapes and Procedures       4-3         4-18.       Test Sequence       4-3         4-19.       Error Halts       4-3         4-20.       Procedures for Loading Diagnostic Tapes       4-5         4-22.       Loading Diagnostic Tapes Using the HP 2748A Tape Reader       4-5         4-23.       Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller       4-6         4-24.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-25.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-26.       Maintenance Features       4-8         4-28.       Basic Troubleshooting Procedures       4-8         4-28.       Basic Troubleshooting Procedures       4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                      |                                                                                                                     |                          |

| 4-3.       General Servicing Information       4-1         4-5.       Program Instruction Formats       4-1         4-8.       Loading Absolute Loader Programs       4-1         4-10.       Loading from Paper Tape       4-1         4-13.       Loading from the Operator Panel       4-1         4-14.       Diagnostic Operating Procedures       4-1         4-15.       General       4-3         4-16.       Required Diagnostic Program Tapes and Procedures       4-3         4-18.       Test Sequence       4-3         4-19.       Error Halts       4-3         4-20.       Procedures for Loading Diagnostic Tapes       4-5         4-22.       Loading Diagnostic Tapes Using the HP 2748A Tape Reader       4-5         4-23.       Loading Diagnostic Tapes with the HP 2758A Reader-Reroller       4-6         4-24.       Loading Diagnostic Tapes With the HP 2758A Teleprinter       4-7         4-25.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-26.       Maintenance Features       4-8         4-28.       Basic Troubleshooting Procedures       4-8         4-28.       Basic Troubleshooting Procedures       4-9         4-30.       Overall Computer Servicing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IV   |                                      |                                                                                                                     |                          |

| 4-5.       Program Instruction Formats       4-1         4-8.       Loading Absolute Loader Programs       4-1         4-10.       Loading from Paper Tape       4-1         4-13.       Loading from the Operator Panel       4-1         4-14.       Diagnostic Operating Procedures       4-3         4-16.       Required Diagnostic Program Tapes and Procedures       4-3         4-18.       Test Sequence       4-3         4-19.       Error Halts       4-3         4-20.       Procedures for Loading Diagnostic Tapes       4-5         4-22.       Loading Diagnostic Tapes Using the HP 2748A Tape Reader       4-5         4-23.       Loading Diagnostic Tapes with the HP 2758A Reader-Reroller       4-6         4-24.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-25.       Loading Halts       4-8         4-26.       Maintenance Features       4-8         4-28.       Basic Troubleshooting Procedures       4-8         4-28.       Basic Troubleshooting Procedures       4-9         4-30.       Overall Computer Servicing Diagram       4-9         4-31.       Central Processor Fervicing Data       4-9         4-32.       Central Processor Fervicing Data       4-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                                      |                                                                                                                     |                          |

| 4-8.       Loading Absolute Loader Programs       4-1         4-10.       Loading from Paper Tape       4-1         4-13.       Loading from the Operator Panel       4-1         4-14.       Diagnostic Operating Procedures       4-1         4-15.       General       4-3         4-16.       Required Diagnostic Program Tapes and Procedures       4-3         4-18.       Test Sequence       4-3         4-19.       Error Halts       4-3         4-20.       Procedures for Loading Diagnostic Tapes       4-5         4-22.       Loading Diagnostic Tapes Using the HP 2748A Tape Reader       4-5         4-23.       Loading Diagnostic Tapes Using the HP 2758A Reader-Reroller       4-6         4-24.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-25.       Loading Halts       4-8         4-26.       Maintenance Features       4-8         4-28.       Basic Troubleshooting Procedures       4-9         4-30.       Overall Computer Servicing Diagram       4-9         4-31.       Central Processor Servicing Data       4-9         4-32.       Central Processor Timing Specifications       4-9         4-43.       Phase 1A       4-30         4-41. <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                      |                                                                                                                     |                          |

| 4-10.       Loading from Paper Tape       4-1         4-13.       Loading from the Operator Panel       4-1         4-14.       Diagnostic Operating Procedures       4-1         4-15.       General       4-3         4-16.       Required Diagnostic Program Tapes and Procedures       4-3         4-18.       Test Sequence       4-3         4-19.       Error Halts       4-3         4-20.       Procedures for Loading Diagnostic Tapes       4-5         4-22.       Loading Diagnostic Tapes Using the HP 2748 A Tape Reader       4-5         4-23.       Loading Diagnostic Tapes with the HP 2758 A Reader-Reroller       4-6         4-24.       Loading Diagnostic Tapes Using the HP 2752 A Teleprinter       4-7         4-25.       Loading Halts       4-8         4-26.       Maintenance Features       4-8         4-28.       Basic Troubleshooting Procedures       4-8         4-28.       Basic Troubleshooting Procedures       4-9         4-30.       Overall Computer Servicing Diagram       4-9         4-31.       Central Processor Servicing       4-9         4-32.       Central Processor Timing Specifications       4-9         4-33.       ROM Microprogram Servicing Diagram       4-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                      |                                                                                                                     |                          |

| 4-13.       Loading from the Operator Panel       4-1         4-14.       Diagnostic Operating Procedures       4-1         4-15.       General       4-3         4-16.       Required Diagnostic Program Tapes and Procedures       4-3         4-18.       Test Sequence       4-3         4-19.       Error Halts       4-3         4-20.       Procedures for Loading Diagnostic Tapes       4-5         4-22.       Loading Diagnostic Tapes Using the HP 2748A Tape Reader       4-5         4-23.       Loading Diagnostic Tapes with the HP 2758A Reader-Reroller       4-6         4-24.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-25.       Loading Halts       4-8         4-26.       Maintenance Features       4-8         4-28.       Basic Troubleshooting Procedures       4-9         4-30.       Overall Computer Servicing Diagram       4-9         4-31.       Central Processor Servicing       4-9         4-32.       Central Processor Timing Specifications       4-9         4-34.       Central Processor Timing Specifications       4-9         4-35.       ROM Microprogram Servicing Data       4-28         4-41.       Set Phase Logic       4-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      | •                                    |                                                                                                                     |                          |

| 4-14.       Diagnostic Operating Procedures       4-1         4-15.       General       4-3         4-16.       Required Diagnostic Program Tapes and Procedures       4-3         4-18.       Test Sequence       4-3         4-19.       Error Halts       4-3         4-20.       Procedures for Loading Diagnostic Tapes       4-5         4-22.       Loading Diagnostic Tapes Using the HP 2748A Tape Reader       4-5         4-23.       Loading Diagnostic Tapes with the HP 2752A Reader-Reroller       4-6         4-24.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-25.       Loading Halts       4-8         4-26.       Maintenance Features       4-8         4-28.       Basic Troubleshooting Procedures       4-9         4-30.       Overall Computer Servicing Diagram       4-9         4-31.       Central Processor Servicing       4-9         4-32.       Central Processor Servicing Data       4-9         4-34.       Central Processor Timing Specifications       4-9         4-35.       ROM Microprogram Servicing Data       4-28         4-41.       Set Phase Logic       4-30         4-43.       Phase 1A       4-30         4-44. <t< td=""><td></td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                      |                                                                                                                     |                          |

| 4-15.       General       4-3         4-16.       Required Diagnostic Program Tapes and Procedures       4-3         4-18.       Test Sequence       4-3         4-19.       Error Halts       4-3         4-20.       Procedures for Loading Diagnostic Tapes       4-5         4-22.       Loading Diagnostic Tapes Using the HP 2748A Tape Reader       4-5         4-23.       Loading Diagnostic Tapes Using the HP 2752A Reader-Reroller       4-6         4-24.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-25.       Loading Halts       4-8         4-26.       Maintenance Features       4-8         4-28.       Basic Troubleshooting Procedures       4-9         4-30.       Overall Computer Servicing Diagram       4-9         4-31.       Central Processor Servicing       4-9         4-32.       Central Processor Servicing Data       4-9         4-34.       Central Processor Timing Specifications       4-9         4-36.       ROM Microprogram Servicing Data       4-28         4-41.       Set Phase Logic       4-30         4-42.       Phase 1B       4-33         4-43.       Phase 2       4-38         4-44.       Phase 3       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                                      |                                                                                                                     |                          |

| 4-16.       Required Diagnostic Program Tapes and Procedures       4-3         4-18.       Test Sequence       4-3         4-19.       Error Halts       4-3         4-20.       Procedures for Loading Diagnostic Tapes       4-5         4-22.       Loading Diagnostic Tapes Using the HP 2748A Tape Reader       4-5         4-23.       Loading Diagnostic Tapes with the HP 2758A Reader-Reroller       4-6         4-24.       Loading Diagnostic Tapes Using the HP 2752A Teleprinter       4-7         4-25.       Loading Halts       4-8         4-26.       Maintenance Features       4-8         4-28.       Basic Troubleshooting Procedures       4-9         4-30.       Overall Computer Servicing Diagram       4-9         4-31.       Central Processor Servicing       4-9         4-34.       Central Processor Timing Specifications       4-9         4-34.       Central Processor Timing Specifications       4-9         4-36.       ROM Microprogram Servicing Data       4-28         4-41.       Set Phase Logic       4-30         4-43.       Phase 1A       4-30         4-45.       Phase 1B       4-33         4-47.       Phase 2       4-34         4-50.       Memory Refer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |                                      |                                                                                                                     |                          |