# HK68/V2E User's Manual

HK68/V2E USER'S MANUAL

001M528

REVISION A October 1989

Heurikon Corporation

•

•

## **P**REFACE

The purpose of this manual is to document the features of the Heurikon HK68/V2E<sup>™</sup> microcomputer board.

This manual covers the unique features of the HK68/V2E board. Although general information, such as MPU, SCSI, CIO, and SCC programming is discussed, more detailed information is available directly from the chip manufacturers.

Feel free to contact Heurikon Corporation's Customer Support Department if you have questions. We are prepared to answer general questions as well as providing help with specific applications.

The information in the manual has been checked and is believed to be accurate and reliable. HOWEVER, NO RESPONSIBILITY IS ASSUMED BY HEURIKON FOR ITS USE OR FOR ANY INACCURACIES. Specifications are subject to change without notice. HEURIKON DOES NOT ASSUME ANY LIABILITY ARISING OUT OF USE OR OTHER APPLICATION OF ANY PRODUCT, CIRCUIT OR PROGRAM DESCRIVED HEREIN. This document does no convey any license under Heurikon's patents or the righs of others.

HK68, HK68/V2E and Hbug are trademarks of Heurikon Corporation

UNIX is a trademark of AT&T Bell Laboratories.

VMEbus is a trademark of Motorola.

. .

# TABLE OF CONTENTS

|     |         | An Overview of the HK68/V2E         |     |

|-----|---------|-------------------------------------|-----|

| 1.1 |         | re Summary                          |     |

| 1.2 | Block   | Diagram                             | 1-3 |

| Cha | pter 2  | Getting Going                       |     |

| 2.1 | Install | lation Steps                        | 2-1 |

| 2.2 | Troub   | leshooting and Service Information  | 2-2 |

| 2.3 | Monit   | or Summary                          | 2-3 |

| Cha | pter 3  | MPU Summary Information             |     |

| 3.1 |         | luction                             |     |

| 3.2 |         | Interrupts                          |     |

| 3.3 |         | Exception Vectors                   |     |

| 3.4 |         | LEDs                                |     |

| 3.5 |         | ol Panel Interface/MPU Status       |     |

| 3.6 |         | Cache Control                       |     |

| 3.7 |         | Cessors                             |     |

|     | 1       |                                     |     |

|     |         | Floating Point Coprocessor (FPP)    |     |

| 4.1 | FPP Fe  | eature summary                      | 4-1 |

| 4.2 | FPP B   | ypass                               | 4-2 |

| Cha |         |                                     |     |

|     |         | System Error Handling               |     |

| 5.1 | Error   | Conditions                          | 5-1 |

| Cha | pter 6  | <b>On-card Memory Configuration</b> |     |

| 6.1 |         | ory Configuration                   | 6-1 |

| 6.2 | ROM     |                                     | 6-1 |

| 6.3 | On-car  | rd RAM                              | 6-3 |

| 6.4 | On-car  | rd Memory Sizing                    | 6-4 |

| 6.5 |         | lemory                              |     |

| 6.6 | Physic  | cal Memory Map                      | 6-5 |

| 6.7 | Memo    | bry Timing                          | 6-6 |

| 6.8 | Non-V   | /olatile RĂM                        | 6-6 |

| Cha | oter 7  | VMEbus Control                      |     |

|     |         | uction                              | 7-1 |

|     |         | ontrol Signals                      |     |

| / • 1 | Ind Odde dollarssission and the second | /-1 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.2   | Bus Control Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

|       | VMEbus, P1 Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|       | VSB, P2 Descriptions - VME Subsystem Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 7.3   | Bus Arbitration and Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7-7 |

| 7.4   | Accesses FROM the VMEbus (Slave mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7-8 |

| 7.5   | VME Bus Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

|       | Interrupter Module Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| 7.5.2 | Interrupt Handler Operation    | <b>7-1</b> 5 |

|-------|--------------------------------|--------------|

| 7.6   | SYSFAIL Control                | 7-16         |

| 7.7   | Bus Addressing (Master Mode)   |              |

|       | Mailbox Interface              |              |

| 7.9   | VSB Interface                  |              |

| 7.10  | Watchdog and Bus Timer         | 7-20         |

|       | Relevant Jumpers - Bus Control |              |

#### Chapter 8 Miscellaneous Devices

### Chapter 9 CIO Usage

| 9.1 | Introduction                   | 9-1 |

|-----|--------------------------------|-----|

| 9.2 | Port A Bit Definition          |     |

| 9.3 | Port B Bit Definition          |     |

| 9.4 | Port C Bit Definition          |     |

| 9.5 | Counter/Timers                 | 9-2 |

| 9.6 | Register Address Summary (CIO) |     |

| 9.7 | CIO Initialization             |     |

| 9.8 | CIO Programming Hints          |     |

#### Chapter 10 Serial I/O

| Introduction                       | 10-1                                                                                                                                                                                                                                                                   |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |                                                                                                                                                                                                                                                                        |

| RS-232 Pinouts                     | 10-1                                                                                                                                                                                                                                                                   |

| Signal Naming Conventions (RS-232) | 10-3                                                                                                                                                                                                                                                                   |

| Connector Conventions              | 10-5                                                                                                                                                                                                                                                                   |

| SCC Initialization Sequence        | 10-5                                                                                                                                                                                                                                                                   |

|                                    |                                                                                                                                                                                                                                                                        |

| Baud Rate Constants                | 10-7                                                                                                                                                                                                                                                                   |

| RS-422 Operation                   | 10-8                                                                                                                                                                                                                                                                   |

| Relevant Jumpers (Serial I/O)      | 10-9                                                                                                                                                                                                                                                                   |

|                                    |                                                                                                                                                                                                                                                                        |

|                                    | Introduction.<br>RS-232 Pinouts.<br>Signal Naming Conventions (RS-232).<br>Connector Conventions.<br>SCC Initialization Sequence.<br>Port Address Summary.<br>Baud Rate Constants.<br>RS-422 Operation.<br>Relevant Jumpers (Serial I/O).<br>Serial I/O Cable Drawing. |

#### Chapter 11 SCSI Port

| 11.1 | Introduction                    | 11-1 |

|------|---------------------------------|------|

| 11.2 | SCSI Implementation Notes       |      |

|      | Register Address Summary (SCSI) |      |

|      | SCSI Port Pinouts               |      |

#### Chapter 12 Centronics Port

| 12.1 | Introduction                        | 12-1 |

|------|-------------------------------------|------|

| 12.2 | Centronics Port Configuration       | 12-2 |

|      | Control Port Addresses - Centronics |      |

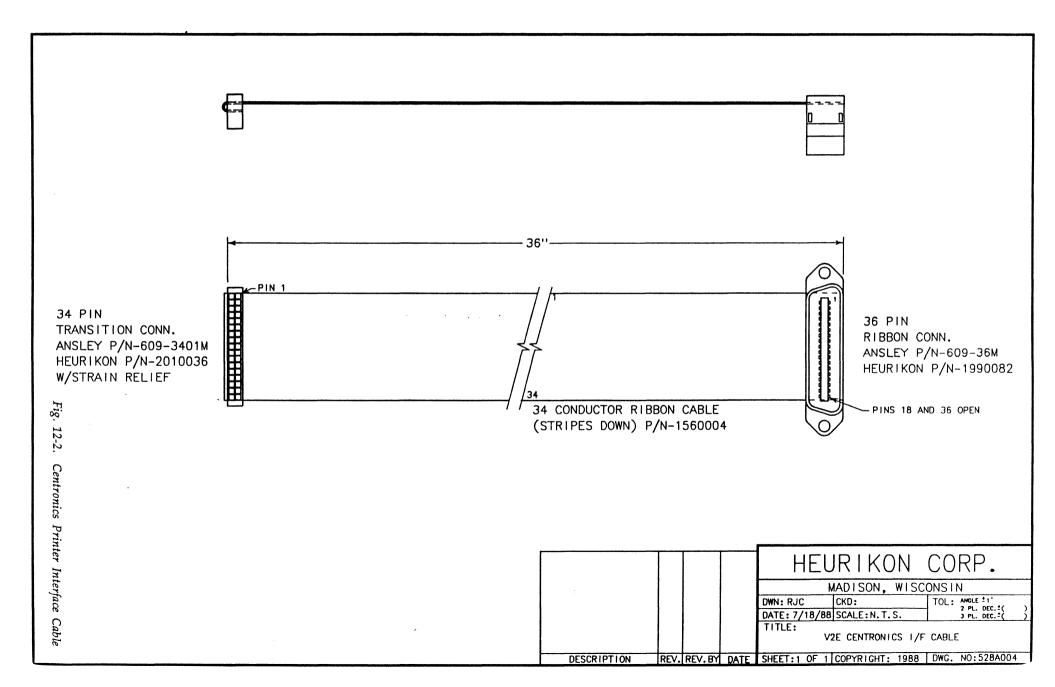

|      | Centronics Printer Interface Cable  |      |

#### Chapter 13 Real-Time Clock (RTC) - Optional Feature

| 13.1 | Introduction | 13- | -1 |

|------|--------------|-----|----|

|      |              |     |    |

### Chapter 14 VMEbus Interface

| 14.1 | Introduction                | <b>14-</b> 1 |

|------|-----------------------------|--------------|

| 14.2 | P1 (VMEbus) Pin Assignments | 14-2         |

|      | P2 (VSB) Pin Assignments    |              |

|      | Power Requirements          |              |

| 14.5 | .Environmental              |              |

| 14.6 | Mechanical Specifications   | 14-5         |

### Chapter 15 Summary Information

| 15.1 | Software Initialization Summary15- | 1 |

|------|------------------------------------|---|

|      | On-Card I/O Addresses              |   |

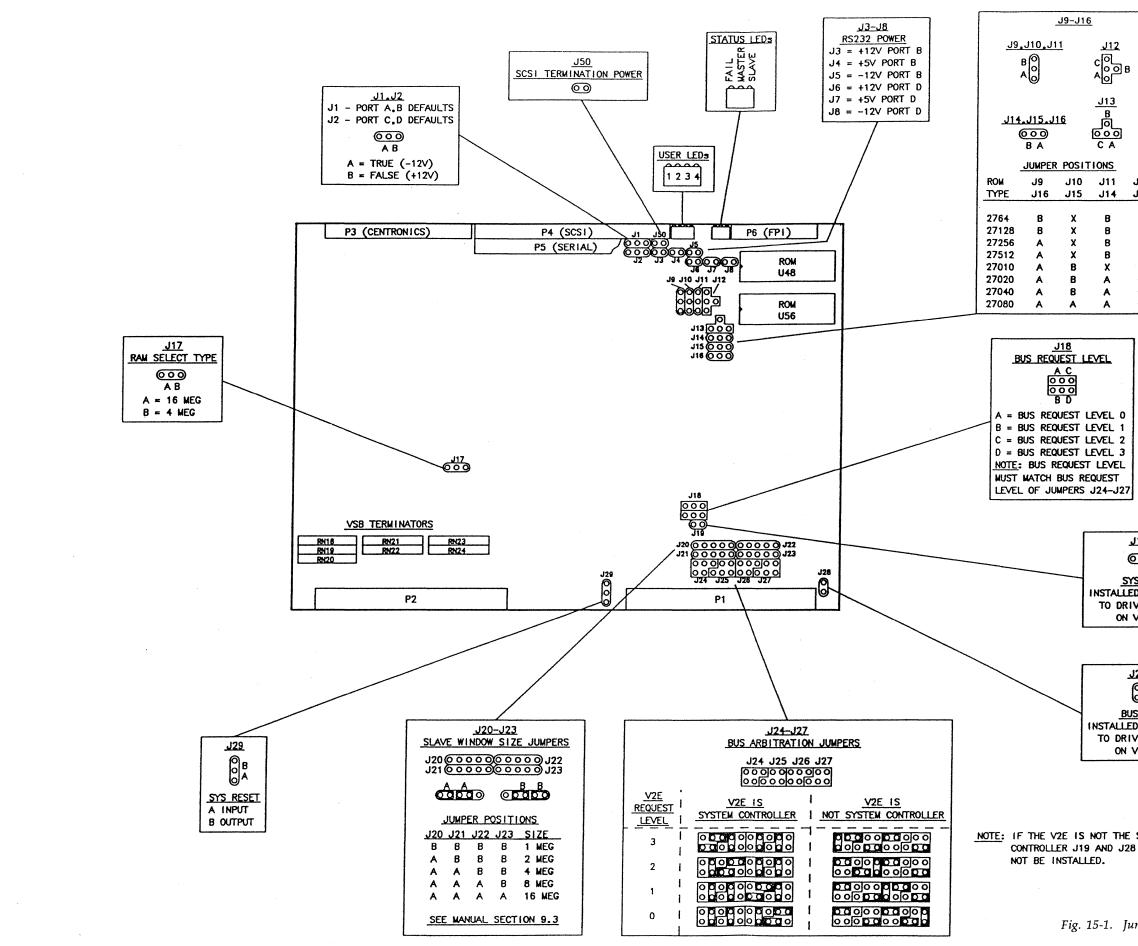

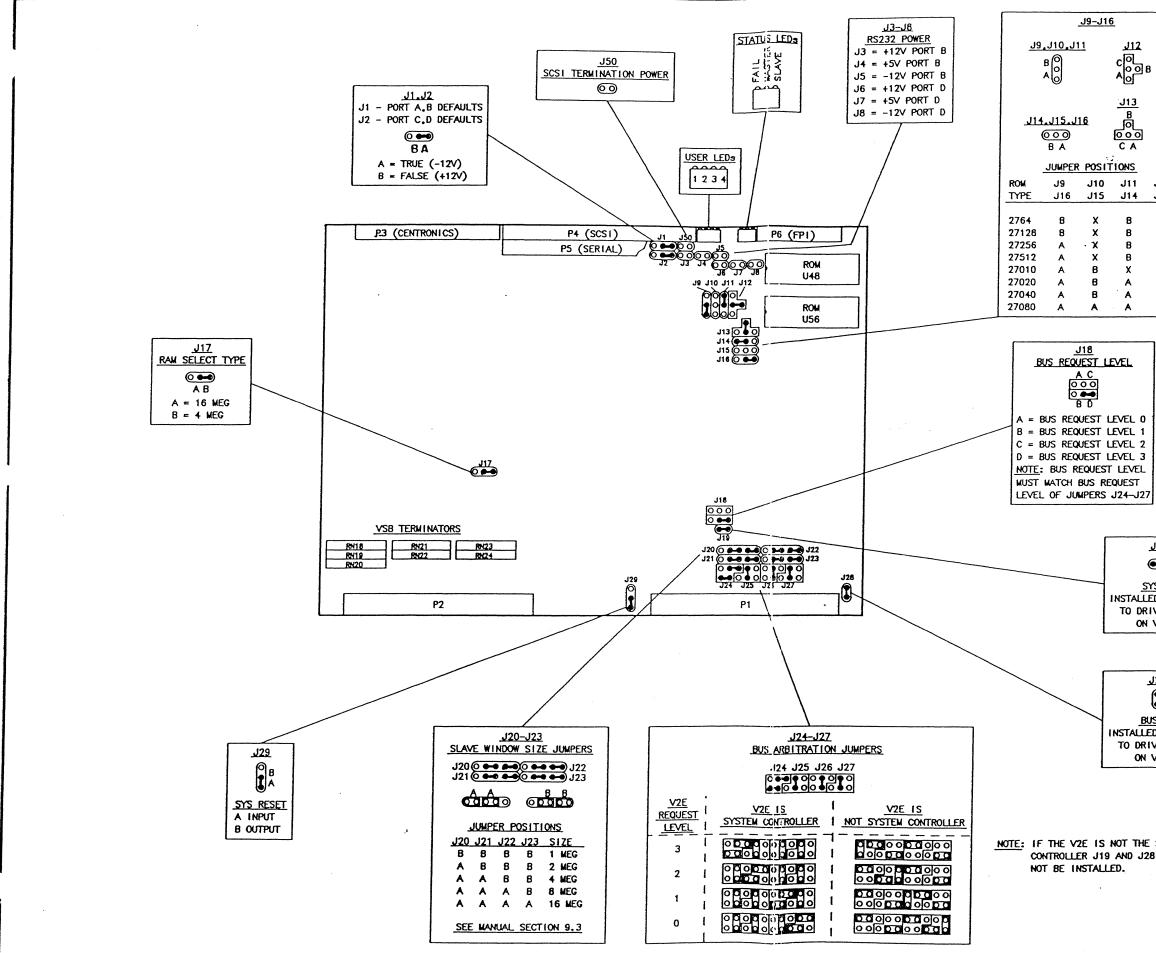

| 15.3 | Hardware Configuration Jumpers15-  | 4 |

|      | Additional Technical Literature15- |   |

#### Tables

| Table 3-1   | MPU Interrupt Levels                    |

|-------------|-----------------------------------------|

| Table 3-2   | MPU Exception Vectors                   |

| Table 3-3   | Suggested Interrupt Vectors             |

| Table 3-4   | Device Interrupt Vector Values          |

| Table 3-5   | Status LEDs                             |

| Table 3-6   | Control Panel Interface (P6)            |

| Table 3-7   | Control Panel Interface (P6)            |

| Table 3-8   | MPU Cache Control                       |

| Table 6-1   | ROM Address Summary6-1                  |

| Table 6-2   | ROM Capacity and Jumper Positions       |

| Table 6-3   | On-card RAM Capacity6-4                 |

| Table 6-4   | Non-Volatile RAM Addresses6-6           |

| Table 6-5   | NV-RAM Contents (partial)6-7            |

| Table 7-1   | System Controller Functions7-7          |

| Table 7-2   | Bus Control Bits7-8                     |

| Table 7-3   | Slave Mode Control7-9                   |

| Table 7-4   | Slave Mode Control7-9                   |

| Table 7-5   | Bus Control Latch (VME slave logic)7-11 |

| Table 7-6   | Slave Address Modifiers7-12             |

| Table 7-7   | VMEbus Interrupter Addresses            |

| Table 7-8   | Interrupt Acknowledge Port Summary      |

| Table 7-9   | VMEbus Regions7-17                      |

| Table 7-10  | Mailbox Control7-18                     |

| Table 7-11  | Mailbox Functions7-18                   |

| Table 7-12  | VSB Terminations7-19                    |

| Table 7-13  | VSB Control7-19                         |

| Table 7-14  | VSB Release Modes7-20                   |

| Table 7-15  | Bus Control Jumpers7-21                 |

| Table 8-1   | User LEDs - Addresses8-1                |

| Table 9-1   | CIO Port A Bit Definitions9-1           |

| Table 9-2   | CIO Port B Bit Definitions9-2           |

| Table 9-3   | CIO Port C Bit Definitions9-2           |

| Table 9-4   | CIO Register Addresses9-3               |

| Table 10-1a | Serial Port Pinouts (P5) - Port A10-1   |

| Table 10-1c | Serial Port Pinouts (P5) - Port B10-2   |

| Table 10-1c | Serial Port Pinouts (P5) - Port C10-2   |

| Table 10-1d | Serial Port Pinouts (P5) - Port D10-3   |

| Table 10-2  | Signal Naming Conventions10-4           |

| Table 10-3 | RS-232 Cable Reversal             | 10-4 |

|------------|-----------------------------------|------|

| Table 10-4 | SCC Initialization Sequence       |      |

| Table 10-5 | SCC Register Addresses            | 10-7 |

| Table 10-6 | Baud Rate Constants               |      |

| Table 10-7 | RS-422 Header Wiring              | 10-8 |

| Table 10-8 | Relevant Jumpers - Serial I/O     |      |

| Table 11-1 | SCSI Register Address Summary     |      |

| Table 11-2 | SCSI Pinouts                      |      |

| Table 12-1 | Centronics Pinout (Connector P3)  | 12-2 |

| Table 12-2 | Centronics Control Addresses      | 12-3 |

| Table 12-3 | Centronics Data/Status Addresses  |      |

| Table 13-1 | RTC module, physical effects      | 13-1 |

| Table 14-1 | P1 (VMEbus) Connector Pinout      |      |

| Table 14-2 | P2 (VMEbus, VSB) Connector Pinout | 14-4 |

| Table 14-3 | Power Requirements                | 14-5 |

| Table 14-4 | Mechanical Specifications         |      |

| Table 15-1 | Address Summary                   |      |

| Table 15-2 | Jumper Summary                    |      |

| Table 15-3 | Additional Technical Literature   |      |

### Figures

| Fig. 1-1  | HK68/V2E Block Diagram                 | 1-3    |

|-----------|----------------------------------------|--------|

| Fig. 6-1  | ROM Positioning Diagram                | 6-3    |

| Fig. 6-2  | Physical Memory Map                    | 6-5    |

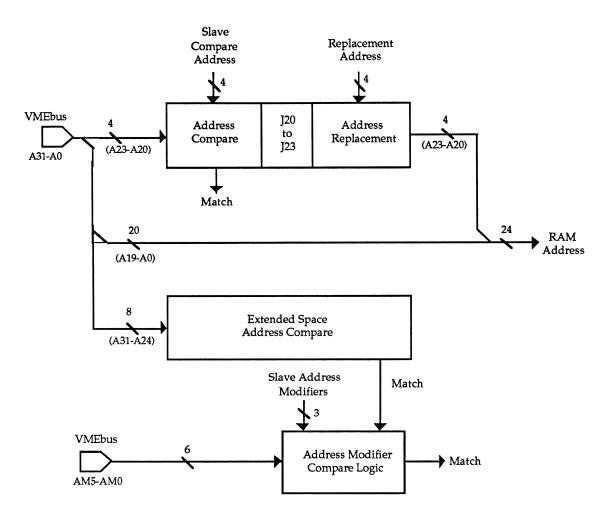

| Fig. 7-2  | Memory Accesses from the VMEbus        | 7-13   |

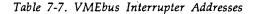

| Fig. 7-3  | Interrupt Signal Routing               | 7-16   |

| Fig. 9-1  | CIO Program Example (C Portion)        | 9-5    |

| Fig. 9-2  | CIO Program Example (Assembly Portion) | 9-5    |

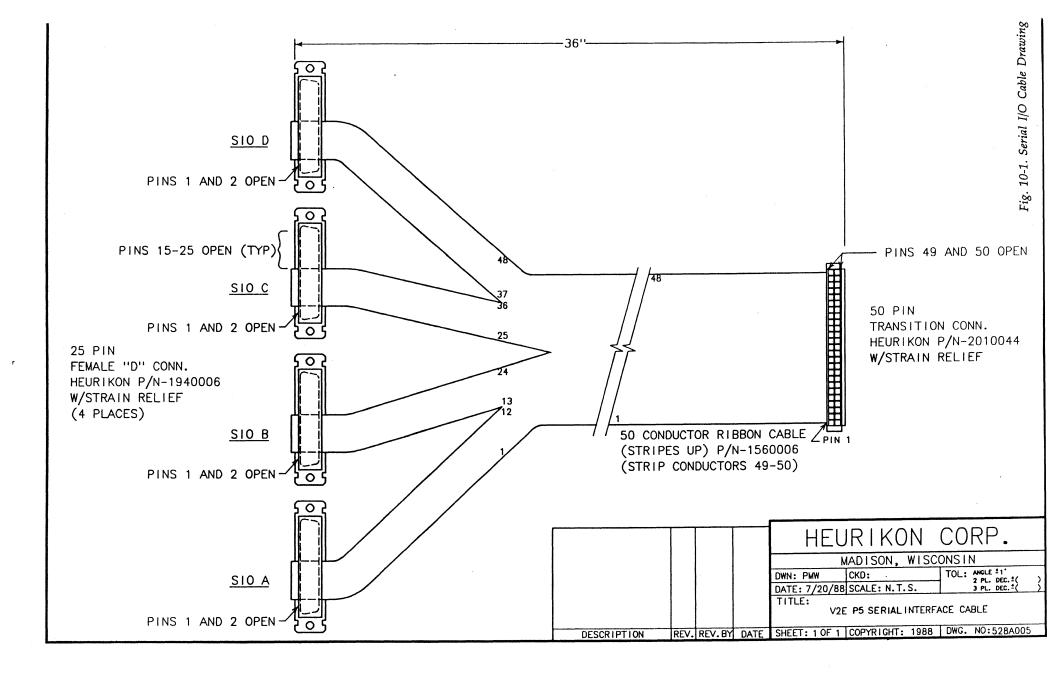

| Fig. 10-1 | Serial I/O Cable Drawing               | 10-10  |

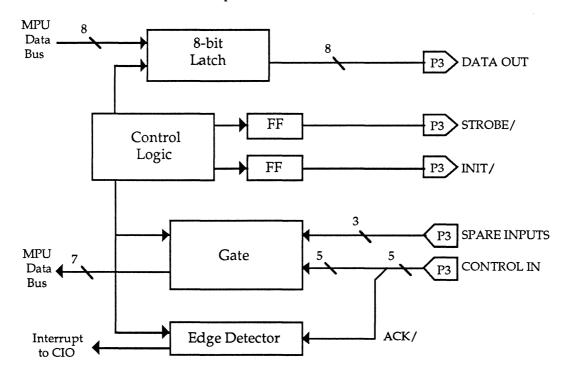

| Fig. 12-1 | Centronics Interface - Block Diagram   | . 12-4 |

| Fig. 12-2 | Centronics Printer Interface Cable     | 12-5   |

| Fig. 13-1 | Real-Time Clock, Example Software      | 13-2   |

| Fig. 15-1 | Jumper Locations                       | 15-5   |

|           |                                        |        |

# AN OVERVIEW OF THE HK68/V2E

1.1 FEATURE SUMMARY

| СРU        | Motorola 68020 microprocessor chip<br>16.67, 20 and 25 Mhz option<br>32-bit internal architecture<br>32-bit address and data paths<br>32 address lines<br>4-gigabyte addressing range<br>256-byte Instruction Cache. (Ref: section 3) |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| FPP        | 68881/68882 Floating Point Co-processor. Uses the IEEE-P754 Binary Floating Point Std. (Ref: section 4)                                                                                                                               |  |

| RAM        | 4 or 16 megabyte capacity<br>One parity bit per byte<br>Uses 1024K x 1 or 4096K x 1 DRAMs. Hardware refresh.<br>(Ref: section 6)                                                                                                      |  |

| EPROM      | Two ROM sockets<br>2 Mbyte total capacity. Page Addressable ROM and<br>EEpROM capability. (Ref: section 6)                                                                                                                            |  |

| VMEbus     | 32-bit addressing (4 gigabyte range)<br>32-bit data bus, compatible with 8-bit boards<br>Seven bus interrupts. (Ref: section 7)                                                                                                       |  |

| VSB        | High speed local memory expansion. Supports sec-<br>ondary bus masters. (Ref: section 7)                                                                                                                                              |  |

| Serial I/O | Four serial I/O ports (two Zilog Z8530 Serial<br>Communication Controllers)<br>Separate baud rate generators for each port<br>Asynchronous and synchronous modes<br>RS-232C interface, RS-422 option. (Ref: section 10)               |  |

- SCSI ANSI X3T9.2 compatible SCSI controller Supports up to 8 disk drive controllers or other devices Synchronous protocol support. (Ref: section 11)

- **Centronics** Control I/F and eight-bit output port for Centronicstype printer. (Ref: section 12)

- LEDs Four user LEDs under software control Three MPU/BUS status LEDs (Ref: section 8)

- CIO Zilog Z8536 Counter/Timer and Parallel I/O Unit; three 16-bit counter/timers Three parallel ports for on-card control functions. (Ref: section 9)

- NV-RAMNonvolatile Static RAM256 x 4 configurationInternal EEpROM100 year retention10,000 store cycle lifetimeFor user definable functions. (Ref: section 6.8)

- Mailbox Allows remote control of the HK68/V2E via specified VMEbus addresses MPU halt, reset, interrupt, and on-card bus lock functions. (Ref: section 7.8)

- RTC Optional Real-Time Clock module for time-of-day maintenance. With battery backup. (Ref: section 13)

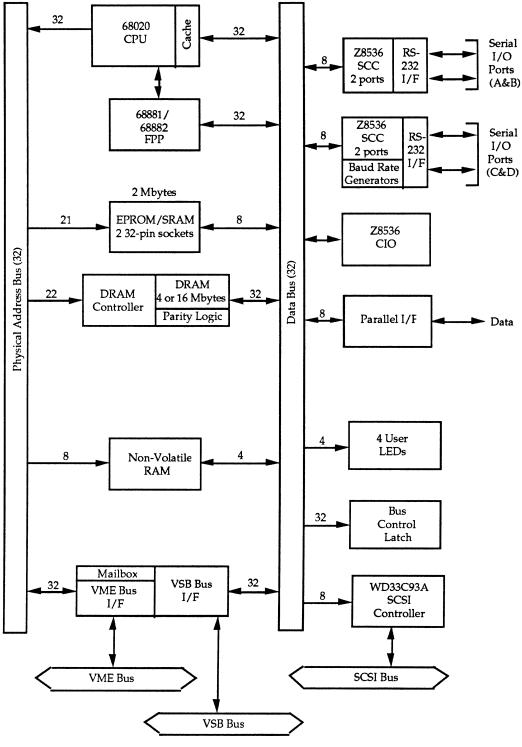

#### 1.2 BLOCK DIAGRAM

Fig. 1-1. HK68/V2E Block Diagram

.

.

## **GETTING GOING**

2.1 INSTALLATION STEPS

Here is what you need to get the Heurikon HK68/V2E "on-theair":

- 1. Heurikon HK68/V2E Microcomputer board

- 2. Card cage and power supply

- 3. Serial I/F cable (RS-232)

- 4. CRT Terminal

- 5. Heurikon Hbug monitor and bootstrap EpROM

CAUTION: All semiconductors should be handled with care. Static discharges can easily damage the components on the HK68/V2E. Keep the board in an anti-static bag whenever it is out of the system chassis and *do not handle the board* unless absolutely necessary. Ground your body before touching the HK68/V2E board.

CAUTION: High operating temperatures will cause unpredictable operation. Because of the high chip density, fan cooling is required for most configurations, even when cards are placed on extenders.

All products are fully tested before they are shipped from the factory. When you receive your HK68/V2E, follow these steps to assure yourself that the system is operational:

1. Visually inspect the board(s) for loose components which could be the result of shipping vibrations. Visually inspect the chassis and all cables. Be sure all boards are seated properly in the card cage. Be sure all cables are securely in place.

- 2. Connect a CRT terminal to Serial Port B, via connector P5. If you are making your own cables, refer to section 12. Set the terminal as follows:

- 9600 baud, full duplex.

- Eight data bits (no parity).

- Two stop bits for transmit data.

- One stop bit for receive data.

- If your terminal does not have separate controls for transmit and receive stop bits, select one stop bit for both transmit and receive.

- 3. Connect AC power and turn the system on.

- 4. Push the system RESET button. A sign-on message and prompt from the monitor should appear on the screen. If not, check your power supply voltages and CRT cabling.

- 5. Now is the time to read the monitor manual and the operating system literature. Short course: To boot the operating system, insert a diskette and enter 'bf' (for boot floppy) or 'bw' (to boot from Winchester.)

- 6. Reconfigure the jumpers, etc, as necessary for your application. See section 15 for a summary of I/O device addresses and configuration jumpers.

2.2 TROUBLESHOOTING AND SERVICE INFORMATION

In case of difficulty, use this checklist:

- 1. Be sure the system is not overheating.

- 2. Inspect the power cables and connectors. If the HK68/V2E board has power, at least one of the four user LEDs (near the Reset button) should be on.

- 3. If the Hbug monitor program is executing, run the diagnostics, via command 'uc' or 'um'.

- 4. Check your power supply for proper DC voltages. If possible, look for excessive power supply ripple or noise using an oscilloscope. Note that the use of P2 is required to meet the power specifications.

- 5. Check the chips to be sure they are firmly in place. Look for chips with bent or broken pins. In particular, check the EPROM.

- 7. Check the jumpers to be sure your board is configured properly. All jumpers should be in the "standard configuration" positions shown in section 17.3.

- 8. After you have checked all of the above items, call our Customer Service Department for help. Please have the following information handy:

- The state of the user and status LEDs (near the Reset button).

- The monitor program revision level (part of sign-on message).

- The HK68/V2E p.c.b. serial number (scribed along card edge).

- The complete HK68/V2E model number, including option codes.

- The serial number of the Operating System.

If you plan to return the board to Heurikon for service, contact our Customer Service Department to obtain a *Return Merchandise Authorization* (RMA) number. Be prepared to provide the items listed above, plus your Purchase Order number and billing information if your HK68/V2E is out of warranty. If you return the board, be sure to enclose it in the anti-static bag, such as the one in which it was originally shipped. Send it prepaid to:

> Heurikon Corporation Factory Service Department 8310 Excelsior Drive Madison, WI 53717

Please put the RMA number on the package so we can handle your problem most efficiently.

#### 2.3 MONITOR SUMMARY

The HK68/V2E monitor and bootstrap program, Hbug, is contained in one EPROM. It is intended to provide a fundamental ability to check the memory and I/O devices, to manually enter a program and to down-line load or bootstrap a larger program into memory. Advanced features and utilities may be loaded from media or via an operating system.

Refer to the **Hbug User's Manual** for details on the commands and command formats.

. . .

Chapter 3

## **MPU SUMMARY INFORMATION**

3.1 INTRODUCTION

This section details some of the important features of the 68020 MPU chip and, in particular, those items which are specific to the implementation on the Heurikon HK68/V2E.

3.2 MPU INTERRUPTS

The MPU can internally set an interrupt priority level in such a way that interrupts of a lower priority will not be honored. Interrupt level seven, however, cannot be masked off.

| Level | Interrupt (bus) | Interrupt (on-card)                        |  |

|-------|-----------------|--------------------------------------------|--|

| 7     | IRQ7            | Parity error, highest priority,            |  |

|       |                 | non-maskable, autovectored                 |  |

| 6     | IRQ6            | CIO (vectored) (sub-priority:              |  |

|       |                 | timer 3, port A, timer 2, port B, timer 1) |  |

| 5     | IRQ5            | -                                          |  |

| 4     | IRQ4            | SCSI (autovectored)                        |  |

| 3     | IRQ3            | -                                          |  |

| 2     | IRQ2            | SCC (vectored) (sub-priority: port C, D)   |  |

|       |                 | (sub-sub-priority: rcv ready, tx ready,    |  |

|       |                 | status change)                             |  |

| 1     | IRQ1            | VSB Interrupt (autovectored)               |  |

| 0     | -               | Idle, no interrupt                         |  |

Table 3-1. MPU Interrupt Levels

When an interrupt is recognized by the MPU, the current instruction is completed and an interrupt acknowledge sequence is initiated, whose purpose is to acquire an interrupt vector from the interrupting device. The vector number is used to select one of 256 exception vectors located in reserved memory locations (see section 3.3 for a listing.) The exception vector specifies the address of the interrupt service routine.

In case there are two interrupts pending at the same level, the oncard device is serviced before the bus interrupt. The VMEbus interrupts are masked on and off via the CIO. Refer to sections 11 and 9.4.

The SCC and CIO devices on the HK68/V2E are capable of generating more than one vector, depending on the particular condition which caused the interrupt. This significantly reduces the time required to service the interrupt because the program does not have to rigorously test for the interrupt cause. Section 7.5 has more information on the HK68/V2E interrupt logic. The VMEbus interrupts are vectored; the vector is automatically read from the interrupting device.

3.3 MPU Exception Vectors

Exception vectors are memory locations from which the MPU fetches the address of a routine to handle an exception (interrupt). All exception vectors are two words long (four bytes), except for the reset vector which is four words. The listing below shows the vector space as it appears to the Heurikon HK68/V2E MPU. It varies slightly from the 68020 MPU manual listing due to particular implementations on the HK68/V2E board. Refer to the MPU documentation for more details. The vector table normally occupies the first 1024 bytes of RAM, but may be moved to other locations under software control. Unused vector positions may be used for other purposes (e.g., code or data) or point to an error routine.

| Vector | Address<br>Offset | Assignment                                    |

|--------|-------------------|-----------------------------------------------|

| 0      | 000               | Reset: Initial SSP (Supervisor Stack Pointer) |

| 1      | 004               | Reset: Initial PC (Supr Program Counter)      |

| 2      | 008               | Bus Error (Watchdog Timer, MMU Fault)         |

| 3      | 00C               | Address Error                                 |

| 4      | 010               | Illegal Instruction                           |

| 5      | 014               | Divide by Zero                                |

| 6      | 018               | CHK Instruction (register bounds)             |

| 7      | 01C               | TRAPV Instruction (overflow)                  |

| 8      | 020               | Privilege Violation (STOP, RESET, RTE, etc)   |

| 9      | 024               | Trace (Program development tool)              |

| 10     | 028               | Instruction Group 1010 Emulator               |

| 11     | 02C               | Instruction Group 1111 Emulator               |

| 11     | 02C               | FPP Coprocessor not present                   |

| 12     | 030               | (reserved)                                    |

| 13     | 034               | (reserved)                                    |

| 13     | 034               | FPP Coprocessor Protocol Violation            |

| 14     | 038               | Format Error                                  |

| 15     | 03C               | Uninitialized Interrupt                       |

| 16-23  | 040-05F           | (reserved-8)                                  |

| 24     | 060               | Spurious Interrupt, not used                  |

| 25     | 064               | Level 1 autovector, VSB                       |

| 26     | 068               | Level 2 autovector, not used                  |

| 27     | 06C               | Level 3 autovector, not used                  |

| 28     | 070               | Level 4 autovector, SCSI Interrupt            |

| 29     | 074               | Level 5 autovector, not used                  |

| 30     | 078               | Level 6 autovector, not used                  |

| 31     | 07C               | Level 7 autovector, parity error, ACFAIL      |

| 32-47  | 080-0BF           | TRAP Instruction Vectors (16)                 |

| 48-54  | 0C0-0DB           | FPP Exceptions (8)                            |

| 55-63  | 0DC-0FF           | (reserved-8)                                  |

| 64-255 | 100-3FF           | User Interrupt Vectors (192)                  |

Table 3-2. MPU Exception Vectors

Autovectoring is used for the parity error, SCSI and VSB interrupts. Interrupts from all other devices can be programmed to provide a vector number (which would likely point into the "User Interrupt Vector" area, above). VMEbus interrupts (IRQ1 - IRQ7) are vectored; the vector is supplied by the interrupting device over the VMEbus.

The following table gives suggested interrupt vectors for each of the possible (on-card) device interrupts which could occur. Note that the listing is in order of interrupt priority, highest priority first.

| Level | Vector   | Device | Condition                                 |  |

|-------|----------|--------|-------------------------------------------|--|

| 7     | 31       |        | Parity err./ACFAIL autovectored interrupt |  |

| 6     | 96       | CIO    | Timer 3                                   |  |

|       | 79       | CIO    | External Interrupt (P6-11)                |  |

|       | 77       |        | EEpROM 1 Ready                            |  |

|       | 75       |        | EEpROM 0 Ready                            |  |

|       | 73       |        | Mailbox Interrupt                         |  |

|       | 71       |        | SCSI DMA Request                          |  |

|       | 69       |        | VME Interrupt in Progress                 |  |

|       | 67,65    |        | -                                         |  |

|       | 98       | CIO    | Timer 2                                   |  |

|       | 78       | CIO    | Centronics Interrupt                      |  |

|       | 76,74,72 |        | -                                         |  |

|       | 70       |        | -                                         |  |

|       | 68       |        | -                                         |  |

|       | 66       |        | -                                         |  |

|       | 64       |        | -                                         |  |

|       | 100      | CIO    | Timer 1                                   |  |

|       | 102      | CIO    | Timer, error                              |  |

| 4     | 28       | SCSI   | SCSI Interface (autovectored)             |  |

| 2     | 92       | SCC    | Port A, Receive character available       |  |

|       | 94       |        | Port A, Special receive condition         |  |

|       | 88       |        | Port A, Transmit buffer empty             |  |

|       | 90       |        | Port A, External/Status change            |  |

|       | 84       |        | Port B, Receive character available       |  |

|       | 86       |        | Port B, Special receive condition         |  |

|       | 80       |        | Port B, Transmit buffer empty             |  |

|       | 82       |        | Port B, External/Status change            |  |

|       | 93       |        | Port C, Receive character available       |  |

| · ·   | 95       |        | Port C, Special receive condition         |  |

|       | 89       |        | Port C, Transmit buffer empty             |  |

|       | 91       |        | Port C, External/Status change            |  |

|       | 85       |        | Port D, Receive character available       |  |

|       | 87       |        | Port D, Special receive condition         |  |

|       | 81       |        | Port D, Transmit buffer empty             |  |

|       | 83       |        | Port D, External/Status change            |  |

| 1     | 25       | VSB    | VSB IRQ Interrupt (autovectored)          |  |

Table 3-3. Suggested Interrupt Vectors

The suggested interrupt vectors for the CIO and SCC devices take into account that the lower bit and upper four bits of the vectors are shared, e.g., all CIO Port A vectors have five bits which are the same for all interrupt causes.

Each vectored on-card device has interrupt enable and control bits which allow the actual interrupt priority levels to be modified under program control by temporarily disabling certain devices.

Of course, fewer vectors may be used if the devices are programmed not to use modified vectors or if interrupts from some devices are not enabled.

If you want to use the suggested vector numbers in the above table, the proper values to load into the device vector registers are:

| Device               | Hex<br>Value | Decimal<br>Value |

|----------------------|--------------|------------------|

| SCC 1 (Ports A & B): | 0x50         | 80               |

| SCC 2 (Ports C & D): | 0x51         | 81               |

| CIO, Port A:         | 0x41         | 65               |

| CIO, Port B:         | 0x40         | 64               |

| CIO, C/T vector:     | 0x60         | 96               |

Table 3-4. Device Interrupt Vector Values (Suggested)

Making your way through the Zilog CIO and SCC manuals in search of details on the interrupt logic is quite an experience. We suggest you start with these recommended readings from the CIO and SCC technical manuals:

| Device    | Item                                      |

|-----------|-------------------------------------------|

| CIO Z8536 | Technical Manual                          |

|           | Vector register: section 2.10.1           |

|           | Bit priorities: section 3.3.2             |

| SCC Z8530 | Technical Manual                          |

|           | Port priorities: section 3.2.2, table 3-5 |

|           | Vector register: section 4.1.3            |

|           | Vectors: section 4.1.10, table 4-3        |

|           |                                           |

3.4 STATUS LEDS

There are three status LEDs which continuously show the state of the board as shown in Table 3.5:

| LED | Name   | Meaning                                                |

|-----|--------|--------------------------------------------------------|

| L1  | Fail   | The SYSFAIL line is being driven active by this board. |

| L2  | Master | The HK68/V2E is the master on the VMEbus.              |

| L3  | Slave  | The HK68/V2E is a slave on the VMEbus.                 |

Table 3-5. Status LEDs

3.5 CONTROL PANEL INTERFACE/MPU STATUS

There are four status outputs which allow remote monitoring of the HK68/V2E processor. Connections are made through a 14 pin connector, P6.

| P6 pin    | Name | Meaning                                                                                             |

|-----------|------|-----------------------------------------------------------------------------------------------------|

| 2         | Supr | The MPU is in the supervisor state.                                                                 |

| 4         | User | The MPU is in the user state.                                                                       |

| 6         |      | n/c                                                                                                 |

| 8         | Halt | The MPU has halted. (Double bus fault,<br>odd stack address or the system reset line<br>is active.) |

| 10        | Bus  | The HK68/V2E is being accessed as a slave on the VMEbus.                                            |

| 1,3,5,7,9 | Vcc  | Vcc (+5) volts                                                                                      |

Table 3-6. Control Panel Interface (P6)

The output signals are low when true. Each is suitable for connection to a LED cathode. An external resistor must be provided for each output to limit current to 15 milliamps. Two input signals are also provided on P6 for interrupt and reset.

| P6 pin | Name   | Function                                                     |

|--------|--------|--------------------------------------------------------------|

| P6-11  | INTR*  | Connected to CIO bit A7, and pull-up (Refer to section 11.1) |

| P6-12  | Gnd    |                                                              |

| P6-13  | RESET* | When low, causes a local reset                               |

| P6-14  | Gnd    |                                                              |

Table 3-7. Control Panel Interface (P6)

A recommended mating connector for P6 is Molex P/N 15-29-8148.

3.6 MPU CACHE CONTROL

The 68020 cache may be controlled as follows:

| Address   | Function (write-only)                                                          |

|-----------|--------------------------------------------------------------------------------|

| 02B0,0002 | MPU Cache Control<br>D0 = 0, cache disabled (default)<br>D0 = 1, cache enabled |

Table 3-8. MPU Cache Control

The cache control register in the MPU itself must also be set properly to enable the MPU cache.

3.7 COPROCESSORS

The HK68/V2E supports the FPP coprocessor, which is described in more detail in section 4.

Chapter 4

### FLOATING POINT COPROCESSOR (FPP)

#### 4.1 FPP FEATURE SUMMARY

The HK68/V2E allows the use of an optional MC68881 (or 68882) floating point processor chip. It runs as a coprocessor with the MPU.

#### **FPP** Feature Summary

- Allows fully concurrent instruction execution with the main processor.

- Eight general-purpose floating-point data registers, each supporting a full 80-bit extended-precision real data format (a 64-bit mantissa plus a sign bit, and a 15-bit biased exponent).

- A 67-bit ALU to allow very fast calculations, with intermediate precision greater than the extended-precision format.

- A 67-bit barrel shifter for high-speed shifting operations (for normalizing, etc.)

- 46 instruction types, including 35 arithmetic operations.

- Fully conforms to the IEEE P754 standard, including all requirements and suggestions. Also supports functions not defined by the IEEE standard, including a full set of trigonometric and logarithmic functions.

- Supports seven data types: byte, word, and long integers; single, double, and extended-precision real numbers; and packed binary coded decimal string real numbers.

- Efficient mechanisms for procedure calls, context switches, and interrupt handling.

FPP programming details are available in the 68881/68882 technical manual.

#### 4.2 FPP Bypass

The HK68/V2E will operate without the FPP chip. Simply unplug the FPP if it is not required. No wires or jumpers are needed.

If the Watchdog Timer is enabled, the software can determine if the FPP chip is installed. An attempt to access a non-existent FPP will result in a Watchdog timeout and a Bus Error, forcing a Line 1111 MPU Exception, vector number 11.

Chapter 5

## System Error Handling

5.1 ERROR CONDITIONS

There are numerous events which could cause an error to occur. The responses to these events are carefully controlled. The following error conditions may arise during MPU cycles: Condition Meaning **RAM Parity** Incorrect parity was detected during a read cycle from on-card RAM memory. This may be due to a true parity error (RAM data changed,) or because the memory location was not initialized prior to the read and it contained garbage. Parity errors generate a level 7 autovector interrupt. A pointer to the parity error handling routine should be loaded at Vector Base Register offset 00007C. Parity checking cannot be disabled. Watchdog Timeout During an access, usually to the bus, no acknowledge was received within a fixed time interval defined by a hardware timer. (about 100 microseconds.) This is usually the result of no bus device being assigned to the specified address. A timeout could also occur if an access from the bus is not terminated by the bus master. For an access *to* the bus, the memory cycle is terminated, the BERR (Bus Error) exception is taken by the MPU and execution resumes at the location specified by the exception vector.

If an access *from* the bus was in progress, no BERR exception occurs.

Double Bus Fault Another bus error occurred during the processing of a previous bus error, address error or reset exception. This error is the result of a major software bug or a hardware malfunction. A typical software bug which could cause this error would be an improperly initialized stack pointer, which points to an invalid address.

A double bus fault forces the MPU to enter the *HALT* state. Processing stops. The HALT status LED will come on. The only way out of this condition is to issue a hardware reset.

**Divide by Zero** The value of the divisor for a divide instruction is zero. The instruction is aborted and *vector 5* is used to transfer to an error routine.

PrivilegedViolationA program executing in the user state at-<br/>tempted to execute a privileged instruction.<br/>The instruction is not executed. Exception<br/>vector 8 is used to transfer control.

Address Error An odd address has been specified for an instruction. The bus cycle is aborted and *vector* 3 is used to transfer control.

Illegal Instruction The bit pattern for the fetched instruction is not legal or is unimplemented. The instruction is not executed. Exception vector 4, 10 or 11 is used to transfer control.

Format Error The format of the stack frame is not correct for an RTE instruction. The instruction is aborted and exception *vector* 14 is used to transfer control.

Line 1111

Emulator The FPP or PMMU Coprocessor is not present and a coprocessor instruction was fetched. The instruction is not executed. Exception *vector 11* will be taken. **FPP Exceptions** The FPP Coprocessor has detected a data processing error, such as an overflow or a divide by zero. The FPP causes the MPU to take one of eight exceptions in the range of 48 to 54.

. . . -

Chapter 6

## **ON-CARD MEMORY CONFIGURATION**

6.1 INTRODUCTION

The Heurikon HK68/V2E microcomputer will accommodate a variety of RAM and ROM configurations. There are two ROM sockets for pROM, page addressable ROM or EEpROM, 36 ZIP RAM positions, and a nonvolatile RAM. Off-card memory may be accessed via the VMEbus or the VSB.

6.2 ROM

Each ROM occupies a fixed 4-megabyte physical address space. At power-on, the MPU fetches the reset vector from the first eight locations of ROM 0 (chip position U48). The reset vector specifies the initial program counter and status register values. ROM access time must be 435 nsec or less.

| Base Address | ROM | Chip |

|--------------|-----|------|

| 0000,0000    | 0   | U48  |

| 0040,0000    | 1   | U56  |

Table 6-1. ROM Address Summary

There are four jumpers for each ROM position which must be set according to the ROM type being used. If more than one ROM is used, they do not have to be of the same type.

| PROM<br>Type       | ROM<br>Capacity | Total Board<br>Capacity | Jump<br>J12/J13 | per Positior<br>J11/J14 | is (U48/U56<br>J10/J15 | 5)<br>J9/J16 |

|--------------------|-----------------|-------------------------|-----------------|-------------------------|------------------------|--------------|

| 2764               | 8 Kbytes        | 16 Kbytes               | С               | В                       | x                      | В            |

| 27128              | 16 Kbytes       | 32 Kbytes               | С               | В                       | x                      | В            |

| 27256              | 32 Kbytes       | 64 Kbytes               | С               | В                       | ×                      | A            |

| 27512              | 64 Kbytes       | 128 Kbytes              | В               | В                       | x                      | Α            |

| 27010              | 128 Kbytes      | 256 Kbytes              | В               | x                       | В                      | Α            |

| 27020              | 256 Kbytes      | 512 Kbytes              | В               | A                       | В                      | A            |

| 27040              | 512 Kbytes      | 1 Meg                   | В               | А                       | В                      | A            |

| 27080              | 1 Meg           | 2 Meg                   | В               | Α                       | А                      | Α            |

| 27513<br>Paged     | 64 Kbytes       | 128 Kbytes              | С               | В                       | x                      | <b>B</b>     |

| 2864 R/W<br>EEpROM | 8 Kbytes        | 16 Kbytes               | x               | В                       | x                      | В            |

| 2817 R/W<br>EEpROM | 2 Kbytes        | 4 Kbytes                | А               | В                       | x                      | В            |

Table 6-2. ROM Capacity and Jumper Positions

Jumpers J9, J10, J11 and J12 are for ROM 0 (U48); J13, J14, J15 and J16 control ROM 1 (U56). See section 15.3 for help in locating the jumper locations.

Each ROM contains consecutive (both even and odd) addresses. When programming pROMs, do not split even and odd bytes between the two chips.

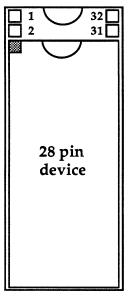

Both ROM sockets are 32 pins. When using a 28 pin device, justify it so socket pins 1, 2, 31 and 32 are empty. Twenty four pin devices are not supported. The ROM access time must be at most 250 nanoseconds.

32 Pin Socket (U 18 & U19)

With 28 Pin Device

Fig. 6-1. ROM Positioning Diagram

The two ROM positions are not contiguous (although a mirror of the lower ROM will be contiguous with the upper ROM). The best way to create a contiguous image is to copy the contents of both ROMs to contiguous RAM areas.

Electrically Erasable or paged pROMs may be used. An EEpROM allows specific addresses to be changed by writing to the ROM. When writing to the EEpROM, a delay must be provided *by the software* between write operations. For the 2864, this delay is 10 milliseconds. The EEpROM Busy/Ready signals are available at the CIO to facilitate this timing; see section 9.1.

Paged ROMs allow future growth of ROM capacity, without adding address pins. A single device can contain multiple 16K byte pages. A specific page is selected by *writing* the page value to the ROM. For example, to select page three of a 27513, write 0x03 to address 0000,0000.

#### 6.3 ON-CARD RAM

The HK68/V2E uses 36 ZIP RAM packages, each one bit wide. There is one parity bit per byte. Standard memory configurations are four or 16 megabytes. On-card RAM occupies physical addresses starting at 0300,0000.

| RAM Type     | Quantity | Capacity     | J17   |

|--------------|----------|--------------|-------|

| 1Meg x 1 ZIP | 36       | 4 Megabytes  | J17-A |

| 4Meg x 1 ZIP | 36       | 16 Megabytes | J17-B |

Table 6-3. On-card RAM Capacity

6.4 ON-CARD MEMORY SIZING

> The following algorithm can be used to determine the amount of on-card RAM memory installed. This procedure takes advantage of "mirrors" which exist in higher addresses when the on-card physical memory size is less than the logical memory space.

- 1. Clear 16 megabytes of memory starting at location 0300,0000.

- 2. Write 5555 (hex) to location 0300,0000.

- 3. Read a word from 0340,0000. If the value read is 5555 the board has four megabytes of memory installed. If the value is zero, the board has 16 megabytes of memory.

6.5 Bus MEMORY

See section 7 for details concerning the bus interface.

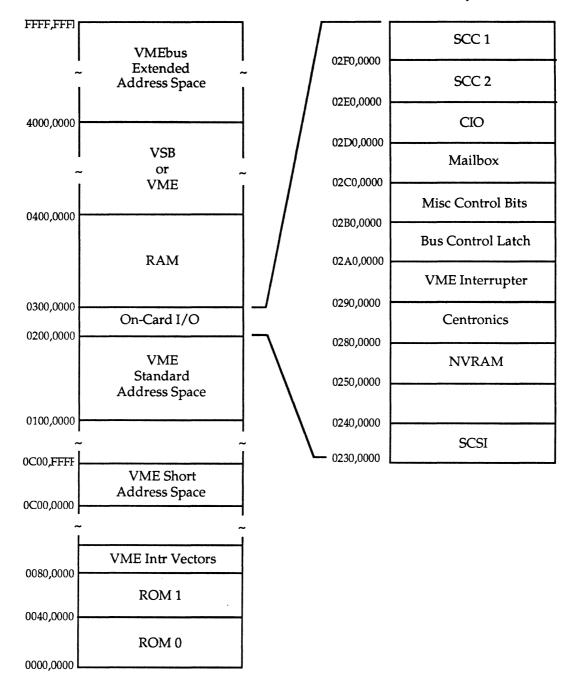

#### 6.6 PHYSICAL MEMORY MAP

See section 15.2 for an I/O device address summary.

Fig. 6-2. Physical Memory Map

#### 6.7 MEMORY TIMING

The information for this section has not been compiled for the HK68/V2E as of this writing. Please consult the factory if you need details.

### 6.8 NON-VOLATILE RAM

A unique feature of the HK68/V2E is its non-volatile RAM (NV-RAM), which allows precious data or system configuration information to be stored and recovered across power cycles. The RAM is configured as 256, four-bit words (low half of a byte). When the MPU reads a byte of data from the NV-RAM, the upper four bits of the value it receives are indeterminate. The NV-RAM is accessible as shown below.

| Address   | Mode  | Function                                                                                                                     |

|-----------|-------|------------------------------------------------------------------------------------------------------------------------------|

| 0250,00xx | R/W   | Read/Write RAM contents (4 bits).                                                                                            |

| 0270,0000 | Read  | Recall RAM contents from Non-volatile memory.                                                                                |

| 0260,0000 | Write | Store RAM contents in Non-volatile memory.<br>The 68020 "tas" (test and set) instruction must<br>be used for this operation. |

Table 6-4. Non-Volatile RAM Addresses

Physically, the NV-RAM (a Xicor X2212 or equivalent) consists of a static RAM overlaid bit-for-bit with a non-volatile EEp-ROM. The store operation takes 10 milliseconds to complete. Recall time is approximately one microsecond. Allowances for those delays should be made in *software*, since the memory hardware does not stop the MPU during the store or recall cycles. The chip is rated for 10,000 store cycles, minimum. During a store operation, only those bits which have been changed are "cycled". The use of a "tas" instruction helps prevent an unintentional store operation by an errant program or a power failure glitch.

At power-up, the shadow RAM contents are indeterminate. Do a recall operation before accessing the NV-RAM for the first time. Recall cycles do not affect the device lifetime.

The HK68/V2E monitor (Hbug) and certain system programs use the NV-RAM. The exact amount reserved for Heurikon usage depends on the system. A major portion of the RAM, however, is available for customer use. Heurikon usage is summarized below (details are available separately):

| Function                                     |  |

|----------------------------------------------|--|

| Magic Number                                 |  |

| Checksum                                     |  |

| Accumulated number of writes                 |  |

| Board type, serial number and revision level |  |

| Hardware configuration information           |  |

| Software configuration information           |  |

| System configuration information             |  |

Table 6-5. NV-RAM Contents (partial)

Chapter 7

### VMEBUS CONTROL

7.1 INTRODUCTION The control logic for the VMEbus allows numerous bus masters to share the resources on the bus. Up to 21 boards may be used on the VMEbus. The VMEbus interface uses 32 Address lines for a total of 4 gigabytes of VMEbus address space, as well as 32 data lines to support 8, 16, 24 or 32-bit data transfers. The "short address" mode, using only 16 address lines, is also supported. In addition, the VSB Expansion Interface is supported, which allows high speed, 32-bit data transfers. There is an INTERRUPTER MODULE as well as an INTERRUPT HANDLER, both of which are capable of utilizing any or all of the seven VMEbus interrupt lines. 7.2 **Bus Control Signals** 7.2.1 VMEBUS, P1 **Descriptions** The following signals on connector P1 and P2 are used for the VMEbus interface. For a complete listing of the pinouts, refer to section 14. ADDRESS bus (bits 1-15). Three-state driven A01-A15 address lines that are used to broadcast a short address. A16-A23 ADDRESS bus (bits 16-23). Three-state driven address lines that are used in conjunction with A01-A15 to broadcast a standard address.

> A24-A31 ADDRESS bus (bits 24-31). Three-state driven address lines that are used in conjunction with A01-A23 to broadcast an extended address.

ACFAIL\* AC FAILURE. An open-collector driven signal which indicates that the AC input to the power supply is no longer being provided or that the required AC input voltage levels are not being met. This signal is connected to MPU interrupt level 7.

AM0-AM5 ADDRESS MODIFIER (bits 0-5). Three-state driven lines that are used to broadcast information such as address size and cycle type. These lines are very similar in usage to the function lines on the MPU.

ADDRESS STROBE. A three-state driven signal that indicates when a valid address has been placed on the address bus.

BUS BUSY. An open-collector driven signal low by the current MASTER to indicate that it is using the bus. When the MASTER releases this line, the resultant rising edge causes the ARBITER to sample the bus request lines and grant the bus to the highest priority requester. Early release mode is supported.

BCLR\* BUS CLEAR. A totem-pole driven signal, generated by an ARBITER to indicate when there is a higher priority request for the bus. This signal requests the current MASTER to release the bus. This signal is an input and an output of the HK68/V2E, associated with J28.

BUS ERROR. An open-collector driven signal generated by a SLAVE or BUS TIMER. This signal indicates to the MASTER that the data transfer was not completed.

BUS GRANT (0-3) IN. Totem-pole driven BG0IN\*-BG3IN\* signals generated by the ARBITER and RE-QUESTERS. "Bus grant in" and "bus grant out" signals form bus grant daisy chains. The "bus grant in" signal indicates, to the board receiving it, that it may use the bus if it wishes to.

> BUS GRANT (0-3) OUT. Totem-pole driven signals generated by REQUESTERS. The bus grant out signal indicates to the next board in the daisy-chain that it may use the bus.

AS\*

**BBSY\***

BERR\*

BG0OUT\*-BG3OUT\*

- **BR0\*-BR3\*** BUS REQUEST (0-3). Open-collector driven signals generated by REQUESTERS. A low level on one of these lines indicates that some MASTER needs to use the bus.

- D00-D31 DATA BUS. Three-state driven bidirectional data lines used to transfer data between MASTERS and SLAVES.

- DS0\*, DS1\* DATA STROBE ZERO, ONE. A three-state driven signal used in conjunction with LWORD\* and A01 to indicate how many data bytes are being transferred (1, 2, 3, or 4). During a write cycle, the falling edge of the first data strobe indicates that valid data is available on the data bus.

- DTACK\* DATA TRANSFER ACKNOWLEDGE. An open-collector driven signal generated by a SLAVE. The falling edge of this signal indicates that valid data is available on the data bus during a read cycle, or that data has been accepted from the data bus during a write cycle. The rising edge indicates when the SLAVE has released the data bus at the end of a READ CYCLE.

- IACK\* INTERRUPT ACKNOWLEDGE. An opencollector or three-state driven signal used by an INTERRUPT HANDLER acknowledging an interrupt request. It is routed, via a backplane signal trace, to the IACKIN\* pin of slot one, where it forms the beginning of the IACKIN\*, IACKOUT\* daisy-chain.

- IACKIN\* INTERRUPT ACKNOWLEDGE IN. A totempole driven signal. The IACKIN\* signal indicates to the VMEbus board receiving it that it is allowed to respond to the INTERRUPT ACKNOWLEDGE CYCLE that is in progress if it so wishes.

- IACKOUT\* INTERRUPT ACKNOWLEDGE OUT. A totem-pole driven signal. The IACKIN\* and IACKOUT\* signals form a daisy-chain. The IACKOUT\* signal is sent by a board to indicate to the next board in the daisy-chain that it is allowed to respond to the INTER-RUPT ACKNOWLEDGE CYCLE that is in progress.

IRQ1\*-IRQ7\* INTERRUPT REQUEST (1-7). Open-collector driven signals, generated by an INTER-RUPTER, which carry interrupt requests. When several lines are monitored by a single INTERRUPT HANDLER the highest numbered line is given the highest priority.

- LWORD\* LONGWORD. A three-state driven signal used in conjunction with DS0\*, DS1\*, and A01 to select which byte location(s) within the 4 byte group are accessed during the data transfer.

- RESERVED RESERVED. A signal line reserved for future VMEbus enhancements. This line must not be used.

- SERCLK SERIAL CLOCK. A totem-pole driven signal which is used to synchronize the data transmission on the VMEbus. Not implemented on the HK68/V2E.

- SERDAT\* SERIAL DATA. An open-collector driven signal which is used for VMEbus data transmission. Not implemented on the HK68/V2E.

- SYSCLK SYSTEM CLOCK. A totem-pole driven signal which provides a constant 16-MHz clock signal that is independent of any other bus timing. This signal is associated with J19.

- SYSFAIL\* SYSTEM FAIL. An open-collector driven signal that indicates that a failure has occurred in the system. Also used at power-on to indicate that at least one VMEbus board is still in its power-on initialization phase. This signal may be generated by any board on the VMEbus. The HK68/V2E drives this line low at power-on. It is released by writing a one to address 02B0,000E.

- SYSRESET\* SYSTEM RESET. An open-collector driven signal which, when low, causes the system to be reset. This signal is associated with jumper J29.

- WRITE\* WRITE. A three-state driven signal generated by the MASTER to indicate whether the data transfer cycle is a read or a write. A high level indicates a read operation; a low level indicates a write operation.

+5V STDBY

+5 Vdc STANDBY. This line supplies +5 Vdc to devices requiring battery backup. Not used on the HK68/V2E.

7.2.2 VSB, P2 DESCRIPTIONS - VME SUBSYSTEM BUS

> The following signals on connector P2 are used for the VSB interface. For a complete listing of the P2 pinouts, refer to section 14. See section 7 for more discussion about the VSB.

- AD00-31 MULTIPLEXED ADDRESSED/DATA LINES. This multiplexed address/data path (32 lines) is controlled by the three-state drivers on the master and slave devices. All lines are active high signals.

- PAS\* VSB ADDRESS STROBE. The falling edge of PAS\* indicates that a valid address is present on AD31-AD00.

- SPACE0-SPACE1 VSB ADDRESS SPACE SELECT. These signals select one of four address spaces or signify an interrupt acknowledge or parallel arbitration cycle. On the HK68/V2E, these signals are not used; they are driven high when the HK68/V2E is the VSB master, which selects the System Address Space.

- DS\* VSB DATA STROBE. The falling edge of DS\* indicates that transfer will occur over AD31-AD00. During write cycles, write data is valid at the falling edge of DS\*.

- WR\* VSB WRITE. WR\*, when low, indicates that a write operation is to be performed and, when high, indicates that a read operation will occur.

- SIZE0,SIZE1 VSB BUS SIZE. These lines, in conjunction with addresses AD00 and AD01, determine the data transfer size and position on the data bus. Lines SIZE0 and SIZE1 are active high signals.

- LOCK\* VSB BUS LOCK. LOCK\*, when low, indicates that the bus is locked and that no other master can obtain possession of the bus. This allows for non-interruptable cycles, such as Read-Modify-Write cycles, to occur from the VSB to a dual ported resource. LOCK\* can also indicate that a block transfer cycle is in progress.

ASACK0\* ASACK1\*

VSB ADDRESS/SIZE ACKNOWLEDGE. The slave device that is selected by address decoding drives at least one ASACK\* signal to control switching the multiplexed address/data bus from address to data. ASACK0\* and ASACK1\* are encoded to indicate to the master the size of the data bus for the slave module to allow dynamic bus sizing.

WAIT\* WAIT\* is gated with AC (Decode Complete) on the master device. The condition AC active and WAIT\* inactive, while PAS\* is asserted, means that no VSB slave module has decoded the address being driven at that time or that there are no VSB slave modules installed. This gives the VSB master the option to switch to the VMEbus when VSB slaves are not responding which allows VSB and VMEbus to share a common address space.

> VSB DECODE COMPLETE. AC is asserted by slave modules to indicate to the master that address decoding has been completed. A slave device allows AC to go high after completing decoding or other conditions (see WAIT\*), regardless of whether the device is selected by the current address on the bus. AC is an active high signal.

> VSB CACHEABLE. CACHE\*, when low, indicates to the master that the selected address location is cacheable. CACHE\* is asserted only by the selected VSB slave module. This signal is not used on the HK68/V2E.

VSB DATA TRANSFER ACKNOWLEDGE. ACK\* is asserted low by the selected slave module to complete the handshake for a transfer operation.

VSB DATA ERROR. ERR\* is asserted low by the selected slave device to indicate a fault condition while attempting the data transfer operation. This would typically be the result of a parity error detected on a slave device.

VSB INTERRUPT REQUEST. IRQ\* when low indicates that a master or slave device is attempting to interrupt another master. On the HK68/V2E, this signal will generate a level 1 autovectored MPU interrupt.

\_\_\_\_\_

7-6

AC

CACHE\*

ACK\*

ERR\*

IRQ\*

.

| BREQ*   | VSB BUS REQUEST. BREQ* is asserted low<br>by a requester whenever bus mastership is re-<br>quired.                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| BGIN*   | VSB BUS GRANT IN. BGIN* is an input to a requester that, when low, indicates to the requester that it has been granted the bus.                   |

| BGOUT*  | VSB BUS GRANT OUT. BGOUT* is asserted<br>low by either an arbiter or a requester to grant<br>the bus to a requester via the BGIN* signal.         |

| BUSY*   | VSB BUS BUSY. BUSY* is asserted low by a requester that has been granted the bus to in-<br>dicate ownership of the bus.                           |

| GA0-GA2 | VSB GEOGRAPHICAL ADDRESSES. These<br>lines are connected to ground on the<br>HK68/V2E; the geographical addressing<br>feature is not implemented. |

7.3 Bus Arbitration and Release

> When the MPU makes a request for VMEbus facilities, the arbitration logic takes over. If necessary, the requesting board enters a wait state until the bus is available (but only for the maximum time allowed by the Watchdog timer).

> Normally, the VMEbus System Controller card provides the system bus clock and access timer, and participates in the arbitration logic. However, a separate System Controller card is *not* needed. The HK68/V2E includes a bus timer and four level (prioritized) VME bus arbiter logic, enabled via jumpers. The following table details the System Controller functions provided by the HK68/V2E.

| Function                 | Setting        |

|--------------------------|----------------|

| System Clock (SYSCLK*)   | J19 (install)  |

| System Reset (SYSRESET*) | J29-B (output) |