# UNCLASSIFIED

# AD 297 312

Reproduced by the

ARMED SERVICES TECHNICAL INFORMATION AGENCY

ARLINGTON HALL STATION

ARLINGTON 12, VIRGINIA

THE ORIGINAL PRINTING OF THIS DOCUMENT CONTAINED COLOR WHICH ASTIA CAN ONLY REPRODUCE IN BLACK AND WHITE

UNCLASSIFIED

NOTICE: When government or other drawings, specifications or other data are used for any purpose other than in connection with a definitely related government procurement operation, the U. S. Government thereby incurs no responsibility, nor any obligation whatsoever; and the fact that the Government may have formulated, furnished, or in any way supplied the said drawings, specifications, or other data is not to be regarded by implication or otherwise as in any manner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture, use or sell any patented invention that may in any way be related thereto.

ゾシ

#### 473L DPSS/ICSS INTERFACE DESCRIPTION

# TECHNICAL DOCUMENTARY REPORT NO. ESD-TDR-63-160 DECEMBER 1962

C.B. Brown

ELECTRONIC SYSTEMS DIVISION

AIR FORCE SYSTEMS COMMAND

UNITED STATES AIR FORCE

L.G. Hanscom Field, Bedford, Massachusetts

Project 473

(Prepared under Contract No. AF 33(600)-39852 by the MITRE Corporation, Bedford, Massachusetts.)

Technical Memorandum TM - 3511

Sheet 1 of 50 Sheets

Centract No. AF33 (600) 39852

SUBJECT:

TO:

FROM:

DEPT.:

DATE:

APPROVED:

473L DPSS/ICSS INTERFACE DESCRIPTION (U) (Project 473)

Distribution List

C. B. Brown

D-25

4 December 1962

1 11/10/0

P. R. Vance

MITRE

Bedford, Massachusetts

ISSUED AT: Bedford, Massachasett

This Technical Memorandum is prepared for Corporation use and for controlled external distribution. Reproduction or further dissemination is not authorized. It has not been reviewed by Office of Security Review, Department of Defense, and therefore is not for public release.

#### ABSTRACT

This document contains material generated at meetings of the 473L Subsystem Integration Design Group (SIDG). Technical material presented herein does not constitute a specification but represents a generally concurred on description of the interface between the 473L Data Processor (AN/FYQ-11) and the System Integrated Consoles (AN/FYA-2, 3, and 4.).

#### TNDEX

#### 1.0 INTRODUCTION

- 1.1 General Description of DPSS/ICSS Interface

- ET AND CONTROL FUNCTION INTERFACE

- 2.1 Data Transmission Rate

- 2.2 Message Formats

- 2.2.1 ET Message Formats

- 2.2.1.1 Data Processor to Console 2.2.1.2 Console to Data Processor

- 2.2.2 Control Message Formats

- 2.2.2.1 Data Processor to Console

- 2.2.2.2 Console to Data Processor

- 2.3 Transmission Modes

- 2.3.1 Data and Control Lines

- 2.3.2 Normal Output Operation (DP to IC)

- 2.3.3 Normal Input Operation (IC to DP)

- 2.4 Error Considerations

- 2.4.1 Error in Output Operation (DP to IC)

- 2.4.1.1 ET Message Error Operations

- 2.4.1.2 Control Message Error Operations 2.4.1.3 Control Line Error Operations

- 2.4.2 Error in Input Operation (IC to DP)

- 2.4.2.1 Control Line Errors

- 2.5 Summary of Console Key Functions Providing Inputs to the Data Processor Via the ET and Control Interface

- 2.6 Summary of Console Indicators Activated by Outputs from the Data Processor Via the ET and Control Interface

- Character Codes and Symbol Set

- 2.8 Physical and Electrical Interface

- 3.0 MULTI-COLORED DISPLAY INTERFACE (TENTATIVE LARGE PANEL DISPLAY INTERFACE)

- 3.1 Data Transmission Rate

- 3.2 M-C Message Formats

- 3.3 Transmission Mode.

- 3.3.2 Normal Output Operation

- 3.4 Error Considerations

- 3.4.1 Data Transfer Errors

- 3.4.2 Control Line Errors

- 3.5 Character Codes and Symbol Set

- 3.6 Physical and Electrical Interface

- 4.0 HARD COPY ASSEMBLY INTERFACE

#### TM-3511

#### 5.0 CONSOLE PRINTER INTERFACE

- 5.1 Data Transmission Rate

- 5.2 Message Format

- 5.3 Transmission Mode

- 5.3.1 Data and Control Lines

- 5.3.2 Normal Output Operation

- 5.4 Error Consideration

- 5.4.1 Data Transfer Errors

- 5.4.2 Control and Data Line Failures

- 5.4.2.1 Data Line Failures 5.4.2.2 Control Line Failures

- 5.5 Character Codes and Symbol Set

- 5.6 Physical and Electrical Characteristics

- APETADIX A 473L EQUIPMENT CHARACTER SET

- APPENDIX B LIBRASCOPE SPECIFICATION L190 000 832

- LIBRASCOPE SPECIFICATION L190 000 833 APPENDIX C

#### facusTRATIONS

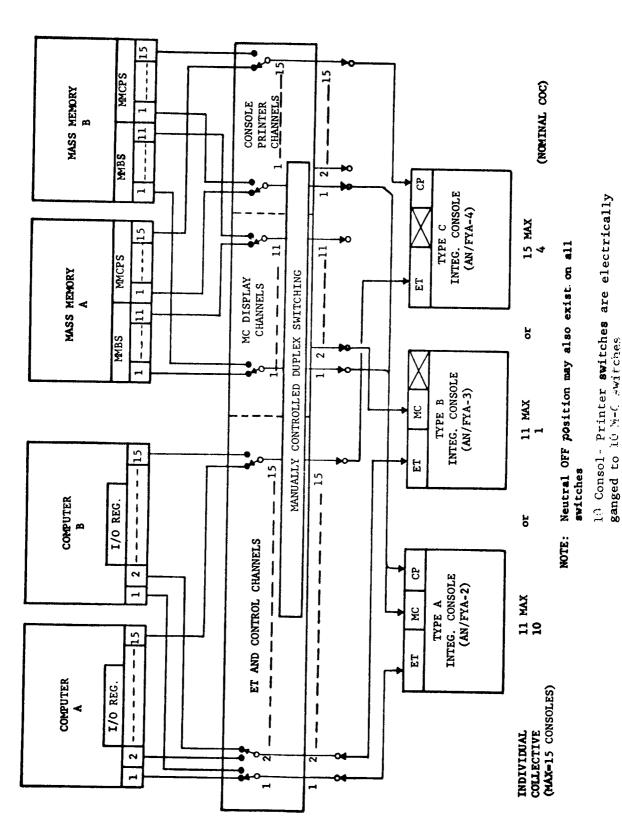

- DPSS/ICSS INTERFACE (SCHEMATIC ONLY) Fig. la

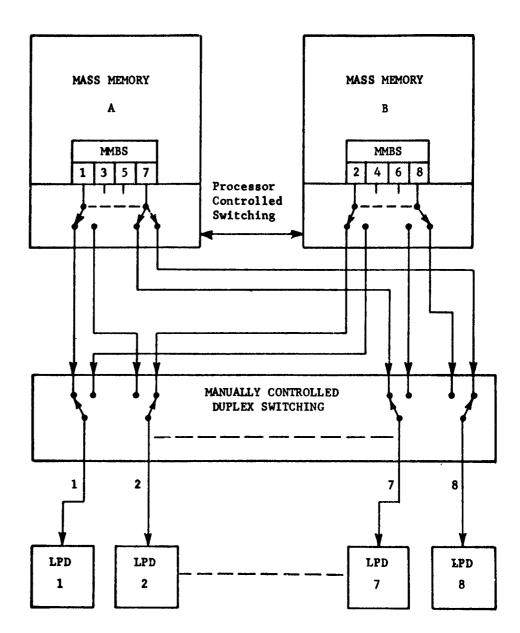

- DPSS/LPD INTERFACE (SCHEMATIC ONLY) Fig. 1b

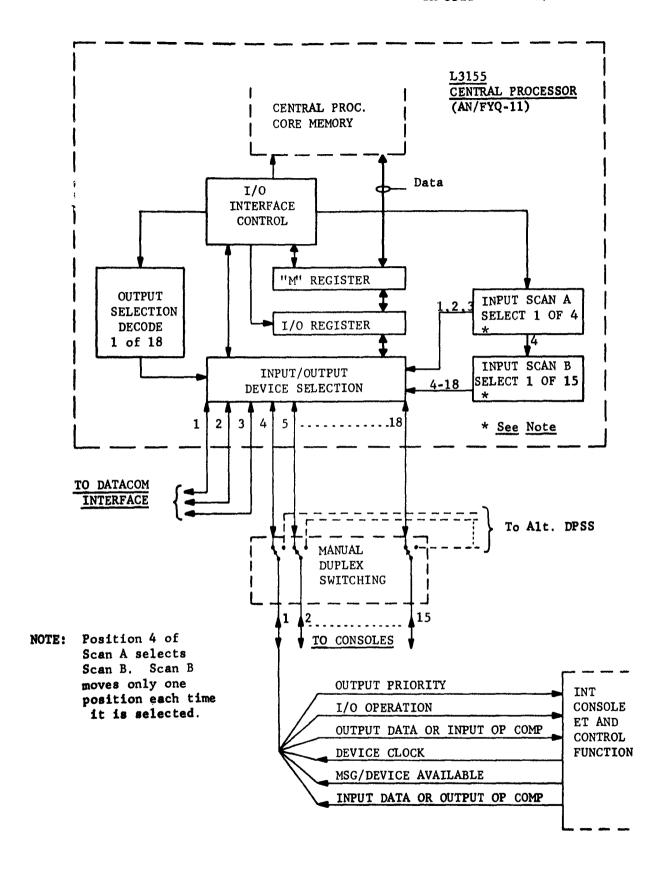

- ET AND CONTROL INPUT/OUTPUT INTERFACE Fig. 2

- Fig. 3 DATA FORMATS - ET/DPSS INTERFACE

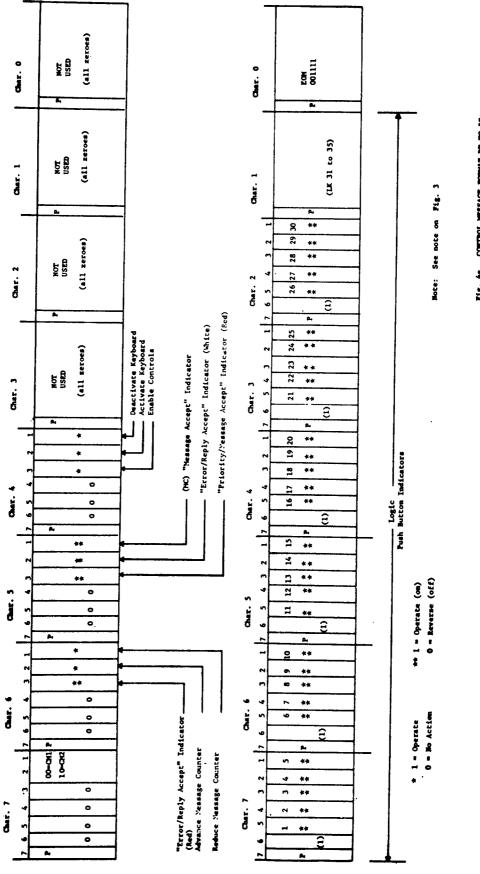

- Fig 4a CONTROL MESSAGE FORMAT DP TO IC

- CONTROL MESSAGE FORMAT IC TO DP Fig. 4b

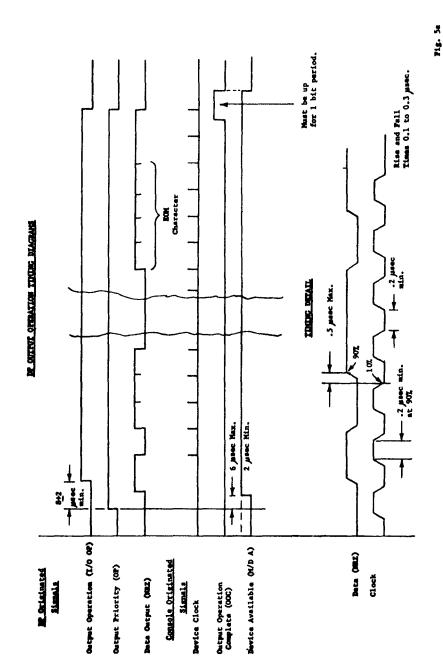

- TIMING DIAGRAMS DATA PROCESSOR OUTPUT OPERATION TO ET AND lie. 5a CONTROL

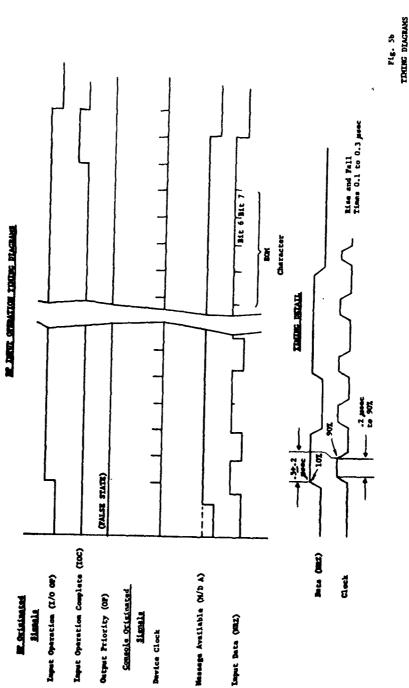

- TIMING DIAGRAMS DATA PROCESSOR INPUT OPERATION FROM INTEGRATED Fig. 5b CONSOLE

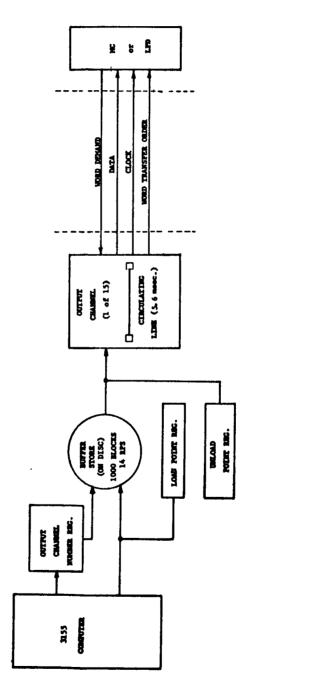

- MC (AND LPD) OUTPUT INTERFACE Fig 6

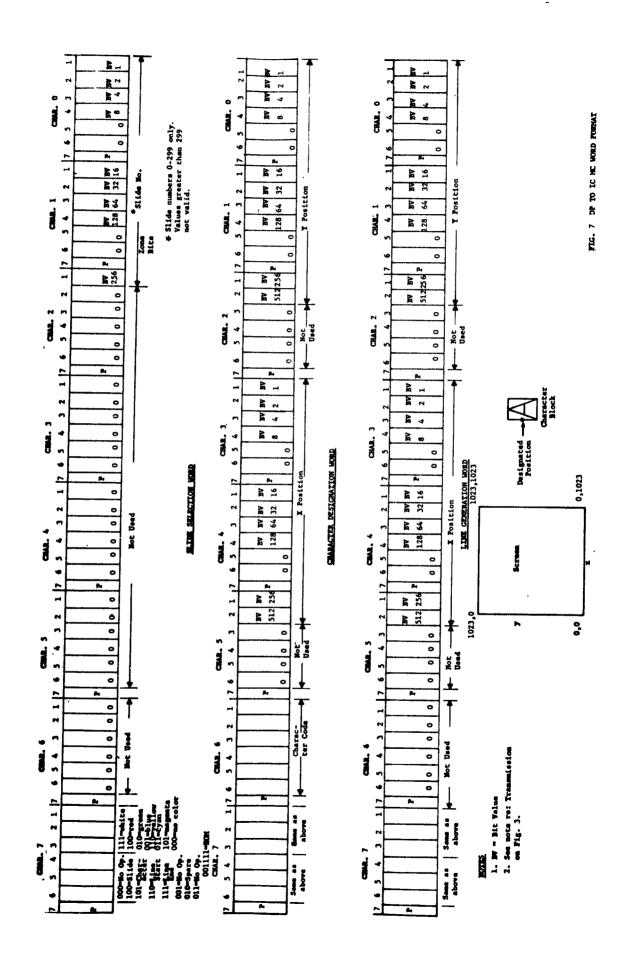

- Fig 7 DP TO IC MC WORD FORMAT

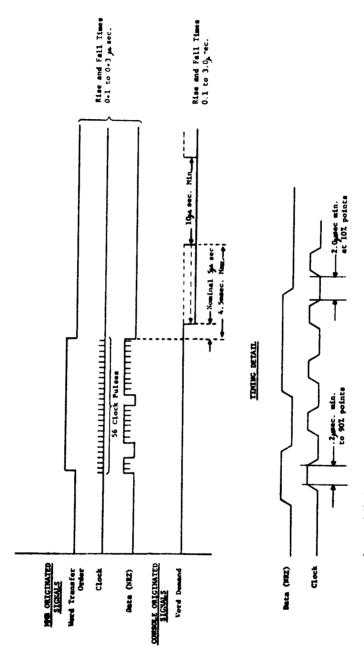

- Fig. 8 TIMING DIAGRAMS DATA PROCESSOR OUTPUT OPERATION TO M-C DISPLAY

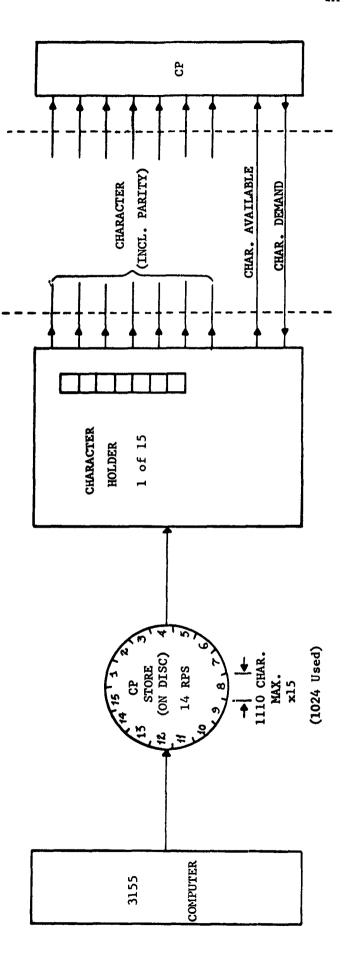

- Fig. 9 CP OUTPUT INTERFACE

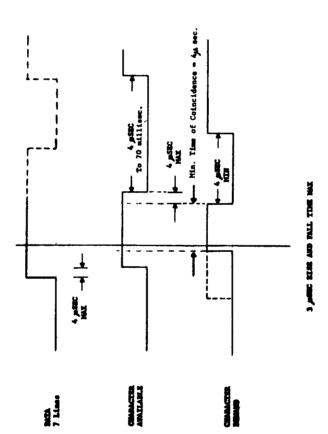

- F/g. 10 SIGNAL CHARACTERISTICS DATA PROCESSOR TO CONSOLE PRINTER

TM-3511

#### 473L DPSS/ICSS INTERFACE DESCRIPTION

#### 1.0 INTRODUCTION

The 473L Data Processing Subsystem (DPSS) communicates on a real-time basis with a number of input/output consoles comprising the Integrated Console Subsystem (ICSS). These consoles are of three types designated the AN/FYA-2, AN/FYA-3 and AN/FYA-4 respectively and differing principally in the aggregation of major functional components provided in each.

The AN/FYA-2 console (Type A) contains all major components, these being:

- 1. Electronic Typewriter/Display (ET) (includes Control Keyboard)

- 2. Logic Keyboard Assembly (LKB)

- 3. Multicolored Display (MC)

- 4. Hard Copy Device (for MC) (HC)

- 5. Console Printer (CP)

The AN/FYA-3 Console (Type B) contains only items 1, 2 and 3 of the above. The AN/FYA-4 Console (Type C) contains only items 1 and 5.

The detailed description of these integrated consoles may be found elsewhere.

This document describes the electrical and functional interface between these consoles and the DPSS and establishes their mode of interaction.

The DPSS and the ICSS will be installed in two phases. These are the IOC phase (Interim Operational Capability) and the COC phase (Complete Operational Capability). The IOC phase requires a partial implementation of system equipment configuration and involves the use of only one AN/FYQ-11 data processor and 4 integrated consoles. For the sake of generality, the following description relates to the COC configuration of which the IOC configuration is but a subset. With the exception of the implications of "duplex" switching between two data processors, the larger number of consoles and the references to the Large Panel Displays, the console interface descriptions are equally applicable to the IOC configuration.

#### 1.1 General Description of DPSS/ICSS Interface

In general, the DPSS provides separate and distinct interfaces for communication with each of three major functional areas in the integrated consoles.

These are: 1. ET, and Control Interface (incl. LKB)

- 2. MC Display Interface (incl. Large Panel Displays)

- 3. Console Printer Interface

An I/O register directly associated with the computer portion of the Data Processor communicates directly with the ET and CONTROL area of the consoles by high speed data transfer in either direction. This ET and CONTROL interface handles all Integrated Console inputs to the Data Processor and all outputs to the ET Display, Logic Keyboard and the Control Keyboard. (i.e., all communications to the console except M-C display and console printer outputs).

The DPSS communicates with the M-C Displays via an area of the MASS MEMORY unit designated the Mass Memory Buffer Store (MMBS).

The M-C Display interface provides solely an output capability, data being transferred from the DPSS to the M-C displays on a word demand basis.

The DPSS communicates with the Console Printers via an area in the MASS MEMORY unit designated the Mass Memory Console Printer Store (MMCPS). An output capability only is provided, data being transferred from the DPSS to the Console Printer on a character demand basis.

Console inputs to the DPSS functionally related to the M-C Displays or Console Printers are transmitted via the ET and Control interface.

In addition to the above, the DPSS communicates with Large Panel Displays in an output function only and via the M-C Display interface. Separate channels in this interface functionally identical to those provided for M-C Displays provide for DPSS output to future LP displays on a word demand basis. Since the LP displays have not yet been specified, this part of the interface is considered tentative.

The COC configuration of the Data Processing Subsystem will provide 15 ET and Control input/output channels and 11 M-C Display, 15 Console Printer and 8 Large Panel Display output channels. With the exception of the 8 LPD channels, the above channel complement is duplicated in each of the two data processors and any or all consoles may be manually switched to either processor with no degradation of output capability (other than that which may result from increasing the load on a given processor).

Only 4 basic LPD channels are provided in each of the two data processing subsystems. The 4 basic output channels are expanded to 8 by processor controlled switching which permits time sharing of outputs to two Large Panel Displays. Any or all LP displays may be manually switched to either Data Processing subsystem but if more than 4 are switched to one processor, time sharing of affected channels will reduce output rate to the related LP displays.

The ET and Control interface input/output channels are not capable of simultaneous operation. No buffer storage is provided and all consoles communicate directly with the same I/O register on a sequential basis for input and on a program selected basis for output. The same I/O register is used to communicate with the DATACOM interface. Data transfers via this register, however, are of sufficient speed that effective practical simultaneity of operation of the Integrated Consoles is achieved. This is further aided by the essentially "off-line" mode of operation of the Consoles between data transfers.

Data transfers to the M-C and LP displays involve a substantial amount of buffer storage in each MMBS. The MMBS is shared among all connected M-C and LP displays, but each output channel contains recirculating storage for two blocks of data. Consequently, outputs via these channels can proceed simultaneously with only minor interactions during channel accesses to the MMBS or data processor accessing of the MMBS.

Data transfer to the Console Printer is via separate buffer storage in the MMCPS allocated to each Console Printer output channel. Outputs via each channel can proceed independently and simultaneously with only minor interactions.

In the COC configurations, all consoles and Large Panel displays interface with the DPSS through manual duplex switching which permits assignment of each console or LPD to either Central Processor. Any or all of the consoles or LPDs may be simultaneously and independently assigned to either processor or they may be distributed between the two processors in any manner desired to meet operational requirements.

The manual switching is accomplished independently for each interface area so that the ET and Control, M-C display and Console Printer portions of each console may be individually assigned to either processor subsystem. Ordinarily, all components of a console would be assigned to the same processor, however failure of a Mass Memory unit may require placing all M-C displays and Console Printers on the remaining Mass Memory unit while the ET and Control portions remain distributed between two processors. Switches for 10 M-C and CO changes are electrically ganged.

The Central Processor program may test the status of the manual duplex switching to determine which interface channels on either processor are actively connected to consoles or LP displays.

The manual switching does not provide the capability to switch devices from one channel to another in the same processor subsystem nor to any arbitrary channel on the alternate processor subsystem. Switching only occurs between a given channel and its alternate. Change of channel assignments beyond this requires relocation of device connectors.

A general outline of the DPSS/ICSS interface including the tentative duplex manual switching is shown in Figure 1 (a).

Figure 1 (b) shows the Large Panel Display interface as it is defined at this time. Although this interface is tentative and cannot be confirmed until the Large Panel Display subsystem is specified and destined in detail, it is expected that little change will occur in the portion described herein.

Fig. 1a DPSS/ICSS INTERFACE (SCHEMATIC ONLY)

LPD's 7 & 8 are shown switched to individual channels LPD's 7 & 8 are shown switched to time share channel 7 of MMA

NOTE: Neutral OFF position may also exist on all manually controlled switches

Fig. 1b DPSS/LPD INTERFACE (SCHEMATIC ONLY)

TM-3511 7

#### 2.0 ET AND CONTROL FUNCTION INTERFACE

The ET and Control Function Interface is illustrated grossly in Figure 2.

ET and control messages are carried in a two-way transmission function over an individual set of lines for each ICSS. These lines communicate directly with a special input-output register connected with the processor core memory, which is also used for Digital Data Link transmission.

"Input to Processor" requests (Message Available signals from the ICSS's) are scanned, with all the Digital Data Links being considered every time an ICSS is considered, to produce a processor "Input" interrupt. The processor, programmatically, determines the source of input, allocates space in core memory and initiates the input operation proper. The processor continues its program execution and may test for completion of the input process. At the end of the message transfer, the processor will receive an "I/O Interface Not Busy" interrupt.

Outputs to the ICSS and Digital Data Links are initiated by processor program execution. Outputs are from core memory through the inequi-output register used for input and proceed independent of program execution. Outputs are sent by address directly to the receiving device without operator intervention but responsive to the "Device Available" signal which indicates console status. A console, when not in the INPUT mode, is always ready to accept an output control message and an output to the ET display usually occurs in response to an input control message request coupled intrinsically with readiness of the ET to receive the output message.

When output to the ET Display occurs in response to a control message respect than those originating in the Logic Keyboard, activation of the request control key clears the ET Display so that it is ready to receive the requested message. When the output to the ET Display occurs in response to a Logic Keyboard operation or without operator request, the ET Display is cleared by the console on receipt of the Message header and prior to transmission of the rest of the message. In the latter instances, transmission of the body of the output message is delayed by the receiving device for approximately 16 milliseconds while the ET Display is cleared.

The 3155 computer program can precede the transmission of an output message by a test of the state of the duplex switching.

The actual output process is initiated by executing an output instruction defining the destination device (with the field selection characters) and the (indexed) memory location of the first word to be transmitted. During transmission, this instruction is held in a special input-output instruction register, so the computer can proceed with its program. Core memory accesses are made by interrupt at logic level.

The output process begins with a signal on the Output Priority Line to the selected device. The device must answer on the Device/Message Available line, or the transmission aborts. Transmission begins when the first data bit is on the Output Data line and the Input/Output Operation line goes ON. Device clock pulses gate successive bits of the message.

The output operation terminates when the device signals Output Operation Complete in response to receipt of an EOM character.

If the computer detects bad parity in a word it is about to transmit, it removes the Input-Output Operation signal, aborts the transmission and causes an error interrupt in the program. This condition is noted in the device and any retransmission is made under program control.

If the receiving device detects bad parity in a character, it removes the Device/Message Available signal, not having sent an Output Operation Complete signal. This condition aborts the transmission and causes a second type of error interrupt in the program. The processor program may attempt to retransmit the aborted ET message. If errors persist, the program may retransmit the ET message with a special header. This header is recognized by the receiving device which then accepts the entire message regardless of parity errors and without sending error signals back to the processor or aborting transmission. The resulting ET Display, in this instance, will show special flashing symbols in place of characters on which bad parity is detected.

If an output instruction selects a device that does not respond with a Device Available signal, a third type of error interrupt occurs. As duplex switching status is separately program testable, this error condition presumably indicates an inoperative device.

The same lines used for output carry imput messages. The input process is signified by an absence of a signal on the Output Priority line.

The input process begins with a device originated signal on the Device/Message Available line. A scanner selects one of the devices asking to input and causes a program interrupt. Transmission begins when the computer executes an input instruction which sends a signal to the selected device on its Input-Output Operation line. The device responds by sending Data and Device Clock. Core memory accesses are made by interrupt at logic level. The input instruction carries the (indexed) memory location where the input message is to start.

The input operation terminates when the computer detects an EOM character and signals Input Operation Complete.

If the computer detects bad parity in a word it is receiving, it removes the signal on the Input-Output Operation line without sending Input Operation Complete. No more characters will be received, and an error interrupt occurs in the program. The device notes failure of reception and the message retransmission, if desired, is performed by the console operator.

TM-3511

The device may recognize that it has bad parity in a character it is sending and abort the transmission by removing the Device/Message Available signal. This is noted in the computer and an error interrupt occurs in the program.

If the device fails to send its clock in response to the Input-Output Operation, a hang-up occurs in the interface. The hang-up is ended by a timer which frees the interface to respond to other inputs and outputs and generates a "Hang-up Error" interrupt.

Any error interrupts to the program in the computer may be selectively ignored, under program control.

#### 2.1 Data Transmission Rate

Data is transmitted between the Data Processor I/O register and the ET and control portion of the integrated console at a rate of 720±15% kilobits/sec. Data is transmitted in a "Non-Return to Zero" (NRZ) signal mode to or from the console and is timed by a console originated clock signal establishing the actual rate of transfer. The maximum data transfer rate acceptable by the Data Processor is 1.1 megabits/sec.

#### 2.2 Message Formats

The two types of messages transferred in the ET and control function interface are ET Display Messages and Control Messages. Data transmission formats are in general governed by the Data Processor 56 bit word format which is alphanumeric and contains 8 characters each comprised of 6 bits plus parity. Data is transmitted to and from the processor, in this interface, serially by bit on a character basis. Each word is transmitted with the least significant bit of the most significant character first in the sequence (i.e., Bit 1, Character 7; Bit 2, Character 7;.... Bit 7, Character 7; Bit 1, Character 6; Bit 2, Character 6;....Bit 7, Character 6;....Bit 1, Character 0; Bit 2, Character 0, etc.) Normally, the format of every message transferred in this interface is headed by a control character, which identifies the nature of the message, and is terminated by an "EOM" character.

#### 2.2.1 ET Message Formats

ET messages from the Data Processor to the console are destined for display on the ET display surface and would normally not exceed 2370 characters including the message header and the "end of message" (EOM) character (i.e., one ET display page). The length of an ET message is arbitrary up to this value. In any event, the console terminates the transmission on receipt of EOM or the 2369th character, whichever occurs first.

ET messages transmitted from the console to the Data Processor cannot exceed 2370 characters including the message header and the EOM character because of limit in page size. The actual length of ET messages transmitted by the console is arbitrary up to this number.

#### 2.2.1.1 Data Processor to Console

The message format applicable to ET message transmissions from the Data Processor to the console is shown in Figure 3. The control character heading the format has two states applicable to ET message transmissions. These designate ET Type 1 and ET Type 2 messages. ET1 messages are subject to interrupt on parity error detection. ET2 messages are transmitted to the ET display in entirety regardless of parity errors occuring during transmission. In the latter case, parity errors are nevertheless detected and indicated to the console operator.

The control character heading the ET message occurs only in the Character 7 position of the first word of the message. Subsequent words may be fully packed with alphanumeric symbol data. The EOM character terminating the message may occur in any character position of the appropriate word in the sequence. The first displayed character in the message is that appearing in the Character 6 position of the first word of the message. Subsequent characters follow in sequence according to the Data Transmission sequence described in Paragraph 2.2.

In an ET message the only control character used other than the header and EOM characters is the "Lower Case" code which may occur anywhere in the ET message and causes the ET to perform the "carriage return/line feed" function. No symbol is displayed on the ET corresponding to this character code.

#### 2.2.1.2 Console to Data Processor

The message format applicable to ET message transmissions from the console to the Data Processor is shown in Figure The first character transmitted in any ET message is a control character identifying the message as an ET message and in some instances indicating to the processor the operation to be performed on the input data. Bit positions 5 and 6 of the control character are used to indicate to the processor which of the three display pages available to the ET Display is being transmitted. The first line of the ET Display (64 characters) is reserved for further instruction to the processor regarding the disposition of the following portion of the message. This line is used for such things as routing address, storage address, etc. Consequently, the format of a complete ET input message header consists of a control character followed by 64 characters in which direction to the processor This is followed by the body of the ET message and terminated by the EOM character. The total ET input message, including header and EOM, cannot exceed 2370 characters. The EOM character can occur anywhere in the ET message following the control character.

The control character code is not responsive to control by the alphanumeric keyboard on the console nor is it displayed on the CRT. The control character for a given message is in general set up by console pushbutton action. Consequently, a direct relationship exists between the character codes utilized and corresponding pushbuttons on the Integrated Console. The utilization and significance of the control character codes available are shown in Figure 3.

#### 2.2.2 Control Message Formats

All control messages transferred between the DPSS and the Integrated Console are headed by a control character identifying the message as a control message. The control character may also contain other information relative to the control function to be performed.

#### 2.2.2.1 Data Processor to Console

The message format applicable to control messages transmitted from the Data Processor to the console is shown in Figure 4(a). These messages consist of two 56 bit words and are terminated by an EOM character at the end of the second word. The control character heading the control message designates whether a CM Type 1 (CM1) or CM Type 2 (CM2) message is being transmitted. Parity error in a CM1 message does not indicate error to the console operator but requests retransmission of the message by the processor. If a parity error occurs in a CM2 message, transmission is aborted, all control indicators\*on the receiving console are not changed, and an appropriate error indicator is lit on the Integrated Console. ("Message Waiting" counters on the console remain at existing count) (\* Logic keyboard indicators will be cleared to OFF.)

With the exception of the characters transmitted controlling the logic keyboard indicators, all characters have "Zero" in bit positions 4, 5, and 6. Logic keyboard control characters always have a "one" in bit position 6. Bits in positions other than those fixed above (except parity) may have any simultaneous values so that a single control message can simultaneously establish several control or indicator conditions. (Obviously some combinations are contradictory and would not normally occur) The location and significance of control message codes are shown in Figure 4(a).

#### 2.2.2.2 Console to Data Processor

The message format applicable to transmission of control messages from the console to the Data Processor is shown in Figure 4(b). These control messages are initiated by console pushbuttons and consist of four characters only. The first character (Ch. 7) uniquely identifies the message as a control message by means of the values 1111 or 1001 in bit positions 1, 2, 3, and 4 respectively. Bits 5 and 6 of the control character designate the ET display page being viewed at the time of transmission of the control message.

Character 4 of the control message is always an EOM character signifying the end of transmission.

Characters 5 and 6 have different meanings depending or whether the control message is originated by the Logic Keyboard or by a control pushbutton. In the former case, character 6 indicates which overlay is in place on the Logic Keyboard while character 5 indicates which Logic Key was depressed. In the latter instance, character 6 is

always "ZERO" and character 5 indicates which control pushbutton was activated. The codes assigned for character position and their significance are shown in Figure 4(b).

#### 2.3 Transmission Modes

#### 2.3.1 Data and Control Lines

The following signal lines are used for transmission of control and ET messages to and from the console. Several lines are dual purpose carrying different signals depending on whether the console is in the "Input Mode" or in the "Output Mode." "Input Mode" is defined as the condition wherein the console is transmitting data to the Data Processor. The "Output Mode" exists when the Data Processor is transmitting data to the console.

| Line | Input                 | Mode          | Output                 | Mode          |

|------|-----------------------|---------------|------------------------|---------------|

|      | Function              | Signal Source | Function               | Signal Source |

| 1    | Input<br>Operation    | Data Proc.    | Output<br>Operation    | Data Proc.    |

| 2    | Imput Op.<br>Complete | Data Proc.    | Ourput<br>Data         | Data Proc.    |

| 3    | Output<br>Priority    | Data Proc.    | Output<br>Priomity     | Data Proc.    |

| 4    | Device<br>Clock       | Console       | Device<br>Clock        | Console       |

| 5    | Input<br>Data         | Console       | Output Op.<br>Complete | Console       |

| 6    | Message<br>Available  | Console       | Device<br>Available    | Console       |

The functions of each of these lines are outlined below.

#### Line 1 - Input/Output Operation (I/O OP)

When in Input Mode this line will go true in response to a "Message Available" signal from the console when the Dana Processor is ready to receive the message to be transmitted. Under these conditions, the "True" state of this line indicates that an Input Operation is in progress. The I/O OP line goes false if a parity error is detected by the processor in the incoming message.

TM-3511 13

When in output mode, this line goes true in response to a "Device Available" signal transmitted by the console on receipt of a Data Processor request to output a message (Output Priority). The true state of the I/O OP line under these conditions indicates that an output operation is in progress. This line will go false if a parity error is detected by the processor in the output message.

#### Line 2 - Input Operation Complete/Output Data (IOC or OD)

In Input Mode, this line goes true when the Data Processor successfully receives an EOM character signifying the end of the input transmission.

In Output Mode, this line carries the data transmitted by the processor to the console.

#### Line 3 - Output Priority (OP)

In Input Mode this line remains false indicating that the console is in the Input Mode.

In Output Mode this line is set true by the processor to indicate to the console the start of Output Message sequence.

#### Line 4 - Device Clock

In both Input and Output Modes this line carries console generated clock signals used to synchronize transfers of data to and from the console.

#### Line 5 - Input Data/Output Operation Complete (ID or OOC)

In Input Mode this line carries data transmitted by the console to the Data Processor.

In Output Mode this line is set true by the console on successful receipt of the EOM character (or on receipt of 2369 characters) signifying completion of the transmission. The line will remain false if a parity error in the transmitted message is detected at the console. (Except when an ET2 message is transmitted)

#### Line 6 - Message Available/Device Available (M/D A)

In Input Mode this line is set true by the console to indicate that a message is ready for transmission to the Data Processor. Provided the OP line is false, the true state of this line causes an "input interrupt" and places the console in the input mode.

In the Output Mode this line goes true in response to receipt of an Output Priority (OP) signal, signifying that the console is operating and ready to receive an output message. This line will go false if a parity error in the transmitted message is detected at the console. This line

is interlocked with other console originated signal lines to ensure that no console error or failure will tie up the I/O interface of the central processor. The false state of this line signifies functional disconnection of the console of "Device Not Available."

#### 2.3.2 Normal Output Operation (DP to IC)

The relative timing of signals and data relevant to an output transmission is shown in Figure 5(a).

An output operation is initiated by the Data Processor by causing the Output Priority Line (OP) to go true. In response to this action the Device Available line must be set true by the console within 6 $\mu$  seconds. If the Device Available line does not go true after  $2\mu$  seconds and before  $6\mu$  seconds after the OP line goes true, or is true before OP goes true, a "Hang-up Error" interrupt of the Data Processor will occur causing the console to be functionally disconnected for that operation.

The Output Operation line will go true, signifying commencement of output transmission, in response to the console originated Device Available signal at  $8+2\mu$  seconds after the Output Priority line goes true. The first data bit is present on the Output Data line at the time that the Output OP line goes true. The console then supplies clock pulses on the Device Clock line controlling output of data.

Upon receipt of the EOM character signifying the end of the transmission, the console switches the Output Operation Complete line (OOC) to the true state for one bit period. In response to the true state of the OOC line the processor returns the Output OP and Output Priority lines to the false state. Clock pulses are supplied by the console until the Ouput Operation line goes false. The Device Available line will be set false by the console at the end of an output operation, coincident with the return of OOC to the false state.

The sequential states of the various control signals during an output operation are summarized in Table 1 below.

| Call  | Response | Transmit                           | End OP             | Receive<br>Error             | Send<br>Error | Device<br>Inoperative |

|-------|----------|------------------------------------|--------------------|------------------------------|---------------|-----------------------|

| OP-#1 | M/D A→1  | OP=1<br>M/D A=1<br>OOC=0<br>I/O →1 | (EOM or full page) | M/D A>0<br>I/O OP=1<br>OOC=0 | O.P>()        | if:                   |

The ET Display cursor is normally positioned over the EOM character after completion of a data transfer from the processor. If a full page transfer is made (2369 characters including header) the cursor is automatically positioned in the first position of the second line of the ET Display.

#### 2.3.3 Normal Input Operation (IC to DP)

The relative timing of control signals and data relevant to an input operation is shown in Figure 5(b).

An input operation is possible only when the Output Priority line is false. Under these conditions the input operation is initiated by the console setting the Message Available line (M/D A) true as a response to operator action.

In response to a true level on the Message Available line, the processor sets the Input Operation line true under program control. Clock pulses and data are then sent to the processor by the console on the Device Clock and Input Data lines.

Upon receipt of the EOM character signifying the end of transmission, the processor sets the Input Operation Complete line (IOC) true. The console must respond to a true level on the IOC line by returning the Message Available line to the false state.

The processor them returns the Input Operation line to the false state on receipt of EOM signifying completion of the input operation. The Device continues to send clock pulses until the IOC line is set false by the processor.

The normal sequence of control signals occuring in an input operation is summarized in Table 2 below.

| Call                     | Response            | Termination   | Receive<br>Error  | Send<br>Error    | Device<br>Inoperative  |

|--------------------------|---------------------|---------------|-------------------|------------------|------------------------|

| M/D A <b>→</b> 1<br>OP=0 | I/O OP→1<br>M/D A=1 | IOC→1<br>OP=0 | I/O OP→O<br>IOC=O | M/D A→O<br>IOC=O | No M/D A-▶1<br>on call |

|                          | IOC=0               | (on receipt   | OP≈0              | I/O OP=1         |                        |

|                          | OP=0                | of EOM)       |                   | OP=0             |                        |

|                          |                     |               |                   | <br>             |                        |

#### 2.4 Error Considerations

In general, three types of malfunction can occur in the DPSS/ICSS interface causing errors in operation. These are errors in the data being transmitted, errors in control line levels or sequence of operation and operator procedure errors. Reliance is placed on parity checking and in some instances code legality checks to discover errors in data transmission and initiate appropriate action. Parity is checked both at the console and at the Data Processor M Register on all message transmissions and error conditions indicated to the operator. Control line errors are detected or prevented by functional or direct interlocking where feasible particularly if such errors cause unwarranted serious degradation of the system. In the latter case, if a console is the source of the error condition, special devices are used to ensure that total interface hang-up does not occur.

Operator procedure errors, where not inhibited by console interlocks are in general detected by the processor program and indicated to the operator via the procedure error indicator and if appropriate by an ET display or console printer message.

Two of the control lines are used to signify error conditions detected at the processor and at the console. The Input/Output Operation line (I/O OP) is used to signal the console that an error condition is detected at the processor while the Message/Device Available line (M/D A) is used to signal the processor regarding error conditions detected at the console. In both instances, the felse state of these lines when they would normally be expected to be true signifies an error condition and halts or prevents the operation in progress. In either case, a data processor interrupt occurs allowing the program and/or the console operator to take appropriate remedial action.

#### 2.4.1 Error in Output Operation (DP to IC)

An output operation will consist of either an ET message transmission or a control message transmission. In either case parity is checked at the Data Processor M Register prior to entry of data into the I/O word register. Parity errors, if they occur, are detected at the end of the word and cause the processor to set the I/O OP line false. A false level on the I/O OP line in conjunction with the false state of the OOC line and the true state of the M/D A line indicates a Data Processor detected parity error. Transmission of the message is stopped and the console disconnected, by virtue of the I/O OP line going false, and an "M" Register Parity Error" interrupt occurs.

Parity checking of both ET and control messages also occurs at the console. In addition the console performs legality checks on the first character (control character) of each incoming message. In event of a console detected error the console will cause the M/D A line to go false and continue to send clock pulses until the Input/Output Operation line (I/O OP) goes false. The processor will set the I/O OP and the Output Priority lines false within  $5\mu$  seconds after the M/D A line goes false, generate a "Data Parity Error" interrupt, and disconnect the console.

In the normal sequence of operations, detection by the console of the EOM character terminating a message, or receipt of 2369 characters causes the console to set the M/D A line to false state terminating transmission and freeing the processor I/O interface to service other devices. Failure by the console to detect EOM will cause transmission to continue until the 2369th "character" is received. If this condition fails to terminate transmission, a timer in the Data Processor will automatically terminate the operation. Any ET or Control message output not terminated normally or by a detected error will be terminated by the processor in 45-85% milliseconds, disconnecting the Console from this interface. The output operation is thereby terminated and an "I/O Hang-up Error" interrupt generated. (Maintache of mediaterance)

All parity errors are indicated to the operator. If a parity or illegal code error is detected in the first character of an output message the console cannot determine what type of message is being received. The processor will attempt to retransmit the message in which the error was detected. After the third unsuccessful attempt, the message is aborted and an indicator on the console lit signifying the inoperative state of that console or output channel.

#### 2.4.1.1 ET Message Error Operations

ET messages are normally transmitted to the console with an ETI control character. Parity or other errors detected in the ETI message are indicated to the processor as described above and cause cessation of transmission and disconnection of the console. Under program control, the processor may retransmit the message with an ETI control character. If errors occur the second time, the processor may elect to retransmit the message with an ET2 control character. This control character causes the console to accept the message regardless of parity errors (except in 1st character) and display the message. Under these conditions, characters on which parity errors are detected are displayed as a special blinking symbol (B).

#### 2.4.1.2 Control Message Error Operations

Control messages are normally transmitted to the console with a CMl control character header. If a parity error is detected on a CMl control message, transmission is halted as above and the control message is ignored. Under program control the CMl message may be retransmitted by the processor. On a third attempt, the Processor may change the control character to a CM2 header. The console detects this header, ignores the input message if a parity error is detected indicates an error condition to the operator. Control indicators remain unchanged. Further remedial action may be taken by the processor.

#### 2.4.1.3 Control Line Error Operations

Control lines active during an output operation may fail in either the false or the true state at either the transmitting or receiving end. Console clock pulses may fail preventing transfer of

TM-3511

data out of the Processor I/O register. Since unilateral failure of the console clock can cause serious degradation of I/O interface this line where feasible, is interlocked with the Message/Device Available line at the console so that failure of clock signals will cause the M/D A line to go false effectively disconnecting the console. A summary of the effects of control line error on an output operation is given below. It is assumed that only one control line will fail at a time. When a timed disconnect occurs, this means that the output operation is terminated by the processor, the console is disconnected from the I/O interface and an "I/O Hang-up Error" interrupt is generated.

#### Line 1 - Input/Output Operation

#### Error 1

1/0 OP Locked False

#### Result

Timed disconnect occurs.

#### Error 2

I/O OP Locked True

#### Result

Not absolutely determined. Either a normal transmission or a timed disconnect will occur.

#### Line 2 - Output Data Line

Locked in False or True state

#### Result

This will cause a first character parity or illegal code error at the console causing disconnection of console and a processor interrupt.

#### Line 3 - Output Priority (OP)

#### Error 1

OP Locked False

#### Result

Fails to signal output operation to console. Absence of M/D A-1 response from console signifies "Device Inoperative" causing "Hang-up Error" interrupt.

#### Error 2

OP Locked True

TM-3511 19

#### Result

Timed disconnect occurs

#### Line 4 - Device Clock

#### Error

Failure of clock signals

#### Result

This condition is interlocked with M/D A line causing a false condition of this line and appropriate disconnect and processor interrupt actions. Timed disconnect occurs if error is not disconnected by other means.

#### Line 5 - Output Operation Complete (OOC)

#### Error 1

OOC Locked False

#### Result

Similar to failure to receive EOM or detect end of page. Timed disconnect occurs.

#### Error 2

00C Locked True

#### Result

Processor sends only one character and ceases transmission. Programming implications not determined.

#### Line 6 - Message/Device Available (M/D A)

#### Error l

M/D A Locked False

#### Result

Signifies Device Inoperative to Processor. A "Hang-up Error" interrupt occurs if the processor attempts to output. If this occurs during an output operation, a "console detected error" is indicated causing an attempt at retransmission and consequent "Hang-up Error" interrupt.

#### Error 2

M/D A Locked True

#### Result

If this condition exists prior to an output operation, the console is locked in the input mode and a "Hang-up Error" interrupt occurs on attempt to output.

If this occurs during an output operation, a timed disconnect will occur.

#### 2.4.2 Error in Input Operation (IC to DP)

An input operation will consist of either an ET message or a control message transmission from the console to the Data Processor. Parity is checked both at the console and at the Data Processor. The response to error conditions is identical for both ET and control messages.

Parity errors on an input message are detected by the Data Processor at the end of a word on transfer of this word from the I/O register to the DP "M Register". A detected parity error will cause the processor to set the Input Operation line to the false state without sending Input Operation Complete, terminate the input operation and generate an "I/O M Register Error" interrupt. The console will recognize this early termination as a Data Processor detected parity error, switch the M/D A line to the false state and notify the operator that a transmission error has occurred.

Parity errors in an input message detected at the console cause the console generated M/D A line to go false terminating the input operation. Indication of input transmission error is given to the operator and to the program as a "Data Parity Error" interrupt. (The computer recognizes the early termination as an error)

The console is not disconnected immediately on the occurrence of an error interrupt. The program, however, can examine the Input Scanner to determine which console is causing the error, disconnect that console and allow the scanner to proceed to the next device.

The stepping circuits of the scanner are inhibited by the presence of an error condition setting any of the detailed error flip-flops associated with the processor I/O interface. The scanner will continue to select the last device used for input until either the "Ignore Error" flip-flop is set or the detailed error flip-flop is reset by the computer program.

If the input operation does not terminate normally or by a detected error it will be terminated by the processor in 45 to 85 milliseconds, generating an "I/O Hang-up Error" interrupt. Program responce to the interrupt can cause the Input scanner to step to the next device, disconnecting the affected console.

Procedure errors in input operations, where not inhibited by functional or electrical interlocks at the console, are detected by the computer program and the console operator notified by a special indicator, and at the discretion of the program, by an ET Display or console printer message.

TM-3511

In general, errors occuring in transmission of ET or control messages terminate the input operation and notify the console operator that an error condition exists. Retransmission of the message is achieved by the operator if desired by repeating the input operation that failed. Persistent failure to achieve a successful input transmission indicates console or DP interface failure requiring maintenance.

#### 2.4.2.1 Control Line Errors

The control lines relevant to an input operation may fail in either a faise or a true state at either the console or the Data Processor. Where necessary to prevent I/O interface hang-up, the controlling levels are functionally or electrically interlocked. A summary of the effects of control line failures on an input operation is given below.

#### Line 1 - Input/Output Operation (I/O OP)

#### Error 1

I/O OP Locked in False State

#### Result.

Timed disconnect occurs

#### Error 2

I/O OP Locked True

#### Result

Not fully determined

#### Line 2 - Input Operation Complete (TOC)

#### Error 1

IOC Locked False

#### Result

This condition causes action similar to "Computer Detected Error" at the console causing the M/D A line to go false. Transmission is terminated normally and error condition indicated to the operator.

#### Error 2

IOC Locked True

#### Result

This will cause early termination of the input operation and causes a processor detected "Data Parity Error" interrupt.

TM-3511

#### 2.2

#### Line 3 - Output Priority (OP)

#### Error 1

OP Locked False

#### Result

No significant effect on input operation unless true at processor end. If true at processor end, a "Hang-up Error" interrupt will occur if an Output operation is attempted.

#### Error 2

OP Locked True

#### Result

Inhibits input operation. No hang-up of I/O interface will occur.

#### Line 4 - Device Clock

#### Error

Locked True or Faise

#### Result

A timed disconnect will occur generating a "Hang-up Error" interrupt.

#### Line 5 - Input Data

#### Error

Locked True or False

#### Result

Because of normal NRZ operation of this line, false condition will transmit all zeros. Parity error detection will halt transmission and signal console operator. If locked true, all ones will be transmitted and a timed disconnect will occur freeing the interface.

#### Line 6 - Message/Device Available (M/D A)

#### Error 1

M/D A Locked in False State

#### Result

No input operation can be initiated. Comsole is in the "Device impperative" state.

#### Error 2

M/D A Locked in True State

#### Result

The console will be in continuous imput mode because of priority of Input mode over Output mode. A timed discornect will occur generating a "Hangup Error" interrupt.

### 2.5 <u>Summary of Console Key Functions Providing Inputs to the Data</u> Processor Via the ET and Control Interface

The following console keys transmit control messages or control characters plus ET messages from the console to the Data Processor. The functions to be performed by these keys will be fully described in technical memoranda pertaining to the design of the integrated console. A number of spare keys and spare codes will exist on the console to accommodate a reasonable number of additions.

2.5.1 The following keys generate and insert a unique control character in the ET message header and initiate transmission of the combined ET message to the processor. Subsequent action is initiated and carried out by the DPSS program. The control character includes designation of the ET display page being viewed at the time of transmission.

| Nam | e                         | Function                                                                        |

|-----|---------------------------|---------------------------------------------------------------------------------|

| 1.  | ENTER                     | Enter ET page                                                                   |

| 2.  | LINE PRINTER              | Enter ET page and print entire related message on line printer.                 |

| 3.  | CONSOLE PRINTER           | Enter ET page and print displayed page on console printer.                      |

| 4.  | NEXT PAGE                 | Enter ET page, clear ET display and display mest page in sequence.              |

| 5.  | PREVIOUS PAGE             | Enter EI page, clear ET display and display previous page in sequence.          |

| 6.  | STORE MESSAGE             | Enter ET page and store total related message in location designated in header. |

| ₹.  | ROUTE MESSAGE (TENTATIVE) | Enner ET page and route related message to destination indicated in header.     |

2.5.2 The following keys generate and insert unique codes for the control character and the third character of a control message, and initiate transfer of a four character control message to the processor. The second and fourth characters of these control messages are "ZERO" and EOM respectively. The control character includes designation of the ET Display page being viewed at the time of transmission.

| Nar | ne                           | Function                                                                                         |

|-----|------------------------------|--------------------------------------------------------------------------------------------------|

| 1.  | HARD COPY                    | Initiate M-C display hard copy cycle and notify processor for security logging.                  |

| 2.  | PRIORITY/MESSAGE ACCEPT      | Clear ET Display and request display of next Priority or ET message in queue.                    |

| 3.  | ERROR/REPLY ACCEPT           | Clear ET Display and request display of next message in "Retrieval" and "Procedure Error" queue. |

| 4.  | MESSAGE ACCEPT (M-C DISPLAY) | Request display of next M-C display in queue.                                                    |

| 5.  | FORMAT INDEX                 | Clear ET Display and request display of index of formats.                                        |

| 6.  | CANCEL OPERATION             | Request processor to cancel all oper-<br>acions initiated by this console.                       |

2.5.3 The following keys generate unique codes for the control character and the third character of a control message. The second character in these control messages is a unique code determined by the designator of the overlay in position on the logic keyboard. The fourth character of all control messages is EOM. The control character includes designation of the ET Display page being viewed at the time of transmission.

| Name              | Function                                                                                   |

|-------------------|--------------------------------------------------------------------------------------------|

| Start (Overlay)   | Start sequence of operations identified by the overlay descriptor; light initial options.  |

| Logic Pushbuttons | Perform operation associated with particular overlay key and overlay descriptor indicated. |

Code assignments for the above functions and their location in the appropriate message formats are shown in the message format diagram.

## 2.6 Summary of Console Indicators Activated by Outputs from the Data Processor Via the ET and Control Interface

$2.6.1\,$  The following console indicators are activated by control messages from the Data Processor.

| Nan | ne                                        | Function                                                                                                                                                                                        |

|-----|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | PRIORITY/MESSAGE COUNTER                  | Indicates number of priority and routed messages waiting in queue for transmission to console.                                                                                                  |

| 2.  | "PRIORITY/MESSAGE ACCEPT" P. B. Indicator | Indicates "Priority" messages waiting if top half of dual indicator is flashing red. Indicates non-priority routed messages waiting if only white portion of indicator lit.                     |

| 3.  | "ERROR/REPLY ACCEPT" P. B. Indicator      | Indicates that "Query" reply or "Procedure Error" message is ready for transmission to console. Dual indicator shows red for "Procedure Error" message, white for "Reply" message.              |

| 4.  | "MESSAGE ACCEPT" P. B. Indicator (M-C)    | Indicates that a message is ready for transmission to the console M-C Display.                                                                                                                  |

| 5.  | "KEYBOARD ACTIVATE" P. B. Indicator       | Indicates OFF, ENABLED and ACTIVE state of ET Keyboard. May be switched between ENABLED state (green) and ACTIVE state (white) by Data Processor Control message as well as by operator action. |

| 6.  | "START"                                   | Indicates initial condition of Logic<br>Key operation or option to restart<br>under control of processor or oper-<br>ator.                                                                      |

| 7.  | LOGIC KEYS                                | Indicate permissible options in Logic Keyboard overlay sequence                                                                                                                                 |

All control pushbuttons, logic keys and local function keys with the exception of power switches, error indicator P. B.'s and miscellaneous test or adjustment controls are disabled during transmission of a message from the console to the DPSS and, if the transmission is successful, remain disabled until the DPSS sends an appropriate enabling control message. These control keys and pushbuttons are also disabled during transmission of messages from the DPSS to the console and when the console is in the "STANDBY" condition.

2.6.2 The following ET indicators are activated by control line conditions in the ET and control portion of the console interface or by internal console action related to data transfers.

| Name         | Function                                                                |

|--------------|-------------------------------------------------------------------------|

| OUT OF ORDER | Indicates detected error in trans-<br>mission from processor to console |

| RE-ENTER     | Indicates detected error in trans-<br>mission from console to processor |

The names assigned for the above keys and indicators are subject to change although the functions are as indicated.

#### 2.7 Character Codes and Symbol Set

(See Appendix A)

#### 2.8 Physical and Electrical Interface

The electrical characteristics of the signals in the ET and Control interface are as follows:

- A logical "True" level (1) is represented by 8.5±2.5 Volts

- A logical "False" level (0) is represented by 0±1.0 Volts

- Rise and fall times on all signals will be between 0.1 and 0.3 microseconds.

The input impedance presented to a line by the receiving device shall be 75 ohms  $\pm$  10% for either logical level. The driving or output impedance is not specified; provision should be made to add a 75 ohm resistor if it is required for termination purposes.

75 ohm coaxial cable with a capacity no greater than 23 pico-farads/foot will be used for all data and control lines between the console and the processor. Cable lengths have not yet been determined.

Detailed electrical and physical characteristics are to be determined and specified in the detailed subsystem interface specification.

Fig. 2 ET AND CONTROL INPUT/OUTPUT INTERFACE

END OF HESSAGE Can Occur in any Cherecter position

DATA

let Displayed Character

DATA

01-ET2

0

IP TO ET HESSACE

BOH 001111

S de s

7

Fig. 4a CONTROL NESSACE PORMAI DF TO IC

| Ü | ă<br>P<br>P | Character 7                      |         | - |          | Ü     | į    | Character 6           | •                                                                                |   | _           |                                                                              | ð        | Character 5          | ¥ 2   |     | _        |                                                                            | đ                                                                  | 200                                                                                                  | Character 4                                                                          | •                                                                           | -                |                                      |                |                          |                                                  |        |                                                  |

|---|-------------|----------------------------------|---------|---|----------|-------|------|-----------------------|----------------------------------------------------------------------------------|---|-------------|------------------------------------------------------------------------------|----------|----------------------|-------|-----|----------|----------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------|--------------------------------------|----------------|--------------------------|--------------------------------------------------|--------|--------------------------------------------------|

| ۰ | 9 5 4       | 3 2 1                            | 7       |   | 7        |       |      |                       | 765432                                                                           | - | -           | 9                                                                            | 7        | 4                    | 3 2   | ~   | 1 7      | 7 6                                                                        |                                                                    | 5 4                                                                                                  | - 1                                                                                  | 3 2                                                                         | 1                |                                      | İ              |                          |                                                  |        |                                                  |

|   |             |                                  |         |   |          |       |      |                       |                                                                                  |   |             |                                                                              |          |                      |       |     |          |                                                                            |                                                                    |                                                                                                      |                                                                                      |                                                                             | н                |                                      | -              | 2                        |                                                  | F      | <b>-</b>                                         |

|   |             |                                  |         |   |          |       |      |                       |                                                                                  |   |             |                                                                              |          |                      |       |     |          |                                                                            |                                                                    |                                                                                                      |                                                                                      |                                                                             | 32               |                                      | 9              | 7                        |                                                  | -      | -                                                |

|   |             |                                  |         | Α |          |       |      |                       |                                                                                  |   | <u> </u>    |                                                                              |          |                      |       |     |          | o<br>a                                                                     | <u> </u>                                                           | -                                                                                                    | _                                                                                    | ~                                                                           | 33               |                                      | 11             | 12                       | _                                                | 13     | <del>                                     </del> |

| * | *           |                                  |         |   |          |       |      |                       |                                                                                  |   |             |                                                                              |          |                      |       |     |          |                                                                            |                                                                    |                                                                                                      |                                                                                      |                                                                             | *                |                                      | 16             | 2                        | -                                                | 92     | <del> </del>                                     |

|   | احد ا       | Control                          | 2 2     | 7 | ا_ ا     |       | S P  | LKB Overlay<br>Ident. | , i                                                                              |   | -           | _                                                                            | and and  | Pushbutton<br>Ident. | 1 1 1 | 1 ' | 1 -      | ┨.                                                                         | }                                                                  | į                                                                                                    | ┨.                                                                                   | ]                                                                           | ]                |                                      | 21             | 77                       | <del>                                     </del> | 23     | ╁                                                |

|   | <u> </u>    | İ                                |         | - | <u> </u> |       | !    |                       |                                                                                  |   | -           | _                                                                            |          |                      | į     | ł   | <b>-</b> |                                                                            | . {                                                                | 3                                                                                                    | .                                                                                    | 1                                                                           | <b>•</b> ¬       |                                      | 92             | 11                       | <del> </del>                                     | 28     | -                                                |

|   |             | 1001 =<br>LKB MSG                |         | † | A A SE   | denti | 8 tr | 63 1                  | All codes used to<br>identify 63 LKB over-<br>lays<br>(EOM = 001111 Not<br>Used) |   | <del></del> | 000000 to 001001<br>010000 to 011001<br>100000 to 101001<br>110000 to 110100 | 8888     | 8888                 | 00100 |     | 1        | 11111                                                                      | 081c<br>081c<br>081c<br>081c                                       | K K K                                                                                                | 1222                                                                                 | Logic Keys 1-10<br>Logic Keys 11-20<br>Logic Keys 21-30<br>Logic Keys 31-35 | fa-manage states |                                      | 001            | LOCIC PUSHBUTTON ASSEMBL | HBUTTO                                           | N ASSE | i ğ                                              |

|   |             | 1111 =<br>CONTROL KEY<br>HESSAGE | 2 E CEX |   | Ę        | HAX   | 8    | ALWAYS 000000         |                                                                                  |   |             | 000000<br>000001<br>000010<br>000011<br>000110<br>000111                     | 85838683 |                      |       |     |          | HARD C<br>PRIORI<br>ERROR/<br>HESSAC<br>FORMAT<br>CANCEL<br>SPARE<br>SPARE | HARD COPY<br>PRIORITY/<br>HESSAGE A<br>FORMAT IN<br>SPARE<br>SPARE | HARD COPT<br>FRIORIT/PSG<br>FREDOR/RIT/PSG<br>FESSAGE ACCE<br>FORMAT INDEX<br>CANCEL OPERA'<br>SPARE | HAND COPY PRIORITY/PSC ACCEPT ESSAGE ACCEPT (MC) FORMAT INDEX CANCEL OPERATION SPARE | HH CO                                                                       | NOTE: S.         | See Note Re. Transmission on Fig. 3. | بر<br>بر<br>بر |                          | go<br>E                                          | F.     | 2                                                |

|   | •           |                                  |         | ı | ı        | ١     |      | l                     | ١                                                                                | l | l           |                                                                              | l        | l                    |       |     | l        |                                                                            | l                                                                  | I                                                                                                    | I                                                                                    | I                                                                           | 1                |                                      |                |                          |                                                  |        |                                                  |

2 8

19 61

LOGIC PUSHBUTTON ASSEMBLY

Fig. 4b CONTROL MESSAGE FORMAT IC TO DE

\*Bits 5 and 6 of Char. 7 indicate which ET DISPLAY page is selected at the time of transmission. See Fig. 3

THEMS DIAGRANS

DATA PROCESSOR LINUT OPPRATION FROM INTEGRATED CONSOLE

# 3.0 MULTI-COLORED DISPLAY INTERFACE (TENTATIVE LARGE PANEL DISPLAY INTERFACE)

Display messages for all M-C and Large Panel displays are output via a portion of the Mass Memory disk file designated as the Mass Memory Buffer Store (MMBS). This MMBS has a capacity of 16,000 words which is shared among fifteen output channels. Eleven of these output channels are assigned for M-C displays while four are reserved for Large Panel Display outputs. Display messages, or portions thereof, sent to the MMBS have destination addresses identifying the appropriate output channels and these messages are automatically routed to the displays connected to these channels at display demand rates. Each output channel contains a circulating register capable of holding two 16-word blocks of a display message and, except during block accesses from the MMBS, providing simultaneous output to all displays.

An outline of the M-C (and LP) display interface is shown in Figure 6.

The MMBS is loaded by the processor under program control by a File Command which initiates the display message output operation. Processor loading of the MMBS is by 16-word block units. Output of data from the MMBS to the circulating registers in the output channels is also by 16-word block units. Outputs to each M-C Display is by word demand from the associated circulating register containing two 16-word blocks of the display message. Transmission of display messages from all output channels can proceed simultaneously and independently except for block accesses to the MMBS which may interfere with one another or may be interfered with by processor loading of the MMBS.

Transmission of a display message to a particular M-C display will continue, subject to word demand signals from the M-C display, until the MMBS is depleted of blocks with the corresponding destination address. This may or may not be the end of the complete display message since the processor may transfer a very long display message into the MMBS in several sections to avoid occupying an excessive amount of the available MMBS storage capacity to service only one display device.

The processor is notified by a special interrupt when the MMBS is depleted of blocks for a particular display. Then, and only then, can additional blocks for that display be entered by the processor into the MMBS.

The end of a display message transmission to a particular M-C display is signified by the occurrence of an EOM character. It is a program requirement that the EOM character, when it occurs, coincide with the depletion of blocks in the MMBS for the associated display. Otherwise, an error condition will occur causing an interrupt to be generated.

#### 3.1 Data Transmission Rate

M-C display data transmission from the MMBS output channel to the display console is by word demand at a maximum rate of approximately 180 words per second. Data transmission in this interface is one way only, no messages from the M-C Display being transmitted to the processor via this route. Control messages for the M-C display are routed through the ET and Control interface.

In most instances the Mass Memory Buffer will supply a word to the M-C Display within a maximum of 5.6 milliseconds after receipt of a word demand signal from the console. Words are transmitted bit serially at a rate of  $356\pm10\%$  kilobits/sec. as determined by the MMBS clock. The least significant bit of the most significant character is transmitted first as in the ET and control interface.

Each character is processed by the M-C display device in approximately 1 millisecond. Vectors require a maximum of 10 milliseconds. If a character or vector is to be displayed in a color different from that of the preceding transmitted symbol, an additional 100 milliseconds is required by the device in order to effect the color changes.

#### 3.2 M-C Message Formats

M-C messages from the DPSS to the console are of arbitrary length and are terminated by an EOM character. When the EOM character is received by the console, the transmission is terminated and the M-C display image is processed.

The message formats applicable to M-C message transmissions are shown in Figure 7.

Three types of word formats are used in the M-C message, Reference Slide Selection Words, M-C Character Words, and M-C Line Coordinate Words. Each type of word is headed by a control character identifying the word and determining the color of the printed character or line. The remainder of the word identifies the reference slide or contains coordinate and character information.

In order to display a line it is necessary to send two words in sequence to the console, one designating the initial coordinate, the second designating the final coordinate. Color designation is repeated in both control characters. If two different colors are designated, the second color only is recognized and implemented by the M-C display.

The reference slide selection word contains the selected slide number in characters 0, 1 and 2. The first bit of character 2 has numerical weight 256; the 4th bit of character 1 has numerical weight 128, etc. If more than one slide selection command occurs in a message, only the first such command will be honored by the console.

The character designation word contains the designated alpha-numeric character in character 6. X and Y coordinates of the character display position are contained in characters 5, 4, and 3 and characters 2, 1, 0, respectively. X and Y position information is in binary form with bit values as indicated in Figure 7.

Line coordinates are sent in character positions identical to those described above for character coordinates and are also designated in binary form.

#### 3.3 Transmission Mode

The following signal lines are used in transfering information to the M-C display:

- a. "Word Transfer Order" MMBS originated signal transmitted concurrent with data and clock signals.