# PROCESS COMPUTER

GENERAL 🍪 ELECTRIC

UTILITY AND PROCESS AUTOMATION

PRODUCTS DEPARTMENT

PHOENIX. ARIZONA

REQN: 282-L3285

The

# Process Computer System

I/O BUFFER

PERIPHERALS

BULK MEMORY

CONSOLES

This instruction book is provided as a basic source of technical information on this system. If problems arise in installation, operation, or maintenance that are not covered in these instructions, the matter should be referred to General Electric Company, Process Computer Products Department, Phoenix, Arizona, U.S.A. Attn. Technical Publications.

General Electric reserves the right to make changes in the equipment or software, and its characteristics or functions, at any time without notice.

# 4822A CSU BASIC I/O BUFFER

### TABLE OF CONTENTS

#### INSTRUCTIONS

OPR - Operate

JCB - Jump If Channel Busy

JDR - Jump If Data Ready

IN - Input

OUT - Output

JNE - Jump If No Error

ABT - Abort

CHARACTER CODING

LOGIC DESCRIPTION

Instruction Decoding

I/O Data Gates

Parity Check And Generate

Tests And Alarms

CLOCK GENERATOR AND COUNTDOWN

Clock Generator

Countdown Circuits

#### 4822A CSU BASIC I/O BUFFER

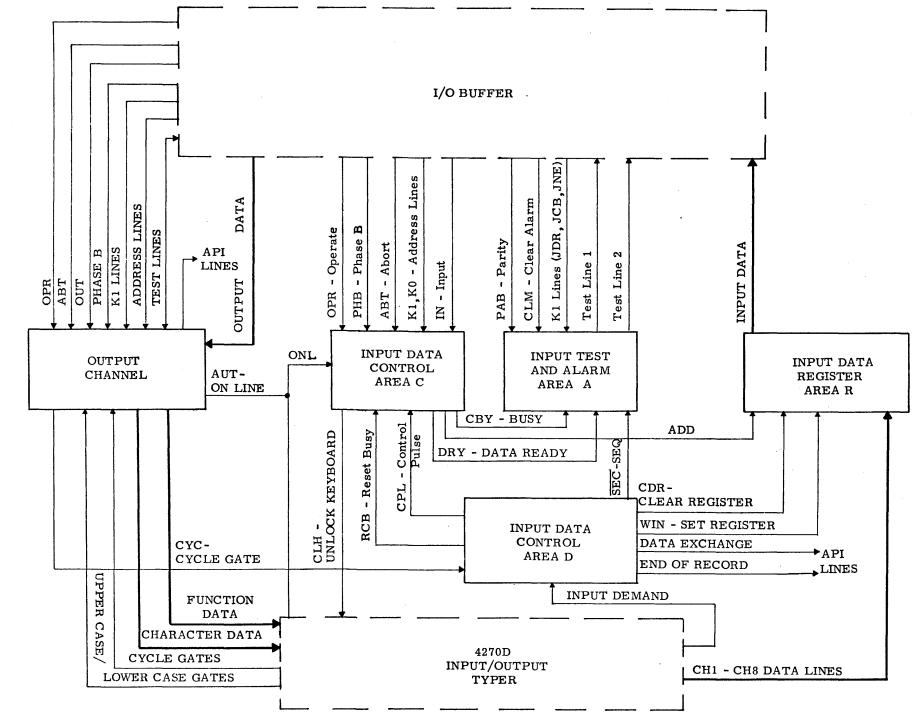

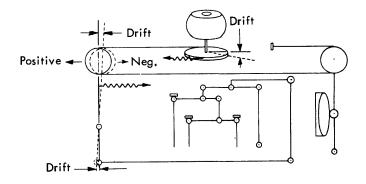

The interfaces between the Arithmetic Unit and a GE-PAC\* 4010 computer system's peripheral devices and communications channels are provided by the I/O Buffer. The I/O Buffer consists of a basic buffer module, one control (or drive) module for each input channel, and one control module for each output channel.

The basic buffer contains data control logic, test and alarm logic, and a parity check/generate circuit. The control modules contain logic and circuitry necessary to operate the attached peripheral device or to communicate through the communications channels. Each control module incorporates a holding register which stores each data character while input channels await access to the AU, or while awaiting access to output devices or channels.

This publication describes both the 4800AS14 Standard CSU Basic I/O Buffer and the 4822ASID Optional CSU I/O Buffer. One of these two basic buffers will be contained in each system. The 4800AS14 Basic Buffer is prewired to accommodate the most common used complement of peripheral drives. The 4822ASID Basic Buffer is wired unique for each system, permitting a wider range of peripheral drives to be implemented. Logic for both of these basic buffers is contained in 70C180909.

This publication provides generalized information which applies to the complete I/O Buffer, and the theory of operation of the basic I/O Buffer. The theory of operation for the control modules (4820BSXX) is provided in the publications which follow this basic description. Maintenance information for the I/O Buffer is included in the publications covering the peripheral devices and communications channels, in the Computer Maintenance Manual.

#### **INSTRUCTIONS**

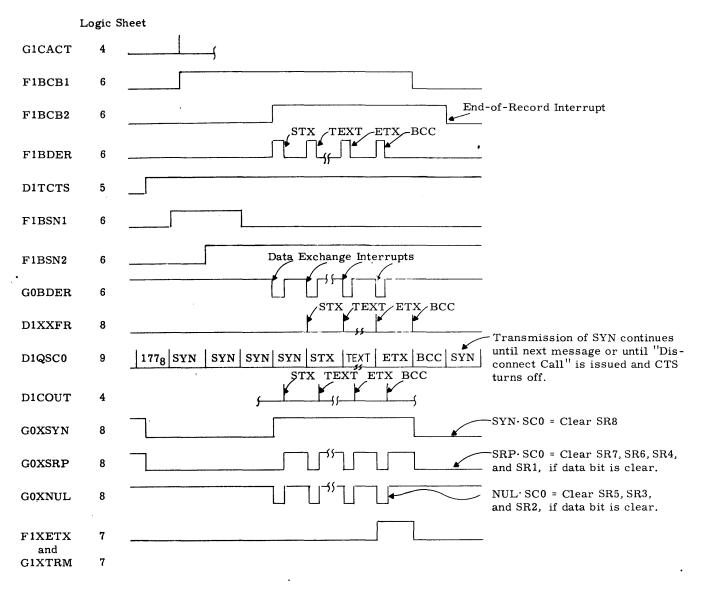

In normal on-line operation, virtually all data transfers through the I/O Buffer are accomplished by the TIM/TOM feature. Once the program has set up a TIM or TOM table, configured the control words in the appropriate API response addresses, and set a buffer channel busy, data records are exchanged via TIM/TOM, with no further interference with the running program, and using very little AU time.

When the control module determines that the final character in a record has been transferred, or when a TIM table becomes full or a TOM table becomes empty, an end-of-record API is generated for the channel, which informs the program that the channel is ready for the next operation. Refer to the description of the Arithmetic Unit in Volume I of this bookset for a detailed description of TIM/TOM operation.

In addition to the TIM/TOM feature, seven GEN 2 instructions affect the I/O Buffer as described in the

following paragraphs. Refer to the AU Theory description in Volume I for a more detailed description of these instructions.

#### **OPR - Operate**

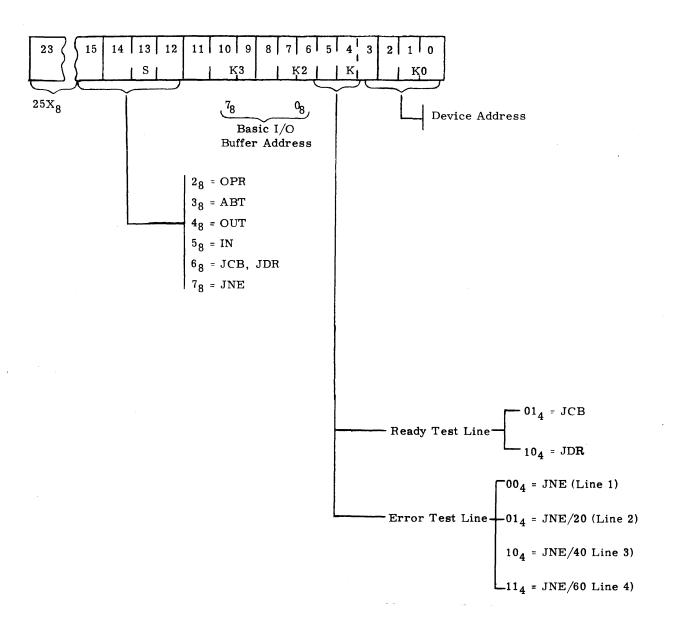

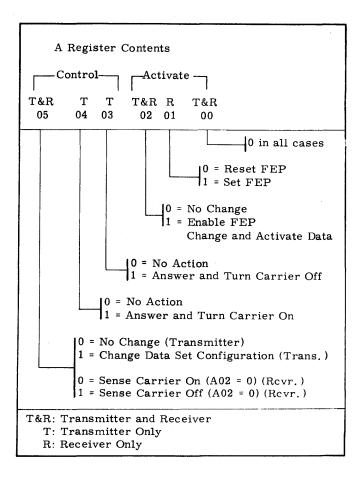

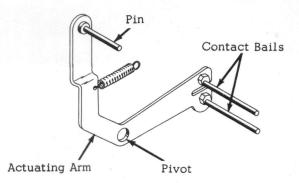

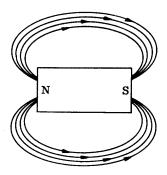

OPR sets the addressed channel (Fig. 1) busy (not ready) and may transfer the contents of the 7 least significant bits of the A Register to the addressed control module. If transferred, the A Register data is decoded to determine a required channel configuration or action to be taken. The A Register remains unchanged. If set, the channel error flip-flop is cleared.

#### JCB - Jump If Channel Busy

If executed while the addressed channel (Fig. 1) is busy, program control "jumps" to the second sequential location. If the addressed channel is not busy, program control is transferred to next sequential location (no jump). A channel is normally busy when a data record transfer is in progress, when an input demand signal from the device or channel is present, and, in some cases, when the companion channel in a dual (input/output) channel is busy (as for an I/O Typer). The K1 bits of the instruction word are decoded in the control module to differentiate between JCB and JDR.

#### JDR - Jump If Data Ready

If, when JDR is executed, the addressed channel (Fig. 1) is busy and is holding a data character for transfer to the AU (input channels), or is ready to accept a data character from the AU (output channels), program control is transferred to the second sequential location. If the channel is not ready to transfer a data character to, or from, the AU, program control is transferred to the next sequential location. The K1 bits of the instruction word are decoded in the control module to differentiate between JDR and JCB.

#### IN - Input

IN transfers a data character from the addressed input channel to the A Register in the AU. The data is right justified (12 bits, max.) and unused bits of A are set to zero. IN resets the data ready test line from the addressed channel. The TIM function has the same effect except that the character is transferred to core through the B Register, leaving the A Register undisturbed.

#### OUT - Output

OUT transfers the contents of the A Register in the AU (12 bits, max.) to the addressed channel. OUT resets the data ready test line from the addressed channel. The TOM function has the same effect except that the character is transferred from core through the B Register, leaving the A Register undisturbed.

<sup>\*</sup> Registered Trademark of General Electric Company

Fig. 1 GEN 2 Instruction Word Format

#### JNE - Jump If No Error

If, when JNE is executed, the error test line from the addressed channel indicates no error, program control is transferred to the second sequential location. If the test line indicates that there is an error, program control is transferred to the next sequential location. Bits 5 and 4 of the instruction word (K1) are decoded in the control modules to differentiate between up to four types of error conditions (see Fig. 1).

These conditions are defined in the descriptions of the control (drive) modules which follow this publication.

#### ABT - Abort

ABT initializes the addressed channel, The busy, data ready, and error test lines are all reset. Pushing the ON/INIT pushbutton on the Programming and Maintenance Console while the console is enabled and in MANual mode, (hardware initialize) has the same effect as ABT on all channels.

#### **CHARACTER CODING**

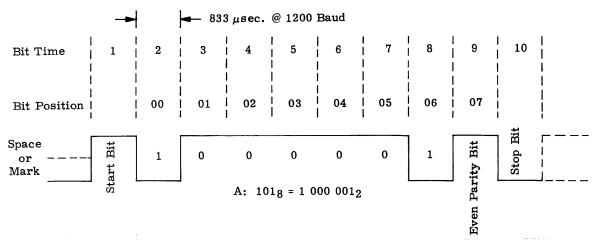

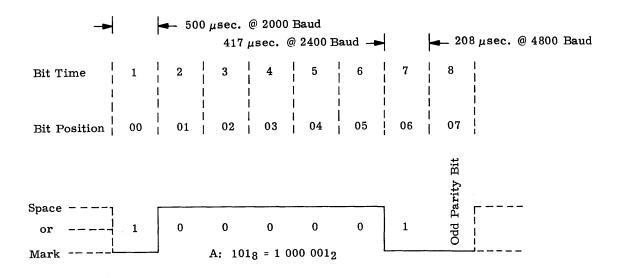

The characters exchanged between the Arithmetic Unit and the devices and communications channels are normally coded or decoded by the program to determine their meaning. For example, if the program wants to print the letter "A" on a teletypewriter, a line printer, or on a video display, it may execute OUT while the A Register contains the code 1018 (on-line programs normally use the TOM function). The device attached to the addressed channel decodes the 1018 bit pattern to determine that "A" is to be printed or displayed.

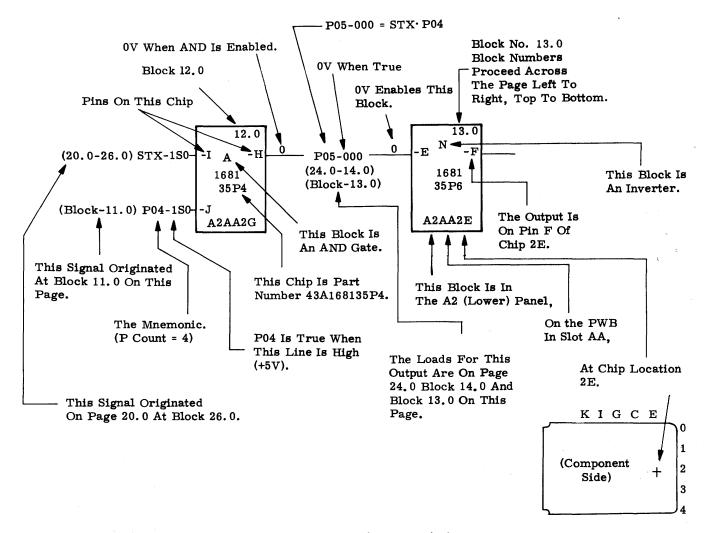

In addition to graphic character coding, such as for the letter "A", some channels employ control character coding. Control characters are used to cause predetermined responses in the devices or terminals receiving the character. For example, STX (002<sub>8</sub>) indicates the start of text in paper tape records and in some communications channel messages. STX indicates that all of the characters between STX and ETX (003<sub>8</sub>) are in the text of the message.

In some channels, the control character codes cause some specific action by the attached device or by the I/O Buffer control module. These codes and the responses to them are defined in the descriptions of the control modules which follow this publication.

Tables 1 and 2 list the character codes in the two principal formats used with GE-PAC equipment. The first table is a partial list of USASCII codes and, in general, is applicable to teletypewriters, line printers, DATANET\* Video Display Subsystems, and the communications channels (ACD and SCU). The second table applies to Fixed Carriage Typers. Refer to the control (drive) module descriptions for further definition of the codes and formats used.

\*Trademark of Honeywell Information Systems, Inc.

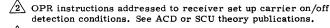

#### LOGIC DESCRIPTION

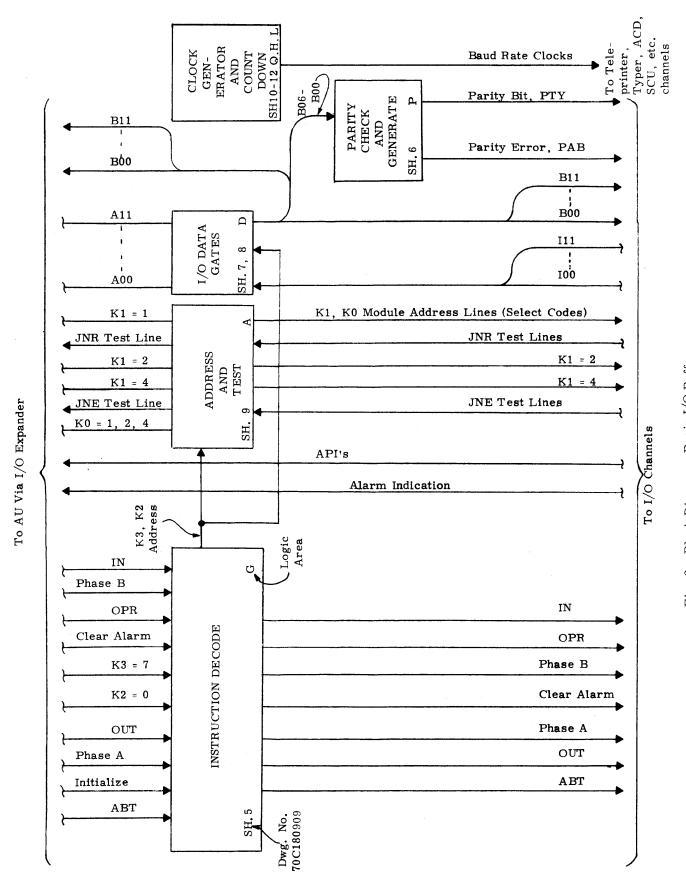

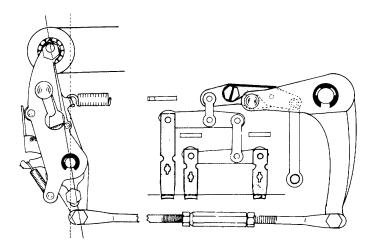

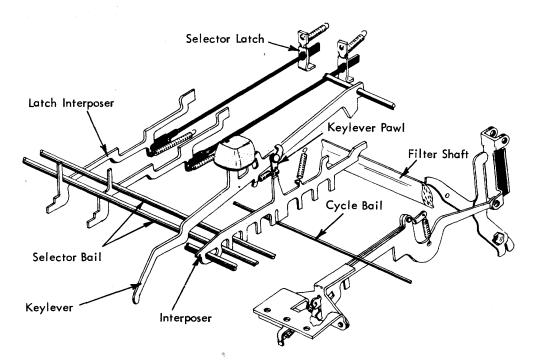

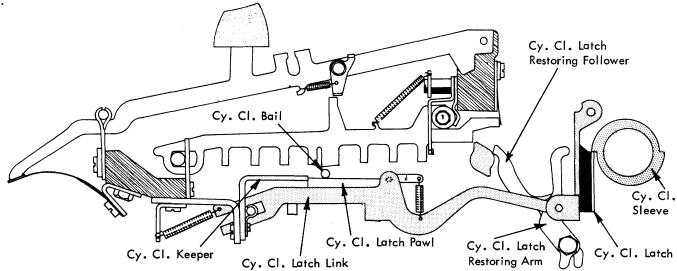

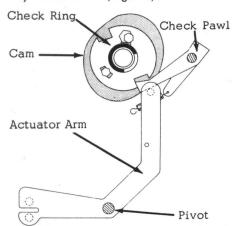

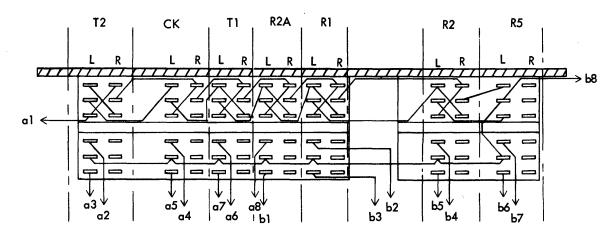

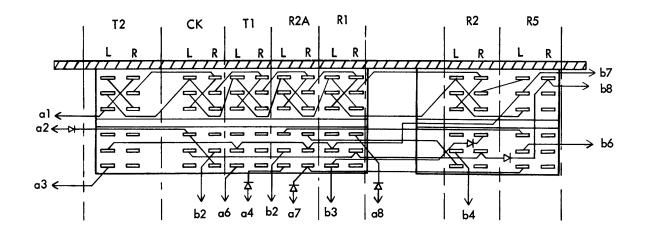

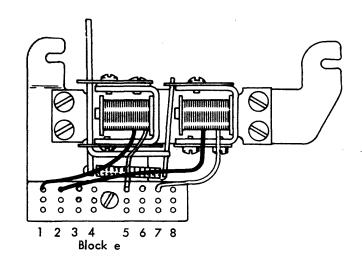

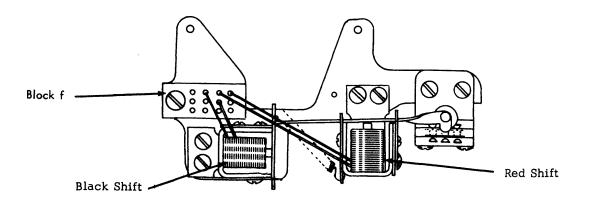

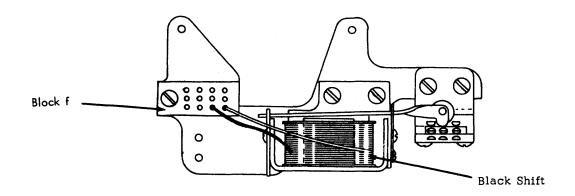

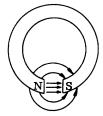

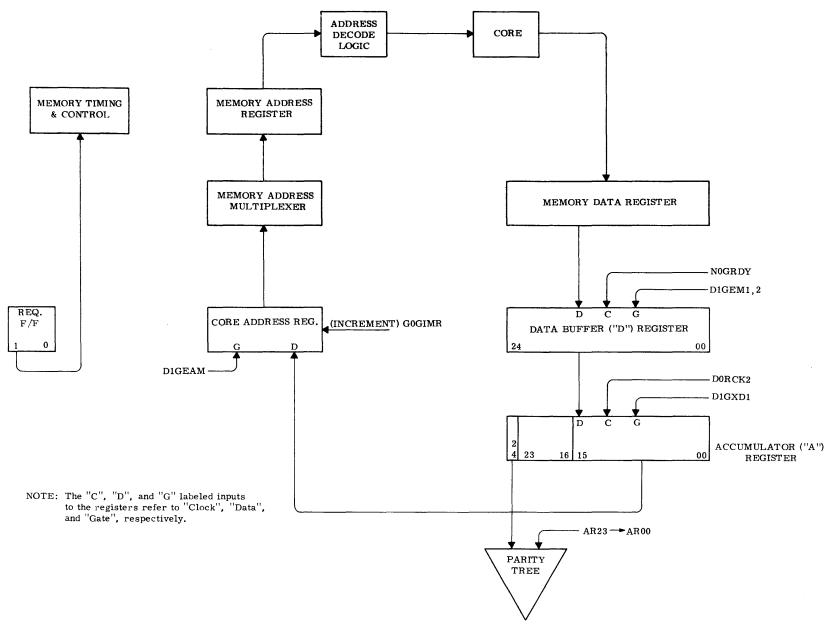

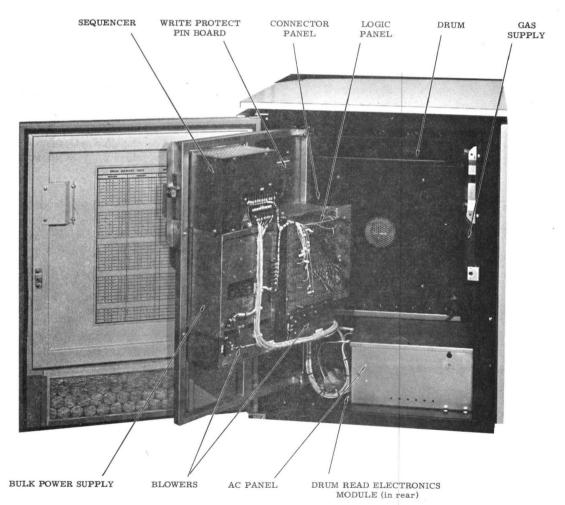

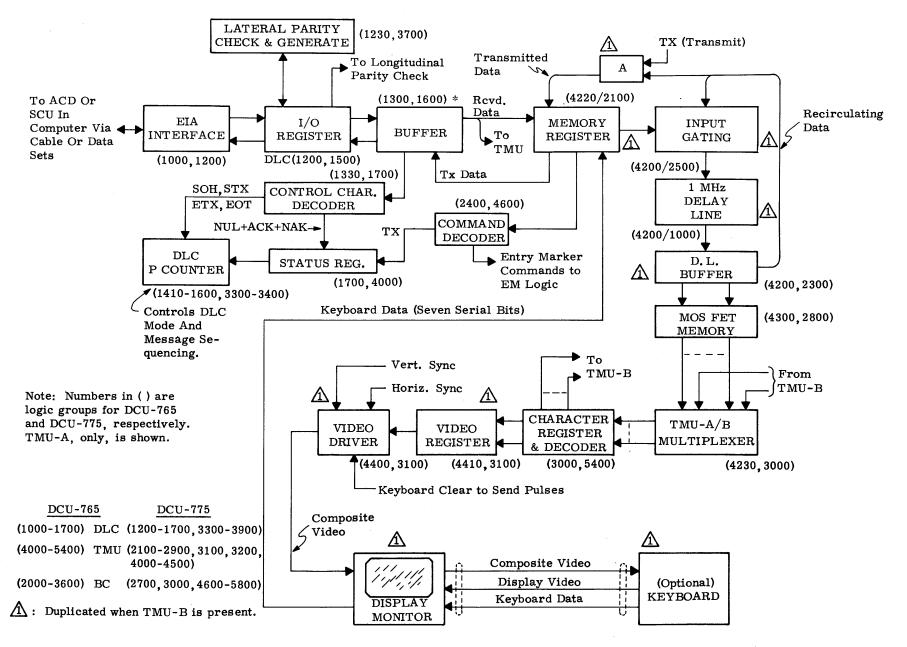

The basic CSU I/O Buffer logic appears on GE drawing number 70C180909. Fig. 2 is a block diagram of the basic buffer with references to sheet numbers on the logic drawing. The basic buffer is comprised of four printed wire boards: PTCA1, 2-PBCJ1's, and PJBA1. These boards are located in slots 13 through 16, respectively, in the CSU M panel. The control (drive) module PWB's are located in slots 17 through 32 of the M panel. Only those control module boards required for implemented devices or channels are installed in any CSU.

The interface between the I/O Buffer and the Arithmetic Unit is through the 4078 I/O Expander. This interface is a high speed GEN 2 interface. The K3 bits in all buffer addresses equal 78, the basic buffer address is specified by (K2), and the device/channel addresses are specified by the K1 and K0 bits as illustrated on Fig. 1. To trace signals between the basic I/O Buffer and the AU, refer to the I/O Expander logic drawing, 70C180899.

The interface between the I/O Buffer and the attached devices is depicted on sheet four of the basic buffer logic, 70C180909, and with greater detail on an interface summary sheet on each of the logic drawings for the control modules. All of the attached devices are plug-connected to jacks on the C panel as indicated on the table on sheet 4 of the - 909 logic.

The wiring between the basic buffer boards and 16 control module slots requires far more wire-wrap connections than can be accommodated by the back panel pins on the boards containing the basic buffer logic. The PJBA1 board in slot 16 is a jumper board which distributes the signals as shown on the slot 16 fan-out illustration at the right hand edge of sheet 4 of the - 909 logic. Connectors A through K on slot 16 provide adequate wire-wrap pins to accommodate the wiring to the control modules.

#### Instruction Decoding

The GEN 2 instruction decoding logic appears on sheet 5 of the - 909 logic. The purpose of this logic is to distribute GEN 2 instruction pulses to the control modules when the basic buffer is addressed.

Jumper pins are provided on the two PBCJ1 boards to select the basic buffer addresses. References in this description to logic terms K3 and K2, infer K3, and K2 are "true" when the buffer is addressed. Decoding of the six GEN 2 instructions is as follows:

OPR - When a GEN 2 instruction with S=2 is decoded in the AU, the EXM0XGS2 signal from the expander goes "true", making N1GOPR on sheet 5 "true". If the basic buffer was addressed, driver D0GOPR is enabled, applying a zero volt OPR pulse to the control modules.

3

$D0GOPR = K2 \cdot K3 \cdot OPR$

| Octal |                        |                      | Octal |                  |            |

|-------|------------------------|----------------------|-------|------------------|------------|

| Code  | Char.                  | <u>Definition</u>    | Code  | Char.            | Definition |

| 000   | NUL                    | Null                 | 063   | 3                |            |

| 001   | SOH                    | Start of Header      | 064   | 4                |            |

| 002   | STX                    | Start of Text        | 065   | 5                |            |

| 003   | ETX                    | End of Text          | 066   | 6                |            |

| 004   | EOT                    | End of Transmission  | 067   | 7                |            |

| 005   | ENQ                    | Enquiry              | 070   | 8                |            |

| 006   | ACK                    | Acknowledge          | 071   | 9                |            |

| 007   | $\mathtt{BEL}$         | Bell                 | 072   | :                |            |

| 010   | BS                     | Back Space           | 073   | ;                | •          |

| 011   | HT                     | Horizontal Tab.      | 074   | <                |            |

| 012   | $_{ m LF}$             | Line Feed            | 075   | =                |            |

| 013   | VT                     | Vertical Tab.        | 076   | >                |            |

| 014   | $\mathbf{F}\mathbf{F}$ | Form Feed            | 077   | <b>&gt;</b>      |            |

| 015   | CR                     | Carriage Return      | 100   | @                |            |

| 016   | SO                     | Shift Out            | 101   | A                |            |

| 017   | SI                     | Shift In             | 102   | В                |            |

| 020   | DLE                    | Data Link Escape     | 103   | C                |            |

| 021   | DC1                    | Device Control 1     | 104   | D                |            |

| 022   | DC2                    | Device Control 2     | 105   | Ē                |            |

| 023   | DC3                    | Device Control 3     | 106   | ${f F}$          |            |

| 024   | DC4                    | Device Control 4     | 107   | G                |            |

| 025   | NAK                    | Negative Acknowledge | 110   | H                |            |

| 026   | SYN                    | Synchronize          | 111   | I                |            |

| 027   | ETB                    | End of Trans. Block  | 112   | J                |            |

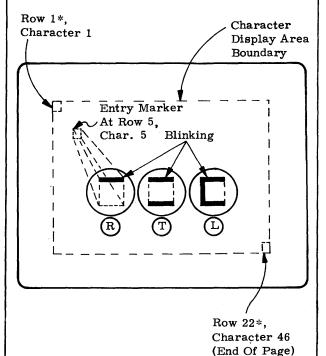

| 031   | EM                     | Entry Marker         | 113   | к                |            |

| 032   | SUB                    | Substitute           | 114   | L                |            |

| 033   | ESC                    | Escape               | 115   | M                | · ·        |

| 036   | RS                     | Record Separation    | 116   | N                |            |

| 040   | SP                     | Space (graphic)      | 117   | 0                |            |

| 041   | · ·                    |                      | 120   | P                |            |

| 042   | 11                     |                      | 121   | Q                |            |

| 043   | #                      |                      | 122   | R                |            |

| 044   | \$                     |                      | 123   | S                |            |

| 045   | %                      |                      | 124   | T                |            |

| 046   | &                      |                      | 125   | ${f U}$          |            |

| 047   | •                      |                      | 126   | v                |            |

| 050   | (                      |                      | 127   | $\mathbf{w}$     |            |

| 051   | )                      |                      | 130   | X                |            |

| 052   | *                      |                      | 131   | Y                |            |

| 053   | +                      |                      | 132   | $\boldsymbol{z}$ |            |

| 054   | •                      |                      | 133   | . [              |            |

| 055   | -                      |                      | 134   | •                |            |

| 056   |                        |                      | 135   | 1`               |            |

| 057   | /                      |                      | 136   | Á                |            |

| 060   | Ó                      |                      | 137   |                  |            |

| 061   | 1                      |                      | 177   | DEL              | Delete     |

| 062   | 2                      |                      |       |                  |            |

| 1     |                        |                      |       |                  |            |

|       |                        |                      |       |                  |            |

|       |                        |                      |       |                  |            |

|       | 2 M 10 C 20 C          |                      |       |                  |            |

Table 1 USASCII Codes

| 000<br>001<br>002<br>003<br>004 | 0<br>1<br>2 | 030 | H       |     |         |

|---------------------------------|-------------|-----|---------|-----|---------|

| 002<br>003                      | 1           | 201 |         | 060 | +       |

| 003                             | 2           | 031 | I       | 061 | /       |

|                                 | - 1         | 032 | &       | 062 | S       |

| 004                             | 3           | 033 | •       | 063 | т       |

|                                 | 4           | 034 | J       | 064 | U       |

| 005                             | 5           | 035 | (       | 065 | v       |

| 006                             | 6           | 036 | <       | 066 | w       |

| 007                             | 7           | 037 |         | 067 | X       |

| 010                             | 8           | 040 | <b></b> | 070 | Y       |

| 011                             | 9           | 041 | J       | 071 | Z       |

| 012                             | [           | 042 | K       | 072 | ← .     |

| 013                             | #           | 043 | L       | 073 | ,       |

| 014                             | @           | 044 | M       | 074 | %       |

| 015                             | :           | 045 | N       | 075 | =       |

| 016                             | >           | 046 | О       | 076 | . "     |

| 017                             | ?           | 047 | P       | 077 | !       |

| 020                             | Space       | 050 | Q       | 100 | CR      |

| 021                             | A           | 051 | R       | 120 | DC4     |

| 022                             | В           | 052 | -       | 130 | Backspa |

| 023                             | C           | 053 | \$      | 140 | HT      |

| 024                             | D           | 054 | *       | 150 | Line Fe |

| 025                             | E           | 055 | )       | 160 | BLK     |

| 026                             | F           | 056 | ;       | 161 | RED     |

| 027                             | G           | 057 | 1       | 171 | STX     |

|                                 |             |     |         | 177 | DEL     |

DC4: Terminate output message

STX: Enable input operation

HT: Horizontal Tab

DEL: Delete

BLK: Print black

Table 2 Fixed Carriage Typer Codes

Fig. 2 Block Diagram, Basic I/O Buffer

- JCB, JDR, and JNE The S bits for these instructions are decoded in the AU and are used in the expander to enable test line gates which transfer the status of the buffer test lines to the AU when the instructions are executed. The K1 and K0 bits are decoded in the basic buffer and the control modules as described under "Tests And Alarms".

- TIM or IN When a GEN 2 instruction with S = 5 is decoded in the AU, the EXMOXGS5 signal from the expander goes "true", making N1GGIN on sheet 5 "true". If the basic buffer was addressed, driver D0GGIN is enabled, producing a positive going pulse at the output of D1GGIN, which is applied to the control modules.

$D0GGIN = K2 \cdot K3 \cdot GIN$

TOM or OUT - When a GEN 2 instruction with S = 4 is decoded in the AU, the EXMOXS4 signal from the expander goes "true", making N1GOUT on sheet 5 "true". If the basic buffer was addressed, driver D0GOUT is enabled, producing a zero volt pulse, which is applied to the control modules.

$D0GOUT = OUT \cdot K2 \cdot K3$

ABT or Initialize - When a GEN 2 instruction with S = 3 is decoded in the AU, the EXMOXS3 signal from the expander goes "true", making N1GABT on sheet 5 "true". If the basic buffer was addressed, driver D0GABT is enabled, producing a positive pulse at the output of D1GABT, which is applied to the control modules. D1GABT is also made "true" when the ON/INIT pushbutton on the Programming and Maintenance Console is pushed while the console is enabled and in MANual mode, which makes EXMOCINI "true".

DOGABT = ABT · PHA· K2· K3

G1GPHA = GEN 2 phase A pulse

#### I/O Data Gates

The I/O data gates, depicted on sheets 7 and 8 of the -909 logic, control the flow of data between the AU and the I/O Buffer and between the attached devices and the I/O Buffer. Logic is provided to control up to 12 data bits plus a parity bit. Most devices or channels use only 7 data bits plus a parity bit. Only the card reader uses gates I07 through I11, or the full 12 bits.

Data bits are transferred from the AU to the output control modules when either an OPR or OUT instruction is executed (or a TOM transfer is effected). The seventh bit, bit 06, is used in the following example.

The operation is the same for all other bits, 00 through 11:

If bit 06 of the A Register is set (or the B Register if TOM) while OPR or OUT is executed, EXMOXA06 from the expander will be 'true'.

This makes G1DO06 'true".

G1DO06 = IN + A06

Input gate G1DI06 will have a "true" output because OPR or OUT has enabled G0GBLB.

G1DI06 = BLB + Input bit 06

GOGBLB = OPR + OUT (sheet 5)

Driver D0DB06 is enabled, applying a negative going bit 06 pulse to all output control modules. The output data character will be gated into the holding register of the addressed control module.

$D0DB06 = K2 \cdot K3 \cdot O06 \cdot I06$

Data bits are transferred from input control modules to the AU when IN is executed (or a TIM transfer is effected). The seventh bit, bit 06, is used in the following example. The operation is the same for all other bits, 00 through 11:

• If bit 06 of the holding register in the addressed control module is set while IN is executed, the bit 06 line from that module to gate G1DI06 (one of 7 input lines) will be "true" (zero volts). Since neither OPR nor OUT are being executed, G1DI06 can be "true" only if one of the input lines is "true".

G1DI06 = BLB + Input bit 06

GOGBLB = OPR + OUT

Output gate G1DO06 will have a "true" output because IN is being executed.

G1DO06 = IN + A06

• Driver D0DB06 is enabled, applying a negative going bit 06 pulse to EXG1ZD06 in the expander, from which it is transferred to the A (or B) Register in the AU.

D0DB06 = K2 · K3 · O06 · I06

#### **Parity Check And Generate**

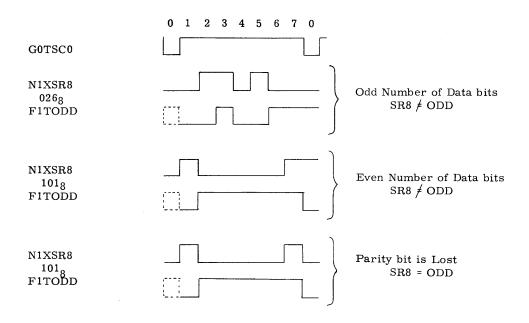

As has been shown, the D0DBxx drivers are enabled, according to the data, whenever a data character is being transferred to the control modules (output) or to the AU (input). This permits the use of the same logic to generate a parity bit for each output character and to check parity on each input character.

Since no parity bit is read by the card reader, only the seven least significant bits plus the parity bit are used for the parity check. The parity check error signal, DODPAB, is applied to all input control modules, but only those associated with a channel which read a parity bit use the error signal.

The seven least significant output bits are used to generate an even output parity bit for all output characters. Only those control modules associated with output devices or channels which punch and/or check the parity bit, supply the parity bit to the attached device.

An analysis of the parity check and generate logic on sheet 6 of the -909 logic drawing will show that, if an even number of bits are set, of bits D0B00 through D0B06 and the input parity bit D0DPTY, the output driver D0PPAB will be enabled. If an odd number of bits are set, D0PPAB is disabled.

Note that for an output data transfer, D0DPTY (sheet 8) is always enabled because the output signal line to gate G1DOPT is grounded, holding the OPT output perpetually "true". The output of driver D0DPTY then, is representative of parity bits from input channels only. D0DPTY will always be "true" for an output character transfer, and will be "true" on input character transfers only when the input parity bit is "true".

$D0DPTY = K2 \cdot K3 \cdot OPT \cdot PTY$

G1DPTY = BLB + Input parity bit

GOGBLB = OPR + OUT

As an example of even parity generation, assume that when OUT is executed, the A Register in the AU contains 1028; an odd number of 1-bits. DODPAB, then, is enabled (0V) because the DODBxx bits are odd and DODPTY is "true", making the total of eight parity circuit inputs, even. The output parity bit driver, D1DPDO, is enabled (0V) in this case, making an even number of 1-bits (0V) on the lines to the output control modules.

As an example of parity checking, assume that when IN is executed, the holding register in the addressed control module contains  $102_8$ , an odd number of 1-bits, but that due to some malfunction, the parity bit input line to G1DPTY is "false". Of the eight parity circuit inputs then, there is an odd number of 1-bits, and D0DPAB is disabled (+3.6V). The PAB signal sets the parity error flip-flop in the addressed control module. The I/O Buffer alarm light on the Programming and Maintenance Console will be illuminated and the error condition may be detected by executing JNE.

#### Tests And Alarms

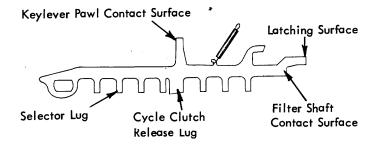

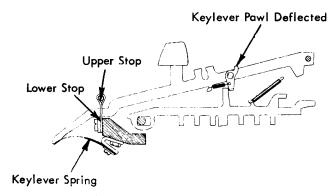

As is indicated on Fig. 1, the K1 bits in the GEN 2 instruction words are used to differentiate between

JCB and JDR, and both the K1 and K0 bits are used to differentiate between four possible JNE test conditions. The logic within the control modules decodes the K1 and K0 bits, both to determine when a module has been addressed and to differentiate between these test and alarm instructions.

The K1 and K0 bits are routed through logic in the basic I/O Buffer as shown on sheet 9 of the -909 logic drawing. In addition to providing signal drive and distribution, this logic makes all of the K1/K0 outputs "true" when the hardware initialize signal is "true". This is to cause all control modules to appear to be addressed when the initialize signal is present.

The JNE and JNR test line logic is also depicted on sheet 9 of the -909 logic. When the outpus of G1AJNE or G1AJNR are at 0V during the execution of JNE or JNR, respectively, program control in the AU does not jump, but is transferred to the next sequential location.

In the case of a JNE instruction, if no alarm or error condition exists in the addressed control module, one of the 16 input lines to G1ALAL and G1AMAL will go to 0V. G1AJNE will then be enabled (0V) during execution of the instruction, holding the test line in the "no jump" state. If an error or alarm condition does exist, G1AJNE will be disabled (+3.6V), causing the program sequence to "jump".

G1AJNE (no jump) = LAL · GK2 + MAL · GK2

NODGK2 = K3' K2 (basic buffer addressed)

If, in the case of a JCB instruction, the addressed channel is not busy; or in the case of a JNR instruction the addressed channel is not ready for data exchange, one of the 16 input lines to G1ALNR and G1AMNR will go to 0V. G1AJNR will then be enabled (0V) during execution of the instruction, holding the test line in the "no jump" state. If the addressed channel is busy or ready for data exchange, G1AJNR will be disabled (+3.6V), causing the program sequence to jump.

$\overline{G1AJNR}$  (no jump) = LNR  $\cdot \overline{GK2}$  + MNR  $\cdot \overline{GK2}$

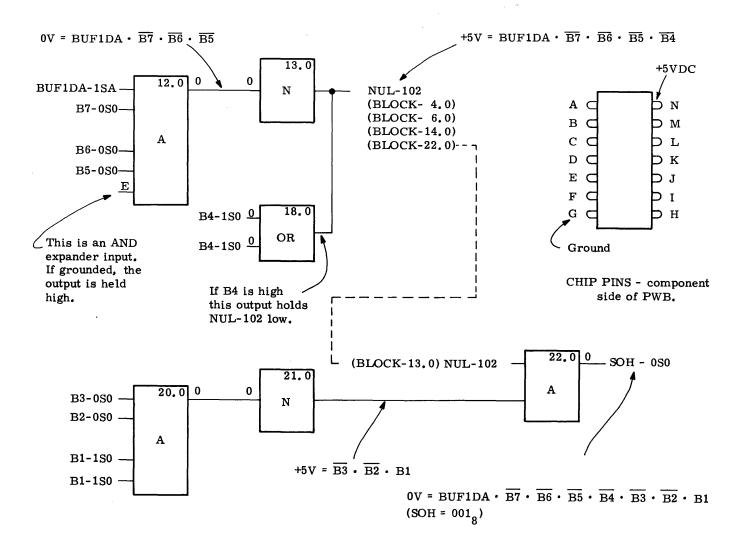

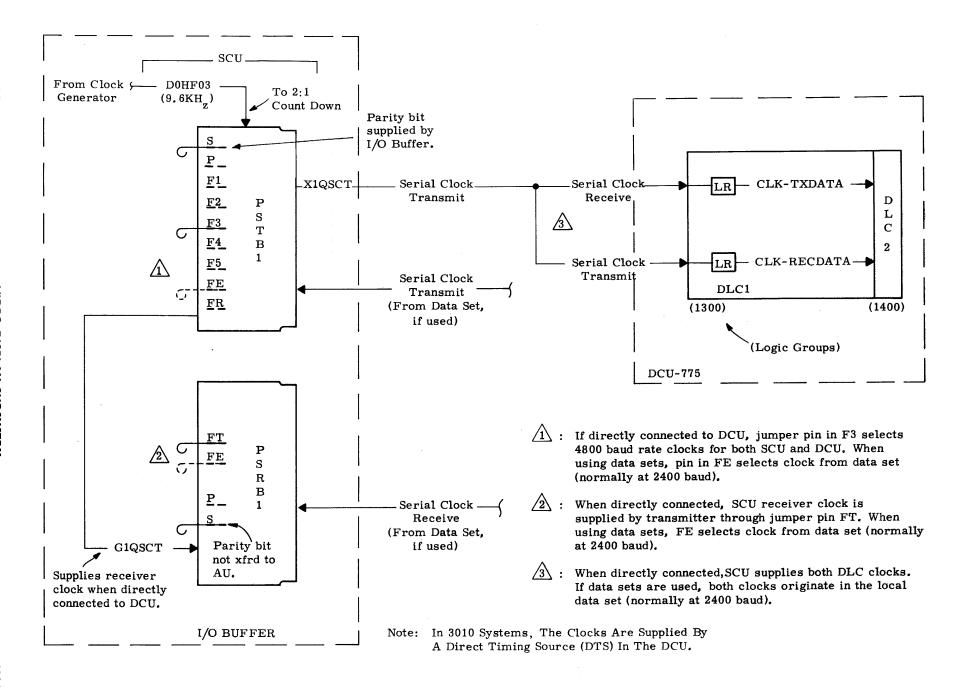

# CLOCK GENERATOR AND COUNTDOWN

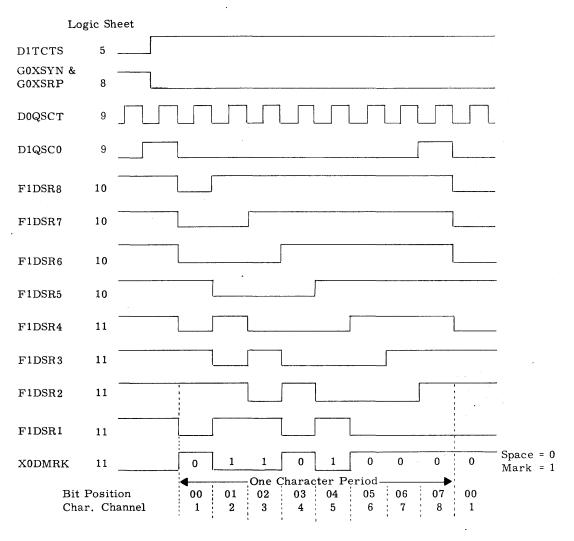

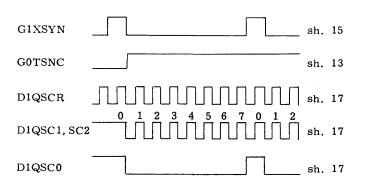

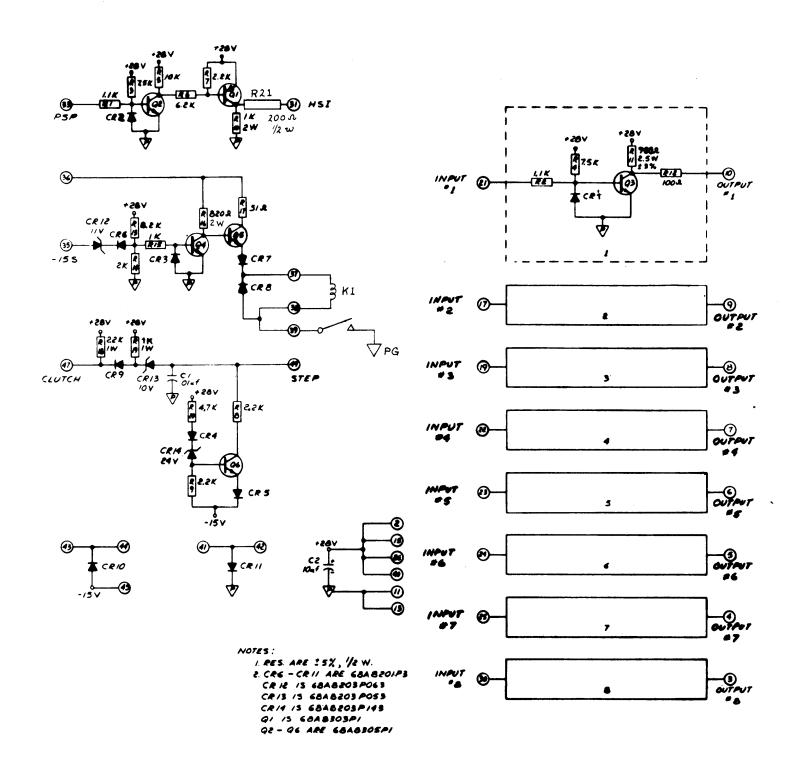

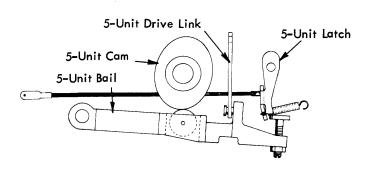

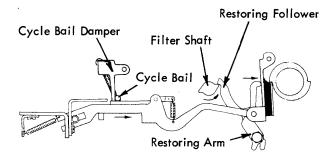

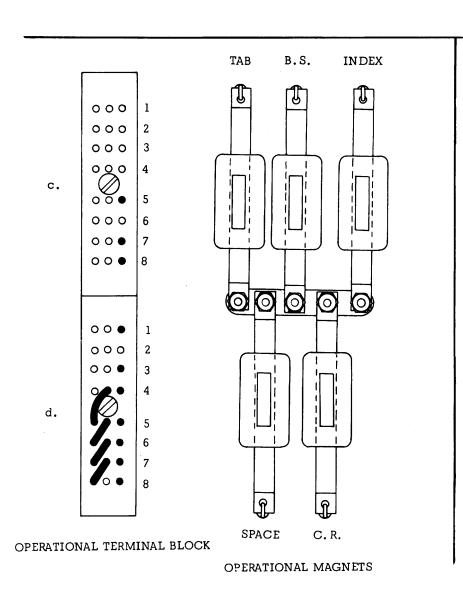

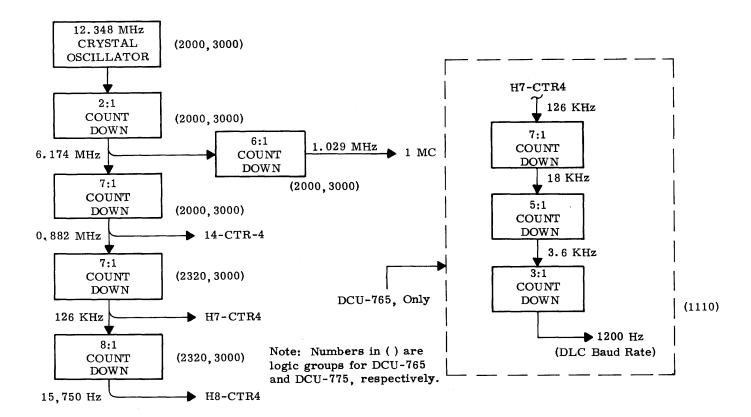

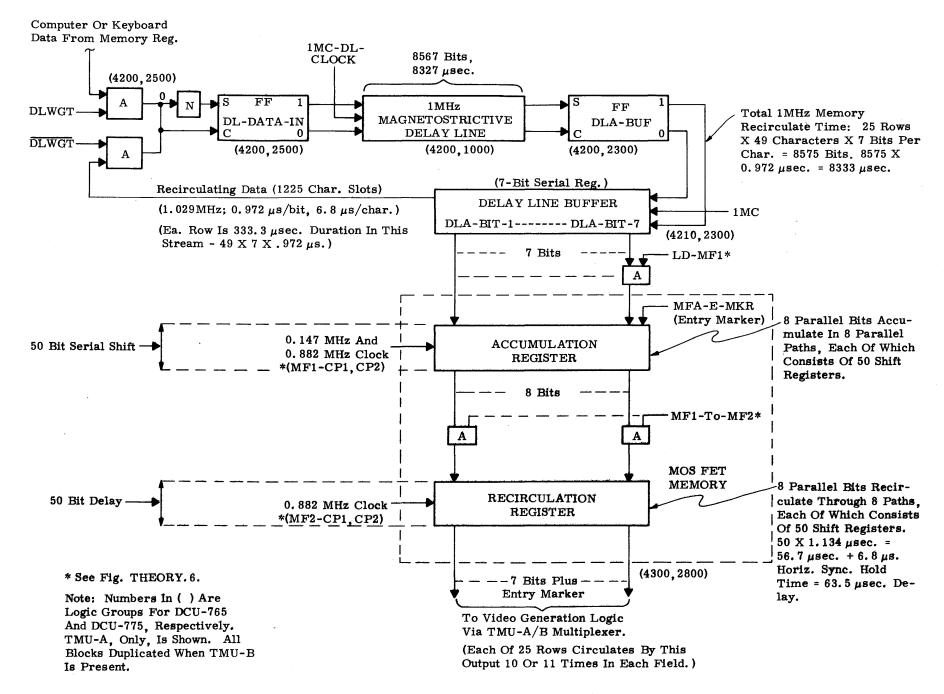

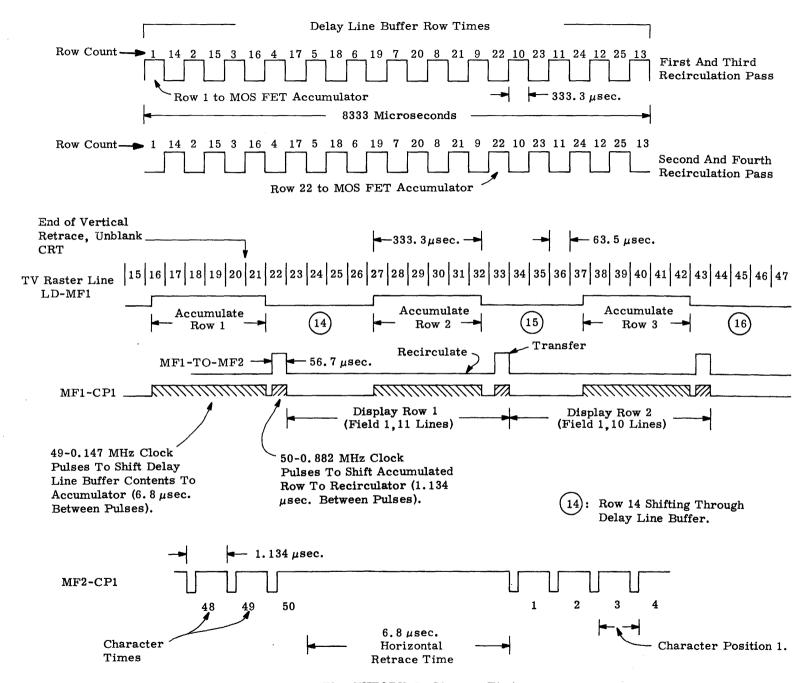

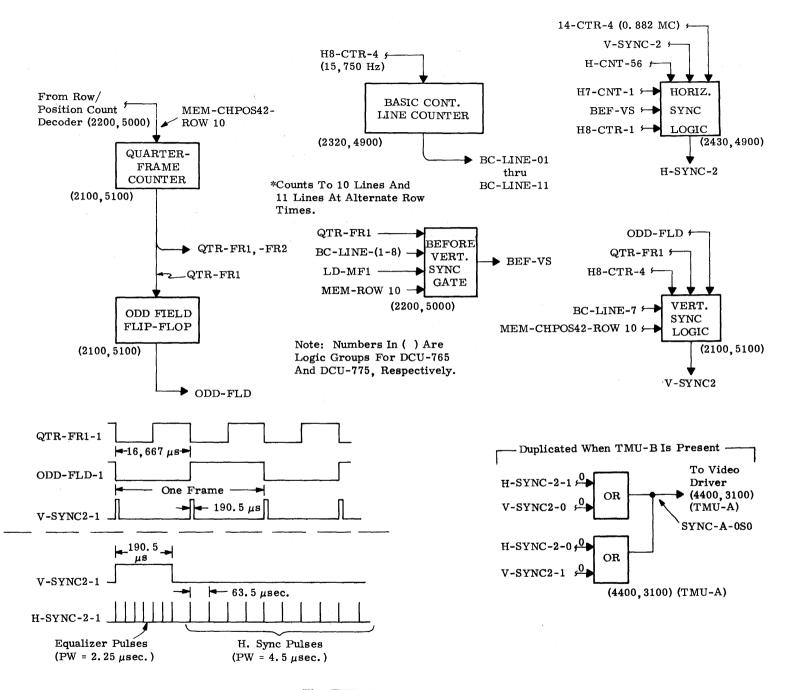

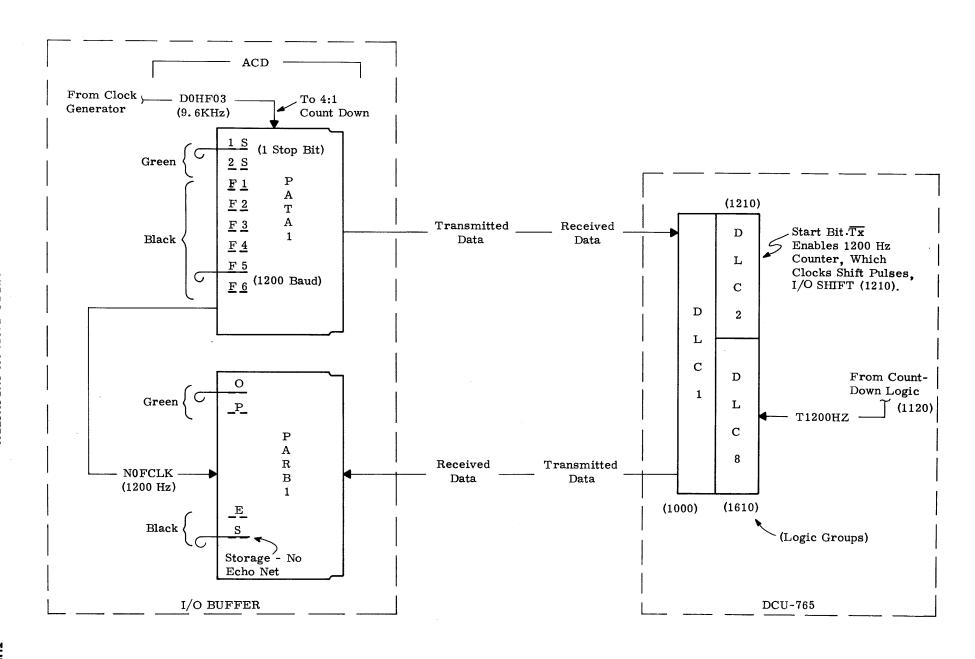

A crystal controlled clock generator and frequency countdown logic are provided on the PTCA1 board in slot M13. The outputs of this board are used in timing the operations of the teletypewriter drives, the Asynchronous Communications Drive (ACD), and the Synchronous Communications Unit (SCU).

The ACD or the SCU may be used to operate a DATANET Video Display Subsystem, or if not implemented for that purpose, either or both may interface with a data set (modem) for communication with a distant terminal. One of the clock generator outputs must always be selected to provide the basic timing signal for the ACD. When the SCU is operated through

a data set, the timing pulses are normally supplied by the data set, and the PTCA1 outputs are used only for test purposes. When an SCU is directly connected to a DATANET Display Controller, the 9.6KHz output of the PTCA1 board is normally used for SCU timing at 4800 baud. However, if the Display Controller incorporates a Direct Timing Source, that source is used for the interface timing.

Refer to the ACD and SCU maintenance instructions in the Communication Drive Section of the Computer Maintenance manual for instructions for selecting the timing signals.

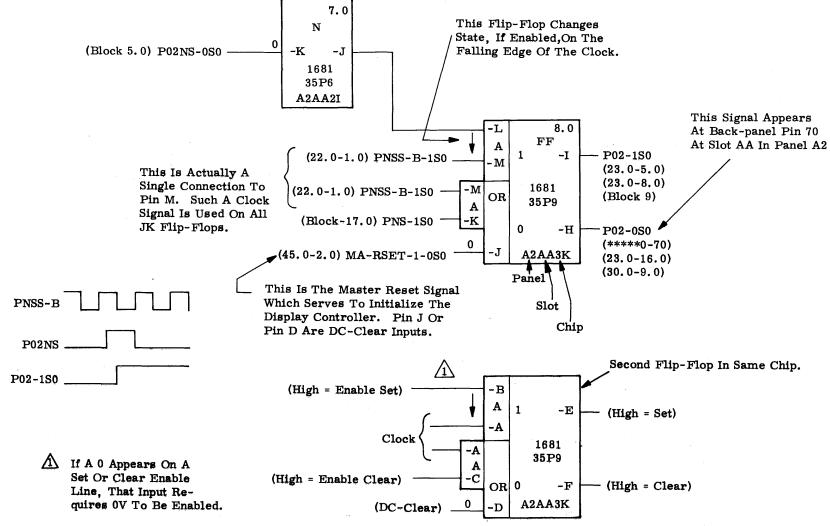

#### Clock Generator

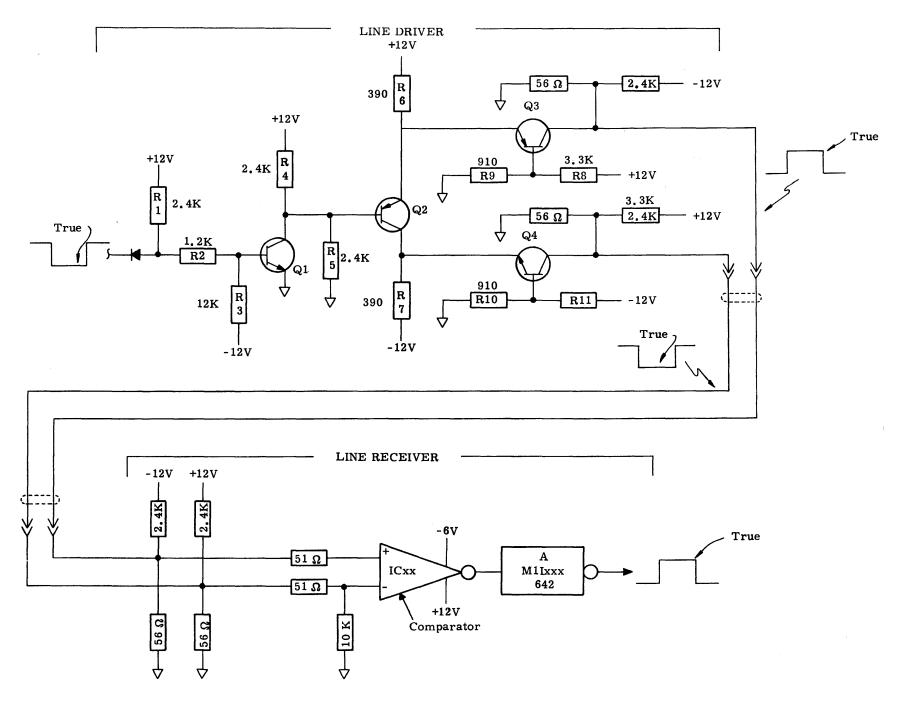

The clock generator circuit, Q1QCLK, is a discrete component circuit consisting of an emitter-coupled crystal oscillator, Q1 and Q2, and two pulse shaper stages Q3 and Q4. The oscillator operates at 633.6 KHz. Pulse shaper stage Q3 is biased near cut-off. The resultant negative going pulses at the collector of Q3 are coupled to the base of Q4. Q4 is normally biased on and is turned off by the pulses. The positive half-microsecond pulses at the collector of Q4 are applied to F1QCLK, which is toggled by each pulse.

Each of the outputs of F1QCLK is a square wave of one half of the crystal oscillator frequency, or 316.8 KHz. The duration of each cycle is 3.157 microseconds, and each half cycle is 1.58 microseconds. The "1" output of F1QCLK is inverted by driver D0QCLK and applied to the high frequency countdown circuits. The "0" output of F1QCLK is inverted by D1QCLK and applied to the low frequency countdown circuit.

#### Countdown Circuits

Counter stages F1H11A, 11B, 11C, and 11D are interconnected such that G0HC11 is enabled at the

trailing edge of every eleventh 316.8 KHz DOQCLK pulse, and disabled at the trailing edge of the next DOQCLK pulse. The C11 pulses are divided by 2 by F1H22A and the output of that stage is applied to the 14.4 KHz output driver, D0HF04, which is enabled by every twenty-second DOQCLK pulse (316.8 KHz/22 = 14.4 KHz).

D0HF04 = CLK · H22A · C11

Counter stages F1L15A, 15B, 15C, and 15D are interconnected such that G0LC15 is enabled at the trailing edge of every fifteenth 316.8 KHz D1QCLK pulse, and disabled at the trailing edge of the next D1QCLK pulse. The C15 pulses are applied to 21.12 KHz driver, D0LF03 which is enabled by every fifteenth D0QCLK pulse (316.8 KHz/15 = 21.12 KHz).

$D0LF03 = CLK \cdot C15$

The remaining countdown outputs are generated in a similar fashion. The rate at which any counter or gate operates can be determined from the logic name in terms of a ratio between the basic clock rate, 316.8KHz, and the count rate. Table 3 provides a tabulation of each countdown output driver and the logic elements which enable them.

Driver D0HF04 may operate at 4.8 KHz or 1.2 KHz, as determined by a jumper between a pair of pin jacks on the PTCA1 circuit board. If the green pin jacks are jumpered, gate G1H264 is disabled, producing a continuous +3.6V at its output. D0HF02 will then operate at a countdown rate of 66:1. If the black pin jacks are jumpered, G1H264 is allowed to operate and D0HF02 operates at a rate of 264:1.

|           |           | Pulse-to-                       |  |  |

|-----------|-----------|---------------------------------|--|--|

| Freque    | ncies     | Pulse Spacing                   |  |  |

| 28.8      | KHz       | 34.7 usec.                      |  |  |

| 21.1      | 2 KHz     | 47.3 usec.                      |  |  |

| 14.4      | KHz       | 69.4 usec.                      |  |  |

| 9.6       | KHz       | 104.1 usec.                     |  |  |

| 4.8       | KHz       | 208.2 usec.                     |  |  |

| 2.4       | KHz       | 416.4 usec.                     |  |  |

| 1.2       | ) KHz     | 833.3 usec.                     |  |  |

| 1.33      | 2 KHz     | 757 usec.                       |  |  |

| 0.8       | 8 KHz     | 1136 usec.                      |  |  |

|           |           |                                 |  |  |

| Output    | Countdown | Driver Logic                    |  |  |

| Frequency | Ratio     | Equation                        |  |  |

| 0.88 KHz  | 360:1     | D0LF01 = CLK · F01 · L120       |  |  |

| 1.20 KHz  | 264:1     | D0HF02 = CLK · H264 · C66 · C11 |  |  |

| 1.32 KHz  | 240:1     | D0LF02 = CLK L240 L120          |  |  |

| 2.4 KHz   | 132:1     | D0HF01 = CLK · C66 · H132 · C11 |  |  |

| 4.8 KHz   | 66:1      | D0HF02 = CLK ·C66 · C11         |  |  |

| 9.6 KHz   | 33:1      | D0HF03 = CLK · 33A · C11        |  |  |

| 14.4 KHz  | 22:1      | D0HF04 = CLK · 22A · C11        |  |  |

| 21.12 KHz | 15:1      | D0LF03 = CLK· C15               |  |  |

| 28.8 KHz  | 11:1      | D0HF05 = CLK ·C11               |  |  |

Table 3 Countdown Outputs

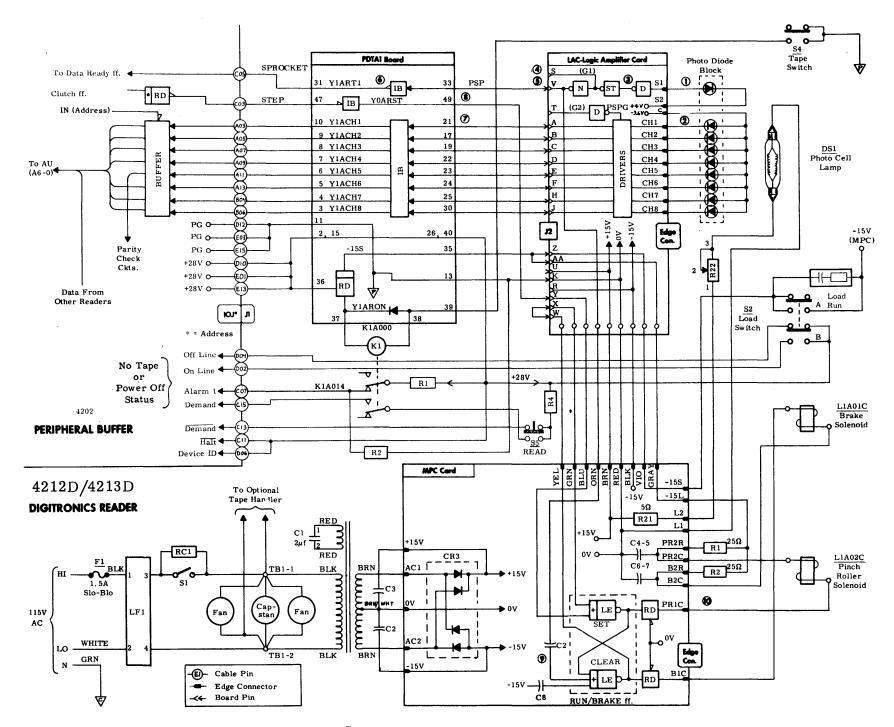

# 4820/4821X01 READER CONTROL DRIVE

### **TABLE OF CONTENTS**

READER CONTROL DRIVE

TRANSFER FORMAT

4244D Card Reader

4212D Paper Tape Reader

SPECIAL CHARACTER DEFINITIONS

4244D Card Reader

4212D Paper Tape Reader

INTERRUPTS

ALARMS

4244D CONTROL LOGIC DESCRIPTION

Card Media Enable

Card Data Enable

Card Media Disable

4212D CONTROL LOGIC DESCRIPTION

Tape Media-Enable

Tape Data-Enable

Tape Media-Disable

PARITY ERROR (4212D)

TIMING ERROR

#### READER CONTROL DRIVE

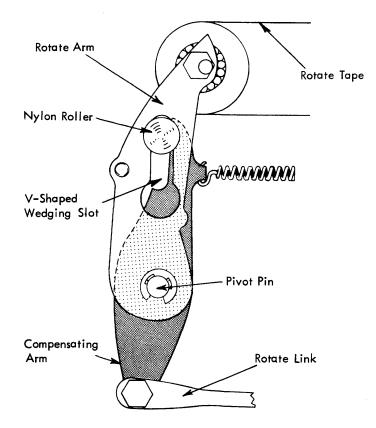

The Reader Control Drive provides input channel interface logic (70C180344) linking the Basic I/O Buffer with the 4244D Card Reader or the 4212D Paper Tape Reader (one drive per channel).

This publication describes the hardware associated with the following GE-PAC\* model numbers:

4DP4820AS01 - Reader Drive for the I/O Buffer in a GE-PAC 4010A System.

4DP4820BS01 - Reader Drive for the Basic Central Systems Unit (CSU) I/O

Buffer in a GE-PAC 4010B System.

4DP4821AS01 - Reader Drive for the Auxiliary Systems Unit (ASU) I/O Buffer (4823ASID) in a GE-PAC 4010B System.

4DP4821BS01 - Reader Drive for the Second Central Systems Unit (CSU) I/O Buffer (4824ASID) in a GE-PAC 4010 System.

The logic for the Reader Drive associated with all of these model numbers is provided in GE drawing, 70C180344.

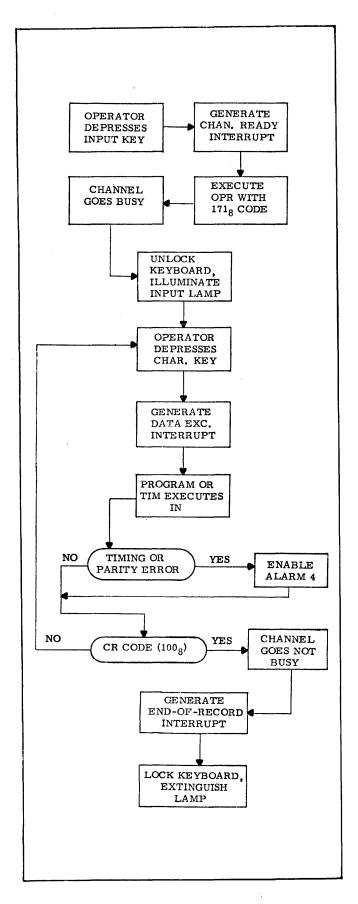

Input operations are performed in a record format. Both reader devices are started (card or tape movement) by program (OPR instruction) and data (characters) are read in as a result of IN instructions or the TIM function. The card reader stops after each card feed cycle. The paper tape reader stops when the DC3 code is read from the tape.

This reader control drive circuitry is contained on the  ${\rm PX1000PBCB1}$  printed wiring board.

#### TRANSFER FORMAT

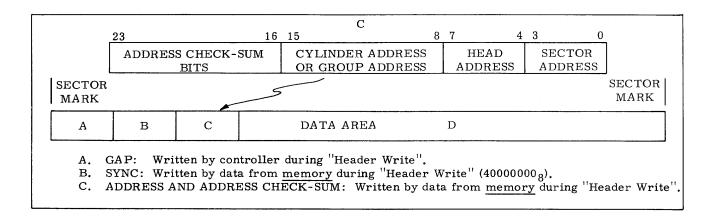

#### 4244D Card Reader

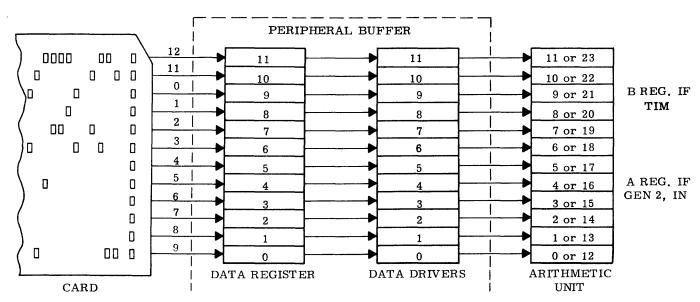

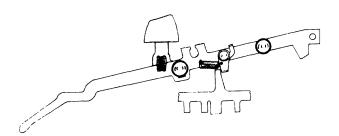

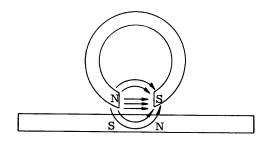

Data from the card reader enters the CPU as illustrated in Fig. 1. Row 9 is transferred to the least significant bit of the A register and row 12 goes to  $A_{11}$  position. When the TIM function is used, row 9 goes to either bit position 0 or 12, depending on the character packing mode.

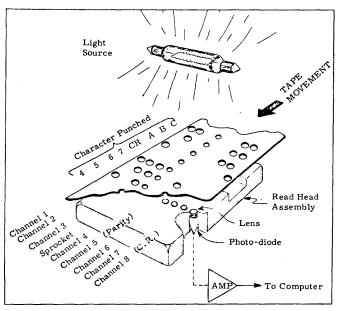

#### **4212D Paper Tape Reader**

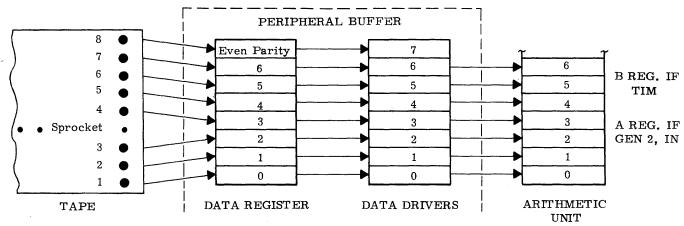

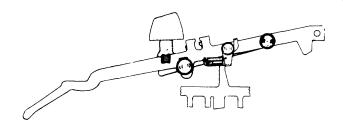

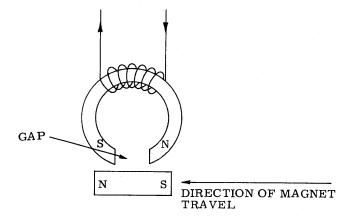

Data from the paper tape reader enters the CPU as illustrated in Fig. 2. The incoming record will contain the following data in the format and sequence shown in the next column.

| Name | Octal Code | Function            |

|------|------------|---------------------|

| NUL  |            | Tape Leader         |

| OPR  | 021        | Device Enable Code  |

| STX  | 002        | Start of Text Code  |

| TEXT |            |                     |

| 1    |            |                     |

| TEXT |            |                     |

| ETX  | 003        | End of Text Code    |

| DC3  | 023        | Device Disable Code |

| CR   | 015        | Inter-Record Code   |

| LF   | 012        | Inter-Record Code   |

| DC4  | 024        | Inter-Record Code   |

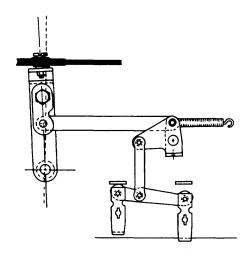

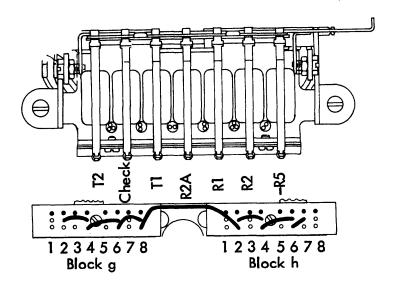

Fig. 1 Card Reader Data Transfer

<sup>\*</sup>Registered Trademark of General Electric Company

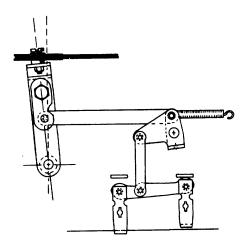

Fig. 2 Tape Reader Data Transfer

# SPECIAL CHARACTER DEFINITIONS

#### 4244D Card Reader

The card reader and control drive do not recognize any special character codes. The OPR instruction initiates the operation that causes one card feed cycle. When the OPR instruction is executed, the contents of the A register can be any code.

#### **4212D Paper Tape Reader**

As shown in the transfer format, several special characters are required on tape or in the program. These characters are defined below.

- NUL The NUL code is used as tape leader and does not get read into memory.

- STX The Start of Text code enables the Data Exchange Ready line which means data is to follow.

- ETX The End of Text code serves no functional purpose on paper tape input. The ETX code is read into memory.

- DC3 The Device Control 3 code disables or turns off the reader and generates the Endof-Record signal. The DC3 code must follow the ETX code.

After the DC3 code is detected, the reader will stop, ready to read the next character which is the CR code. When the next OPR instruction is executed, all characters preceding the next STX are ignored by the I/O Buffer and, therefore, serve only as interrecord codes on paper tape input.

• CR-LF-DC4 - Serve as inter-record codes.

#### **INTERRUPTS**

Two interrupts are generated by the reader control drive logic: A data exchange interrupt (DEI) is used to inform the AU that a character is available for input. An end-of-record interrupt (EOR) is used to inform the AU that all data in a record has been read and transferred.

For the card reader, EOR is enabled when the card reader makes a light check at about column 84. For the tape reader, EOR is enabled when the DC3 character is read and decoded. Both devices can simulate the EOR interrupt by depressing then releasing the demand switch.

The DEI is normally non-inhibitable and the EOR is normally an inhibitable interrupt.

#### **ALARMS**

Properly encoded JNE instructions, addressed to the desired input device (D) will detect the following alarm conditions:

Alarm Line 1 - Device off line - K1 = 00D<sub>2</sub>

Alarm Line 2 - Device failure -  $K1 = 01D_2$

Alarm Line 3 - Bin Alert - K1 = 10D<sub>2</sub> (card reader only)

Alarm Line 4 - Timing error - K1 = 11D2

- Device not plugged in

- Parity error (tape reader only)

# 4244D CONTROL LOGIC DESCRIPTION

The 4244D card readers are capable of reading 80 column, 12 row cards at speeds of 100 or 300 cards per minute, depending on the model option. Characters are read as a result of IN commands; one is required for each of the 80 characters. Each time a character passes over the photocells of the reader device, it is gated from the punched card to the A-register of AU. This action continues until the entire card has passed over the photocells and the end of the card is detected. Continuous card reading is made possible by properly spacing the OPR instructions in the program.

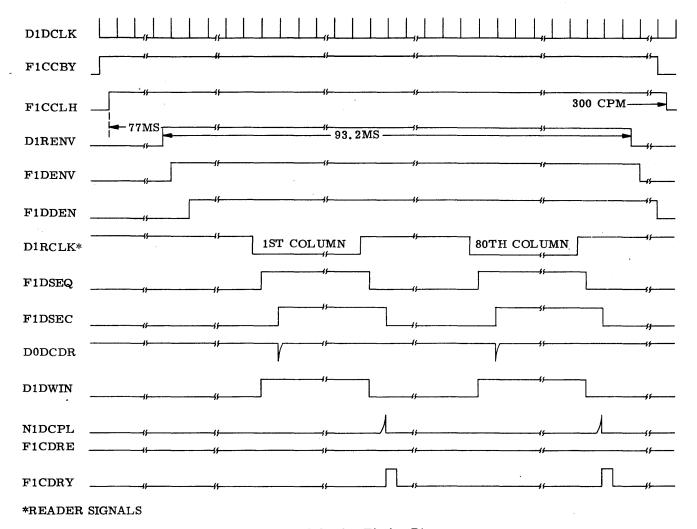

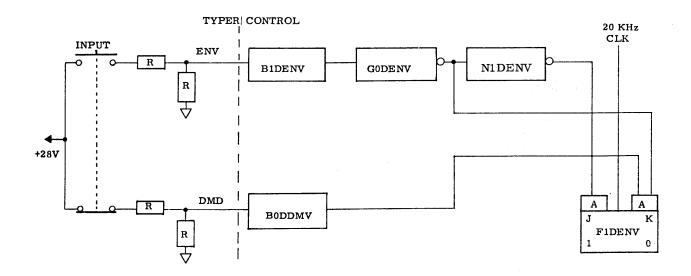

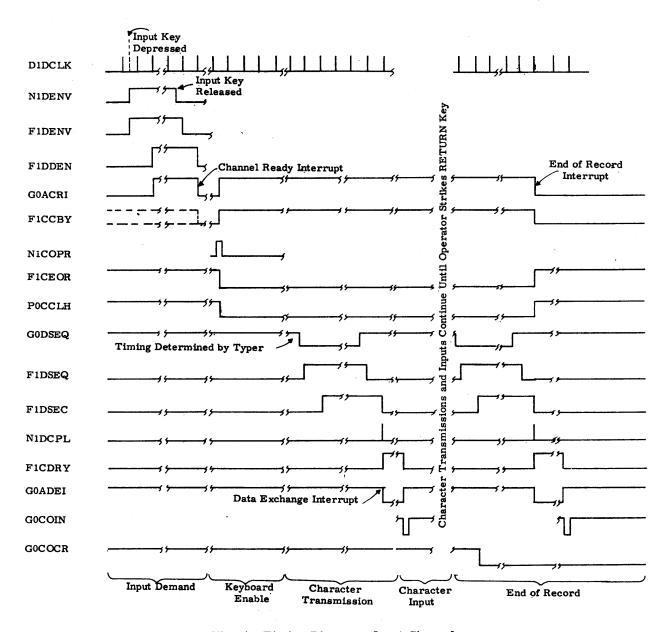

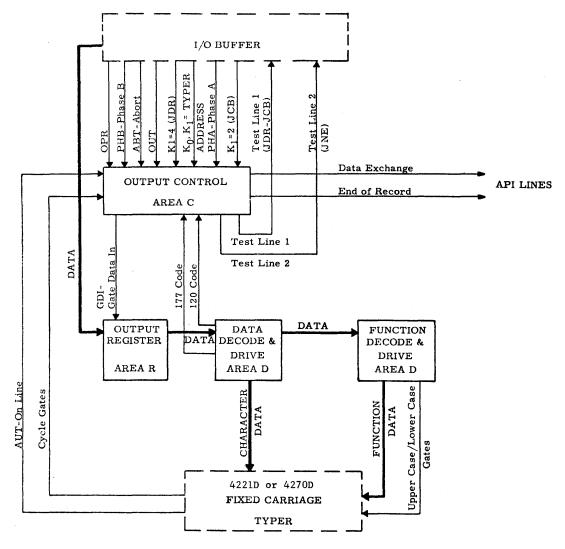

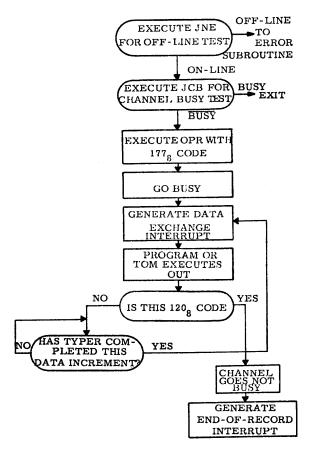

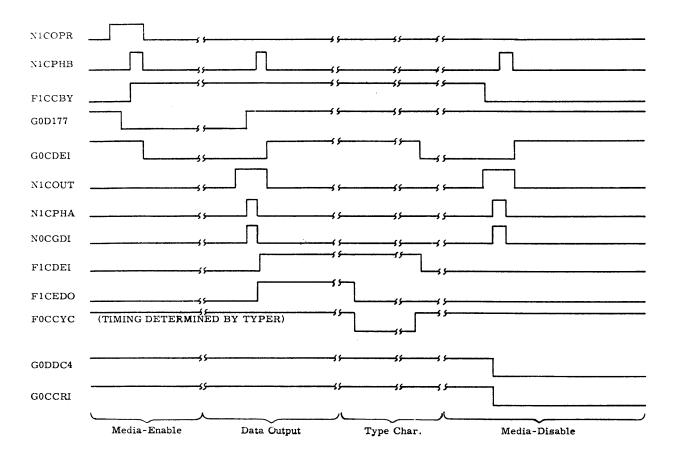

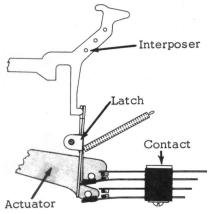

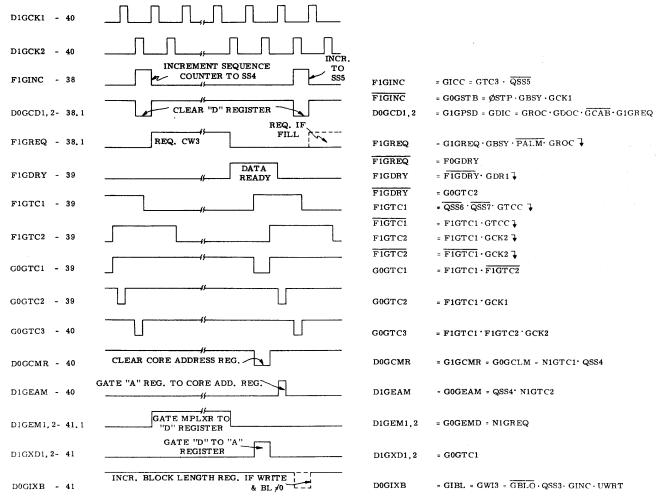

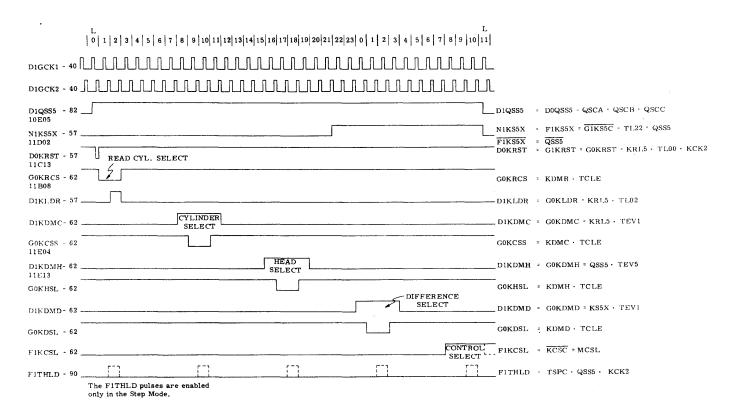

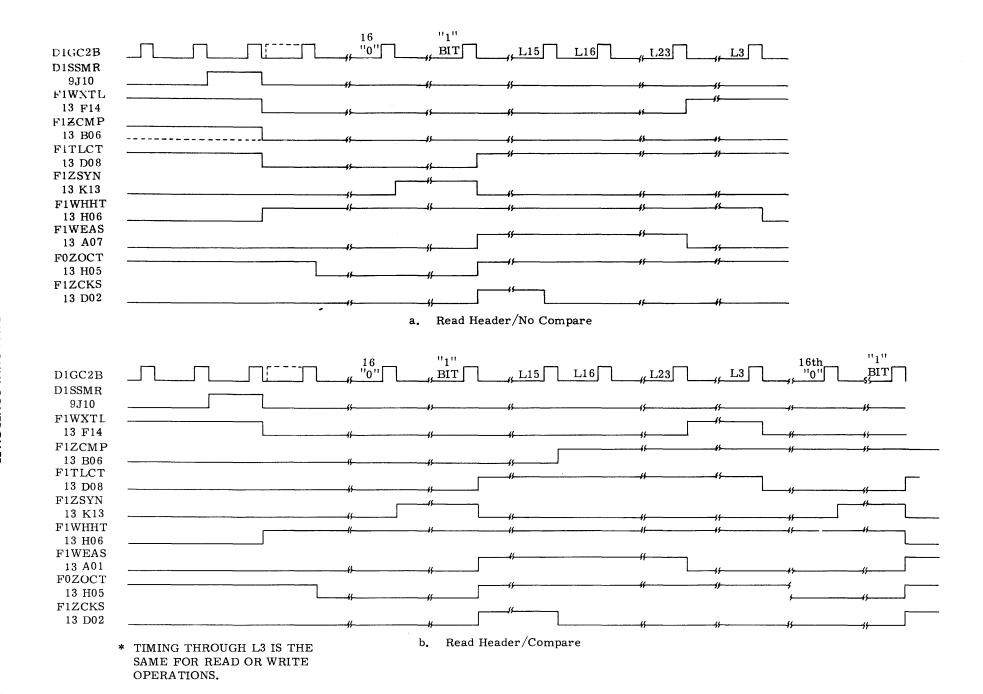

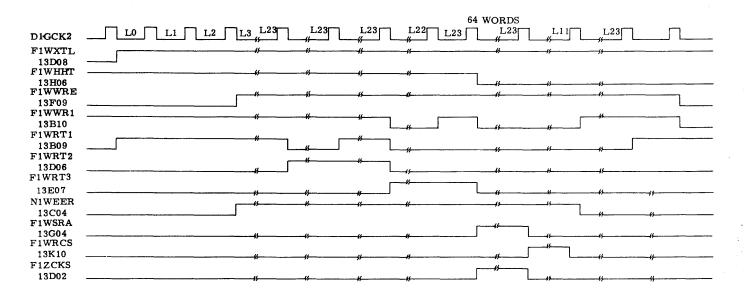

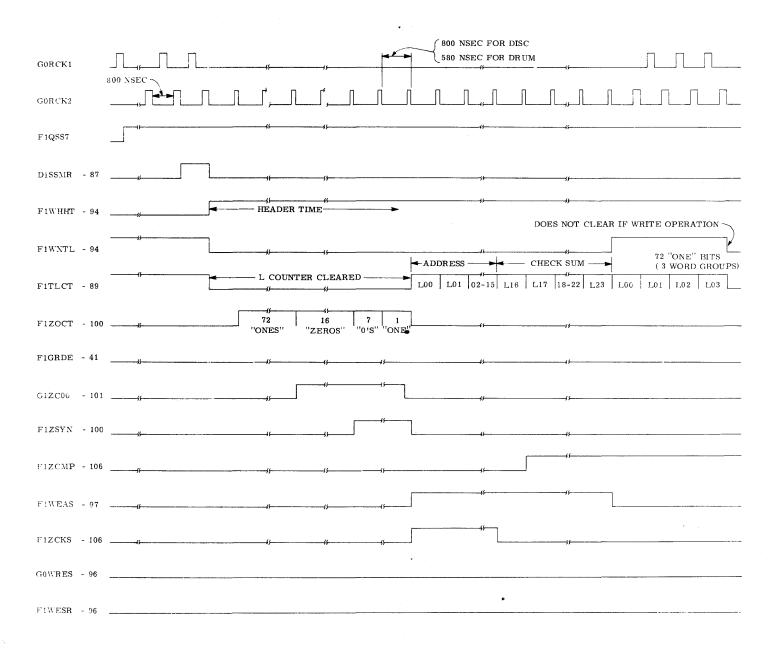

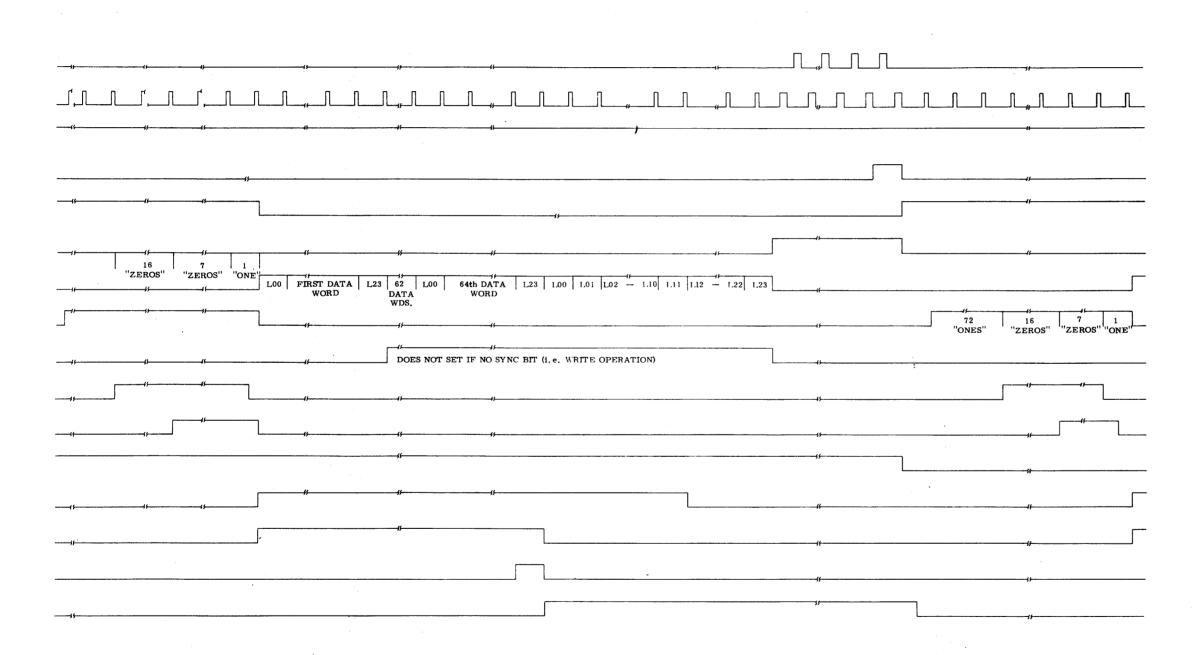

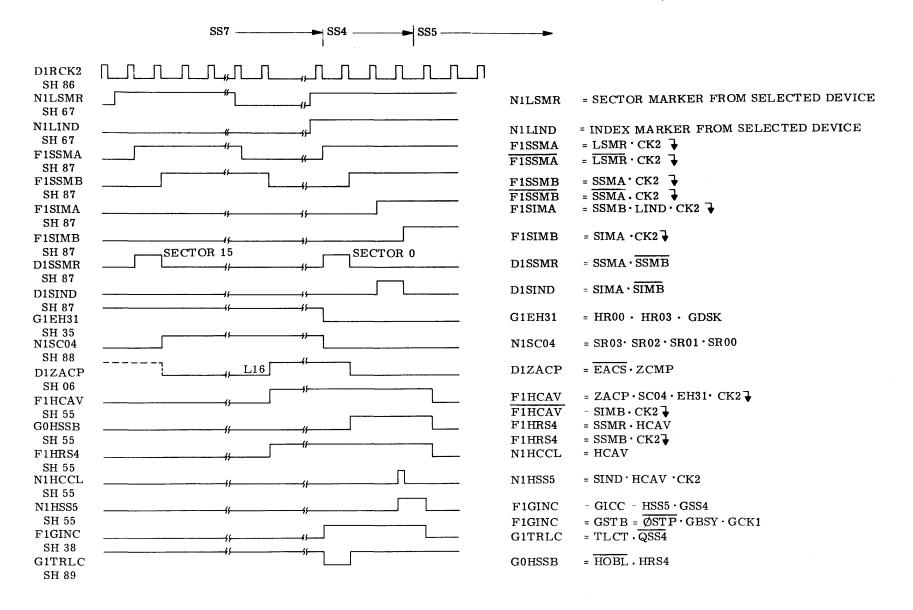

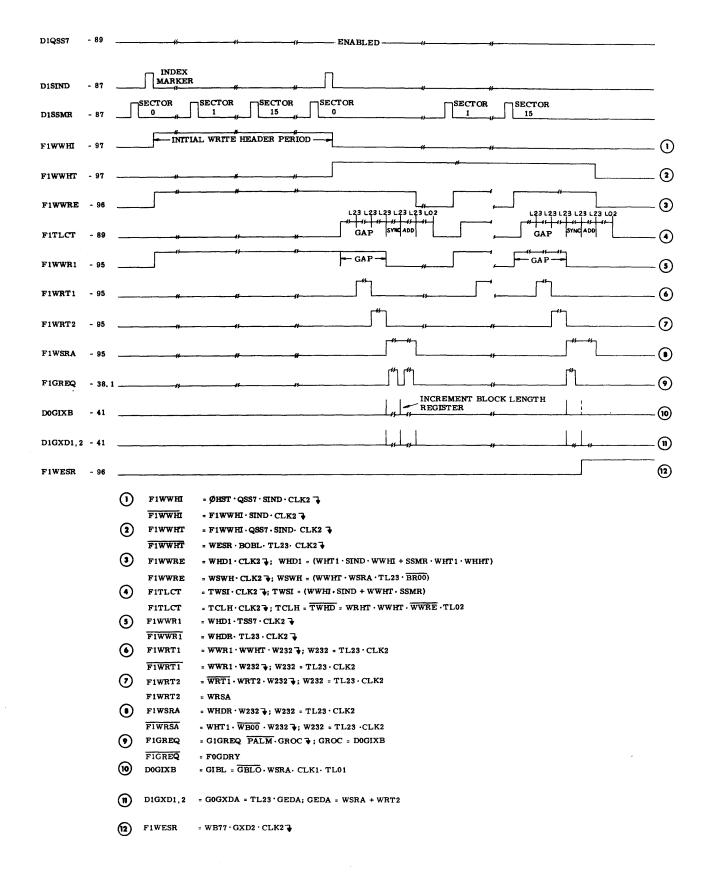

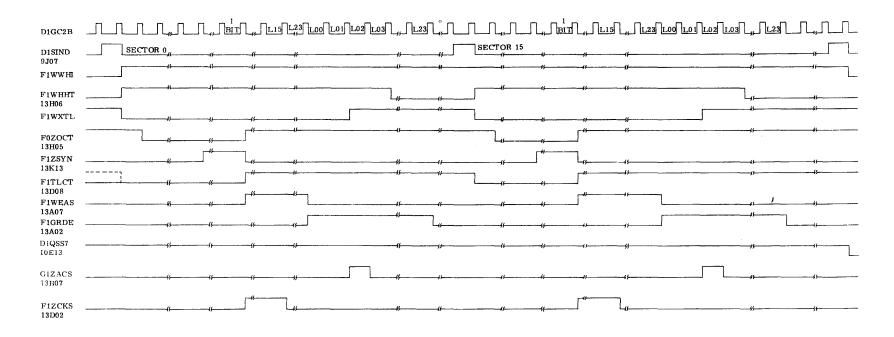

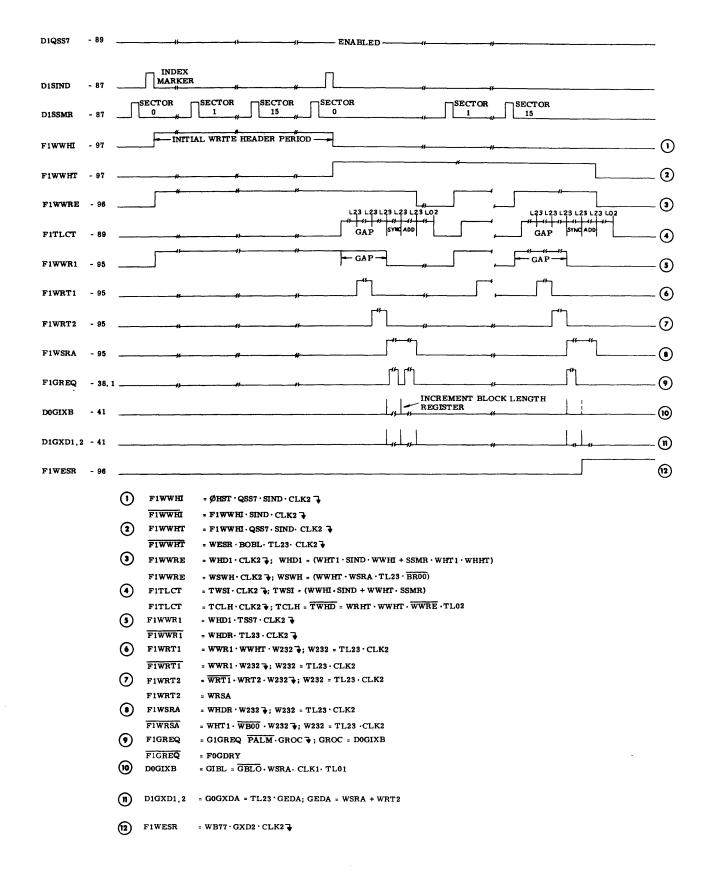

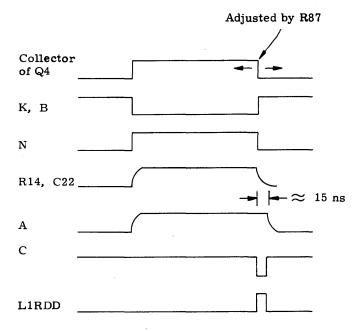

Model 4244D card readers are fully described elsewhere in this manual. The following text is devoted to the logic and timing of the reader input cycle, referenced to the timing diagram of Fig. 3, and to the logic schematics of GE drawing, 70C180344.

Fig. 3 Card Reader Timing Diagram

Initially, the channel must be ready (not busy). The channel busy flip-flop, F1CCBY, normally had been cleared at the end of the previous record. The ABT instruction will also clear the channel busy condition.

A channel test is made by the program via the JNR instruction. If the channel is not busy, the test line 1 gate, GOATL1, is enabled and the program will step to the next sequential instruction.

G0ATL1 = CBY · DEN · K12 · ADD F1DDEN = No manual or prior demand

A demand for an interrupt can be manually initiated by momentarily depressing the DEMAND pushbutton on the card reader device. Flip-flop F1DDEN sets, the channel busy flip-flop resets, and a channel ready interrupt occurs.

F1DENV = B1DENV · CLK

F1DDEN = F1DENV · CLK

GODRCB = F1DDEN · F1DENV · CLK

GOAEOR = FICCBY · FIDDEN

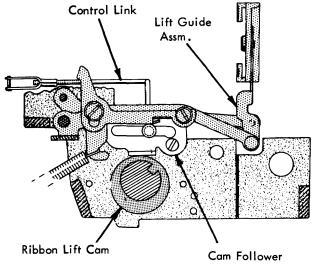

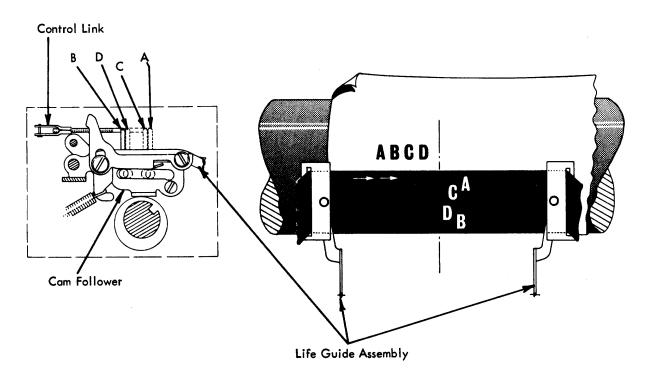

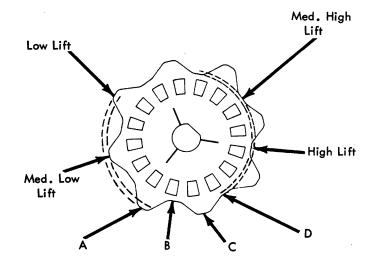

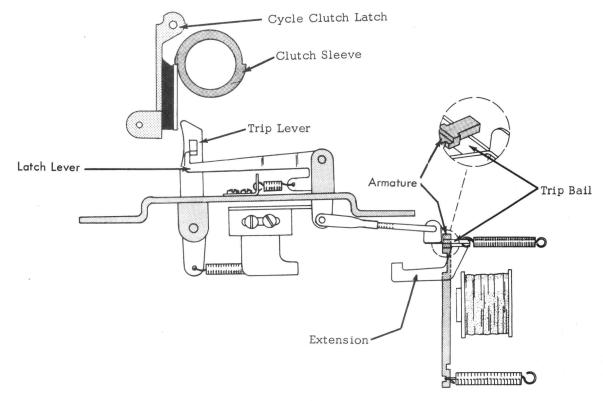

#### Card Media Enable

The next sequential instruction is OPR, addressed to the input channel. Any code that may exist in the Aregister is disregarded by the reader control logic. OPR sets the input channel busy flip-flop, F1CCBY, which sets clutch flip-flop F1CCLH, if the device is on-line, and clears test line 1. The program is released to await an interrupt.

F1CCBY = OPR · PHB · ADD F1CCLH = CBY · ONL

#### Card Data Enable

Relay driver DOCCLH activates the reader's card feed mechanism. The timing hole on the reader's clock belt that is associated with each data column generates a signal (DCLK0) that is used as one of the timing signals in the reader control logic.

When the first column passes over the photocells of the reader, its clock signal, at zero volts, sets sequence flip-flop F1DSEC on the next D1DCLK clearing the data register. Window driver D1DWIN is enabled with the setting of F1DSEQ.

F1DSEQ = B1DSEQ · F1CCLH · D1DCLK

$F1DSEC = F1DSEQ \cdot D1DCLK$

D1DWIN = F1DSEQ

D0DCRD = D1DCLK · F1DSEQ · F1DSEC

The first data character is gated into the data register.

DR SET = DATA · D1DWIN

Data ready enable flip-flop F1CDRE is set continuously, the only condition being that the card reader device is connected to the control module. Data ready flip-flop F1CDRY sets with a control pulse that is generated as a result of the space between clock holes on the reader clock belt being sensed. Data exchange interrupt gate G0ADEI is enabled.

F1CDRY = F1CDRE · N1DCPL

N1DCPL = F1DSEQ · F1DSEC · D1DCLK

GOADEI = F1CDRY · F1DSEC

The computer responds to the interrupt with an IN command. The data is transferred from the data register, through the I/O Buffer, to the AU. Flipflop F1CDRY is cleared to await the next character. All 80 characters are transferred to memory in a like manner, i.e., an IN command is required for each character.

#### Card Media Disable

At the end of a card (approximately column 84), the card envelope signal B1DENV goes to zero volts. This condition clears the channel busy flip-flop, clears the clutch flip-flop, and generates an end-of-record interrupt. The computer must respond with another OPR before the next card will feed.

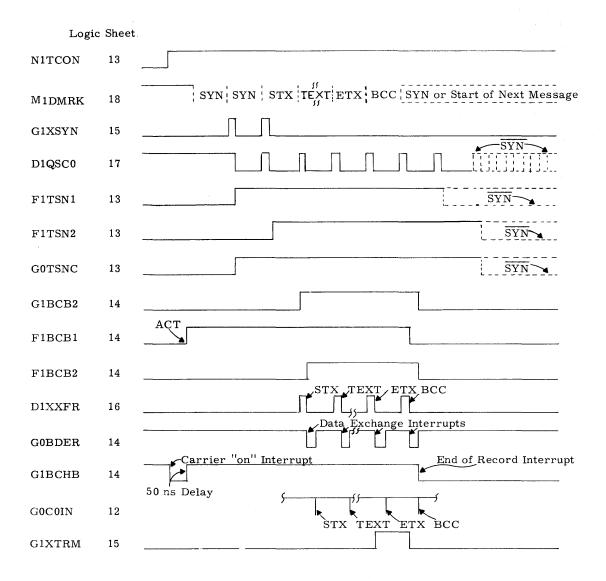

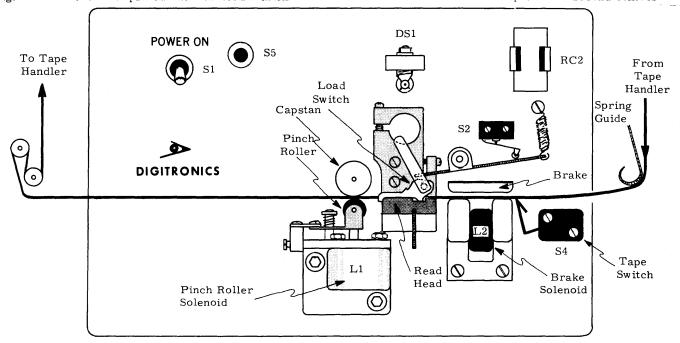

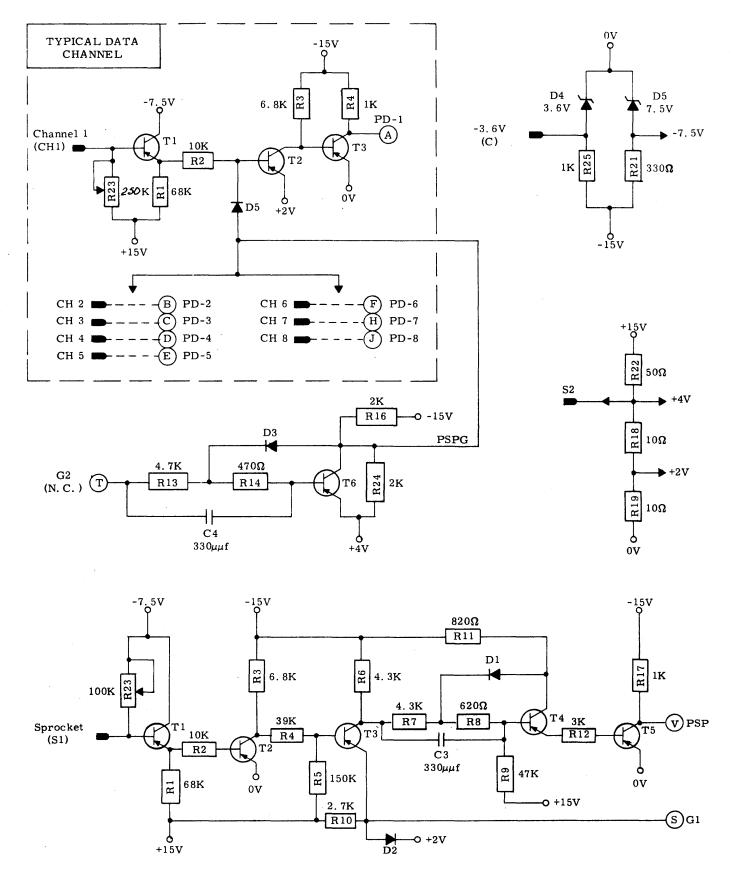

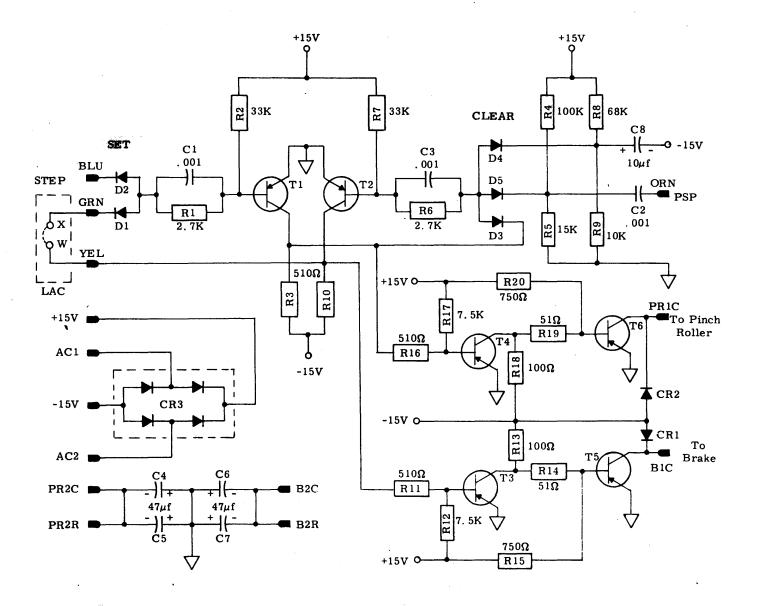

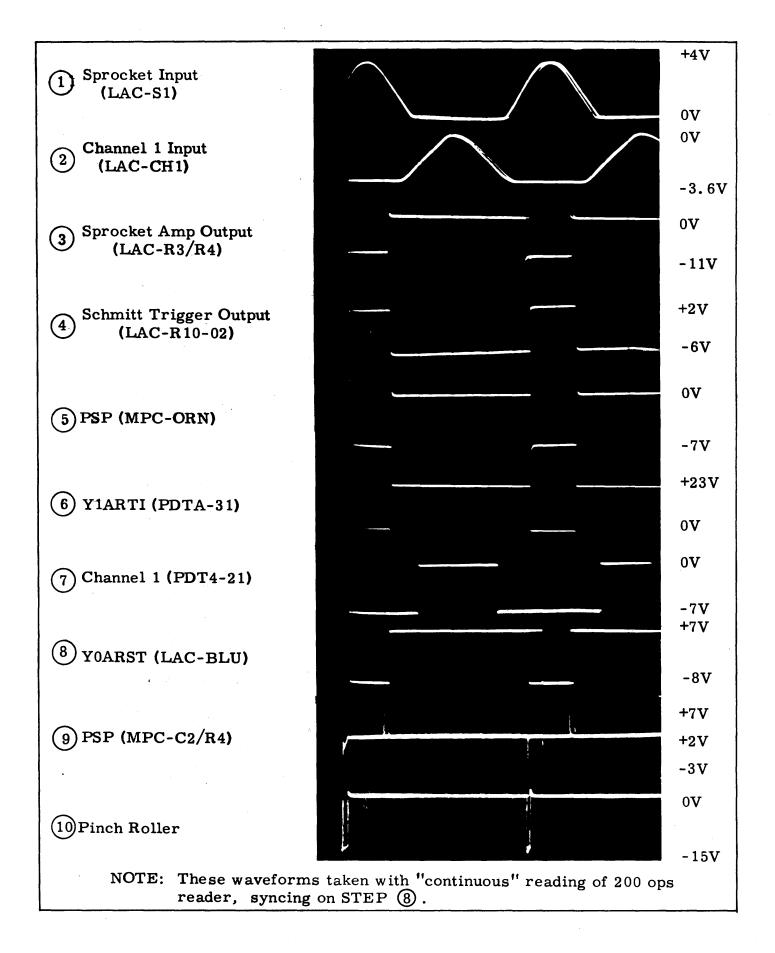

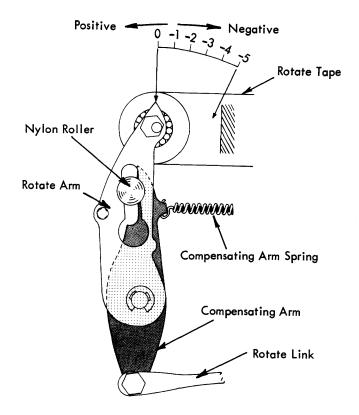

# 4212D CONTROL LOGIC DESCRIPTION

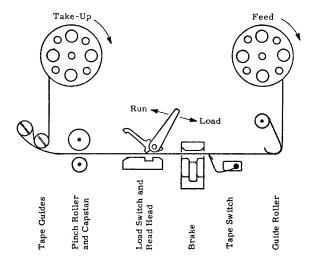

The 4212D paper tape reader is capable of reading 8-channel (maximum) tape at a speed of 100 characters per second. Characters are read as a result of the IN command. One character at a time is gated from the tape to the A register of the AU each time a character passes over the photo-diodes of the reader device. This action continues until the media-disable code (DC3) is detected. The ETX code that precedes the DC3 code is read into memory as data. Tape movement ceases so that the frame following the DC3 code is positioned for reading.

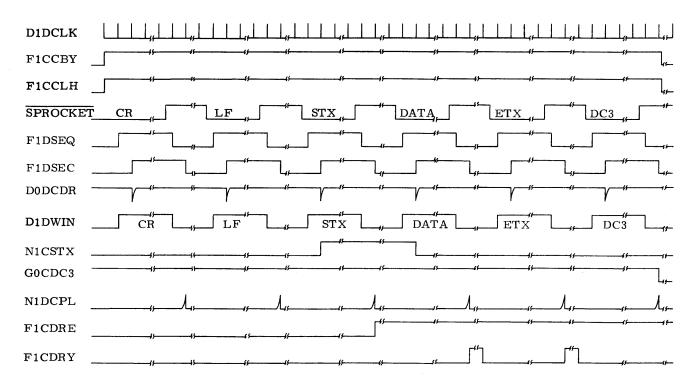

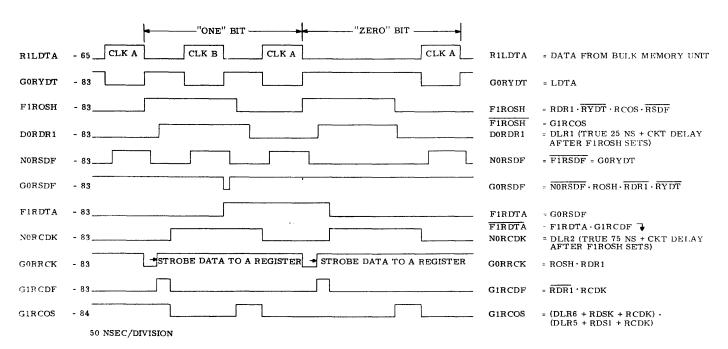

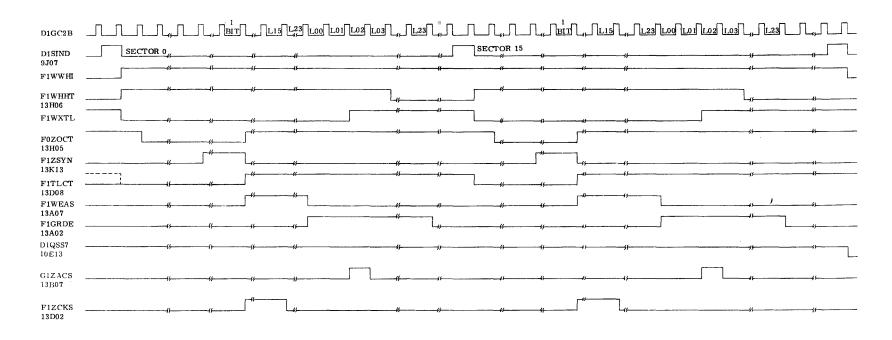

The basic IN command is discussed earlier in this section. The 4212D reader is fully described elsewhere in this manual. The following text is devoted to the logic and timing of the reader input cycle,

referenced to the timing diagram of Fig. 4 and to the logic schematics of GE drawing, 70C180344.

Initially, the channel must be ready (not busy). The channel busy flip-flop, F1CCBY, is normally cleared (reset) by the media-disable code (DC3) from the previous input operation. The Abort instruction will also clear the channel busy condition.

A channel test is made by the program via the JNR instruction. If the channel is not busy, the test line 1 gate, GOATL1, is enabled and the program will step to the next sequential instruction:

$GOATL1 = \overline{CBY} \cdot \overline{DEN} \cdot K12 \cdot ADD$

DEN = No Manual Demand.

A demand for an interrupt may also be manually initiated by momentarily depressing the READ push-button on the paper tape reader device. Flip-flop F1DDEN sets, the channel busy flip-flop resets, and a channel ready interrupt occurs.

F1DENV = B1DENV · CLK

F1DDEN = F1DENV · CLK

GODRCB = F1DDEN · F1DENV · CLK

$GOAEOR = \overline{F1CCBY} \cdot F1DDEN$

#### Tape Media-Enable

The next sequential instruction is OPERATE, addressed to the input channel. The DC1 code (021g), if present in the A register, is disregarded by the reader control logic. OPR sets the input channel busy flip-flop, F1CCBY; clears the data ready enable flip-flop, F1CDRE; sets the clutch flip-flop, F1CCLH, if the device is on-line; and clears test line 1. The program is released to await an interrupt.

F1CCBY = OPR · PHB · ADD

F1CCLH = CYB · ONL

#### Tape Data-Enable

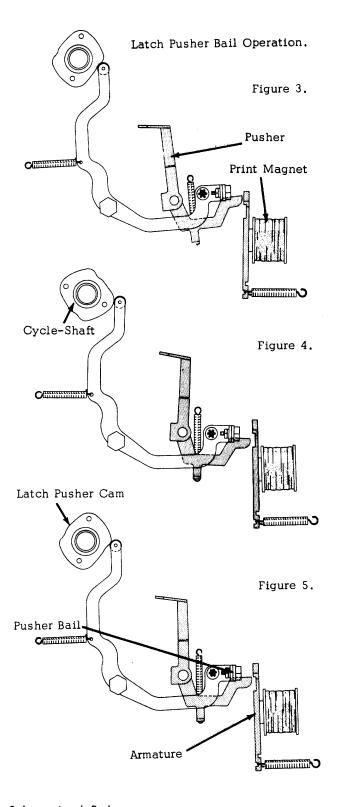

Relay driver DOCCLH activates the tape feed mechanism. The sprocket hole associated with each frame of information is used as one of the timing signals. All inter-record codes prior to the STX code are gated to the data register but are discarded because only the STX code can set the data ready enable flip-flop which is necessary to generate a data exchange interrupt.

When the STX code passes over the photo diodes of the reader, its sprocket signal, RT1 at zero volts, sets sequence flip-flop F1DSEQ. Sequence control

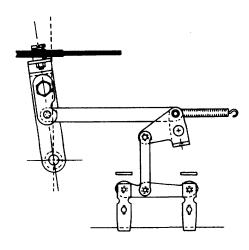

Fig. 4 Tape Reader Timing Diagram

flip-flop F1DSEC sets at the following clock pulse and the data register is cleared. Window driver D1DWIN is enabled with the setting of F1DSEQ.

F1DSEQ = B1DSEQ · F1CCLH · D1DCLK

F1DSEC = F1DSEQ · D1DCLK

D1DWIN = F1DSEQ

D0DCDR = D1DCLK · F1DSEQ · F1DSEC

The STX code (002g) is gated to the data register.

DR SET = CODE · D1DWIN.

The STX code is decoded by gate G0CSTX and the signal is inverted by N1CSTX. The data ready enable flip-flop F1CDRE sets, indicating that the next data received from the reader will be meaningful.

F1CDRE = N1CSTX  $\cdot$  F1CCBY  $\cdot$  N1DCPL N1DCPL = F1DSEC  $\cdot$  F1DSEQ  $\cdot$  D1DCLK

Data ready flip-flop F1CDRY sets at the next control pulse, enabling data exchange interrupt gate G0ADEI. By this time the first data character has set the data register.

GOADEI = F1CDRY · F1DSEC

The program is interrupted and either an IN command is executed or a TIM operation is started. The data is transferred from the data register, through the I/O Buffer, to the AU. Flip-flop F1CDRY is cleared to await the next character.

Each data character, including the ETX code, is transferred to memory in a like manner, i.e., an interrupt and an IN command are required for each character.

#### Tape Media-Disable

When the DC3 code (0238) has been detected by the reader and is in the data register, it is decoded by gate G0CDC3. Channel busy flip-flop, F1CCBY, and clutch flip-flop, F1CCLH, are cleared. With F1CCBY cleared, gate G0AEOR is enabled and its output goes from 3.6V to 0V. This signal is recognized by the AU as the End-of-Record interrupt.

#### PARITY ERROR (4212D)

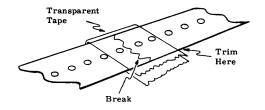

In addition to the seven data characters on the paper tape, there is an even parity bit. This bit, like data, is gated to the data register and subsequently to the I/O Buffer. If the parity checking circuitry of the I/O Buffer detects a parity error, signal DOPPAB will be 3.6V. Alarm gate GOAALM is enabled and the alarm flip-flop, F1AALM, is set.

$GOAALM = \overline{DOPPAB} \cdot N1RPTR \cdot N1COIN$

#### TIMING ERROR

Alarm gate GOAALM is also enabled if a timing error has occurred.

$GOAALM = \overline{SEC} \cdot SEQ \cdot DRY$

If, for any reason, the AU has not serviced the Data Ready interrupt, the alarm condition can indicate that a data character has been lost.

5

# PAPER TAPE/CARD PUNCH DRIVE

## TABLE OF CONTENTS

| INTRODUCTION                  |

|-------------------------------|

| PAPER TAPE PUNCH DRIVE        |

| INTERRUPTS                    |

| RECORD FORMAT                 |

| TRANSFER FORMAT               |

| SPECIAL CHARACTER DEFINITIONS |

| CONTROL LOGIC DESCRIPTIONS    |

| Alarms                        |

| Busy Tests                    |

| Media Enable                  |

| Data Enable                   |

| Media Disable                 |

|                               |

| CARD PUNCH DRIVE              |

| RECORD FORMAT                 |

| INTERRUPTS                    |

| LOGIC DESCRIPTION             |

| Alarms                        |

| Busy Tests                    |

| Media Enable                  |

| Data Enable                   |

| Media Digable                 |

# PAPER TAPE/CARD PUNCH DRIVE

#### **INTRODUCTION**

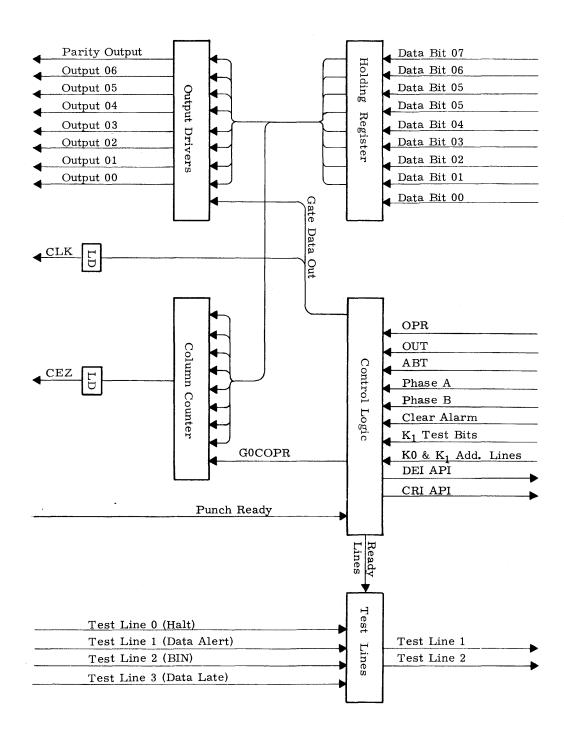

The Punch Drive is an optional part of the I/O Buffer that can be used to drive the 4253 Paper Tape Punch or the 4283 Card Punch. Its primary functions are to provide a holding register and program selectable data formating (USASCII or EIA Standard) for output information being sent to the punch. This frees the basic control portion of the I/O Buffer for communication with other optional drive logics. Information held in the holding register is transferred to the respective device through transformer coupled AC drive lines, providing isolation of the device's inherently noisy power supplies from those of the computer.

This publication describes the hardware associated with the following GE-PAC\* model numbers:

- 4DP4820AS02 Punch Drive for the I/O Buffer in a GE-PAC 4010A System.

- 4DP4820BS02 Punch Drive for the Basic Central Systems Unit (CSU) I/O

Buffer in a GE-PAC 4010B

System.

- 4DP4821AS02 Punch Drive for the Auxiliary Systems Unit (ASU) I/O Buffer in a GE-PAC 4010B System.

- 4DP4821BS02 Punch Drive for the Second Central Systems Unit (CSU) I/O Buffer in a GE-PAC 4010B System.

The logic for the Punch Drive associated with all of these model numbers is provided in GE drawing, 70C180346 (Transformer Coupled Drive I).

All necessary circuitry for the drive is contained on one standard-size GEAPS\*\* printed wiring board (PX1000PBCF1). When installed as part of the I/O Buffer it is hard-wired to the Basic I/O Buffer and to the output connector jack. Since control and data requirements vary slightly between the two devices, signal connections at the device end differ according to which particular one is connected. Also, significance of the alarms sent back to the drive logic from the device differ according to which device is connected to the drive.

Further device distinction is accomplished by decoding the K1 bits of the OPR command, used to initiate device operation. The status of the K1 bits during execution of an OPR command determines which data format will be used and automatically enables the logic to detect the correct end-of-record code for the corresponding device.

Although the logic (drawing number 70C180346) is virtually the same, regardless of the device connected to it, differences in the format, interrupt usage, alarm significances and actual device operation require an independent description of the logic for each device. For this reason there are two separate descriptions, one for each possible device, following this introduction. If desired, the description not relating to the drive as implemented for your system can be removed.

<sup>\*</sup>Registered Trademark of General Electric Company

<sup>\* \*</sup> Trademark of General Electric Company

#### PAPER TAPE PUNCH DRIVE

The 4253 Paper Tape Punch connects to the I/O Buffer through the Punch Drive Logic to provide an output medium for permanently recording programs and data on paper tape. By specifying  $\mathrm{K}_1$  = 00X during the OPR command, ensuing data is punched in the USASCII code. EIA standard RS-244 code will be punched following the execution of an OPR with  $\mathrm{K}_1$  = 01X. Although the tape punches incrementally, by punching the transmitted code and spacing the tape ready for the next character, output operations to the punch are performed in a record format.

#### INTERRUPTS

Paper tape interrupts require two program interrupt points. The data-exchange interrupt signals the computer each time data is required by the punch and the end-of-record interrupt informs the computer when the record has been completed. The data-exchange interrupt is normally non-inhibitable and the end-of-record interrupt is usually inhibitable.

#### RECORD FORMAT

The outgoing data should contain the following data in the format and sequence shown:

| _N  | Iame C                              | octal Code | Function                                          |

|-----|-------------------------------------|------------|---------------------------------------------------|

| OPI | R K <sub>1</sub> =00X               | 022        | Media enable-ASC II Code                          |

|     | $K_1 = 01X$                         | 033        | Media enable-EIA Code                             |

| OU? | Γ-NUL**                             | 000        | Tape Leader                                       |

|     | STX                                 | 002        | Data Enable Code (not used with EIA Standard)     |

|     | $\mathop{^{\rm TEXT}}_{\dot{\bot}}$ |            |                                                   |

|     | TEXT                                |            |                                                   |

|     | ETX                                 | 003        | Software recognition (not used with EIA Standard) |

|     | DC3                                 | 023        | (For paper tape reader)                           |

|     | CR                                  | 015        | Software Standard                                 |

|     | LF                                  | 012        | Software Standard                                 |

| CUO | Γ-DC4                               | 024        | Media disable for ASC II Code                     |

|     | -DEL                                | 177        | Media disable for EIA Std.<br>Code                |

- \* Contents of A-register during OPR. Not significant for this device; ensures program compatability with TTY punch.

- \*\* NUL Code repeated until desired amount of tape leader has been generated.

#### TRANSFER FORMAT

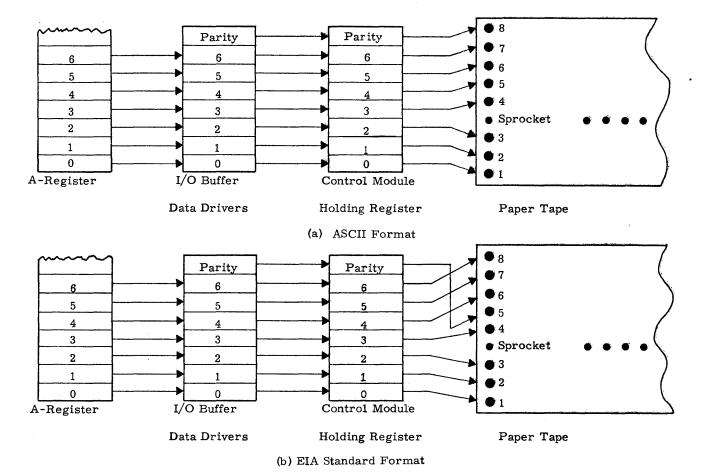

Data are transferred from the central processor to the paper tape punch as illustrated in Fig. PTP.1. When the TOM function is used, the least significant bits of the B-register are transferred.

#### SPECIAL CHARACTER DEFINITIONS

As shown in the record format, several special characters are recorded in the tape record. These special characters are defined below:

- NUL The NUL code is used as tape leader.

- DC2 The Device Control 2 code has no functional purpose on paper tape output but is used to be consistent with TTY punch requirements. The DC2 code is not punched.

- STX The Start-of-Text code has no functional purpose on paper tape output but is required by tape readers. The STX code is punched.

- ETX The end-of-Text code has no functional purpose on paper tape output but is required to be consistent with TTY punch software when using ASCII code. The ETX code is punched.

- DC3 The Device Control 3 code has no functional purpose on paper tape output but is required by tape readers when using ASCII code. The DC3 code is punched.

- CR/LF The Carriage Return and Line Feed codes have no functional purpose on paper tape output but are used to be consistent with TTY Punch software requirements. The CR and LF codes are punched.

- DC4 The Device Control 4 generates the End-of-Record signal when outputting ASC II format. The DC4 code is punched.

- ESC The Escape code signals the control module that the EIA Standard data is to be punched. Tape channels are switched as shown in Fig. PTP.1. The ESC code is not punched.

- DEL The Delete code generates the End-of-Record signal when punching EIA Standard data. The DEL is not punched.

#### CONTROL LOGIC DESCRIPTIONS

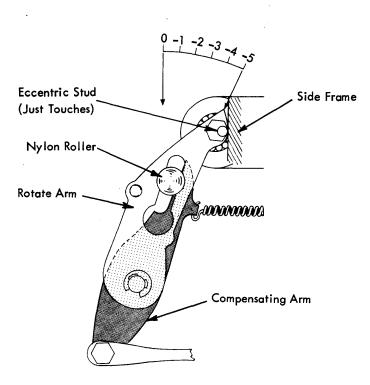

Model 4253 Paper Tape Punches are capable of punching 8-channel (maximum) tape at a speed of 120 frames per second. Characters are punched as a result of OUT commands. One character at a time is sent from the central processor to the punch each time the punch signals that it is positioned ready to receive the next character.

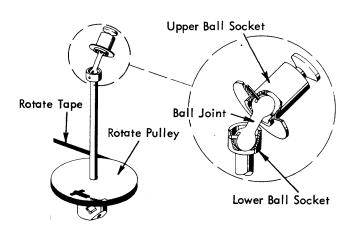

Fig. PTP. 1. Transfer Formats

This action continues until the media-disable code is detected by the control logic. Tape movement then ceases with the frame following the media-disable code positioned for punching.

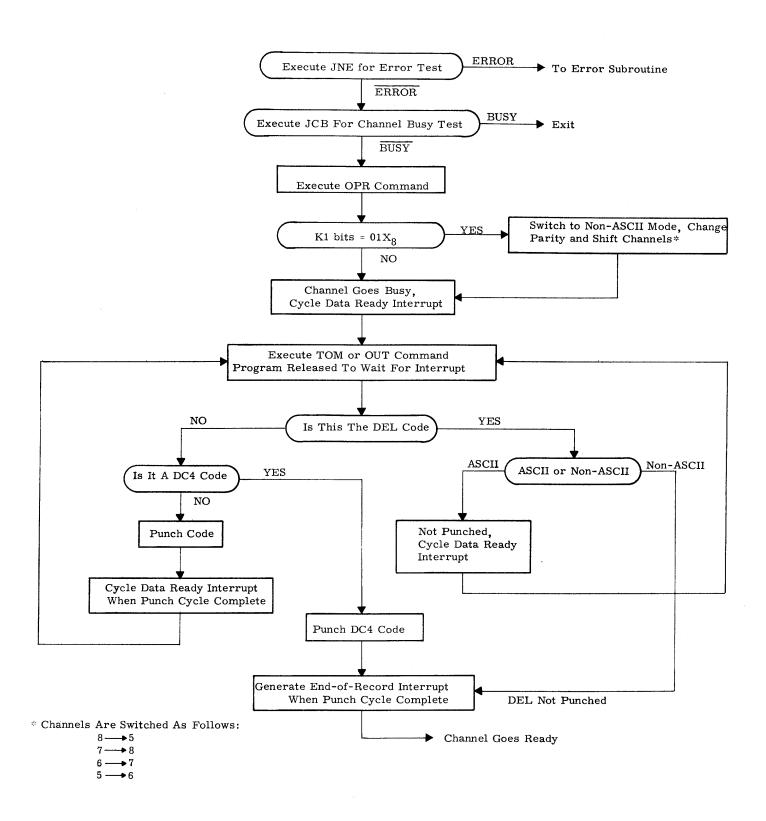

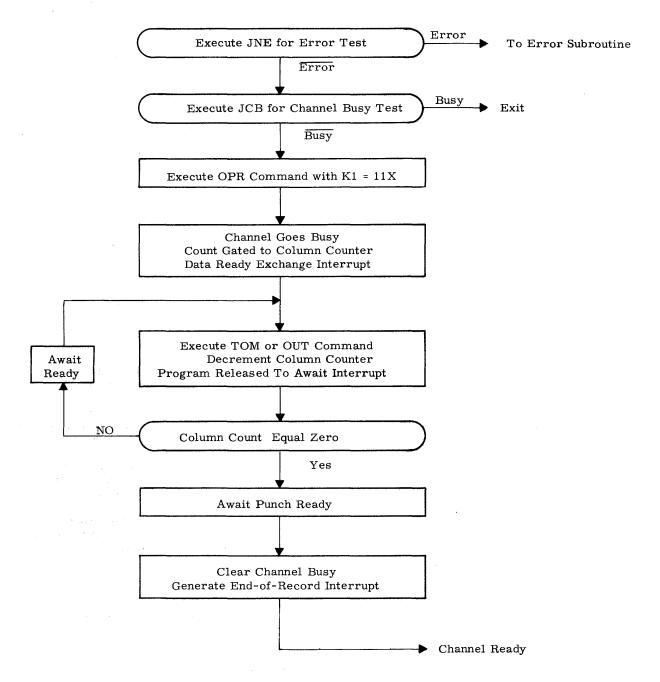

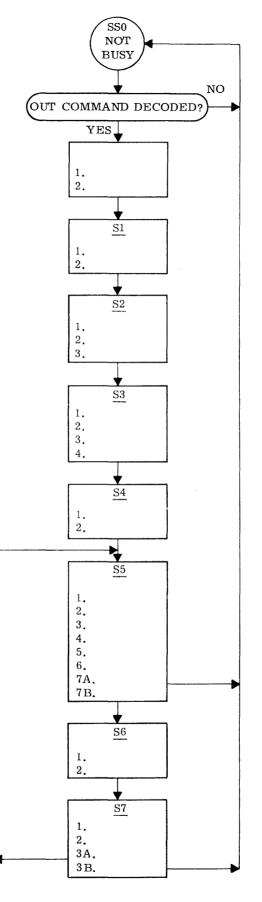

A description of the OUT command is contained in the Arithmetic Unit portion of Volume I. The Model 4253 Paper Tape Punch is fully described elsewhere in this volume. During the following description, reference should be made to the flow chart of Fig. PTP. 2, the timing diagram of Fig. PTP. 3, and to the logic schematics of GE Drawing 70C180346.

#### **Alarms**

The following alarm conditions can be detected by using properly encoded JNE commands addressed to the drive logic:

- Text Line 0 Test Line 0 is "true" when the punch is in the off-line condition.

- Test Line 1 Test Line 1 is "true" when the punch is out of tape or the tape has broken.

Both alarm lines are sampled at gate GOATL2 in the drive logic. The specific line sampled during the JNE command's execution is determined by the status of the JNE's K1 bits:

- K1 = 00X Text Line 0

- K1 = 01X Test Line 1

The output of GOATL2 is routed through the Basic I/O Buffer to the AU where the decoded JNE causes the line to be sampled. Should the test line being sampled be "true", the corresponding AND input is enabled and GOATL2 yields zero volts. A zero volt output during the JNE's execution causes the program to step to the next sequential location, indicating an error condition. If the test line being sampled is "false", the AND gate is disabled and GOATL2's output is plus five volts. A plus five volt output indicates that there is no error and the program jumps to the second sequential location.

G0ATL2 = CADD

$$(\overline{K14} \cdot \overline{K12} \cdot TL0 + \overline{K14} \cdot K12 \cdot TL1)$$

Test lines two and three are not connected to the punch.

Fig. PTP. 2. Paper Tape Punch Flow Chart

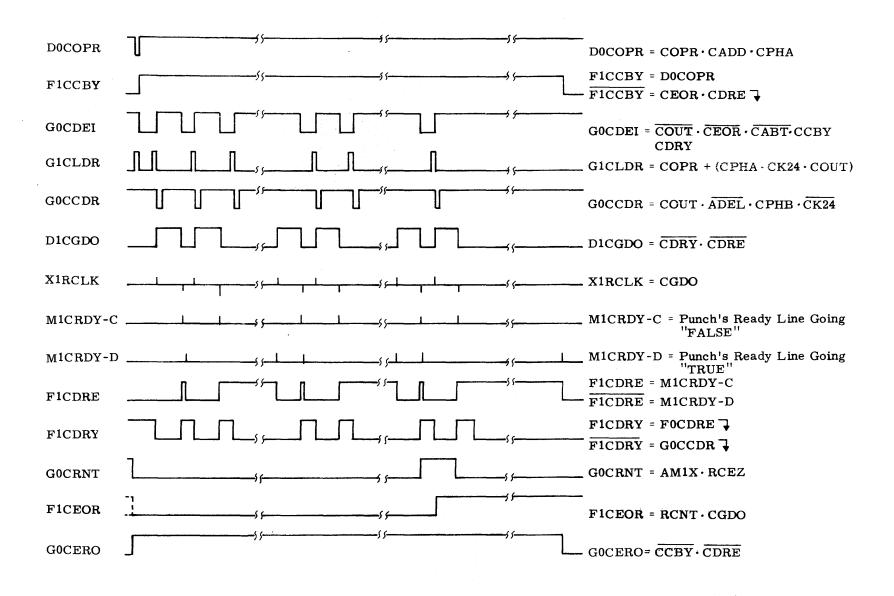

Fig. PTP. 3 Timing Diagram - Paper Tape Punch

#### **Busy Tests**

A JDR (Jump if Data Ready) or JCB (Jump if Channel Busy) test can be addressed to the drive logic to determine the respective data ready or channel busy status of the channel. Both commands are variations of the JNR command; the JDR is a JNR (2506 $_8$ ) with K1=4 and the JCB is a JNR with K1=2.

When the channel is addressed with K1=2, the status of the channel busy flip-flop is sampled by an AND input to GOATL1 of the drive logic. This line is routed through the Basic I/O Buffer to the AU where the decoded JCB causes the line to be sampled. Should the channel-busy (CCBY) or data-ready-enable (CDRE) flip-flops be set, the AND input is disabled and GOATL1's output is plus five volts. A plus five volt output indicates that the channel is busy and the program jumps to the second sequential location. If the channel-busy and data-ready-enable flip-flops are both cleared, the AND input to GOATL1 is enabled and GOATL1's output is zero volts. The zero volt output during the JCB's execution causes the program to step to the next sequential location.

Addressing the channel with K1=4 causes the data-exchange-interrupt gate (CDEI) to be sampled by the other AND input to G0ATL1. The decoded JDR causes the line to be sampled in the AU. Should the data-exchange-interrupt gate be at zero volts, indicating data is not ready, the AND input to G0ATL1 is disabled and G0ATL1's output is plus five volts. A plus five volt output indicates that the channel is busy and the program jumps to the second sequential location. If the data-exchange-interrupt gate is at plus five volts, indicating a data ready condition, the AND input to G0ATL1 is enabled and G0ATL1's output is zero volts. A zero volt output indicates the channel is ready to accept new data and the program steps to the next sequential location.

#### Media Enable

Channel action is initiated with the execution of an Operate (OPR) instruction, addressed to the output channel. OPR sets the channel-busy flip-flop (F1CCBY) which cycles the data-exchange interrupt, clears the end-of-record flip-flop (F1CEOR), and gates the eight least significant bits of the A-register to the column counter (via the holding register).

D0COPR = OPR.PHA.ADD

G0COPR = OPR•PHB•ADD

F1CCBY = G0COPR

FICEOR = G0COPR

GOCDEI = OUT · EOR · ABT · CBY · DRY

D1ROPR = G0COPR

Data being gated to the column counter is held temporarily in the holding register. At phase A of the OPR, the column counter is preset to "ones" and the data from the A-register is gated to the holding register.

At phase B of the OPR command, a single-ended transfer of the information in the holding register is made to the clear side of the column counter's flip-flops. This transfer is not significant for the paper tape drive function, but is used for the card punch drive.

#### Data Enable

As a result of the negative transition of signal GOCDEI, when the channel busy flip-flop (CBY) was set by the OPR command, an API is generated to inform the computer to initiate data transfers to the paper tape punch. These data transfers are accomplished using GEN II OUT commands. During phase A time of the OUT command, the load-data-register gate, D1CLDR, is enabled and the eight bits, including parity, from the basic I/O Buffer are gated to the holding register of the control drive:

D1CLDR = G0CLDR

$GOCLDR = PHA \cdot \overline{K24} \cdot OUT$

The transfer format (USASCII or EIA Standard) for the entire record was established by the status of the K1 bits during the OPR's execution. Mode 01 (K1 =  $01X_8$ ) establishes the EIA format; mode 00 (K1 =  $00X_8$ ) provides USASCII format. The corresponding translation is performed by gates at the output of the holding register.

USASCII format = G0AM01

EIA Std format = N1AM01

$N1AM01 = G0AM01 = MX1 \cdot \overline{M1X}$

MX1 = K1 equal to 2 during execution of OPR

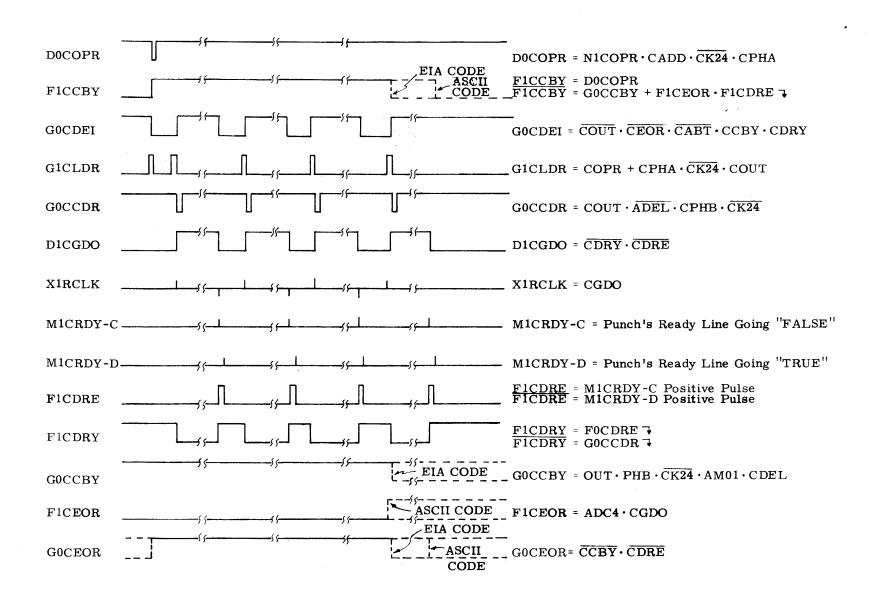

The data are transferred to the device through the output drivers. Accompanying the data is a clock signal, X1RCLK, to gate the data into the device's holding register. Both the clock signal's generation and the gating of data from the holding register to the output driver are accomplished by the gate-data-output signal, D1CGDO. D1CGDO is enabled upon receipt of the OUT command and remains "true" until a data received signal (Ready) is received from the device.

X1RCLK = D1CGDO

$D1CGDO = G0CGDO = \overline{N0CDRY} \cdot \overline{F0CDRE}$

$\overline{N0CDRY} = \overline{F1CDRY}$

F1CDRY = G0CCDR = OUT.DEL.PHB.K24

F1CDRY = F0CDRE going negative

(F0CDRE remains "true" during receipt of Ready signal from device)

The first X1RCLK signal activates the punch motor and when the motor is up to speed the first character is punched. Following the punch operation a ready signal (M1CRDY) is sent to the punch drive logic. The output of M1CDRY appears as a positive pulse at line receiver output "C" that corresponds to the leading edge of the ready signal from the device, followed by a positive pulse from "D" that corresponds to the trailing edge of the ready signal. The pulse from point C sets F1CDRE, which again clears when the pulse from point D is received. The output of the data-ready-enable flip-flop, F1CDRE, is used to set the data-ready flip-flop, F1CDRY, which enables the data-exchange-interrupt gate, G0CDEI, causing an API requesting new data.

The punch motor continues to run. With each OUT command that responds to the data exchange interrupt, characters are transferred to the punch in the manner described by the foregoing text until a media-disable code is recognized by the drive logic.

#### Media Disable

When punching in the USASCII format, the DC4 code (024<sub>8</sub>) follows the data and inter-record codes, is decoded in the drive logic, and is recognized as the end-of-record signal. The end-of-record flip-flop sets as soon as the DC4 code is recognized by the decode logic. However, the actual end-of-record interrupt is not generated until the character has been punched on the tape and the punch ready signal returned to the drive logic.

The end-of-record flip-flop, when set, enables the "clear" input to the channel-busy flip-flop, F1CCBY, which actually is triggered to the reset condition by

the trailing edge of the ready signal from the device. As F1CCBY clears, it enables G0CEOR to generate the end-of-record interrupt.

GOCERO = FICCBY FOCDRE

F1CCBY = F1CEOR•F1CDRE going negative

F1CEOR = G0CCER = DC4

F1CDRE goes negative on the trailing edge of the Ready signal from the punch.

When punching in the EIA Standard format, the DEL (no operation) code (177g) is used at the end of the record in place of the DC4 code. The DEL is decoded at phase A time of the OUT command that delivers it and prevents clearing of the data-ready flip-flop. This prevents the gate-data-output gate (CGDO) from being enabled and the character is not transmitted to the punch. At phase B of the same OUT command, the DEL code is used to clear the channel busy flip-flop, via GOCCBY. The clearing of F1CCBY enables the end-of-record gate, GOCEOR, generating the end-of-record interrupt.

F1CDRY = G0CCDR

GOCCDR = GOADEL

GOCEOR = F1CCBY DRE

F1CCBY = G0CCBY = OUT •K24 •MO1 • DEL

MO1 = EIA Standard Code established at OPR execution.

Regardless of which format is used, the device logic turns off the punch drive motor when there have been no X1RCLK (activate) signals from the control module for approximately one second.

#### **CARD PUNCH DRIVE**

The 4283 Card Punch connects to the I/O Buffer through the Punch Drive Logic to provide an output medium for permanently recording programs and data on 80-column cards. This is the only one of the two devices described in this publication that requires the use of the K1 = 4 bit when addressing the drive with an OPR command. As a result of the OPR's execution, the contents of the A-register are transferred to a column counter in the drive logic. Ultimately, this count determines the point at which the end-of-record interrupt is generated. This occurs when the column counter, decremented once with each data transfer that follows the OPR command, changes from zero to minus one.

Each card that is to be punched requires the execution of an OPR command to initiate a card punch operation. This is followed by the desired number of data transfers, established by the column count sent with the OPR command and requested by the device at the proper times.

Data are transferred to the punch in eight-bit bytes containing six information bits, one filler bit, and one parity bit. The parity bit is inserted by the basic I/O Buffer before it reaches the drive logic and is sampled when it reaches the device.

The format of the data punched on the card is established by the arrangement of the bits in the corresponding register of the AU at the time of their transfer to the punch. Transfers are binary and, except for the addition of the parity bit, the bits are unchanged. The transfer sequence is such that the first data transfer appears in rows 12, 11, 10, 1, 2 and 3, while the second transfer appears in rows 4 through 9 of column one. Succeeding column transfers are in the same order.

No special characters are utilized for communicating with the card punch. The record format sequence and the logical description of the drive's operation follows.

#### **RECORD FORMAT**

The outgoing record contains the following information in the format and sequence shown.

| Name                                       | Octal Format | Function        |  |  |

|--------------------------------------------|--------------|-----------------|--|--|

| OPR                                        | K1 = 11X     | Media<br>Enable |  |  |

| OUT - column 1 (12-3)                      |              |                 |  |  |

| - column 1 (4-9)                           |              |                 |  |  |

| - column 2 (12-3)                          |              |                 |  |  |

| - column 2 (4-9)                           |              |                 |  |  |

| - column X* (12-3)                         |              |                 |  |  |

| OUT - column X (4-9)                       |              |                 |  |  |

| * X = last column requested to be punched. |              |                 |  |  |

#### **INTERRUPTS**

Model 4283 Card Punches utilize two interrupts. A data-exchange-ready interrupt signals the computer each time data is required by the device and an end-of-record interrupt signals the computer after a punch cycle is completed. The data-exchange-ready interrupt is normally non-inhibitable and the end-of-record interrupt is usually inhibitable.

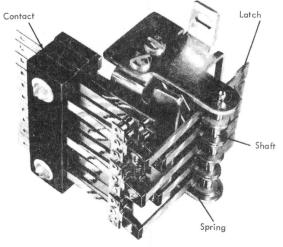

#### LOGIC DESCRIPTION

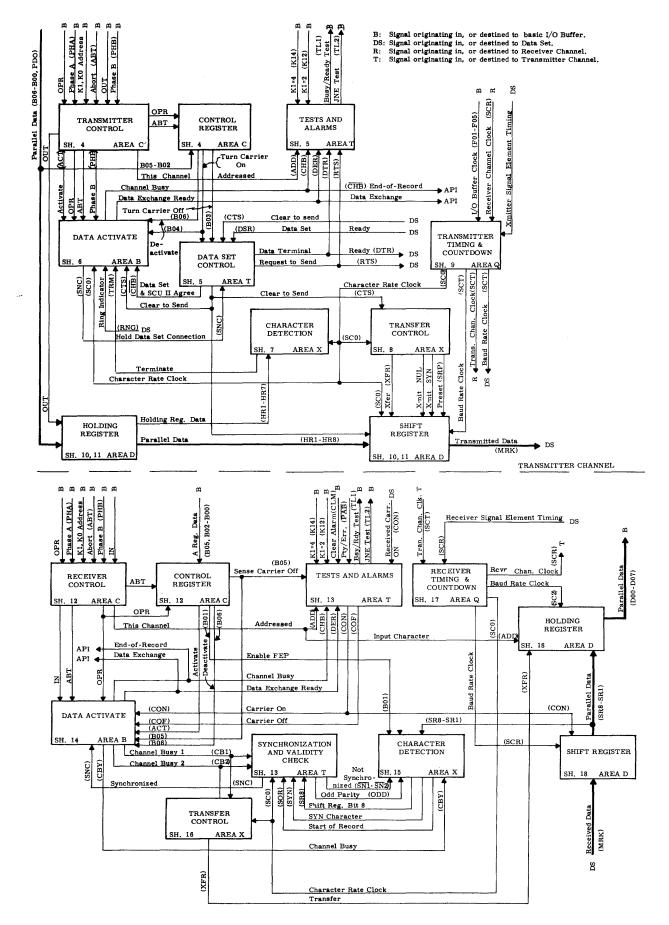

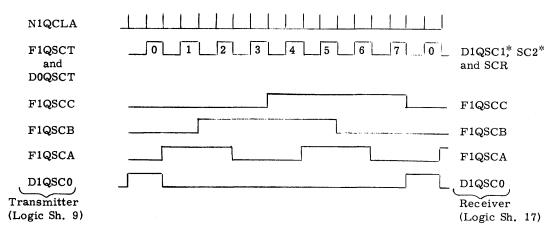

This description covers the logic that appears on drawing 70C180346, as it pertains to interfacing the card punch with the Basic I/O Buffer. The description of the Basic I/O Buffer precedes this publication in this section of the manual. The device description is also found in this volume under publication number 4283. Reference should be made to the simplified block diagram, Fig. CP.1, the flow chart, Fig. CP.2, and the timing diagram, Fig. CP.3.

#### **Alarms**

The following alarm conditions can be detected by using properly encoded JNE instructions addressed to the drive logic:

- Test Line 0 Test Line 0 is designated the

"Halt" line by the Serial Card

Punch Logic. It is "true"

whenever any detectable punch

problem occurs or the punch

is switched to the off-line

mode.

- Test Line 1 Indicates an interlock open, a punch error, registration error, or a jam.

- Test Line 2 Indicates that either the input hopper is empty or the output stacker is full.

- Test Line 3 Indicates a data parity error, a card eject late, or a data late condition.

Definitions of the individual alarms can be found in the 4283 Serial Card Punch Theory publication.

All four alarm lines are sampled at gate GOATL2 in the drive logic. The specific line sampled during the JNE command's execution is determined by the status of the JNE's K1 bits:

- K1 = 00X Test Line 0

- K1 = 01X Test Line 1

Fig. CP. 1 Simplified Block Diagram - Card Punch Drive

- K1 = 10X Test Line 2

- K1 = 11X Test Line 3

The output of G0ATL2 is routed through the Basic I/O Buffer to the AU where the decoded JNE causes the line to be sampled. Should the test line being sampled be "true", the corresponding AND input is enabled and G0ATL2 yields 0V. A 0V output during the JNE's execution causes the program to step to the next sequential location, indicating an error condition. If the test line being sampled is "false", the AND gate is disabled and G0ATL2's output will be +5V. A +5V output indicates that there is no error and the program jumps to the second sequential location.

G0ATL2 = CADD (

$$\overline{K14} \cdot \overline{K12} \cdot \text{TL} \cdot 0 + \overline{K14} \cdot \overline{K12} \cdot \text{TL} + \overline{K14} \cdot \overline{K12} \cdot \text{TL} + \overline{K14} \cdot \overline{K12} \cdot \text{ALM}$$

)

F1AALM = CBY•TL3

Test line 3 going "true" sets the drive logic's alarm flip-flop. While set, the output drives an alarm display. This flip-flop is cleared, turning off the display, when the clear alarm switch is depressed, or when an Operate or Abort command are sent to the drive logic.

#### **Busy Tests**

A JDR (Jump if Data Ready) or JCB (Jump if Channel Busy) test can be addressed to the drive logic to determine the respective data ready or channel busy status of the channel. Both commands are variations of the JNR command; the JDR is a JNR ( $2506_8$ ) with K1 = 4 and the JCB is a JNR with K1 = 2.

When the channel is addressed with K1 = 2, the status of the channel busy (CCBY) flip-flop is sampled by an AND input to G0ATL1 of the drive logic. This line is routed through the Basic I/O Buffer to the AU where the decoded JCB causes the line to be sampled. Should the channel-busy (CCBY) or dataready-enable (CDRE) flip-flops be set, the AND input is disabled and G0ATL1's output is +5V. A+5V output indicates that the channel is busy and the program jumps to the second sequential location. If the channel-busy and data-ready-enable flip-flops are both cleared, the AND input to G0ATL1 is enabled and G0ATL1's output is 0V. The 0V output during the JCB's execution causes the program to step to the next sequential location.

Addressing the channel with K1 = 4 causes the data-exchange-interrupt gate (CDEI) to be sampled by the other AND input to GOATL1. The decoded JDR causes the line to be sampled in the AU. Should the data-exchange-interrupt gate be at 0V, indicating data is not ready, the AND input to GOATL1 is disabled and GOATL1's output is +5V. A +5V output indicates that the channel is busy and the program jumps to the second sequential location. If the

data-exchange-interrupt gate is at +5V, indicating a data ready condition, the AND input to G0ATL1 is enabled and G0ATL1's output is 0V. A 0V output indicates the channel is ready to accept new data and the program steps to the next sequential location

#### Media Enable

Channel action is initiated with the execution of an OPERATE (OPR) instruction, addressed to the output channel. OPR sets the channel-busy flip-flop (F1CCBY), which cycles the data-exchange interrupt, clears the end-of-record flip-flop (F1CEOR), and gates the eight least significant bits of the A-register to the column counter (via the drive's holding register).

D0COPR = OPR.PHA.ADD

G0COPR = OPR.PHB.ADD

F1CCBY = G0COPR

F1CEOR = G0COPR

G0CDEI = OUT.EOR.ABT.CBY.DRY

D1ROPR = G0COPR

During phase A of the OPR command, the column counter is preset to "ones" and the data from the I/O Buffer is gated into the drive logic's holding register. A direct transfer of the eight bits from the basic I/O Buffer is made to the holding register. Bit seven is gated into the holding register's parity flip-flop while the parity bit from the Buffer is ignored due to the enabling of GOCBIN. GOCBIN is enabled throughout the execution time of the OPR command.

At phase B time, the data is gated from the holding register to the clear sides of the column counter's flip-flops. In each case where there was a "zero" in the corresponding bit of the holding register, the column counter flip-flop is DC cleared. This establishes the column count for the card and will determine the point in the card where punching will terminate.

#### Data Enable

As a result of the negative transition of signal GOCDEI, when the channel busy flip-flop (CBY) was set by the OPR command, an API is generated to inform the computer to initiate data transfers to the card punch. These data transfers are accomplished using GEN II OUT commands. During phase A time of the OUT command, the load-data-register gate, D1CLDR, is enabled and the eight bits, including parity, from the basic I/O Buffer are gated to the holding register of the control drive:

D1CLDR = G0CLDR

GOCLDR = PHA · K24 · OUT

Although the transfer of information during the execu-

Fig. CP. 2 Card Punch Drive Flow Chart

tion of the OPR was strictly binary, with the parity bit being ignored, data transfers during OUT commands will be binary with the parity bit included. The parity will be checked in the punch upon its receipt of the data from the drive logic.

The data are transferred to the device through the drive logic's output drivers. Accompanying the data is a clock signal, X1RCLK, to inform the punch logic that the data is available. Both the clock signal's generation and the gating of data from the holding register to the output drivers are accomplished by the gate-data-output signal, D1CGDO. D1CGDO is enabled upon receipt of the OUT command and remains "true" until a data-received signal (Ready) is received from the punch.

X1RCLK = D1CGDO

D1CGDO = G0CGDO = N0CDRY•F0CDRE

NOCDRY = F1CDRY

F1CDRY = G0CCDR = OUT•DEL•PHB•K24

F1CDRY = F0CDRE going negative

Upon recognition of the data from the drive logic, the punch's ready flip-flop, F1CRDY is "cleared". (The punch's ready flip-flop should not be confused with the drive logic's flip-flop, F1CDRY.) When the punch's ready flip-flop goes "false", it causes a pulse to be transmitted through transformer coupled drive lines to line receiver M1CRDY in the drive logic. The resulting positive pulse from pin "C" of M1CRDY ANDs with G0CHLT to cause the output of G1CSDE to go to zero volts. This sets the dataready-enable flip-flop, F1CDRE. F0CDRE, going to zero volts, disables the gate-data-out gate (CGDO) and causes the drive logic's ready flip-flop (CDRY) to set. The setting of F1CDRY causes the data-exchange-interrupt line (CDEI) to go to zero volts, initiating an interrupt request for new data.

GOCDEI = COUT CEOR CABT CCBY CDRY

CDRY = F0CDRE going negative

CGDO = F0CDRE

CDRE = G1CSDE at zero volts