◆DataGeneral

ECLIPSE® 32-Bit Systems Principles of Operation

**◆**DataGeneral

# **ECLIPSE® 32-Bit Systems** Principles of Operation

#### **Notice**

Data General Corporation (DGC) has prepared this document for use by DGC personnel, customers, and prospective customers. The information contained herein shall not be reproduced in whole or in part without DGC's prior written approval.

DGC reserves the right to make changes in specifications and other information contained in this document without prior notice, and the reader should in all cases consult DGC to determine whether any such changes have been made.

THE TERMS AND CONDITIONS GOVERNING THE SALE OF DGC HARD-WARE PRODUCTS AND THE LICENSING OF DGC SOFTWARE CONSIST SOLELY OF THOSE SET FORTH IN THE WRITTEN CONTRACTS BETWEEN DGC AND ITS CUSTOMERS. NO REPRESENTATION OR OTHER AFFIRMATION OF FACT CONTAINED IN THIS DOCUMENT INCLUDING BUT NOT LIMITED TO STATEMENTS REGARDING CAPACITY, RESPONSE-TIME PERFORMANCE, SUITABILITY FOR USE OR PERFORMANCE OF PRODUCTS DESCRIBED HEREIN SHALL BE DEEMED TO BE A WARRANTY BY DGC FOR ANY PURPOSE, OR GIVE RISE TO ANY LIABILITY OF DGC WHATSOEVER.

IN NO EVENT SHALL DGC BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS DOCUMENT OR THE INFORMATION CONTAINED IN IT, EVEN IF DGC HAS BEEN ADVISED, KNEW OR SHOULD HAVE KNOWN OF THE POSSIBILITY OF SUCH DAMAGES.

DASHER, DATAPREP, ECLIPSE, ENTERPRISE, INFOS, microNOVA, NOVA, PROXI, SUPERNOVA, ECLIPSE MV/6000, ECLIPSE MV/8000, TRENDVIEW, MANAP, and PRESENT are U.S. registered trademarks of Data General Corporation, and AZ-TEXT, DG/L, ECLIPSE MV/4000, ECLIPSE MV/9000, REV-UP, SWAT, XODIAC, GENAP, DEFINE, CEO, SLATE, microECLIPSE, BusiPEN, BusiGEN, and BusiTEXT are U.S. trademarks of Data General Corporation.

Ordering No. 014-000704

© Data General Corporation, 1981, 1982, 1983, 1984

All Rights Reserved

Printed in the United States of America

Rev. 03, August 1984

Revision History: Original Release - December 1981 First Revision - March 1982 Second Revision - February 1983

Third Revision - August 1984

# **Preface**

The *Principles of Operation 32-Bit* ECLIPSE® *Systems* manual explains the processor independent concepts, functions, and instruction set to an assembler programmer. The processor dependent information can be found in a companion manual — a processor specific functional characteristics manual.

The companion manual, which contains information such as physical memory size and instruction execution times, is organized with a structure similar to that of the *Principles of Operation 32-Bit* ECLIPSE® *Systems* manual. The similar structures make it easier to locate the cross-referenced information.

Another related manual, the ECLIPSE MV/Family Instruction Reference Booklet, presents a brief summary of the instruction set and related information. The reference booklet lists each instruction by assembler-recognizable mnemonic with a shorthand description of their function.

# **Organization**

The 32-bit Principles of Operation manual contains 10 chapters.

Chapter 1 presents the system overview.

Chapters 2-9 present (in a functional framework) the processor independent concepts, functions, and instruction set. The chapters explain:

- Fixed-point computation

- Floating-point computation

- Stack management

- Program flow management

- Queue management

- · Device management

- System and memory management

- ECLIPSE C/350 compatible instructions

Chapter 10 presents the instruction dictionary (alphabetical order).

Appendices A-E present anomalies, ASCII codes, powers of 2 table, fault codes, and the glossary.

# **Standard Symbols**

The manual uses certain conventions and abbreviations.

| []                              | The square brackets indicate an optional argument. Omit the square brackets when you include an optional argument with an Assembler statement.                                                          |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UPPERCASE<br>and/or<br>Boldface | Uppercase or boldface characters indicate a literal argument in an Assembler statement. When you include a literal argument with an Assembler statement, use the exact form.                            |

| lowercase<br>and/or<br>Italic   | Lowercase or italic characters indicate a variable argument in an Assembler statement. When you include the argument with an Assembler statement, substitute a literal value for the variable argument. |

| *                               | An asterisk indicates multiplication. For instance, 2*3 means 2 multiplied by 3.                                                                                                                        |

| ac                              | The ac abbreviation indicates a fixed-point accumulator                                                                                                                                                 |

| acs                             | The acs abbreviation indicates a fixed-point accumulator called a source accumulator.                                                                                                                   |

| acd                             | The acd abbreviation indicates a fixed-point accumulator called a destination accumulator.                                                                                                              |

| fac                             | The fac abbreviation indicates a floating-point accumulator                                                                                                                                             |

| facs                            | The facs abbreviation indicates a floating-point accumulator called a <i>source accumulator</i> .                                                                                                       |

| facd                            | The facd abbreviation indicates a floating-point accumulator called a destination accumulator.                                                                                                          |

# **Table of Contents**

| 1 | System Overview                       |      |

|---|---------------------------------------|------|

|   | Functional Capabilities               | 1-1  |

|   | Fixed-Point Computation               | 1-2  |

|   | Floating-Point Computation            | 1-3  |

|   | Stack Management                      | 1-4  |

|   | Program Flow Management               | 1-5  |

|   | Queue Management                      | 1-5  |

|   | Device Management                     | 1-5  |

|   | System Management                     | 1-6  |

|   | Memory Management                     | 1-6  |

|   | ECLIPSE C/350 Compatible Instructions | 1-8  |

|   | Accessing Memory                      | 1-8  |

|   | Current Segment                       | 1-8  |

|   | Other Segments                        | 1-9  |

|   | Memory Reference Instructions         | 1-9  |

|   | Address Modes                         | 1-10 |

|   | Indirect and Effective Addresses      | 1-11 |

|   | Operand Access                        | 1-12 |

|   | Protection Capabilities               | 1-16 |

|   | Summary                               | 1-17 |

| 2 | Fixed-Point Computing                 |      |

|   | Overview                              | 2-1  |

|   | Binary Operation                      | 2-1  |

|   | Data Formats                          | 2-1  |

|   | Move Instructions                     | 2-3  |

|   | Arithmetic Instructions               | 2-3  |

|   | Carry Operations                      | 2-5  |

|   | Shift Instructions                    | 2-6  |

|   | Skip Instructions                     | 2-7  |

|   | Overflow Fault                        | 2-8  |

|   | Processor Status Register             | 2-9  |

|   | Logical Operation                     | 2-12 |

|   | Data Formats                          | 2-12 |

|   | Logic Instructions                    | 2-12 |

|   | Shift Instructions                    | 2-14 |

|   |                                       |      |

vi Table of Contents

|          | Skip Instructions                                             | 2-14 |

|----------|---------------------------------------------------------------|------|

|          | Decimal and Byte Operations                                   | 2-15 |

|          | Data Formats                                                  | 2-16 |

|          | Move Instructions                                             | 2-20 |

|          | Arithmetic Instructions                                       | 2-22 |

|          | Shift Instructions                                            | 2-22 |

|          | Skip Instructions                                             | 2-22 |

|          | Data Type Faults                                              | 2-23 |

|          | Decimal Arithmetic Example                                    | 2-23 |

| 3        | Floating-Point Computing                                      |      |

|          | Overview                                                      | 3-1  |

|          | Data Formats                                                  | 3-1  |

|          | Move Instructions                                             | 3-3  |

|          | Floating-Point Arithmetic Operations                          | 3-4  |

|          | Appending Guard Digits                                        | 3-4  |

|          | Aligning the Mantissas                                        | 3-5  |

|          | Calculating and Normalizing the Result                        | 3-5  |

|          | Truncating or Rounding the Result                             | 3-5  |

|          | Storing the Result                                            | 3-6  |

|          | Arithmetic Instructions                                       | 3-6  |

|          | Addition                                                      | 3-6  |

|          | Subtraction                                                   | 3-7  |

|          | Multiplication                                                | 3-7  |

|          | Division                                                      | 3-8  |

|          | Skip Instructions                                             | 3-8  |

|          | Faults and Status                                             | 3-9  |

| 4        | Stack Management                                              |      |

|          | Overview                                                      | 4-1  |

|          | Wide Stack Operations                                         | 4-1  |

|          | Wide Stack Registers                                          | 4-2  |

|          | Wide Stack Base                                               | 4-2  |

|          | Wide Stack Limit                                              | 4-2  |

|          | Wide Stack Pointer                                            |      |

|          | Wide Frame Pointer                                            | 4-3  |

|          |                                                               | 4-3  |

|          | Wide Stack Register Instructions Wide Stack Data Instructions | 4-4  |

|          |                                                               | 4-4  |

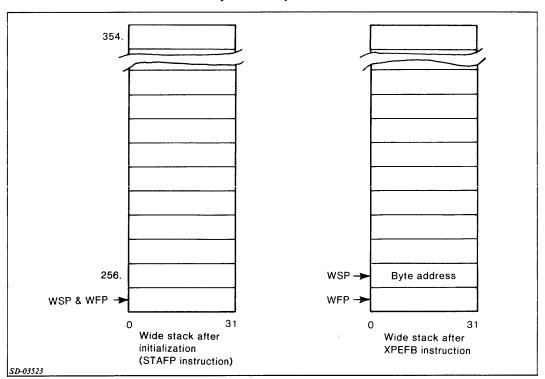

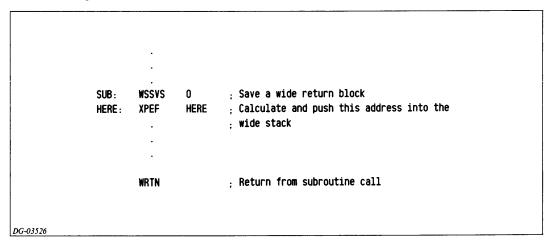

|          | Initializing A Wide Stack                                     | 4-6  |

|          | Wide Stack Faults                                             | 4-7  |

| <u>5</u> | Program Flow Management                                       |      |

|          | Overview                                                      | 5-1  |

|          | Program Flow                                                  | 5-1  |

|          | Related Instruction Groups                                    | 5-2  |

|          | Execute Accumulator                                           | 5-2  |

|          | Jump                                                          | 5-2  |

|          | Skip                                                          | 5-2  |

|          | Subroutine                                                    | 5-4  |

|          | Transferring Program Control to Another Segment               | 5-9  |

|          | Subroutine Call                                               | 5-9  |

|          | Subroutine Return                            | 5-13 |

|----------|----------------------------------------------|------|

|          | Fault Handling                               | 5-13 |

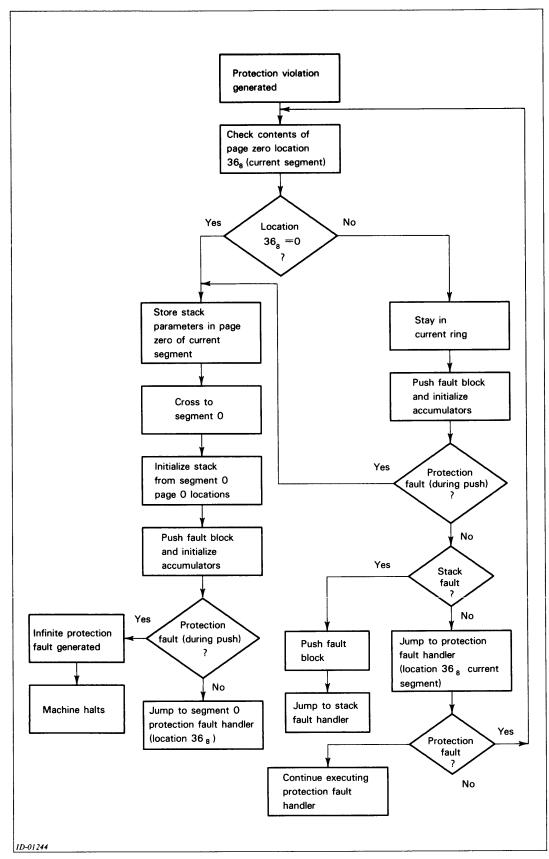

|          | Protection Violations                        | 5-14 |

|          | Umimplemented Instructions                   | 5-19 |

|          | Fixed-Point Overflow Fault                   | 5-19 |

|          | Floating-Point Overflow and Underflow Faults | 5-20 |

|          | Decimal and ASCII Data Faults                | 5-21 |

|          | Stack Faults                                 | 5-25 |

| <u>6</u> | Queue Management                             |      |

|          | Queues                                       | 6-1  |

|          | Building a Queue                             | 6-1  |

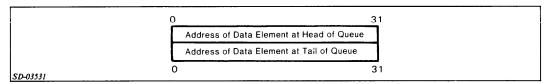

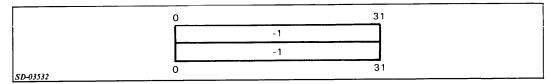

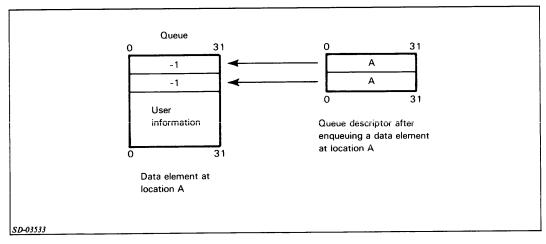

|          | Queue Descriptor                             | 6-2  |

|          | Setting Up and Modifying a Queue             | 6-2  |

|          | Examples                                     | 6-3  |

|          | Queue Instructions                           | 6-5  |

| 7        | Device Management                            |      |

|          | Overview                                     | 7-1  |

|          | Device Access                                | 7-1  |

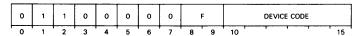

|          | General I/O Instructions                     | 7-3  |

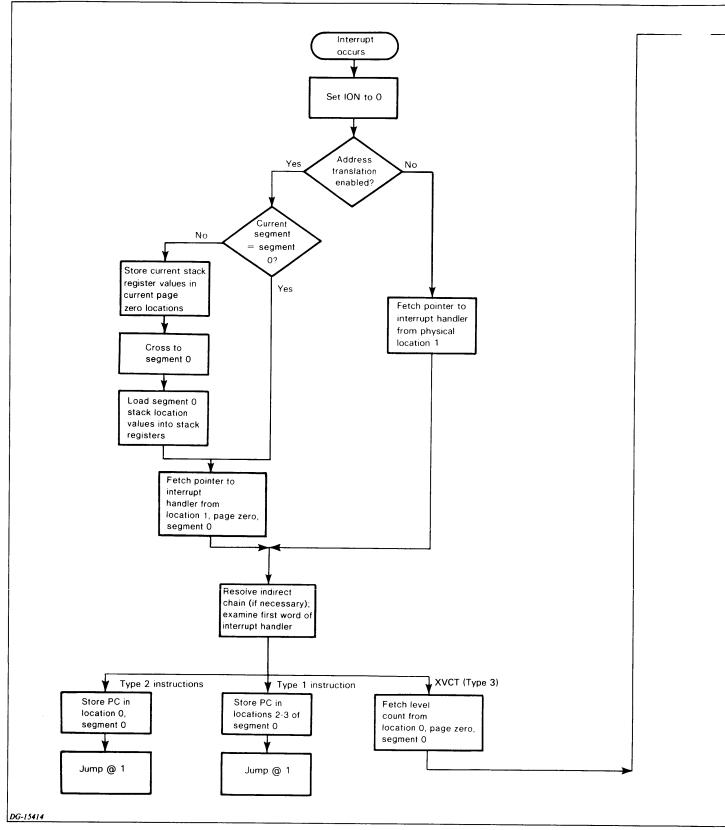

|          | Interrupts                                   | 7-5  |

|          | Interrupt On Flag                            | 7-6  |

|          | Instruction Interruption                     | 7-6  |

|          | Interrupt Mask                               | 7-6  |

|          | Interrupt Servicing                          | 7-6  |

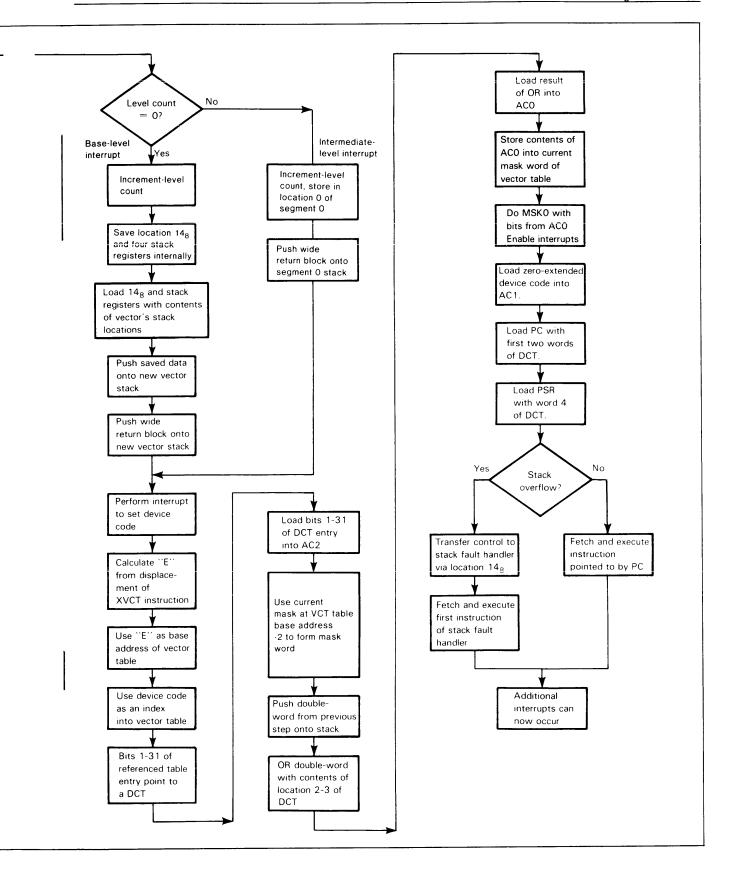

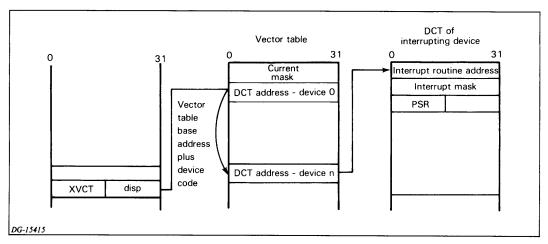

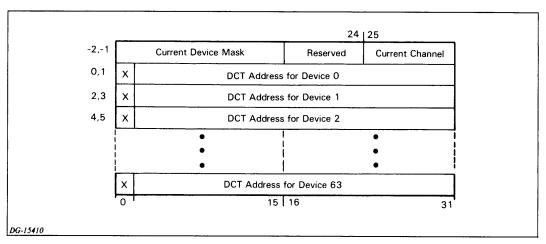

|          | Vectored Interrupt Processing                | 7-10 |

|          | Base-Level Interrupt Processing              | 7-10 |

|          | Intermediate-Level Interrupt Processing      | 7-11 |

|          | Final Interrupt Processing                   | 7-11 |

| 8        | Memory and System Management                 |      |

|          | Overview                                     | 8-1  |

|          | Segment Access and Address Translation       | 8-2  |

|          | Segment Base Registers                       | 8-2  |

|          | Page Tables                                  | 8-4  |

|          | Address Translation                          | 8-6  |

|          | Page Access                                  | 8-7  |

|          | Central Processor Identification             | 8-11 |

|          | Protection Violations                        | 8-12 |

| 9        | C/350 Programming                            |      |

|          | Overview                                     | 9-1  |

|          | C/350 Registers                              | 9-1  |

|          | C/350 Stack                                  | 9-2  |

|          | C/350 Faults and Interrupts                  | 9-3  |

|          | Expanding an ECLIPSE C/350 Program           | 9-3  |

|          | Expanding an ECLIPSE C/350 Subroutine        | 9-4  |

|           | C/350 Instructions                  | 9-4  |

|-----------|-------------------------------------|------|

|           | C/350 Memory Reference Instructions | 9-4  |

|           | Fixed-Point Instructions            | 9-7  |

|           | Floating-Point Instructions         | 9-9  |

|           | Program Flow Instructions           | 9-10 |

|           | Stack Instructions                  | 9-11 |

| <u>10</u> | Instruction Dictionary              |      |

|           |                                     |      |

| A         | Anomalies                           |      |

|           | C/350 Instruction Results           | A-1  |

|           | Wide Instruction Opcodes            | A-1  |

|           | Program Counter Wraparound          | A-1  |

|           | Float/Fixed Conversions             | A-1  |

|           | Address Wraparound                  | A-2  |

|           | C/350 Signed Divide Instructions    | A-2  |

|           | NIO CPU Instructions                | A-2  |

|           | Floating-Point Trap                 | A-2  |

|           | Floating-Point Numerical Algorithms | A-2  |

|           | C/350 Commercial Faults             | A-3  |

| B         | ASCII Codes                         |      |

| C         | Powers of 2 Table                   |      |

|           |                                     |      |

| <u>D</u>  | Fault Codes                         |      |

|           | Protection Faults                   | D-1  |

|           | Stack Faults                        | D-2  |

|           | Decimal/ASCII Faults                | D-2  |

| E         | Glossary                            |      |

|           | The Addressing Scheme               | E-1  |

|           | Logical Addresses                   | E-1  |

|           | Segmentation                        | E-1  |

|           | Mapping and Demand Paging           | E-1  |

|           | Page                                | E-1  |

|           | Page Table                          | E-1  |

|           | Protection                          | E-2  |

|           | The Instruction Set                 | E-2  |

|           | Wide Instructions                   | E-2  |

|           | C/350 Compatibility                 | E-2  |

|           | True and Impure Zero                | E-2  |

|           | Normalized Format                   | E-3  |

|           | Magnitude                           | E-3  |

# Chapter 1 System Overview

# **Functional Capabilities**

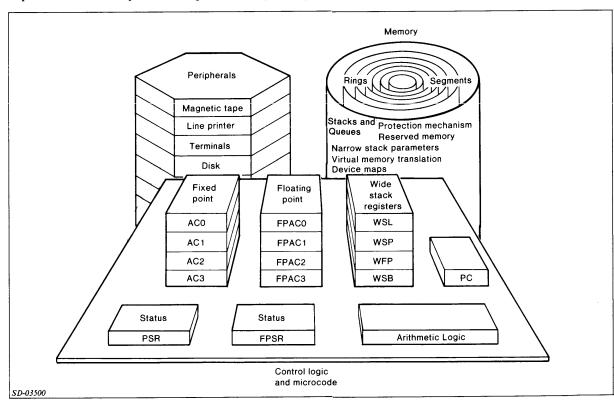

The ECLIPSE® 32-bit central processor -- hereafter called the processor -- provides facilities to manage data, to access memory, and to control program flow (see Figure 1.1).

The processor can perform fixed-point or floating-point computation, as well as stack, program, queue, device, system, and memory management. In addition, the processor contains the ECLIPSE C/350 compatible instructions for 16-bit program development and upward program compatibility.

This System Overview chapter provides a brief description of the processor functional capabilities, memory address space, and system protection capabilities.

Figure 1.1 Functional components

#### **Fixed-Point Computation**

Fixed-point computation consists of fixed-point binary arithmetic with signed and unsigned 16-bit and 32-bit numbers. The processor also performs decimal arithmetic, logical operations, and manipulates 8-bit bytes.

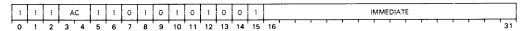

The processor contains four 32-bit fixed-point accumulators (AC0-AC3) and a processor status register (PSR). The following two sections summarize the fixed-point registers. Refer to the Fixed-Point Computing chapter for additional information.

**NOTE:** The lower numbered bit of a register (such as bit 0) is the most significant bit. The higher numbered bit (such as bit 31) is the least significant bit.

#### **Fixed-Point Accumulators**

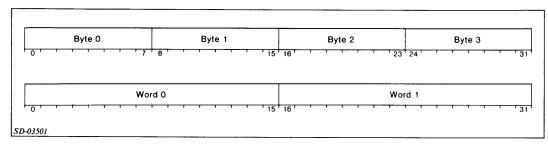

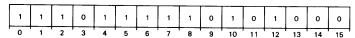

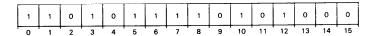

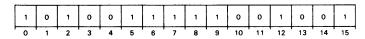

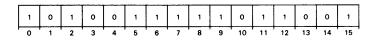

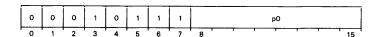

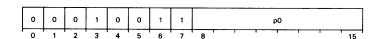

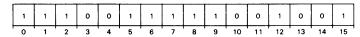

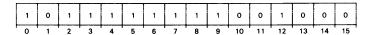

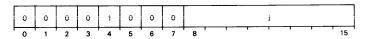

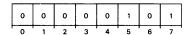

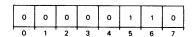

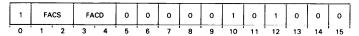

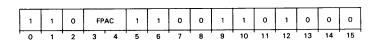

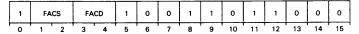

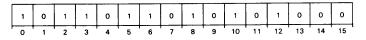

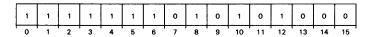

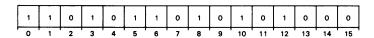

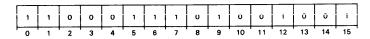

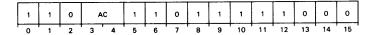

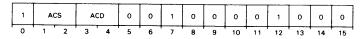

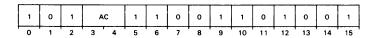

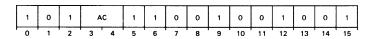

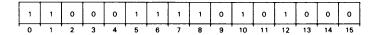

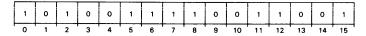

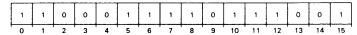

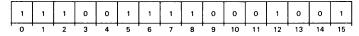

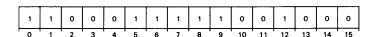

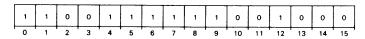

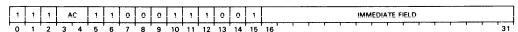

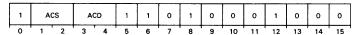

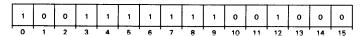

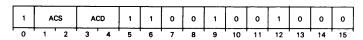

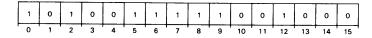

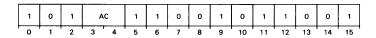

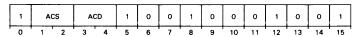

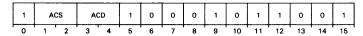

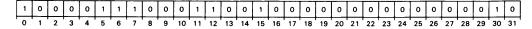

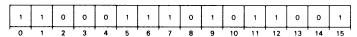

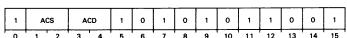

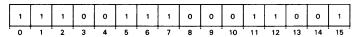

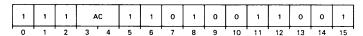

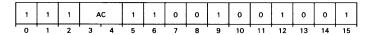

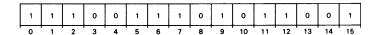

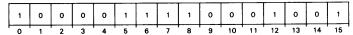

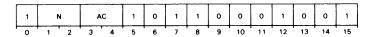

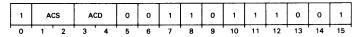

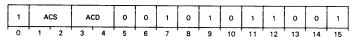

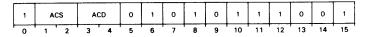

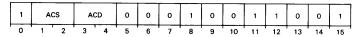

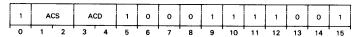

You access a fixed-point accumulator with instructions that manipulate a bit, byte, word, or double word (see Figure 1.2).

Figure 1.2 Fixed-point accumulator

A word or double word operand must begin on a word boundary (bit 0 or 16); a byte must begin on a byte boundary.

In addition to using an accumulator for fixed-point computation

- You can read a fault code in AC1, which the processor stores in the accumulator.

- · You can load or build an instruction in an accumulator, and then execute it.

- You can use AC2 or AC3 in relative addressing (in place of the program counter).

#### **Processor Status Register**

The processor status register contains status flags such as an overflow fault service mask and a fixed-point overflow fault flag. The overflow fault service mask enables or disables the processor from servicing the fault. The processor sets the overflow fault flag when the results of a fixed-point computation exceed the processor storage capacity. The remaining flags are processor-dependent.

You can access the processor status register bits with instructions that set a bit or that test and skip on condition of a bit. Refer to the Fixed-Point Computing chapter for additional information.

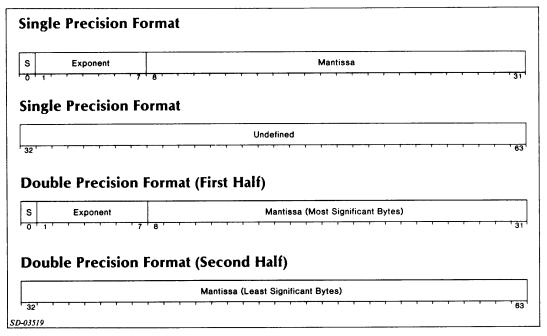

#### Floating-Point Computation

Floating-point computation consists of floating-point binary arithmetic with signed, single precision (32-bits) and double precision (64-bits), numbers.

The processor contains four 64-bit floating-point accumulators (FPAC0- FPAC3) and a floating-point status register (FPSR). The following two sections summarize the floating-point registers. Refer to the Floating-Point Computing chapter for additional information.

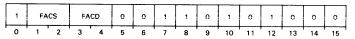

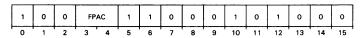

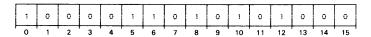

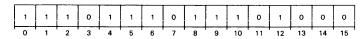

#### Floating-Point Accumulators

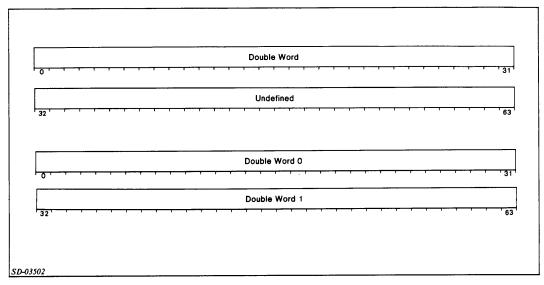

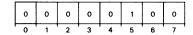

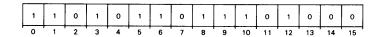

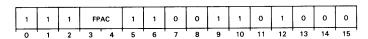

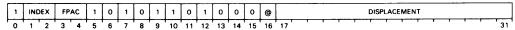

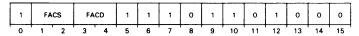

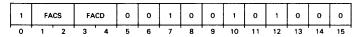

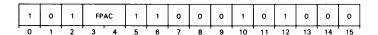

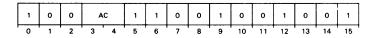

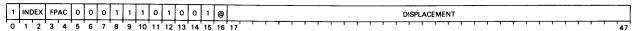

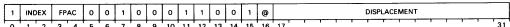

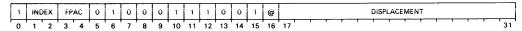

You access a floating-point accumulator with instructions that manipulate single and double precision floating-point numbers (see Figure 1.3).

Figure 1.3 Floating-point accumulator

A single precision number requires a double word (two consecutive words), while a double precision number requires two double words (four consecutive words).

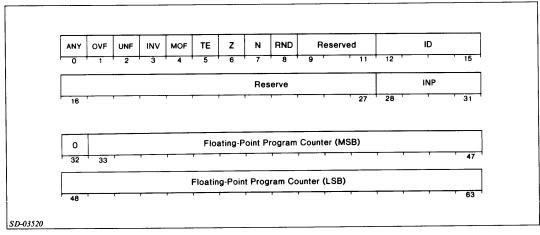

#### Floating-Point Status Register

The floating-point status register contains overflow and underflow fault flags, fault service mask, mantissa status flags, rounding flag, and processor status flags.

The processor sets an overflow or underflow fault flag when the result of a floating-point computation exceeds the processor storage capacity. The fault service mask enables or disables the processor from servicing a fault. The remaining flags provide processor status.

You can access the contents of the register with instructions to initialize it or to test and skip on a condition.

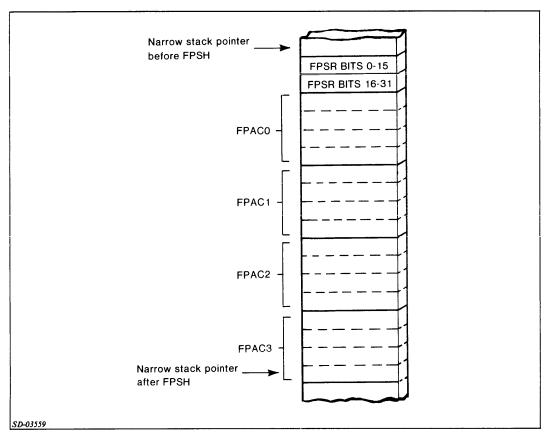

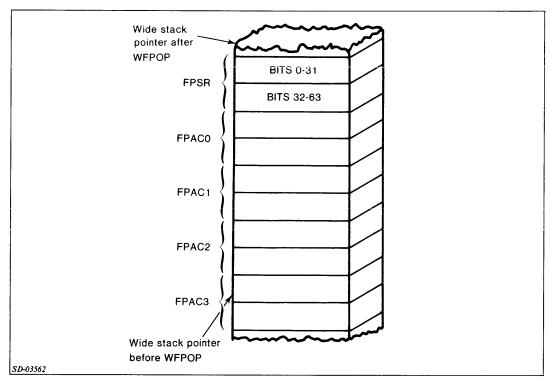

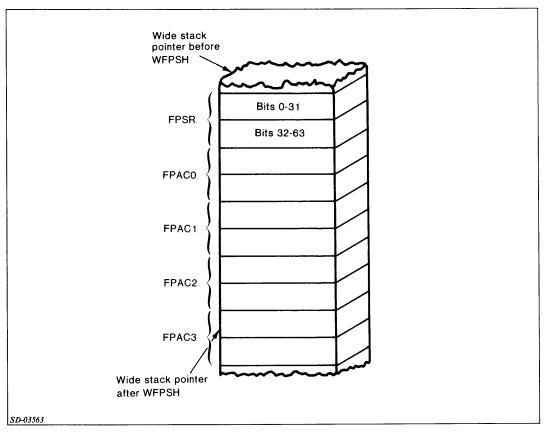

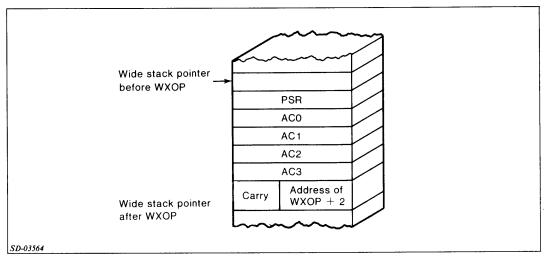

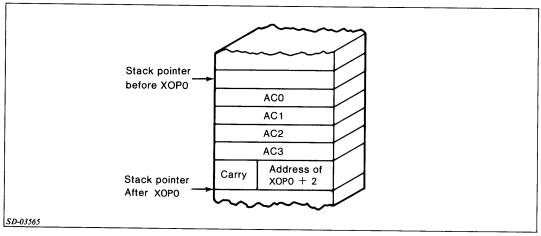

#### Stack Management

The processor contains facilities for narrow and wide stack management. A stack is a series of consecutive locations in memory. Typically, a program uses a stack to pass arguments between subroutine calls and to save the program state when servicing a fault. After executing a subroutine or fault handler, the processor restores the program and continues program execution.

The narrow stack consists of a contiguous set of words for supporting ECLIPSE C/350 program development and upward program compatibility. Narrow stack management includes three 16-bit narrow stack management parameters. Refer to the C/350 Programming chapter for additional information on the narrow stack.

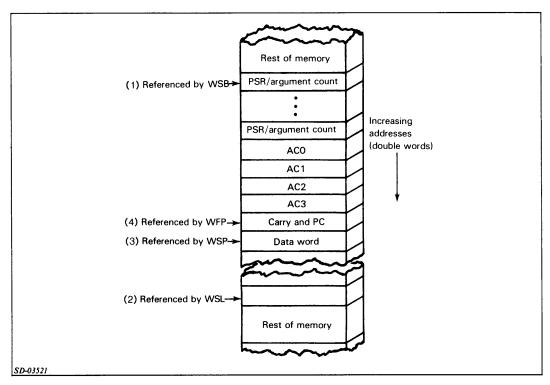

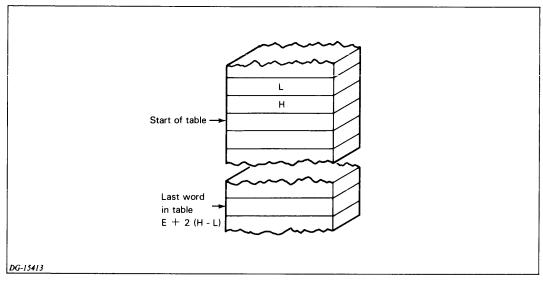

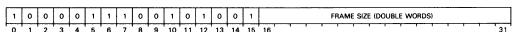

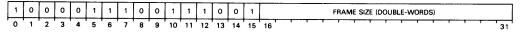

The wide stack consists of a contiguous set of double words for supporting the 32-bit processor programs. Wide stack management includes four 32-bit wide stack management parameters, for each memory segment. (A memory segment is a logically addressable subset of memory. Refer to the Memory Management section for additional information on memory and segments.)

Wide stack management for the current segment also includes four 32-bit wide stack management registers. (The segment field of the program counter defines the *current segment*.) The Stack Management section summarizes the wide stack concepts. Refer to the Stack Management chapter for additional information on the wide stack.

The following list summarizes the wide stack management registers.

- The wide stack base (WSB) defines the lower limit of the wide stack.

- The wide stack limit (WSL) defines the upper limit of the wide stack.

- The wide stack pointer (WSP) addresses the current location on the wide stack.

- The wide frame pointer (WFP) defines a reference point.

You access a stack management register with instructions that load or store a register value.

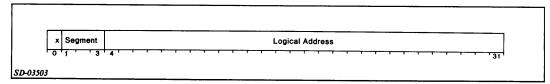

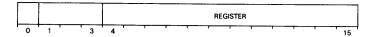

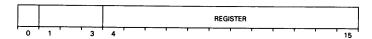

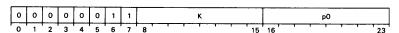

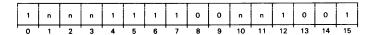

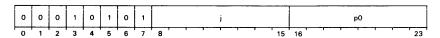

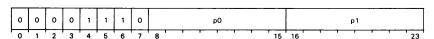

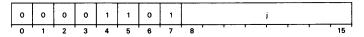

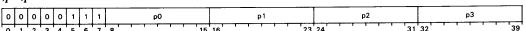

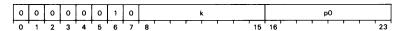

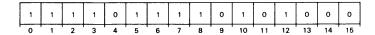

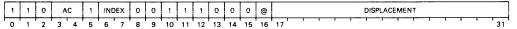

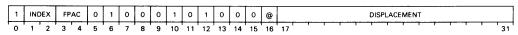

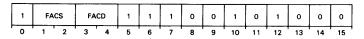

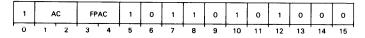

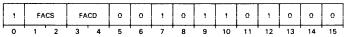

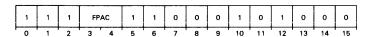

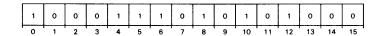

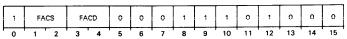

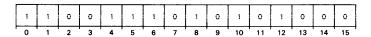

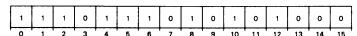

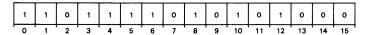

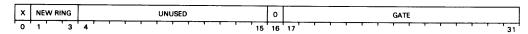

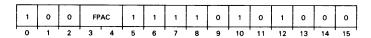

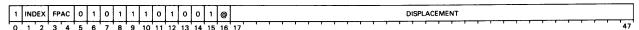

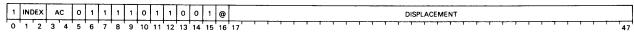

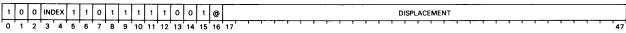

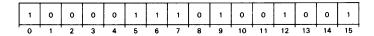

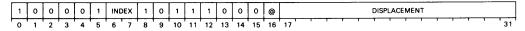

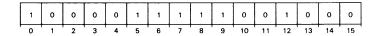

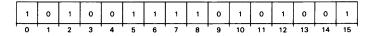

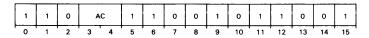

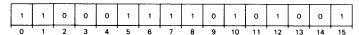

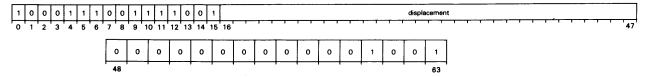

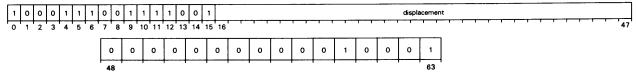

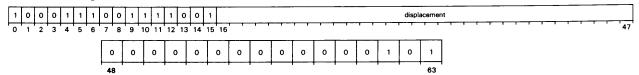

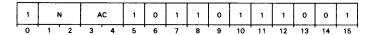

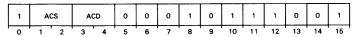

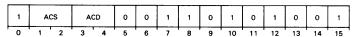

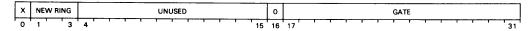

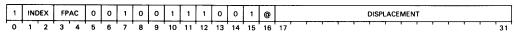

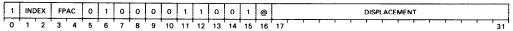

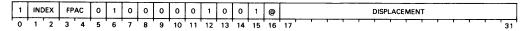

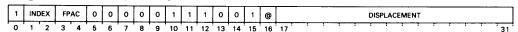

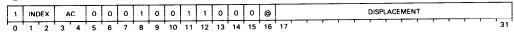

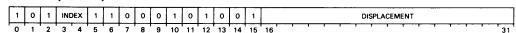

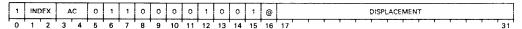

The processor accesses the stack management registers to save or restore them when changing program flow between segments. Figure 1.4 shows the format of the registers.

Figure 1.4 Wide stack management register format

where

X Bit 0 is reserved for future use.

Segment Bits 1-3 specify the segment location of the stack.

Logical Bits 4-31 specify a logical address within the segment. Address

Address wraparound can occur within the current segment.

#### **Program Flow Management**

Program flow management consists of controlling the program execution (such as calling a subroutine) and handling faults. The Program Flow Management section summarizes program control. Refer to the Program Flow Management chapter for additional information.

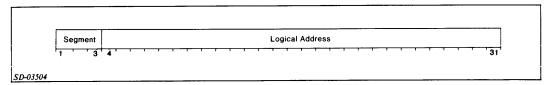

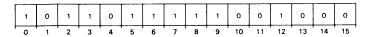

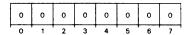

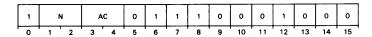

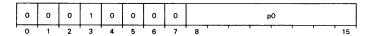

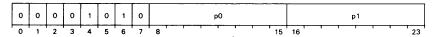

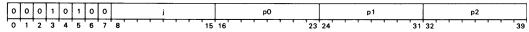

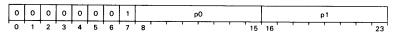

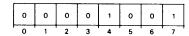

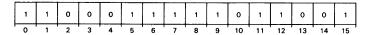

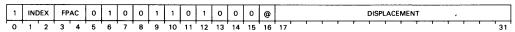

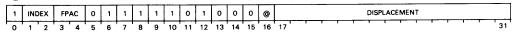

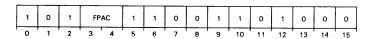

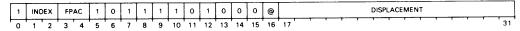

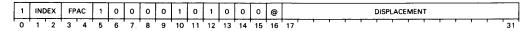

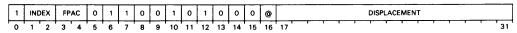

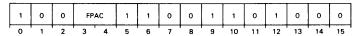

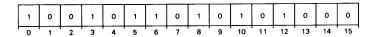

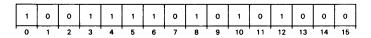

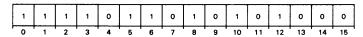

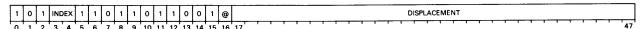

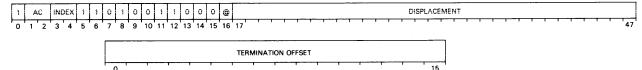

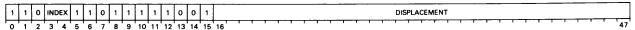

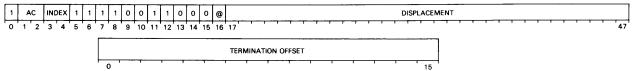

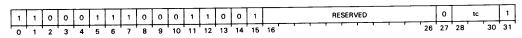

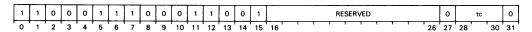

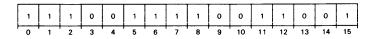

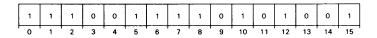

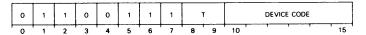

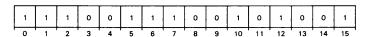

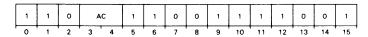

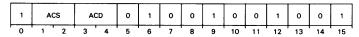

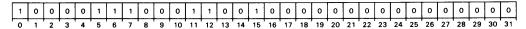

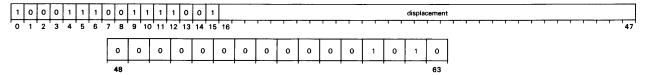

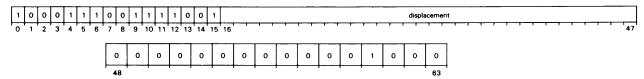

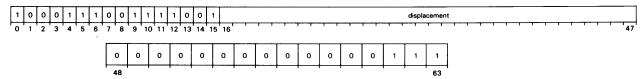

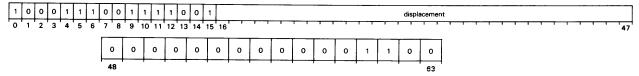

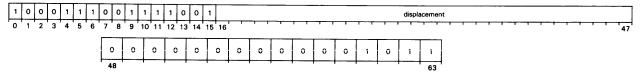

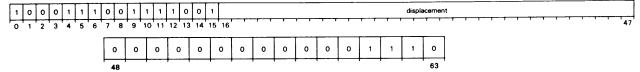

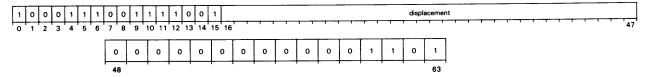

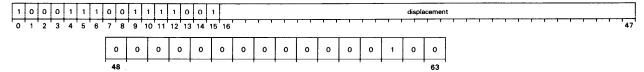

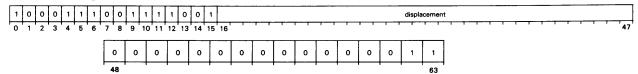

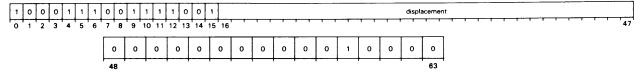

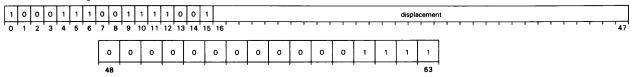

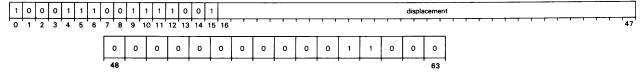

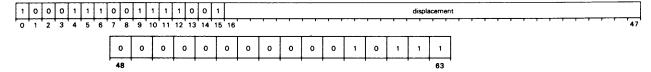

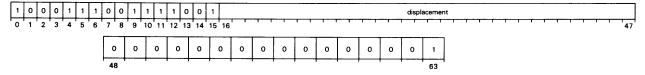

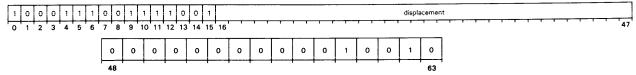

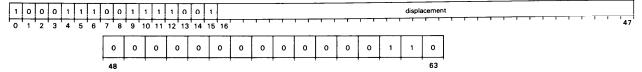

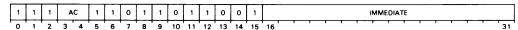

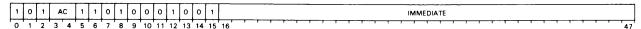

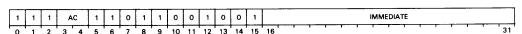

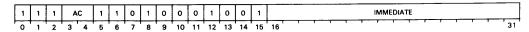

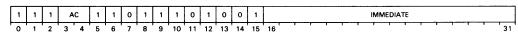

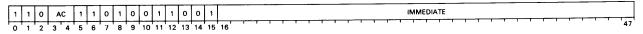

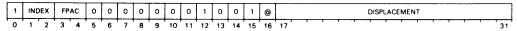

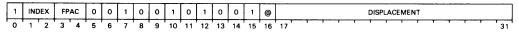

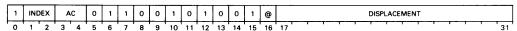

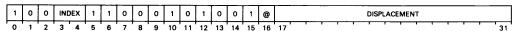

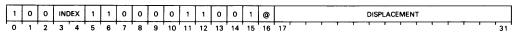

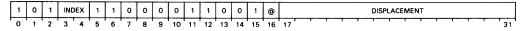

The processor controls program flow with a 31-bit program counter (PC). Figure 1.5 shows the format of the program counter.

Figure 1.5 Program counter format

where

Segment Bits 1-3 specify the current segment.

The processor provides specific procedures when modifying the current

segment field.

Logical Address Bits 4-31 specify a logical address within the segment.

During normal program flow, the processor increments bits 4-31 of the program counter. Thus, address wraparound occurs within the current segment.

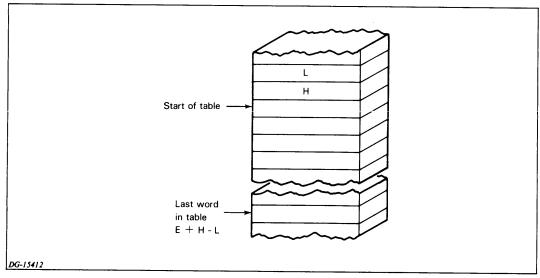

#### Queue Management

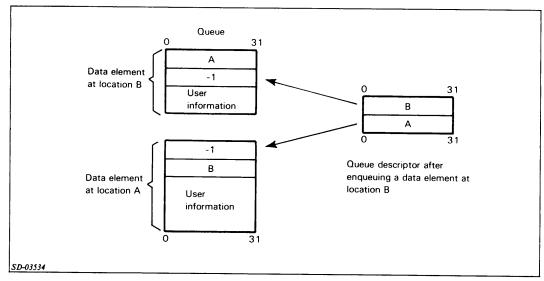

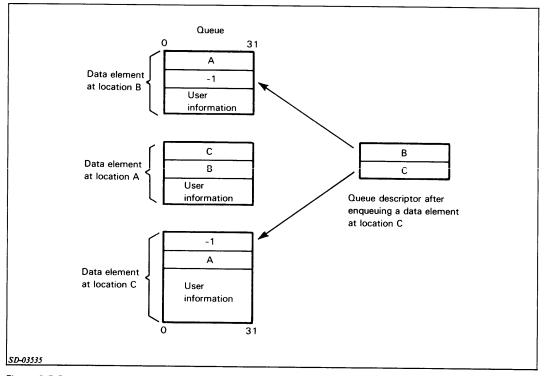

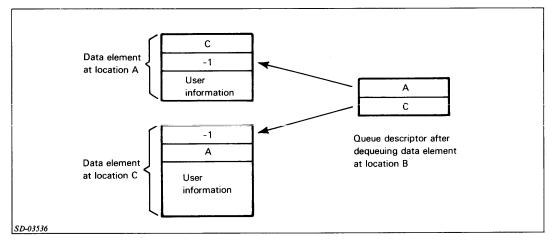

Queue management consists of inserting, deleting, and searching for elements in a queue. A queue is a variable-length list of linked entries. Typically, an operating system uses queues to keep track of processes that it must run, such as printing files on a line printer.

Refer to the Queue Management chapter for further information on the queue facilities and management.

#### **Device Management**

Device management entails transferring data between memory and a device. The processor can transfer data (bytes, words, or blocks of words) with the programmed I/O, the data channel I/O (DCH), or the high speed burst multiplexor channel (BMC). The Device Management section summarizes the three transfer facilities.

Common to the three transfer facilities are the I/O instructions, mapped or unmapped memory addressing, and the interrupt system. Refer to the Device Management chapter for additional information on using the I/O instructions and the interrupt system.

#### Programmed I/O

With the programmed I/O facility, you transfer bytes or words between an accumulator and a device. You can use the programmed I/O facility to transfer data with a slow speed device, or to initialize a data channel or a burst multiplexor channel.

#### Data Channel I/O

With the data channel I/O, you initiate a transfer of words between memory and a device. The data channel accesses memory directly (with or without a device map). Thus, the data transfer bypasses the accumulators.

#### **High Speed Burst Multiplexor Channel**

With the burst multiplexor channel, you initiate a transfer of blocks of words between memory and a device. The burst multiplexor channel accesses memory directly (with or without a device map). Thus, the data transfer bypasses the accumulators.

#### System Management

System management provides facilities that determine processor dependent configurations, such as the processor identification and the size of the main memory.

Refer to the Memory and System Management chapter for additional information.

#### **Memory Management**

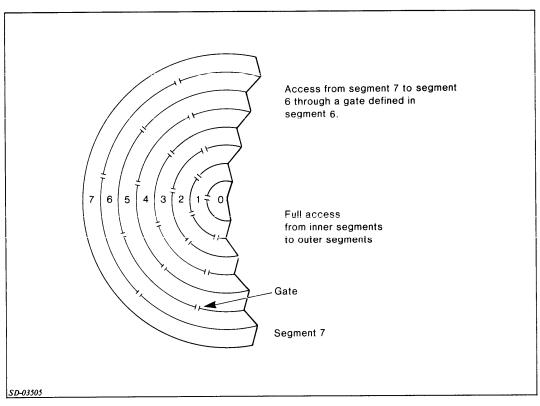

The processor uses a *virtual memory* of 4 Gbytes. Virtual memory consists of eight segments and rings, which facilitate memory management. A *segment* is an addressable unit of memory that contains programs and data. A *ring* is a collection of protection mechanisms, which safeguards the contents of a segment.

Since rings and segments are similar and inter-related, the manual uses the term segment to indicate either term or both terms. For instance, the manual refers to crossing segments; although gaining access to another segment also requires a ring crossing.

The processor addresses a segment through a 0-7 numbering system. Each segment contains 512 Mbytes. Figure 1.6 illustrates the concept of the segments, the contents of which are:

#### Segment 0

The processor executes privileged and nonprivileged instructions as the kernel operating system.

#### • Segments 1-7

The processor executes nonprivileged instructions in segments 1-7. Refer to the appropriate operating system programmer's manual for the implementation-dependent usage of the segments.

Memory management entails allocating the virtual memory to various software functions, and then defining the memory access restrictions. The processor imposes a few restrictions when allocating the virtual memory, such as executing the kernel of an operating system in segment 0, and executing the system calls in or below the segment where you call them. Refer to the Accessing Memory section for more information on the memory access restrictions.

Figure 1.6 Virtual address space

Since the logical address space is larger than physical memory,

- The processor translates a logical address to a physical address.

- A logical address specifies a segment number and a logical location within the segment. You write programs using these logical addresses. The processor converts them to physical addresses, and then accesses the contents.

- The operating system stores portions of the virtual memory (pages of 2 Kbytes) on a disk.

The hardware facilities for address translation include eight memory management registers (SBR0-SBR7), which define eight memory segments and the access protocols. The processor performs an address translation as explained in the Accessing Memory section.

With a privileged instruction, you can access a memory management register to load or to store the contents of a register. Refer to the Memory and System Management chapter for additional information.

#### ECLIPSE C/350 Compatible Instructions

The processor contains an ECLIPSE C/350 compatible instruction set (and stack facilities) for 16-bit program development and upward program compatibility. Refer to the C/350 Programming chapter for additional information.

## **Accessing Memory**

The processor addresses and accesses memory for an instruction or for an operand. To address memory, the processor uses a word as the standard unit of address. For instance, when loading a byte into an accumulator, the processor first resolves a word address, and then selects one of the two bytes.

The instruction that the processor accesses can be a word or a multiple of words. The operand can be a bit, byte, word, double word, or multiple of double words. You specify the address of the instruction or of the data with a memory reference instruction.

A memory reference instruction refers to a class of instructions that accesses memory for data or for another instruction. The memory reference instruction contains the information for

- Determining the effective address of an operand.

- The processor reads or writes an operand.

- Determining the effective address of the next nonsequential instruction.

The processor modifies the program counter with the effective address, and then executes the instruction that the program counter identifies.

A memory reference instruction attempts to access memory in the current segment or in another segment. The validity of the access depends on a comparison of the access protocols permitted for the memory page and the type of access that the instruction attempts to perform. The access protocols are explained in the Current Segment and the Other Segments sections.

### **Current Segment**

When a memory reference instruction addresses the current segment, the processor compares the page protocols with the type of access that the instruction requests, determining the validity of the reference. The *page protocols* are identified as a valid page, read access, write access, and execute access.

For instance, when loading a byte into an accumulator from the current segment, the processor reads the byte from memory if it resides where the page protocols permit a read access.

The processor also compares the segment field of every indirect address reference with the current segment. For accessing data (read or write access), indirect addressing can occur within the current segment or towards a higher numbered segment. For transferring program control (execute access), indirect addressing must occur in the current segment.

The processor aborts the access and services the protection violation fault for an invalid reference. Refer to the Memory and System Management chapter for further details on page accesses and the Program Flow Management chapter for more information on protection violation faults.

#### **Other Segments**

When executing a memory reference instruction that addresses another segment,

• The processor compares the current segment with the destination segment to determine the direction validity of the reference. The *destination segment* is the segment containing the operand or nonsequential instruction.

A read or write access must be to the current or to a higher numbered segment. An execute access must be to the current or to a lower numbered segment.

• The processor compares the segment and page protocols with the type of access that the instruction requests to determine the access validity of the reference. The processor first checks the segment protocols, and then checks the page protocols.

For a read or write access to a higher numbered segment, the segment protocol is a check for a valid segment. For an execute access to a lower numbered segment, the segment protocols are a check for a valid segment and gate. Refer to the Program Flow Management chapter for an explanation of a gate.

For instance, when loading a byte into an accumulator from a higher numbered segment, the processor reads the byte if it resides in a valid segment and page protocols permit a read access.

The processor aborts the access and services the protection violation fault for an invalid reference. Refer to the Memory and System Management chapter for further details on page accesses and the Program Flow Management chapter for more information on protection violation faults.

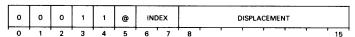

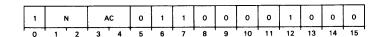

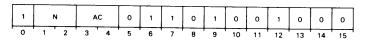

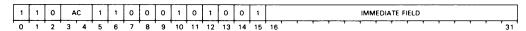

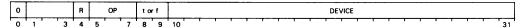

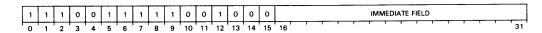

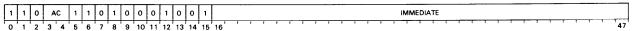

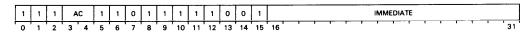

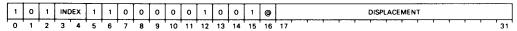

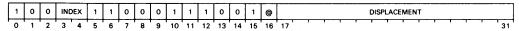

## **Memory Reference Instructions**

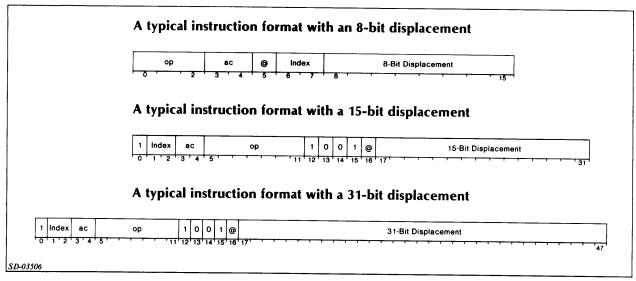

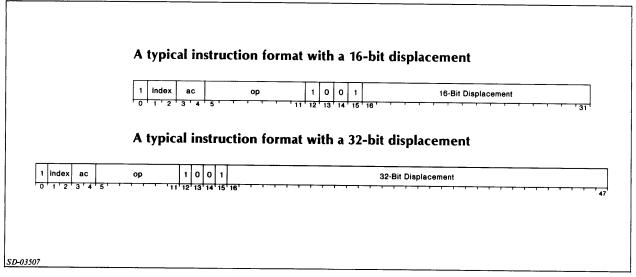

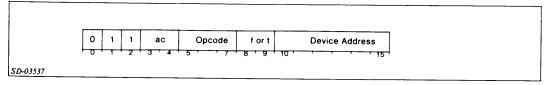

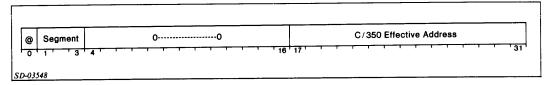

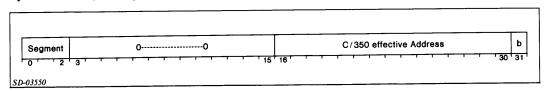

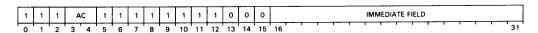

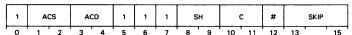

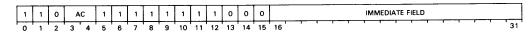

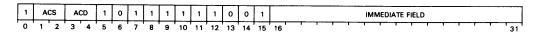

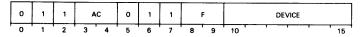

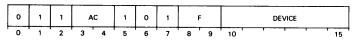

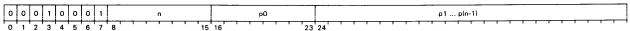

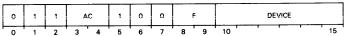

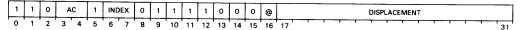

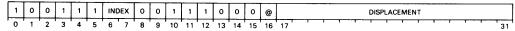

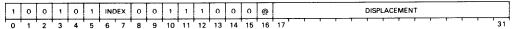

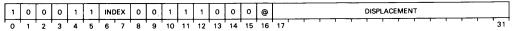

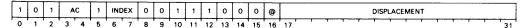

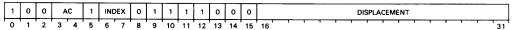

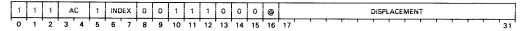

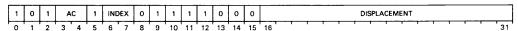

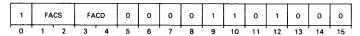

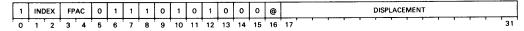

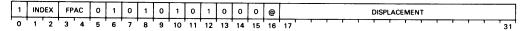

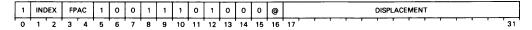

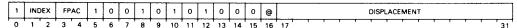

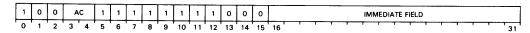

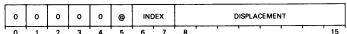

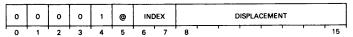

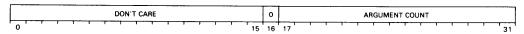

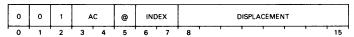

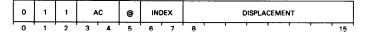

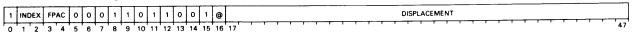

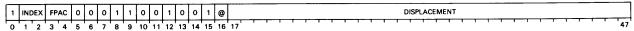

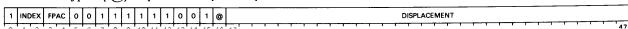

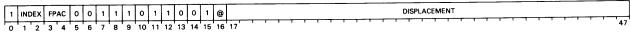

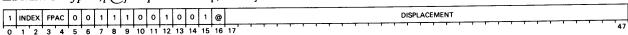

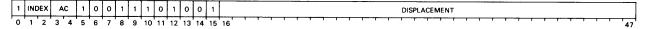

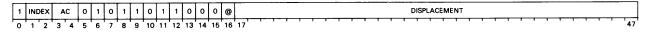

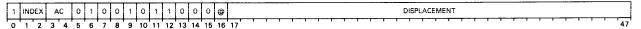

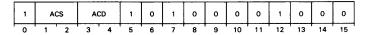

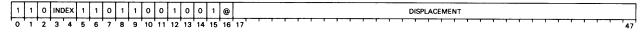

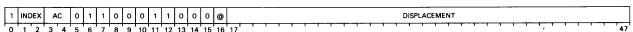

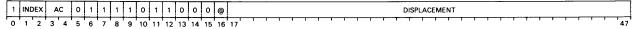

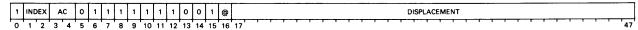

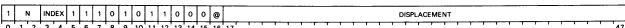

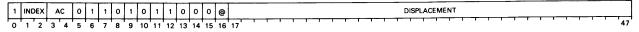

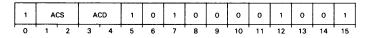

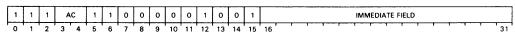

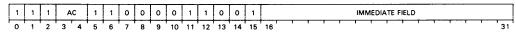

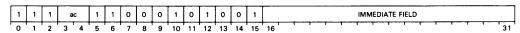

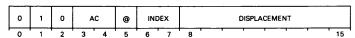

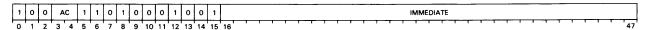

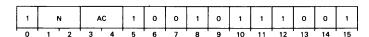

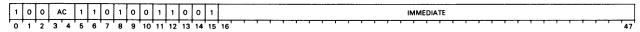

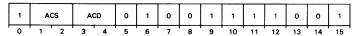

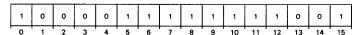

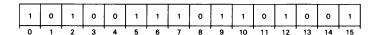

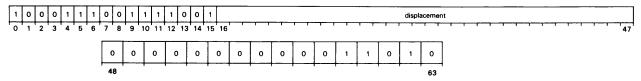

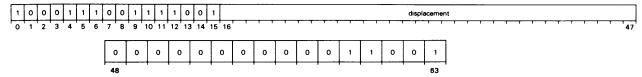

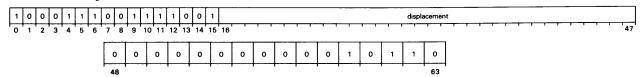

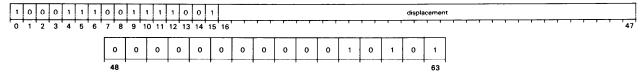

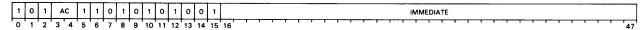

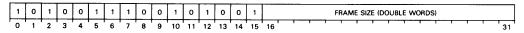

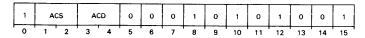

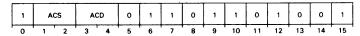

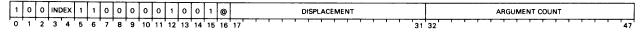

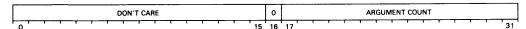

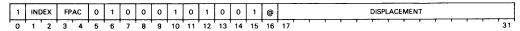

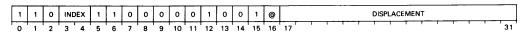

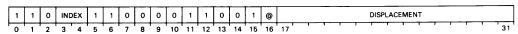

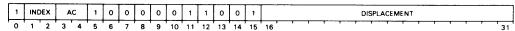

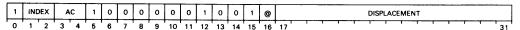

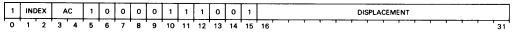

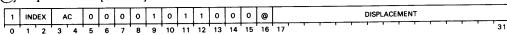

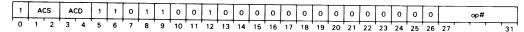

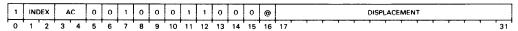

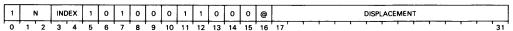

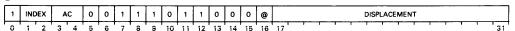

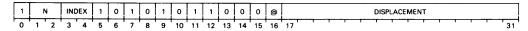

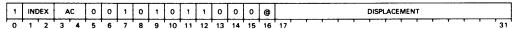

Figure 1.7 shows the typical memory reference instruction formats for word addressing. Figure 1.8 shows the typical memory reference instruction formats for byte addressing. The instruction formats for word addressing contain an indirect (@) field. The instruction formats for word and byte addressing contain index and displacement fields, and also an optional accumulator (ac) field. The optional accumulator field specifies a source or destination accumulator in the range of zero to three.

For instance, with the ac field equal to zero (ac = 0) for a load accumulator instruction, the processor loads an operand from memory into the destination accumulator (AC0 or FPAC0).

**NOTE:** With the ac field, a fixed-point instruction specifies a fixed-point accumulator; a floating-point instruction specifies a floating-point accumulator.

The combination of the index, displacement, and indirect (@) fields specify the effective address that contains the instruction or operand. To resolve the effective address, the processor first identifies the addressing mode, then any indirect address(es), and finally the effective address.

Figure 1.7 Memory reference instruction word addressing formats

Figure 1.8 Memory reference instruction byte addressing formats

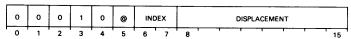

#### **Address Modes**

Using the index field (see Table 1.1), the processor determines if the instruction specifies an absolute or relative addressing mode. The Assembler (in conjunction with the appropriate pseudo-op) produces object code with absolute or relative addressing.

#### **Absolute Addressing**

For absolute addressing, the displacement field contains an indirect or an effective address. The address, expressed as an unsigned integer (8, 15, or 31 bits wide), specifies an addressing range as shown in Table 1.1.

With a few exceptions (LDA, LDB, LDI, LDIX, LEF, LSN, and XOP0), an assembler mnemonic of a memory reference instruction indicates the size and the range of the displacement. For instance, a memory reference instruction

- Without the X or L prefix, uses a standard displacement of 8 bits.

- With the X prefix, uses an extended displacement of 15 bits.

- With the L prefix, uses a long displacement of 31 bits.

**NOTE:** When using an 8- or 15-bit displacement, the processor zero extends the displacement to 28 bits.

Thus, the displacement becomes an indirect or an effective absolute address.

#### **Relative Addressing**

For relative addressing, the index field defines a register (see Table 1.1) the contents of which becomes a base address. The processor adds the base address to the displacement (8-, 15-, or 31-bit, two's complement integer). When using an 8- or 15-bit displacement, the processor sign extends the displacement to 31 bits.

In addition, if executing an instruction with an extended (15-bit) or long (31-bit) displacement, the processor adds a constant to the sum for program relative addressing. The additional increment adjusts the sum to address the first word of the displacement, which begins following the word that contains the instruction opcode. An instruction with an 8-bit displacement contains the displacement in the same word as the opcode.

Thus, the address becomes an indirect or effective relative address.

#### **Indirect and Effective Addresses**

When the indirect field equals zero, the absolute or relative address becomes the effective address. The processor translates an effective address to a physical address, and accesses the physical address.

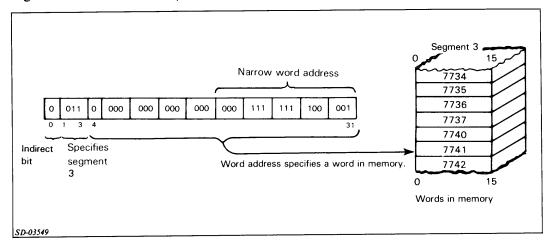

When the indirect field equals one, the absolute or relative address becomes an indirect address (or pointer). The processor translates the indirect address to a physical address and uses the contents of that physical address as another indirect or direct address.

**NOTE:** For a C/350 compatible instruction, the processor accesses a single word in memory as an indirect pointer; otherwise, the processor accesses a double word.

The processor tests bit 0 of the pointer contents, which defines additional (if any) indirect addressing.

- When bit 0 equals zero, the contents become the effective address.

The processor translates the effective address to a physical address and accesses it.

- When bit 0 equals one, the contents become another pointer.

The processor continues to resolve pointers until bit 0 equals zero.

The processor can resolve up to 15<sub>10</sub> pointers. However, for an instruction that can specify two indirect-addressing chains (such as WBLM), the total number of pointers for the two chains must be equal to or less than 15.

**NOTE:** If the processor attempts to resolve more than 15 indirect addresses, a protection violation occurs.

|                 |       |                                     | Displacement Range |                                                                       |

|-----------------|-------|-------------------------------------|--------------------|-----------------------------------------------------------------------|

| Address<br>Mode | Index | Intermediate<br>Logical<br>Address* | Prefix**           | Octal Words (decimal)                                                 |

| Absolute        | 00    | D                                   |                    | 0 to 377<br>(0 to 255)                                                |

|                 |       | D                                   | x                  | 0 to 077777<br>(0 to 32,767)                                          |

|                 |       | D                                   | ·L                 | 0 to 1777777777<br>(0 to 2,147,483,647)                               |

| PC Relative     | 01    | PC±D                                |                    | - 200 to + 177<br>(- 128 to + 127)                                    |

|                 |       | PC+n±D                              | x                  | - 40000 to + 37777<br>(- 16,384 to + 16,383)                          |

|                 |       | PC+n±D                              | L                  | - 10000000000 to + 0777777777<br>(- 1,073,741,824 to + 1,073,741,823) |

| AC2 Relative    | 10    | AC2±D                               |                    | - 200 to + 177<br>(- 128 to + 127)                                    |

|                 |       | AC2 ± D                             | x                  | - 40000 to + 37777<br>(- 16,384 to + 16,383)                          |

|                 |       | AC2±D                               | L                  | - 10000000000 to + 0777777777<br>(- 1,073,741,824 to + 1,073,741,823) |

| AC3 Relative    | 11    | AC3±D                               |                    | - 200 to + 177<br>(- 128 to + 127)                                    |

|                 |       | AC3±D                               | ×                  | - 40000 to + 37777<br>(- 16,384 to + 16,383)                          |

|                 |       | AC3±D                               | L                  | - 10000000000 to + 0777777777<br>(- 1,073,741,824 to + 1,073,741,823) |

Table 1.1 Effective addressing

The *n* variable in the PC relative addressing mode equals the number of words that precede the first word of the displacement, for the current instruction.

#### **Operand Access**

Before accessing a memory operand (for fixed- or floating-point computation), the processor first resolves an effective address.

The processor accesses an operand as a bit, byte, several bytes, word, double word, or several double words. The following sections explain the word, byte, and bit accesses. (For the processor to access several bytes, it must first access a byte; to access several words or double words, it must first access a word.)

<sup>\*</sup>The processor ignores bit 0 of PC, AC2, and AC3 when calculating the intermediate logical address.

<sup>\*\*</sup>The X or L corresponds to the prefix of an instruction mnemonic, which identifies the instruction as containing an extended (X) or long (L) displacement field.

#### Word

The processor accesses a word operand for fixed-point computation. A fixed-point instruction mnemonic with a prefix of N (such as NADD) indicates a narrow or one word operand.

An instruction that requests a word (such as NLDA) supplies the effective address parameters to the processor. The processor then resolves the effective address.

#### **Double Word**

The processor accesses a double word operand for fixed-point or floating-point computation. A fixed-point instruction mnemonic with a prefix of W (such as WADD) indicates a wide or two word operand. A single precision floating-point instruction requires one double word, while a double precision instruction requires two double words.

An instruction that requests a double word (such as WLDA) supplies the effective address parameters to the processor. The processor then resolves the effective address, which points to the first word of the double word operand.

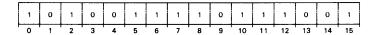

#### **Byte**

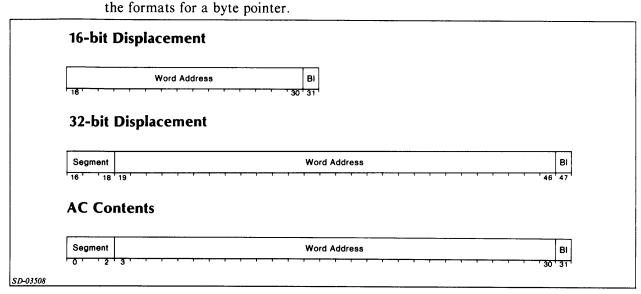

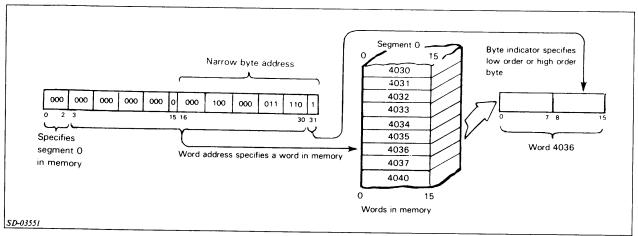

An instruction which requests a byte forms a byte pointer from the contents of an accumulator or from the contents of the index field and the 16- or 32-bit displacement. A byte pointer consists of an effective address and a byte indicator. The least significant bit of the byte pointer contains the byte indicator.

NOTE: Byte addressing excludes indirect addressing.

The processor identifies a byte as follows

#### 16-Bit displacement

For an instruction with a 16-bit displacement (such as XLDB), the processor extends the displacement to 29 bits (absolute addressing) or 32 bits (relative addressing), calculates the effective address, and then identifies the byte.

#### 32-Bit displacement

For an instruction with a 32-bit displacement (such as LLDB), the processor calculates the effective address, and then identifies the byte.

#### Accumulator

For an instruction that requires a byte pointer in an accumulator, you must first use a load effective byte address instruction (such as LLEFB). The load effective byte address instruction calculates an effective byte address, and then loads it into an accumulator.

Figure 1.9 Byte pointer format

where

Segment The segment field identifies the current or an outward memory segment.

Word The word address field identifies a 16-bit word in the memory segment.

Address

BI The BI field identifies the byte.

When BI field equals zero, the processor accesses the most significant byte (bits 0-7).

When BI field equals one, the processor accesses the least significant byte (bits 8-15).

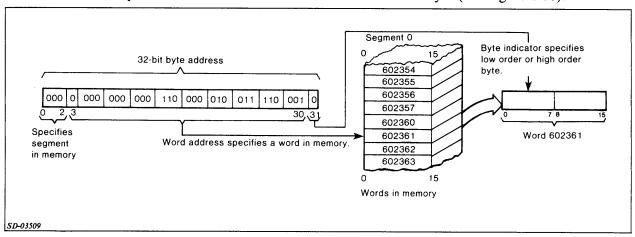

The processor accesses the word and then locates the byte (see Figure 1.10).

Figure 1.10 Byte addressing

#### Bit

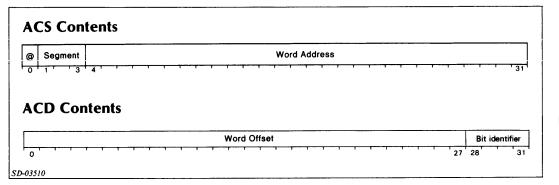

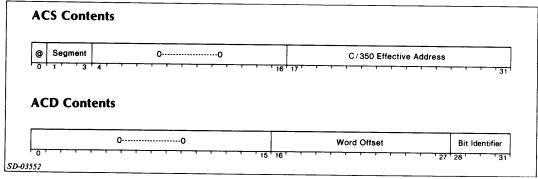

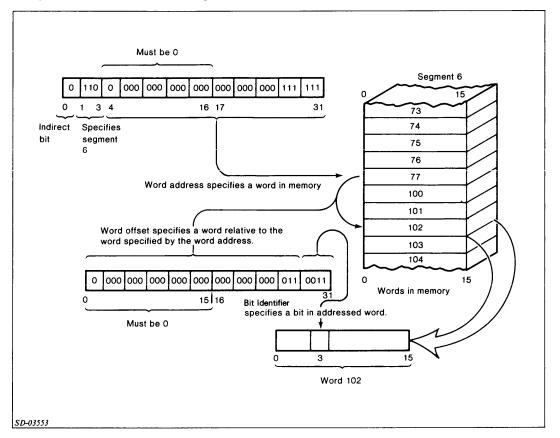

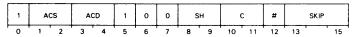

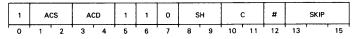

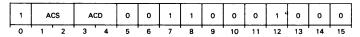

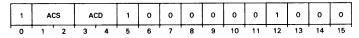

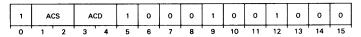

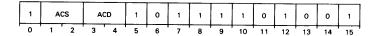

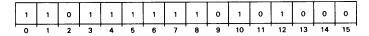

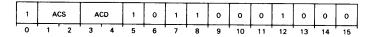

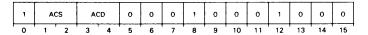

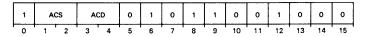

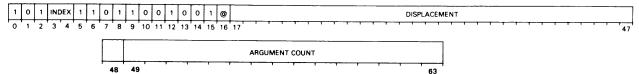

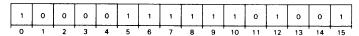

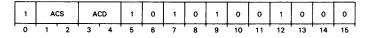

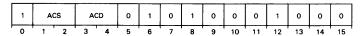

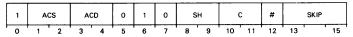

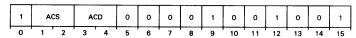

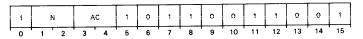

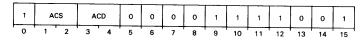

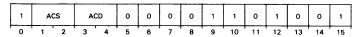

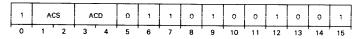

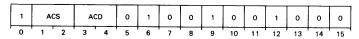

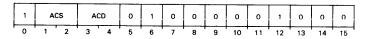

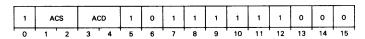

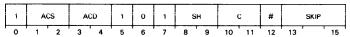

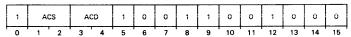

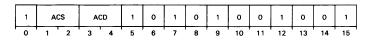

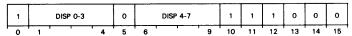

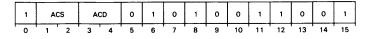

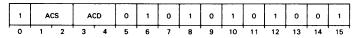

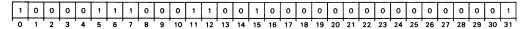

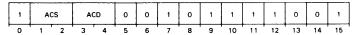

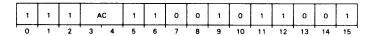

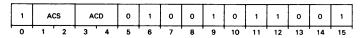

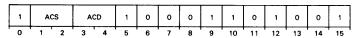

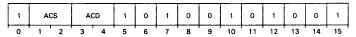

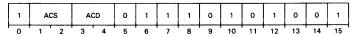

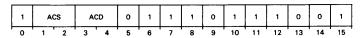

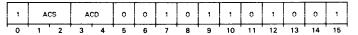

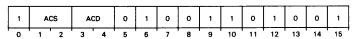

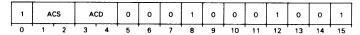

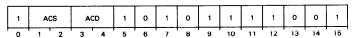

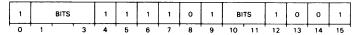

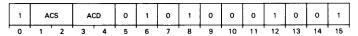

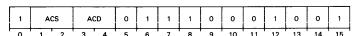

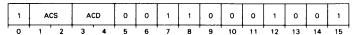

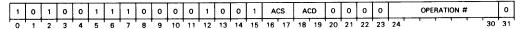

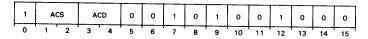

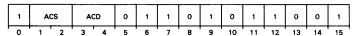

An instruction that accesses a bit in memory (such as WBTO, WBTZ, WSNB, WSZB, and WSZBO) forms a bit pointer from the contents of two accumulators. The bit pointer is composed of a word pointer and a bit identifier. The word pointer consists of an effective address (in the ACS accumulator) and a word offset (in the ACD accumulator). The bit identifier is located in the least significant bits of the ACD accumulator.

Figure 1.11 shows the accumulator formats for the WBTO, WBTZ, WSNB, WSZB, and WSZBO instructions.

Figure 1.11 Bit pointer format

where

| @                 | When the @ field equals one, it identifies an indirect address.                                                                               |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

|                   | When the @ field equals zero, it identifies a direct address.                                                                                 |

| Segment           | The segment field identifies the current or an outward memory segment.                                                                        |

| Word<br>Address   | The word address field identifies a 32-bit word in the memory segment.                                                                        |

| Word<br>Offset    | The processor adds the word offset bits, an unsigned integer, to the effective address and arrives at a final word address (see Figure 1.12). |

| Bit<br>Identifier | The bit identifier field specifies the bit position (0-15) in the final word.                                                                 |

Figure 1.12 Bit addressing

The processor uses the ACS accumulator contents to calculate an effective address. If a bit instruction specifies the two accumulators as the same accumulator, then the effective address is zero in the current segment.

# **Protection Capabilities**

While executing an instruction, the processor checks for the validity of a memory reference or an I/O operation (protection violation), a page reference (nonresident page), a stack operation, a computation, and a data format. Table 1.2 lists the validity checks (or faults).

| Fault                                                                                                    | Туре                                                          |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| Nonresident page Protection violation Stack operation Fixed-point computation Floating-point computation | Privileged<br>Nonprivileged<br>Nonprivileged<br>Nonprivileged |

| Invalid decimal or ASCII data format                                                                     | Nonprivileged<br>Nonprivileged                                |

Table 1.2 Faults

If the processor detects an error, a nonprivileged or privileged fault occurs before executing the next instruction. A nonprivileged fault occurs when the processor detects a computation error. The processor limits the I/O and memory access using a hierarchical protection mechanism. For instance

- Before executing an I/O instruction, the processor checks the I/O validity flag in the current segment.

- Before executing a memory reference instruction, the processor checks the validity of the reference.

The processor executes an I/O or memory reference instruction when validity checks permit the access. Otherwise, the processor initiates a protection violation. Thus, an operating system can restrict access to the devices to specific segment(s).

Accessing and changing a protection mechanism requires a privilege instruction or data access, typically controlled by the operating system. Refer to the Program Flow Management chapter for further details on servicing a nonprivileged fault.

A privileged fault occurs when the processor detects a page fault, such as a nonresident memory page reference. Refer to the Memory and System Management chapter for further details on servicing a privileged fault.

# **Summary**

The remainder of the *Principles of Operation 32-Bit ECLIPSE® Systems* manual explains the computation and management facilities. Chapters 2 through 9 present the facilities in a functional framework. Chapter 10 presents the instructions in alphabetical order, and the appendixes present C/350 anomalies and fault codes.

# Chapter 2 Fixed-Point Computing

#### Overview

With fixed-point computations, the processor can add, subtract, multiply, and divide 16-and 32-bit signed (two's complement) and unsigned binary data. The processor also performs logical operations on 16- and 32-bit data.

In addition to the binary arithmetical and logical operations, the processor can manipulate 8-bit bytes (as alphanumeric ASCII data) and can perform binary coded decimal (BCD) arithmetic. The processor performs the byte manipulation with the fixed-point operations. The processor performs the BCD arithmetic with the fixed- and floating-point operations.

Following a computation, the processor can shift (arithmetically or logically) the contents of an accumulator, and can skip on a condition (the result of the computation and/or shift). Finally, the processor can store the result in an accumulator or memory.

The Fixed-Point Computing chapter explains the various computations (binary, logical, and decimal and byte) and the processor status register.

# **Binary Operation**

The processor performs fixed-point binary arithmetic in the arithmetic logic unit. You control the processor and arithmetic logic unit operations with the move, arithmetic, shift, and skip instructions.

#### **Data Formats**

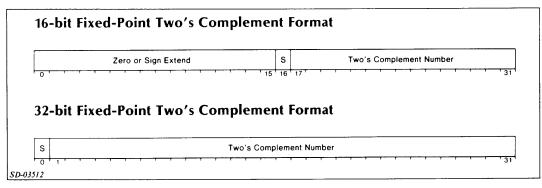

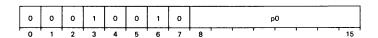

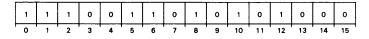

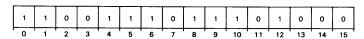

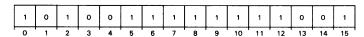

The fixed-point arithmetic instructions require two's complement binary numbers. For instance, the ADD instruction adds two 16-bit two's complement binary numbers. The 16- and 32-bit numbers must begin on word boundaries. Figure 2.1 shows the fixed-point accumulator formats for the 16- and 32-bit two's complement numbers.

Figure 2.1 Fixed-point two's complement data formats

where

Zero or Sign Extend The zero or sign extend bits contain 16 zeros or 16 ones.

For moving and computing narrow data, the processor sign extends narrow data when loading it into an accumulator. The processor sign extends narrow data before or after narrow data operations, when converting it to wide data.

S The S bit equals the sign bit.

Bit 16 contains the sign bit for narrow data; bit 0 contains the sign bit for wide data. The sign bit equals zero for a positive number, and equals one for a negative number.

Two's Complement Number The processor requires two's complement binary numbers for fixed-point arithmetic computation. Table 2.1 shows the precision of 16-and 32-bit two's complement binary numbers.

| Form of Data | 16-bit Precision | 32-bit Precision   |

|--------------|------------------|--------------------|

| Unsigned     | O to 65,535      | 0 to 4,294,967,295 |

| Signed       | -32,768 to       | -2,147,483,648 to  |

|              | +32,767          | +2,147,483,647     |

Table 2.1 Range of 16- and 32-bit two's complement numbers

Table 2.2 lists the instructions that explicitly convert 16-bit data to or from 32-bit data. Other sections list the instructions that convert the precision before or after another function. For instance, when loading narrow data (16-bit) from memory into an accumulator, the processor sign extends the number before loading it. When executing a narrow fixed-point instruction (NADD), the arithmetic logic unit sign extends the result.

| Instruction | Operation                      |

|-------------|--------------------------------|

| CVWN        | Convert from 32-bit to 16-bit  |

| SEX         | Sign extend 16-bits to 32-bits |

| ZEX         | Zero extend 16-bits to 32-bits |

Table 2.2 Fixed-point precision conversion

#### **Move Instructions**

Table 2.3 lists the load and store accumulator instructions.

The wide block move instruction (WBLM) requires an effective address in an accumulator. Use a load effective address instruction (LLEF or XLEF) to calculate and to load the effective address into an accumulator.

| Instruction | Operation                                           |  |

|-------------|-----------------------------------------------------|--|

| LDATS       | Load accumulator with double word addressed by WSP  |  |

| LNLDA       | Narrow load accumulator                             |  |

| LNSTA       | Narrow store accumulator                            |  |

| LWLDA       | Wide load accumulator                               |  |

| LWSTA       | Wide store accumulator                              |  |

| MOV *       | Move and skip                                       |  |

| NLDAI       | Narrow load immediate                               |  |

| STATS       | Store accumulator into double word addressed by WSP |  |

| WBLM        | Wide block move                                     |  |

| WLDAI       | Wide load with wide immediate                       |  |

| WMOV        | Wide move                                           |  |

| WPOP        | Wide pop accumulators                               |  |

| WPSH        | Wide push accumulators                              |  |

| WXCH        | Wide exchange accumulators                          |  |

| XCH *       | Exchange accumulators                               |  |

| XNLDA       | Narrow load accumulator                             |  |

| XNSTA       | Narrow store accumulator                            |  |

| XWLDA       | Wide load accumulator                               |  |

| XWSTA       | Wide store accumulator                              |  |

Table 2.3 Fixed-point data movement instructions

#### **Arithmetic Instructions**

Tables 2.4 through 2.7 list the arithmetic instructions.

The ECLIPSE C/350 compatible instructions (such as, ADC, ADD, MUL, and DIVS) ignore bits 0-15 of the source accumulator. The results of C/350 compatible instructions generally leave bits 0-15 of the destination accumulator undefined, except where noted otherwise.

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Operation                             |  |

|-------------|---------------------------------------|--|

| ADC *       | Add complement and skip               |  |

| ADD *       | Add and skip                          |  |

| ADDI *      | Extended add immediate                |  |

| ADI *       | Add immediate                         |  |

| INC *       | Increment and skip                    |  |

| LNADD       | Narrow add memory word to accumulator |  |

| LNADI       | Narrow add immediate                  |  |

| LWADD       | Wide add memory word to accumulator   |  |

| LWADI       | Wide add immediate                    |  |

| NADD        | Narrow add                            |  |

| NADDI       | Narrow extended add immediate         |  |

| NADI        | Narrow add immediate                  |  |

| WADC        | Wide add complement                   |  |

| WADD        | Wide add                              |  |

| WADDI       | Wide add with wide immediate          |  |

| WADI        | Wide add immediate                    |  |

| WINC        | Wide increment (no skip)              |  |

| WNADI       | Wide add with narrow immediate        |  |

| XNADD       | Narrow add accumulator to memory word |  |

| XNADI       | Narrow add immediate                  |  |

| XWADD       | Wide add memory word to accumulator   |  |

| XWADI       | Wide add immediate                    |  |

Table 2.4 Fixed-point addition instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Operation                   |

|-------------|-----------------------------|

| LNSBI       | Narrow subtract immediate   |

| LNSUB       | Narrow subtract memory word |

| LWSBI       | Wide subtract immediate     |

| LWSUB       | Wide subtract memory word   |

| NSBI        | Narrow subtract immediate   |

| NSUB        | Narrow subtract             |

| SBI *       | Subtract immediate          |

| SUB *       | Subtract and skip           |

| WSBI        | Wide subtract immediate     |

| WSUB        | Wide subtract               |

| XNSBI       | Narrow subtract immediate   |

| XNSUB       | Narrow subtract memory word |

| XWSBI       | Wide subtract immediate     |

| XWSUB       | Wide subtract memory word   |

Table 2.5 Fixed-point subtraction instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction                               | Operation                                                                                                         |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| LNMUL<br>LWMUL<br>MUL *<br>MULS *<br>NMUL | Wide multiply memory word Wide multiply memory word Unsigned multiply Signed multiply Narrow sign extend multiply |

| WMUL<br>WMULS<br>XNMUL<br>XWMUL           | Wide multiply Wide signed multiply Narrow multiply memory word Wide multiply memory word                          |

Table 2.6 Fixed-point multiplication instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Operation                 |

|-------------|---------------------------|

| DIV *       | Unsigned divide           |

| DIVS *      | Signed divide             |

| DIVX *      | Sign extend and divide    |

| HLV *       | Halve (AC/2)              |

| LNDIV       | Narrow divide memory word |

| LWDIV       | Wide divide memory word   |

| NDIV        | Narrow sign extend divide |

| WDIV        | Wide divide               |

| WDIVS       | Wide signed divide        |

| WHLV        | Wide halve                |

| XNDIV       | Narrow divide memory word |

| XWDIV       | Wide divide memory word   |

Table 2.7 Fixed-point division instructions

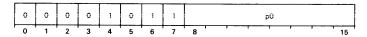

# **Carry Operations**

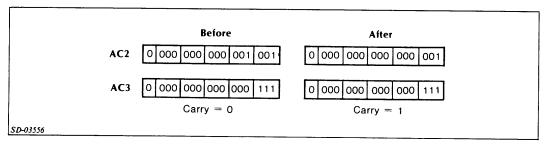

For fixed-point arithmetic operations, the processor maintains a carry flag (CARRY). The CARRY flag contains a value of zero or one. For instance, for an instruction that adds 16-bit data, the carry occurs from bit 16. For an instruction that adds 32-bit data, the carry occurs from bit 0.

You can initialize the value of the CARRY flag before a binary operation by executing an explicit carry instruction. Table 2.8 lists the instructions that initialize the CARRY flag. The processor retains the value of the CARRY flag for use with another instruction.

<sup>\*</sup>ECLIPSE C/350 compatible instruction

The processor changes the value of the CARRY flag as a result of executing an ECLIPSE MV/Family arithmetic instruction or an ECLIPSE C/350-compatible fixed-point instruction. For an ECLIPSE MV/Family arithmetic instruction, the processor loads the result of carry into the CARRY flag; it is not relative to its former value (as it is with an ECLIPSE C/350-compatible instruction). For an ECLIPSE C/350-compatible instruction, the processor complements the CARRY flag during

- addition when the two most significant bits (0 for unsigned and 1 for signed) and the CARRY flag produce a carry;

- subtraction when borrowing from the most significant bit.

With a C/350 compatible instruction, the processor initializes the CARRY flag, performs the binary operation on the data, and then modifies the CARRY flag (depending on the magnitude of the result).

| Instruction | Operation                                           |

|-------------|-----------------------------------------------------|

| ADC *       | Add complement with optional CARRY initialization   |

| ADD *       | Add with optional CARRY initialization              |

| AND *       | AND with optional CARRY initialization              |

| COM *       | One's complement with optional CARRY initialization |

| CRYTC       | Complement CARRY                                    |

| CRYTO       | Set CARRY to one                                    |

| CRYTZ       | Set CARRY to zero                                   |

| INC *       | Increment with optional CARRY initialization        |

| MOV *       | Move with optional CARRY initialization             |

| NEG *       | Negate with optional CARRY initialization           |

| SUB *       | Subtract with optional CARRY initialization         |

Table 2.8 Initializing carry instructions

#### **Shift Instructions**

The wide arithmetic shift instructions (WASH and WASHI) move 32 bits of an accumulator left or right (0 to 31 bit positions), depending on an 8-bit two's complement number. The 8 bits in the source accumulator for the WASH instruction or the 8 bits in the immediate displacement of the WASHI instruction contain the 8-bit number.

• With an 8-bit positive number, the processor shifts from 0 to 31 bit positions to the left, and zero extends the vacated bit positions. A fixed point overflow occurs if the sign bit changes.

**NOTE:** Shifting a negative number more than 31 bit positions to the left guarantees a fixed-point overflow.

- With an 8-bit number equal to zero, no shifting occurs.

- With an 8-bit negative number, the processor shifts from 0 to 31 bits to the right, and sign extends the vacated bit positions. The processor drops the bits shifted from the least significant bit position.

For instance, when the processor shifts +3 to the right one bit position, the result yields +1; shifting +1 to the right one bit position yields 0.

<sup>\*</sup>ECLIPSE C/350 compatible instruction

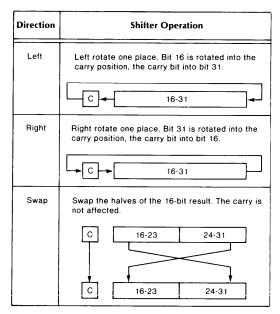

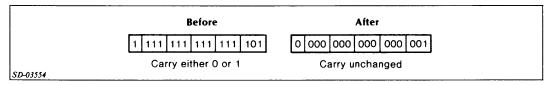

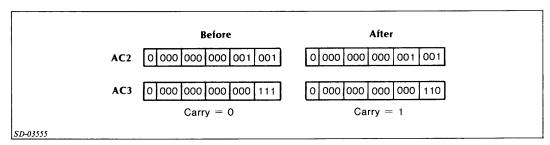

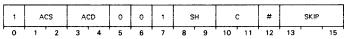

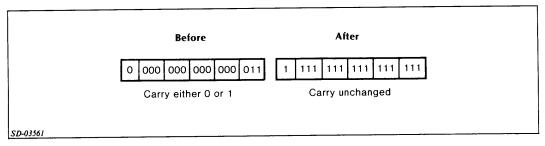

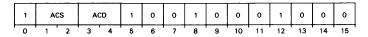

The ECLIPSE C/350 compatible arithmetic instructions (ADC, ADD, INC, MOV, and SUB) can shift an intermediate result one bit position or swap the two bytes (see Figure 2.2). The shift can be

• One bit to the left.

The CARRY flag assumes the state of the most significant bit, and the least significant bit assumes the state of the CARRY flag.

One bit to the right.

The CARRY flag assumes the state of the least significant bit, and the most significant bit assumes the state of the CARRY flag.

• A swap of the most significant byte with the least significant byte.

The processor preserves the state of the CARRY flag.

SD-03513

Figure 2.2 ECLIPSE C/350 compatible shift operations

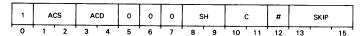

## **Skip Instructions**

With a skip instruction, the processor tests the result of an operation for a specific condition and directs the processor to skip the word or to execute the word after the skip instruction.

For an instruction that includes a skip option (such as ADD), the processor tests the result during its temporary storage. The processor can then save the result of the computation or ignore it. For an instruction that excludes a skip option (such as NADD), the processor stores the result in memory or an accumulator. You can then test the result with an explicit test and skip on condition instruction (such as skip on OVR reset -- SNOVR).

Tables 2.9 and 2.10 list the fixed-point skip on condition instructions. When a skip occurs, the processor increments the program counter by one and executes the second word after the skip instruction.

NOTE: Be sure that a skip does not transfer control to the middle of a 32-bit or longer instruction.

| Instruction | Operation                                                |

|-------------|----------------------------------------------------------|

| ADC *       | Add complement with optional skip                        |

| ADD *       | Add with optional skip                                   |

| INC *       | Increment with optional skip                             |

| MOV *       | Move with optional skip                                  |

| NSALA       | Narrow skip on all bits set in accumulator               |

| NSALM       | Narrow skip on all bits set in memory location           |

| NSANA       | Narrow skip on any bit set in accumulator                |

| NSANM       | Narrow skip on any bit set in memory location            |

| SGE *       | Skip if ACS greater than or equal to ACD                 |

| SGT *       | Skip if ACS greater than ACD                             |

| SNOVR       | Skip on OVR reset                                        |

| SUB *       | Subtract with optional skip                              |

| WCLM        | Wide compare to limits and skip                          |

| WSALA       | Wide skip on all bits set in accumulator                 |

| WSALM       | Wide skip on all bits set in double word memory location |

| WSANA       | Wide skip on any bit set in accumulator                  |

| WSANM       | Wide skip on any bit set in double word memory location  |

| WSEQ        | Wide skip if ACS equal to ACD                            |

| WSEQI       | Wide skip if equal to immediate                          |

| WSGE        | Wide signed skip if ACS greater than or equal to ACD     |

| WSGT        | Wide signed skip if ACS greater than ACD                 |

| WSGTI       | Wide skip if AC greater than immediate                   |

| WSKBO       | Wide skip on AC bit set to one                           |

| WSKBZ       | Wide skip on AC bit set to zero                          |

| WSLE        | Wide signed skip if ACS less than or equal to ACD        |

| WSLEI       | Wide skip if AC less than or equal to immediate          |

| WSLT        | Wide signed skip if ACS less than ACD                    |

| WSNB        | Wide skip on nonzero bit                                 |

| WSNE        | Wide skip if ACS not equal to ACD                        |

| WSNEI       | Wide skip if AC not equal to immediate                   |

| WSZB        | Wide skip on zero bit                                    |

| WSZBO       | Wide skip on zero bit and set bit to one                 |

| WUGTI       | Wide unsigned skip if AC greater than immediate          |

| WULEI       | Wide unsigned skip if AC less than or equal to immediate |

| WUSGE       | Wide unsigned skip if ACS greater than or equal to ACD   |

| WUSGT       | Wide unsigned skip if ACS greater than ACD               |

Table 2.9 Fixed-point skip on condition instructions

#### **Overflow Fault**

The processor checks for a fixed-point overflow when attempting division by zero or when calculating a two's complement number. An overflow occurs if the result is too large to store in memory or in a fixed-point accumulator. At the end of the current instruction cycle, the processor sets the overflow flag (OVR) to one. The processor status register contains the OVR flag. Refer to the Program Flow Management chapter for information on fault handling.

<sup>\*</sup>ECLIPSE C/350 compatible instruction

| Instruction | Operation                                                 |

|-------------|-----------------------------------------------------------|

| DSZTS       | Decrement the double word addressed by WSP (skip if zero) |

| INC *       | Increment and skip                                        |

| ISZTS       | Increment the double word addressed by WSP (skip if zero) |

| LNDSZ       | Narrow decrement and skip if zero                         |

| LNISZ       | Narrow increment and skip if zero                         |

| LWDSZ       | Wide decrement and skip if zero                           |

| LWISZ       | Wide increment and skip if zero                           |

| XNDSZ       | Narrow decrement and skip if zero                         |

| XNISZ       | Narrow increment and skip if zero                         |

| XWDSZ       | Wide decrement and skip if zero                           |

| XWISZ       | Wide increment and skip if zero                           |

Table 2.10 Fixed-point increment or decrement word and skip instructions

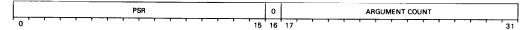

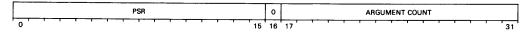

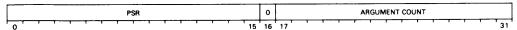

#### **Processor Status Register**

The processor contains a 16-bit processor status register (PSR), which retains information about the status of fixed-point computations. You access the register with instructions that test and set the register contents. Refer to the Skip section for a list of the instructions that test the register contents. Table 2.11 lists the instructions that set the register contents.

| Instruction | Operation                                               |

|-------------|---------------------------------------------------------|

| ВКРТ        | Breakpoint                                              |

| FXTD        | Disable fixed-point trap (resets OVK and disables trap) |

| FXTE        | Enable fixed-point trap (sets OVK and enables trap)     |

| LCALL       | Call subroutine                                         |

| LPSR        | Load PSR into ACO                                       |

| PBX         | Pop block and execute                                   |

| SPSR        | Store PSR from ACO                                      |

| WPOPB       | Wide pop block                                          |

| WRSTR       | Wide restore                                            |

| WDPOP       | Wide pop context block                                  |

| WRTN        | Wide return                                             |

| WSAVR       | Wide save and set OVK to zero                           |

| WSAVS       | Wide save and set OVK to one                            |

| WSSVR       | Wide special save and set OVK to zero                   |

| WSSVS       | Wide special save and set OVK to one                    |

| XCALL       | Call subroutine                                         |

| XVCT        | I/O vector interrupt                                    |

Table 2.11 PSR manipulation instructions

<sup>\*</sup>ECLIPSE C/350 compatible instruction

<sup>\*</sup>ECLIPSE C/350 compatible instruction

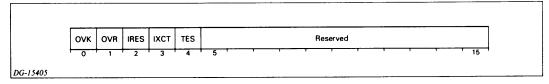

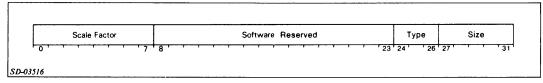

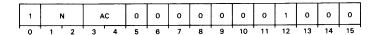

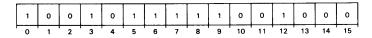

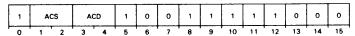

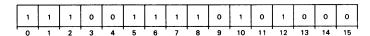

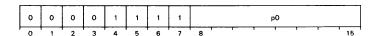

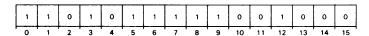

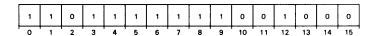

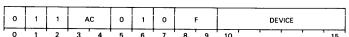

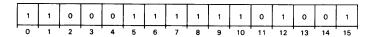

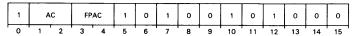

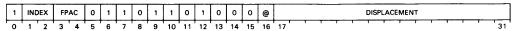

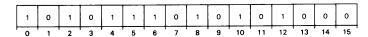

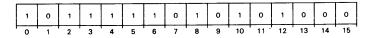

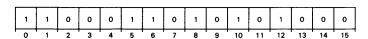

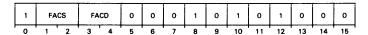

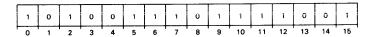

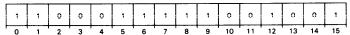

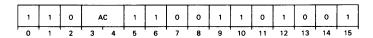

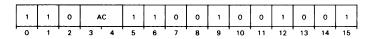

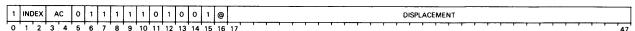

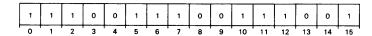

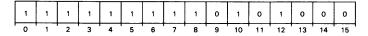

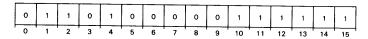

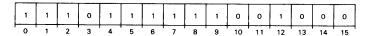

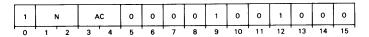

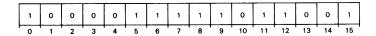

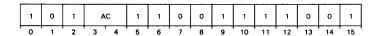

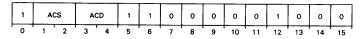

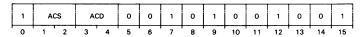

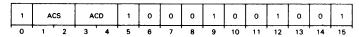

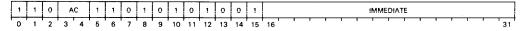

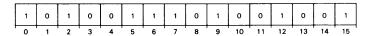

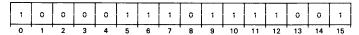

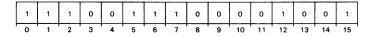

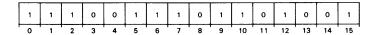

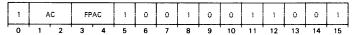

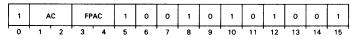

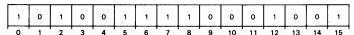

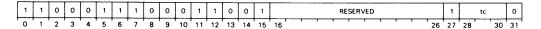

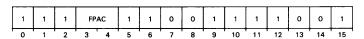

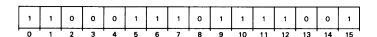

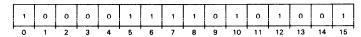

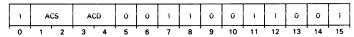

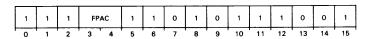

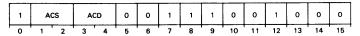

Figure 2.3 shows the format of the processor status register.

Figure 2.3 Processor status register format

**NOTES:** The IRES, IXCT and TES bits are for hardware use. Do not modify the state of these bits; otherwise, results are unpredictable.

Although all MV/Family machines implement Bits 0 and 1, some MV/Family machines may not implement the remaining PSR bits. Refer to the appropriate functional characteristics manual for more specific information.

where

OVK The OVK bit is an overflow mask.

The processor (or you) enable fixed-point overflow detection and servicing by setting the OVK mask to one. You can set the OVK mask to one with the FXTE, LPSR, WSAVS, and WSSVS instructions. (See Table 2.11).

The processor saves or restores the status of the OVK mask when going to or returning from a subroutine or fault handler. For the processor to detect and service an overflow fault, the OVK mask must be set to one before the processor sets the OVR flag to one.

OVR The OVR bit is an overflow flag.

The processor sets the OVR flag to one when it detects a fixed-point overflow condition.

The processor detects a fixed-point overflow condition when the result exceeds the 16-bit precision (for narrow data instruction) or 32-bit precision (for wide data instruction).

The overflow condition (overflow) exists for the duration of the fixed-point instruction that causes the overflow. The processor stores the transient overflow condition by performing a logical inclusive OR of overflow and the OVR flag before completing the instruction.

The OVR flag remains set to one until any of the following events occur

I/O interrupt request

Refer to the Device Management chapter for additional details.

Fault detection and servicing

Refer to the Program Flow chapter for additional details.

Power up, I/O reset, or system reset

Refer to the specific functional characteristics manual for additional details.

• Processor executes an instruction listed in Table 2.11

**IRES** The IRES bit is an interrupt resume flag.

> The processor sets the IRES flag when it interrupts a resumable instruction that requires the processor to save its state on the user stack. For example, when the processor interrupts a wide edit (WEDIT) instruction, the processor sets the IRES flag and saves the microstate on the user stack.

> When a resumable instruction begins execution, it first tests the IRES flag. If the flag is 0, the instruction begins an initial execution. If the flag is 1, the instruction restores the state, resets the IRES flag to 0, and resumes execution.

> NOTE: Although the processor can interrupt some instructions, most instructions cannot be interrupted. Refer to the specific functional characteristics manual for additional information.

**IXCT** The IXCT bit is an interrupt-executed opcode flag.

> When the processor executes the BKPT instruction, it pushes a wide return block onto the current stack. AC0 in the return block contains the one-word instruction (or the first word of a multi-word instruction). Then when returning program control, the PBX instruction (located at the end of the breakpoint handler) pops the wide return block and continues the normal program flow with the saved instruction in ACO.

> If an interrupt occurs while executing the saved instruction (PC points to the BKPT instruction), the processor sets the IXCT flag in the PSR and pushes the opcode of the saved instruction onto the wide stack. Upon returning from the interrupt handler, the BKPT instruction tests the IXCT flag. If the flag is set, the BKPT instruction resets the flag to 0, pops the saved opcode of the interrupted instruction off the wide stack, and executes it.

The TES bit contains the state of the Trap Enable (TE) flag of the Floating-Point Status Register (FPSR). The TES bit is applicable to systems with parallel floating-point units.

Before handling either an Interrupt or Page Fault, the processor must wait for any floating-point instruction executing in a parallel floatingpoint unit (FPU) to complete.

In order to guarantee that any floating-point fault is serviced in the proper context, the processor inhibits the floating-point trap until the completion of the Page Fault or the Interrupt service. To accomplish this, the processor sets bit 4 (TES) of the PSR to reflect the current value of the TE bit in the FPSR. The processor then clears the TE bit of FPSR to inhibit floating-point faults and services the page fault or interrupt.

Upon return from the service routine, the processor restores the FPSR TE bit from the PSR TES bit and clears the PSR TES bit. If the restored FPSR TE bit is 1, the processor services any pending floating-point traps after the next instruction boundary is crossed, such as after a WDPOP or WRSTR instruction.

TES

#### Reserved

The processor sets the reserved bits to zero when storing them in memory. The processor ignores the reserved bits when loading the PSR.

NOTE: Do not set the PSR bits 5 through 13 to store transient data while they are in memory (such as in a return block); these reserved bits must remain unused.

When stored in memory, bits 14 and 15 are reserved for Data General software.

# **Logical Operation**

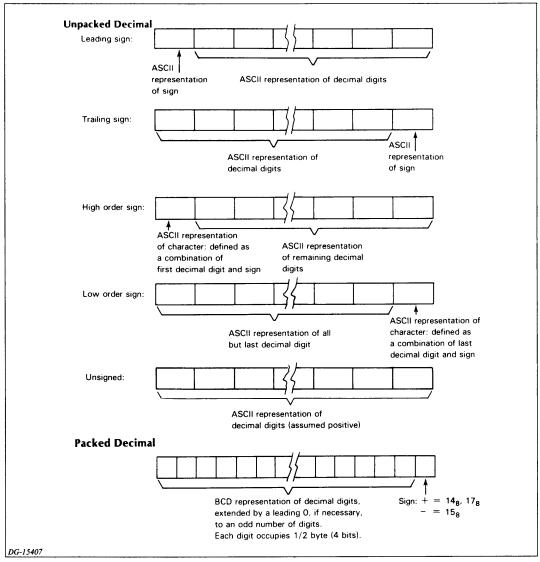

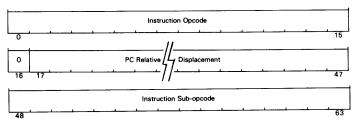

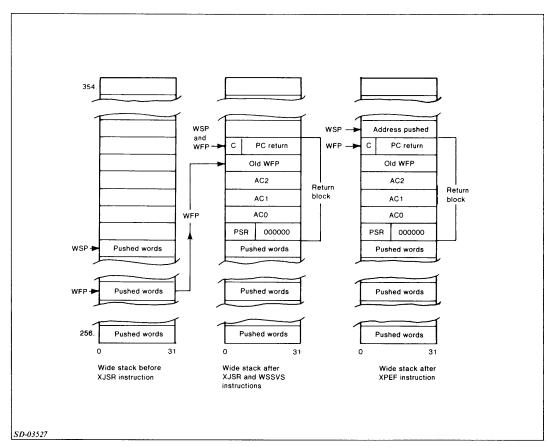

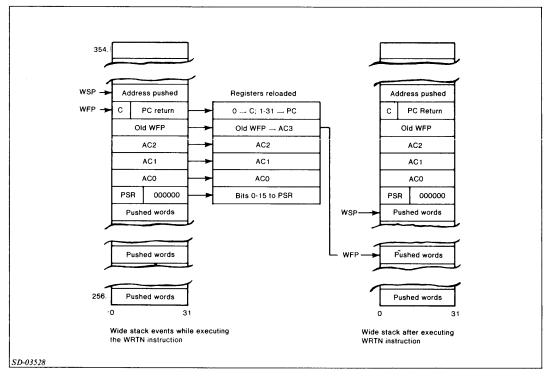

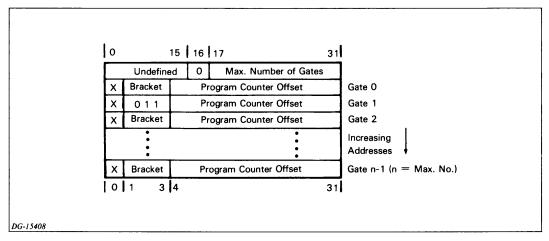

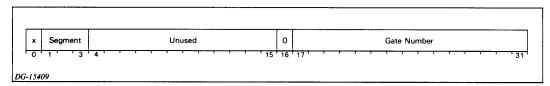

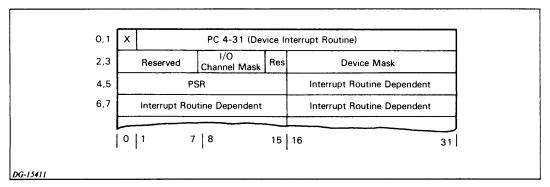

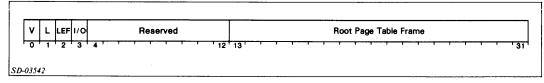

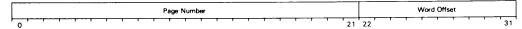

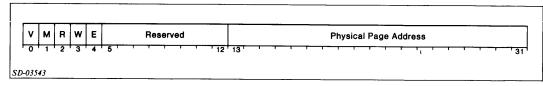

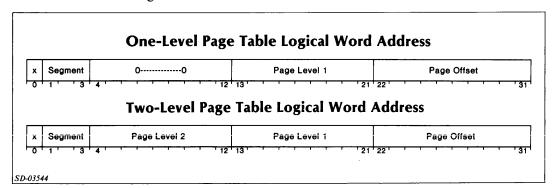

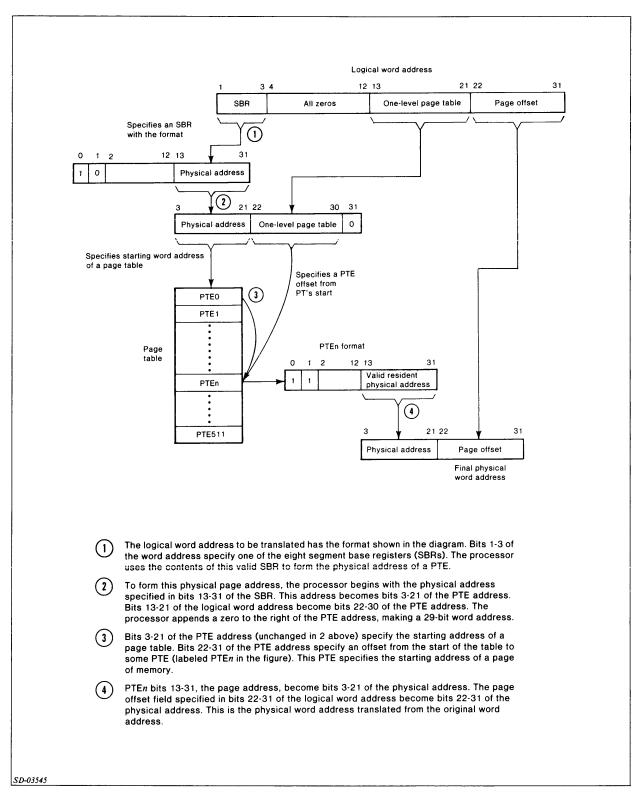

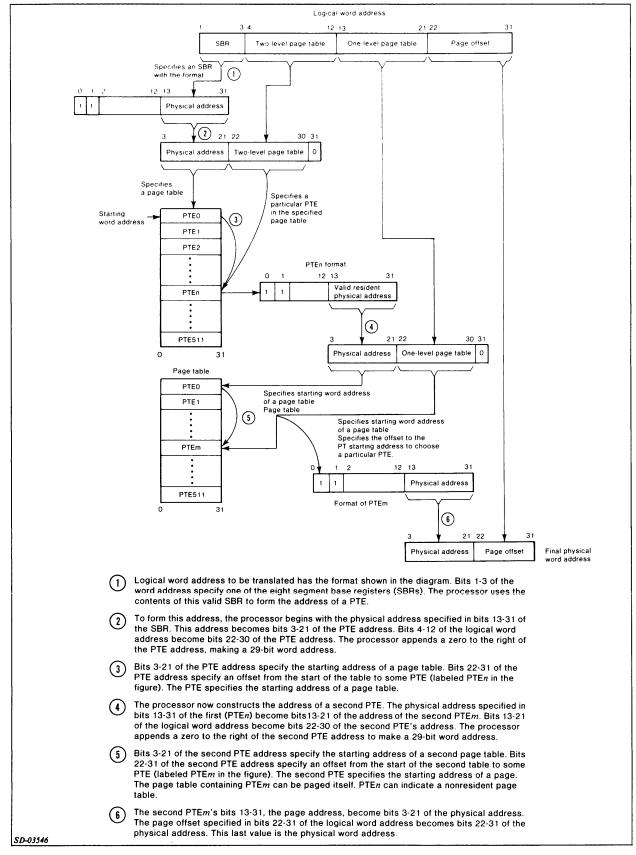

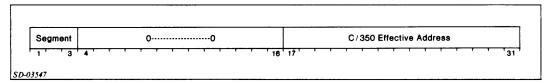

The processor performs fixed-point logical arithmetic in the arithmetic logic unit. You control the processor and arithmetic logic unit operations with the move, logic, shift, and skip instructions.