# KDA50-Q

TECHNICAL DESCRIPTION

KDA5Ø-Q TECHNICAL DESCRIPTION

FOR INTERNAL USE ONLY

Digital Equipment Corporation Colorado Springs, Colorado

# Copyright © 1985 by Digital Equipment Corporation All Rights Reserved

The material in this manual is for informational purposes and is subject to change without notice. DIGITAL assumes no responsibility for any errors which may appear in this manual.

Digital Equipment Corporation does not grant licenses to make, use or sell equipment as described in this manual, and makes no claim that use of its products with those of other manufacturers will not infringe on existing or future patent rights.

This equipment generates, uses, and may emit radio frequency energy. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC rules for operation in a commercial environment. If this equipment is operated in a residential area, the user, at his own expense, may be required to take corrective measures.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC     | DECnet       | RQDX        |

|---------|--------------|-------------|

| DECUS   | DECsystem-10 | RC25        |

| HSC5Ø   | DECSYSTEM-20 | VT          |

| digital | DECwriter    | KDA5Ø-Q     |

| PDP     | RA8Ø         | RSTS        |

| UNIBUS  | RSX          | UDA5Ø       |

| VAX     | MASSBUS      | <b>V</b> MS |

| RA81    | RA6Ø         |             |

# CONTENTS

| CHAPTER | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1.1<br>1.1.1<br>1.1.2<br>1.1.3<br>1.1.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | KDA50-Q DISK CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CHAPTER | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | QBUS OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | 2.1<br>2.1.1<br>2.2<br>2.2.1<br>2.2.2<br>2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INTRODUCTION2-1QBUS Master-Slave Relationship2-1QBUS SIGNAL FUNCTIONS2-1QBUS Priority Chains2-2QBUS Signals Functional Description2-3QBUS TRANSACTIONS2-11Power-up/down Protocol2-12Interrupt Protocol2-15Bus Mastership Protocol2-21Data Transfer Protocol2-24Data Transfers2-25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CHAPTER | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | KDA5Ø-Q FUNCTIONAL BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

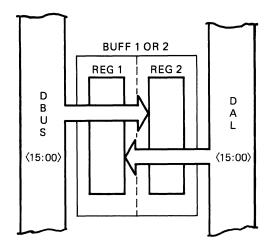

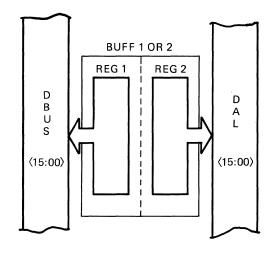

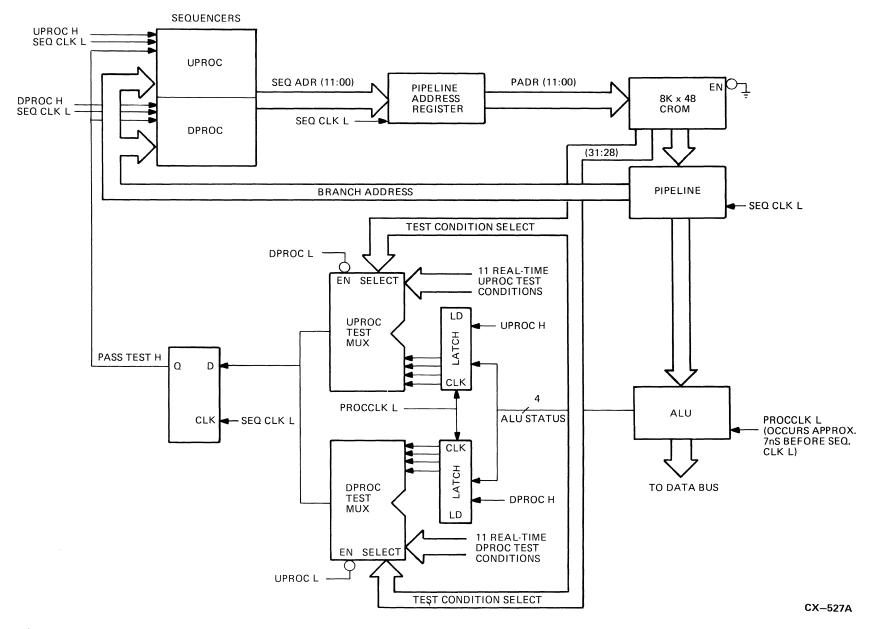

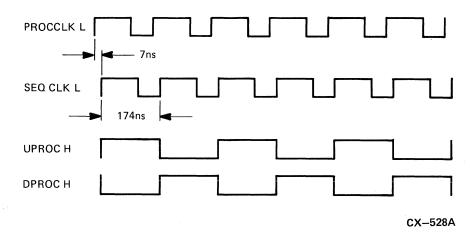

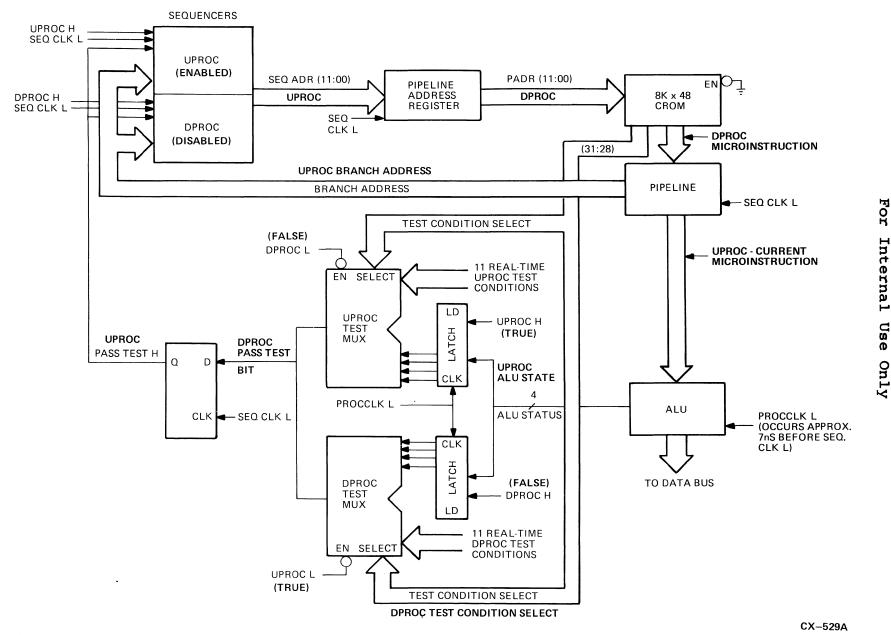

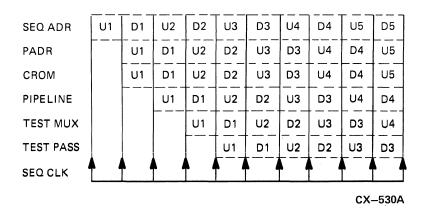

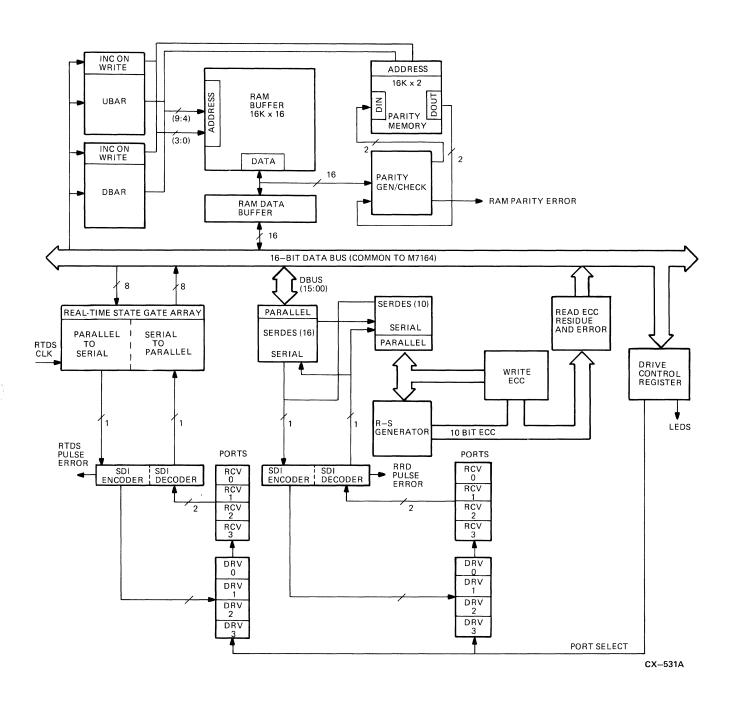

|         | 3.1<br>3.2<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.2.6<br>3.2.7<br>3.2.8<br>3.2.9<br>3.2.10<br>3.2.11<br>3.2.12<br>3.2.13<br>3.2.14<br>3.2.15<br>3.2.16<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3<br>3.3 | INTRODUCTION       3-1         PROCESSOR BLOCK DIAGRAM       3-2         Bus Transceivers       3-4         Address/Data Buffers       3-4         Buffer Control Logic       3-6         QBUS State Machine       3-8         2901 ALU Slice       3-8         2911 Sequencer Slice       3-10         Micro Trap       3-11         Pipeline Address/Data Register (PADR)       3-12         Pipeline Address Register       3-12         Control Store (CROM)       3-12         CROM Parity       3-12         ALU Status Latches       3-12         Test Multiplexer       3-13         Pipeline Register       3-13         UPROC Control Register       3-13         Pipelining Concepts       3-13         SDI BOARD BLOCK DIAGRAM       3-20         U And D Buffer Address Register       3-22         RAM Data Buffer       3-22         RAM Buffer       3-22         Parity Circuit       3-24         SDI Encoder/Decoder (ENC/DEC)       3-24          SDI Encoder/Decoder (ENC/DEC)       3-24 |

|         | 3.3.7<br>3.3.8 | SERDES 10, SERDES 16, And R-S Gen 3-24 Drive Control Register 3-26                  |

|---------|----------------|-------------------------------------------------------------------------------------|

| CHAPTER | 4              | KDA50-Q MICROINSTRUCTION FORMAT                                                     |

|         | 4.1            | INTRODUCTION                                                                        |

|         | 4.2            | KDA5Ø-Q MICROINSTRUCTION 4-1                                                        |

|         | 4.2.1          | CRY Field 4-2                                                                       |

|         | 4.2.2          | AD Field                                                                            |

|         | 4.2.3          | AF Field                                                                            |

|         | 4.2.4          | AS Field                                                                            |

|         | 4.2.5          | AB Field                                                                            |

|         | 4.2.6          | CE Field                                                                            |

|         | 4.2.7          | RB Field                                                                            |

|         | 4.2.8          | TEST Field                                                                          |

|         | 4.2.9          | BD Field                                                                            |

|         | 4.2.10         | @ Field                                                                             |

|         | 4.2.11         | IOC Field                                                                           |

|         | 4.2.12         | LITERAL Field                                                                       |

|         | 4.2.13         | RA Field                                                                            |

|         | 4.2.14         | [BS] Field                                                                          |

|         | 4.2.15         | S Field                                                                             |

|         | 4.2.16         | EN Field                                                                            |

|         | 4.2.17         | K Field                                                                             |

|         | 4.2.17         | P Field                                                                             |

|         | 4.2.19         | BA Field                                                                            |

|         | 4.2.19         | SAMPLE MICROINSTRUCTIONS                                                            |

|         | 4.3.1          |                                                                                     |

|         |                | Sample 1                                                                            |

|         | 4.3.2          | Sample 2                                                                            |

| CHAPTER | 5              | KDA50-Q ERROR HANDLING                                                              |

|         | 5.1            | TNIEDODIJOETON                                                                      |

|         | 5.2            | INTRODUCTION                                                                        |

|         | 5.3            |                                                                                     |

|         |                |                                                                                     |

|         | 5.3.1          | QBUS Packet Read Error (ER.PRD) 5-5                                                 |

|         | 5.3.2          | QBUS Packet Write Error (ER.PWR)5-6<br>KDA50-Q ROM And RAM Parity Error (ER.RRP)5-7 |

|         | 5.3.3          |                                                                                     |

|         | 5.3.4          | KDA50-Q ROM Parity Error (ER.ROP) 5-8                                               |

|         | 5.3.5          | KDA50-Q RAM Parity Error (ER.RAP) 5-9                                               |

|         | 5.3.6          | QBUS Ring Read Error (ER.RRD) 5-10                                                  |

|         | 5.3.7          | QBUS Ring Write Error (ER.RWR) 5-11                                                 |

|         | 5.3.8          | QBUS Interrupt Master Failure (ER.INT) 5-12                                         |

|         | 5.3.9          | Host Access Timeout Error (ER.HTO) 5-13                                             |

|         | 5.3.10         | Host Exceeded Command Limit (ER.NIM) 5-14                                           |

|         | 5.3.11         | QBUS Bus Master Failure (ER.MST) 5-15                                               |

|         | 5.3.12         | DM XFC Fatal Error (ER.DMX) 5-16                                                    |

|         | 5.3.13         | KDA50-Q Hardware Error (ER.TMO) 5-17                                                |

|         | 5.3.14         | Invalid Virtual Circuit Identifier (ER.VCI) . 5-18                                  |

|         | 5.3.15         | Interrupt Write Error On QBUS (ER.IWR) 5-19                                         |

|         | 5.3.16         | Too Many Subunits On KDA50-Q (ER.SUN) 5-20                                          |

|         | 5.3.17         | Mapping Register Read Error (ER.MRR) 5-20                                           |

|         | 5.4            | ERROR LOG FORMAT Ø (CONTROLLER ERROR) 5-21                                          |

|         | 5.4.1          | SERDES Overrun Error (SC.OVR) 5-22                                                  |

|          | 5.4.2<br>5.4.3<br>5.5.5<br>5.5.1<br>5.5.5.5<br>5.6.1<br>5.6.2<br>5.6.3<br>5.6.4<br>5.6.3<br>5.6.5<br>5.7.1<br>5.7.2<br>5.7.3<br>5.7.4<br>5.7.5<br>5.7.7<br>5.7.8<br>5.7.9 | EDC Error (SC.EDC)                                |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| APPENDIX | X A                                                                                                                                                                       | SELECTED CHIP DESCRIPTIONS AND STATUS/EVENT CODES |

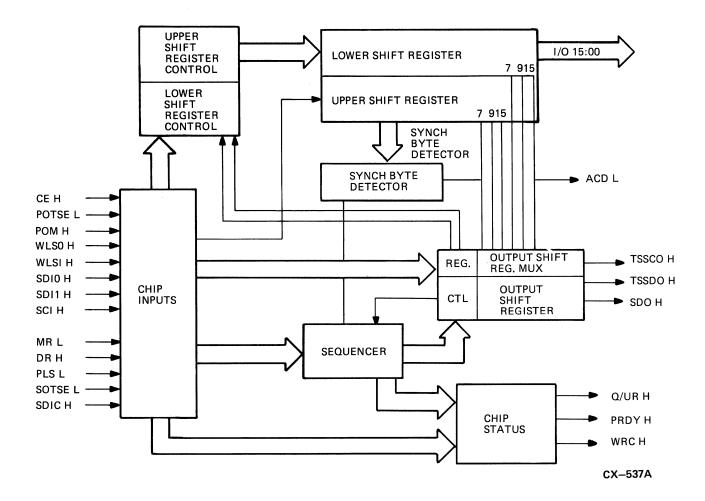

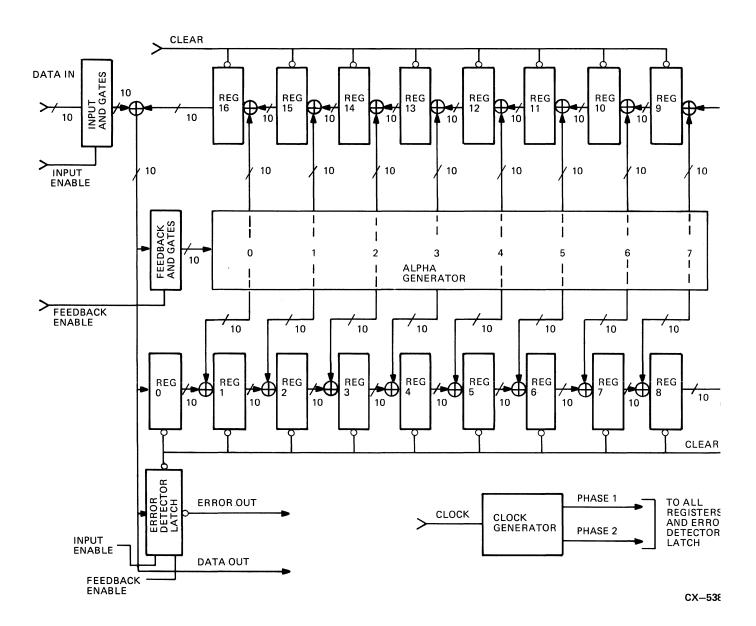

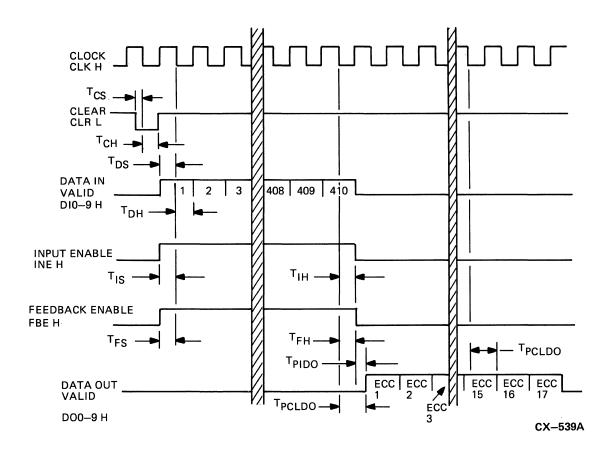

|          | A.1<br>A.2<br>A.3                                                                                                                                                         | SERDES 10 & 16                                    |

| INDEX    |                                                                                                                                                                           |                                                   |

| FIGURES  |                                                                                                                                                                           |                                                   |

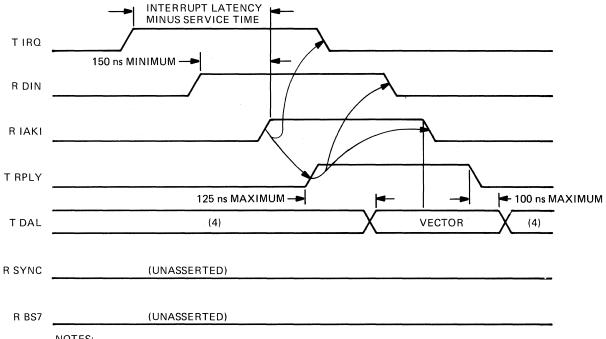

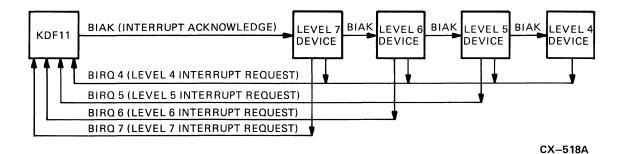

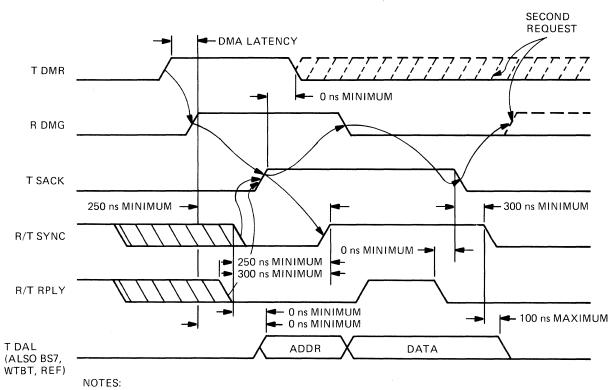

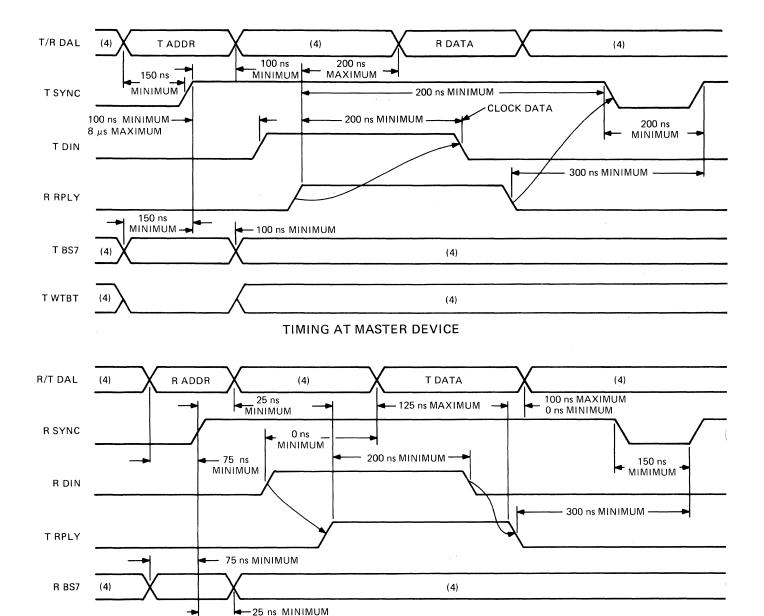

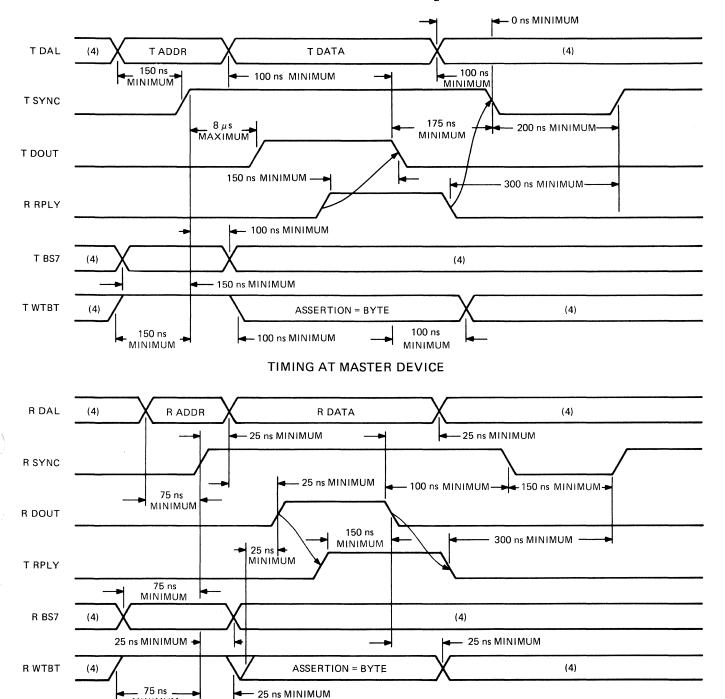

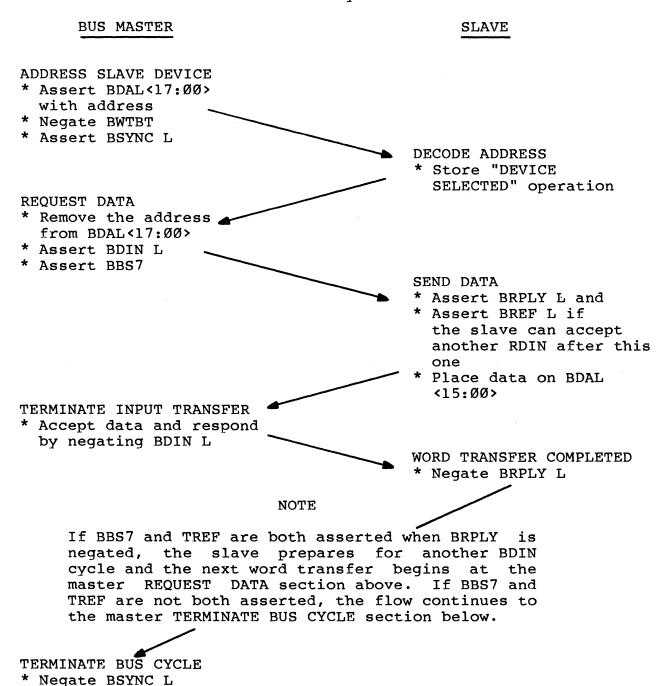

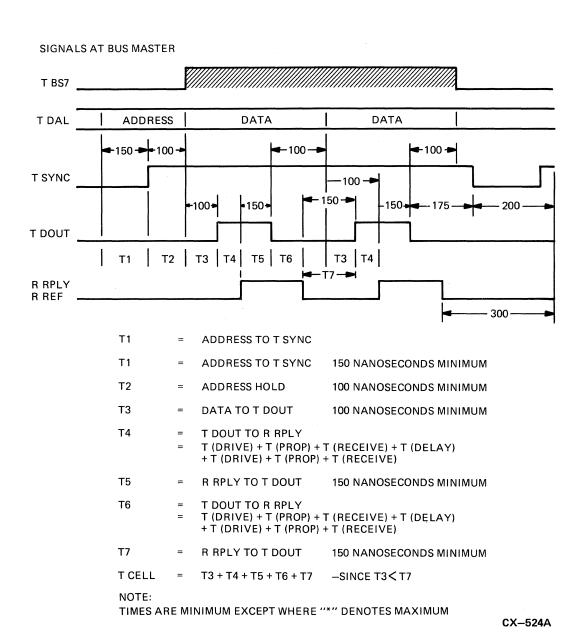

|          | 1-1<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6<br>3-7                                               | KDA50-Q Disk Subsystem Configuration              |

|        | 4-1          | KDA50-Q Microinstruction Format 4-2                  |

|--------|--------------|------------------------------------------------------|

|        | 5-1          | System Hardware Relationship 5-2                     |

|        | 5-2          | System Software/firmware Relationship 5-3            |

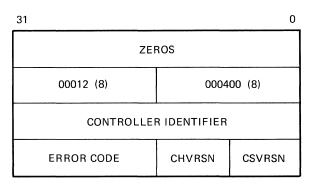

|        | 5-3          | MSCP Last Fail Packet Format 5-4                     |

|        | 5 <b>-</b> 4 | MSCP Controller Error Log Packet Format 5-21         |

|        | 5-5          | MSCP Host Memory Access Error Log Packet Format 5-24 |

|        | 5 <b>-</b> 6 | MSCP Disk Transfer Error Log Packet Format 5-29      |

|        | 5 <b>-</b> 7 | MSCP SDI Error Log Packet Format 5-35                |

| •      | A-1          | SERDES Pin Layout                                    |

|        | A-2          | SERDES Functional Block Diagram                      |

|        | A-3          | R-S Gen Functional Block                             |

|        | A-4          | R-S Gen Typical Write Operation A-13                 |

|        | A-5          | R-S Gen Typical Read Operation A-14                  |

|        |              |                                                      |

| TABLES |              |                                                      |

|        | 1-1          | KDA5Ø Specifications 1-7                             |

|        | 2-1          | Summary Of Signal Line Functions 2-2                 |

|        | 2-2          | QBUS Signal Functional Description 2-3               |

|        | 2-3          | Interrupt Levels 2-18                                |

|        | 2-4          | Position-Independent Interrupts 2-20                 |

|        | 2-5          | I/O Page Addresses                                   |

|        | 2-6          | QBUS Memory Address Ranges 2-25                      |

|        | 2-7          | Data Transfer Types 2-26                             |

|        | 4-1          | ALU Source Operands 4-4                              |

|        | 4-2          | Bus Destinations 4-6                                 |

|        | 4-3          | Bus Sources                                          |

|        | A-1          | SERDES Signal Definitions And Functions A-1          |

|        | A-2          | Reed-Solomon Generator Signal Definitions And        |

| •      |              | Functions A-10                                       |

|        | A-3          | Error Log Status Event Codes                         |

|        |              |                                                      |

#### 1.1 KDA5Ø-Q DISK CONTROLLER

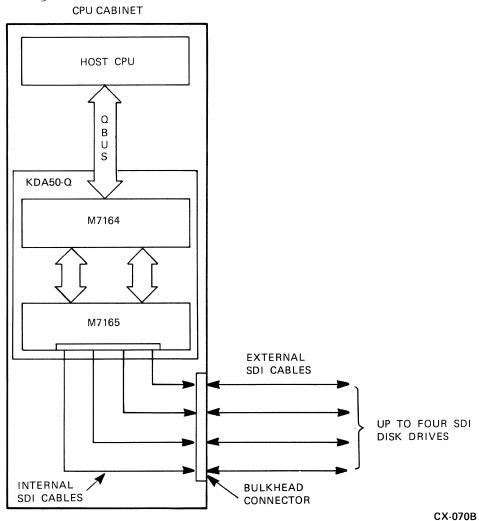

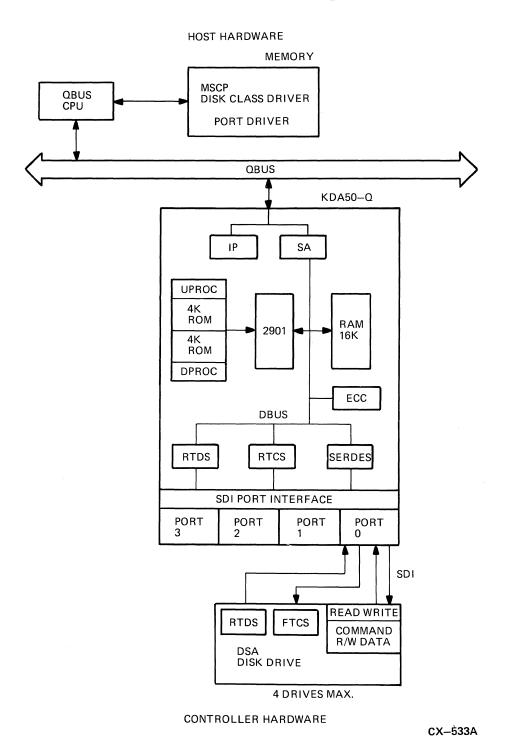

The KDA50-Q is an intelligent controller which interfaces up to four 16-bit RA series disk drives with any CPU that utilizes a QBUS. The physical controller-to-drive interface is accomplished using a radial bus instead of the conventional daisy-chain (serial) method. Radial configuration means a separate I/O cable is attached to each disk drive. Figure 1-1 shows the KDA50-Q subsystem configuration.

Figure 1-1 KDA50-Q Disk Subsystem Configuration

# 1.1.1 KDA5Ø-Q Hardware

The SDI module and the processor module make up the KDA50-Q. The SDI module is the communication interface between the KDA50-Q microprocessor module and the disk drives. The processor module (M7164) is the control portion of the KDA50-Q and is responsible for the QBUS interface.

- 1.1.1.1 SDI Module Some of the circuitry and functions of the SDI module are as follows:

- Contains a 32K-byte high-speed buffer used during data The buffer allows controller-to-drive transfers. transfers to occur a higher rate at controller-to-host transfers. This improves performance by minimizing missed disk revolutions due to buffer-full condition.

- Converts the KDA50-Q buffer format (parallel) to SDI format (serial) and vice versa.

- Generates the real-time error correction code (ECC). This code has a correction capability of up to eight 10-bit error bursts per block (sector).

- Implements the real-time and electrical interface to the SDI, including error detection on the SDI and RAM.

- 1.1.1.2 Processor Module Some of the circuitry and functions of the processor module are listed below:

- Performs all KDA50-Q interaction with the QBUS via two registers: the initializing and polling (IP) register, and the status/address (SA) register. The IP register has a default octal address of 172150. The SA register address is always the IP register address plus 2 (172152 in this case). A switch pack is used to set the I/O page register address.

- Reports microcode detected errors through four LEDs on the processor module and four LEDs on the SDI module.

The error code reported indicates the module to replace.

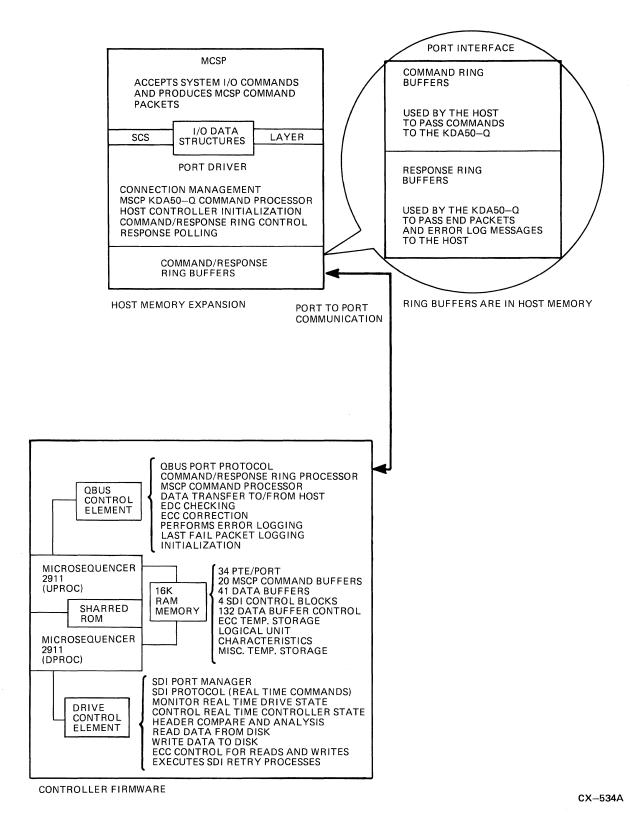

Also located on the processor module is a dual microprocessor. It is made up of two 12-bit microprogram sequencers which share a common 16-bit ALU. The combination of the sequencers and the shared ALU enables the dual microprocessor to execute two independent, interleaved microprograms (from Read Only Memory) at the same time. One of the sequencers controls the KDA50-Q to host interaction, and the other controls the KDA50-Q to disk drive interaction. For greater efficiency, one sequencer fetches an instruction while the other executes an instruction.

#### 1.1.2 Functional Microcode

The functional microcode may be divided into two functional flows or streams: the drive control stream which manages the controller-to-disk-drive interface, and the QBUS control stream which manages the controller-to-host interface.

- 1.1.2.1 Drive Control Stream Some of the functions that the drive control stream performs are listed below:

- Monitors Attention from the drives. When the drive attention bit has been set and detected, the drive control stream gets the drive status, compares it with the previous status, and takes appropriate action.

- Constructs and sends packets to the disk drives. The packets may be the result of a host request (Read, Write, Replace, etc.) or in response to a drive attention condition.

- Receives and validates packets from the drives.

- Monitors the drive status flags from the QBUS control stream. The drive status flags supply communication between the QBUS control stream and the drive control stream.

- Performs tasks as required by the drive status flags.

Some of these tasks are as follows:

- Initiates Read, Write, Seek, and Head-Select packets to the drive.

- Reads and verifies the block (sector) header.

- Performs data transfers between internal RAM and the disk drive.

- Updates drive status and buffer use flags.

- Performs data error analysis and recovery.

- Performs bad block revectoring.

- 1.1.2.2 QBUS Control Stream Some of the functions that the QBUS control stream performs are as follows:

- Vectors to the appropriate handling routine in the microcode when the host has a command to send to the KDA5Ø-Q or the KDA5Ø-Q has a response to send to the host.

- Exchanges information packets with the host in memory.

- Validates each packet from the host.

- Constructs the KDA50-Q response packets for transmission to the host.

- Analyzes the drive packets and performs the functions listed below:

- Decodes the logical block number (LBN) to cylinder, group, track, and sector information.

- Optimizes seek selection from the outstanding commands.

- Allocates data buffer space.

- Computes and stores parameters for each sector transfer.

- Performs packet error detection.

- Performs memory mapping for mapped requests.

- Transfers data between the host and internal memory (including automatic support for block mode memories).

- Performs ECC error correction.

- Polls the command queue at the completion of each command.

- Performs initialization

- Initiates drive control stream packet executions.

# 1.1.3 Digital Storage Architecture (DSA)

The KDA50-Q belongs to the family of DSA products which implements the Standard Disk Interconnect (SDI). DSA defines the operating rules of mass storage subsystems and how they interface with the host computer. Some of the characteristics of DSA are as follows:

- I/O management has been moved from the host to the controller.

- The host views the disk subsystem as one contiguous string of sectors known as logical blocks. A logical block contains 512 bytes of information.

- The host is not concerned with disk geometry such as cylinder, track, sector, etc.

- Host and subsystem exchange messages using the Mass Storage Control Protocol (MSCP).

# 1.1.4 Mass Storage Control Protocol (MSCP)

The KDA50-Q Disk Controller is a Mass Storage Control Protocol (MSCP) device, and MSCP is a communication protocol used with intelligent mass storage controllers. MSCP hides device-dependent requirements, such as disk geometry and error recovery strategies, from the host, and so enables one class driver to be replaced by several different device drivers.

To request an I/O operation, the host constructs an MSCP message and sends it to the controller. The MSCP message contains the drive address, the function to be performed, the starting logical block (sector) number, and the amount of data requested. The message does not contain drive geometry information because MSCP hides device-dependent requirements.

When the subsystem receives the request, it independently performs all drive management and data movement, as well as any necessary error recovery. For example, for the recovery technique called revectoring, the KDA50-Q accesses a replacement sector instead of the original sector found to be in error. The sector in error is then marked as bad and replaced via a cooperative process between the host software and the KDA50-Q. Upon completion, the subsystem gives status information by sending the host an MSCP response message. This flow differs from conventional subsystems in which host computer resources would be used to control the drive.

The KDA50-Q Disk Controller Specifications are described in Table 1-1.

Table 1-1 KDA50 Specifications

| Characteristics                                   | Specifications                                                                                                                                                                                                             |

|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Physical components                               | KDA50 module 1 (M7164) KDA50 module 2 (M7165) 50-pin flat cable assembly 40-pin flat cable assembly SDI cable assembly I/O bulkhead assemblies                                                                             |

| Power consumption                                 | 70 watts nominal                                                                                                                                                                                                           |

| Heat dissipation                                  | Approximately 246 Btu/hour                                                                                                                                                                                                 |

| Electrical voltage<br>and current<br>requirements | 13.5 amps at +5 volts, 30 milliamps at +12 volts                                                                                                                                                                           |

| QBUS Loading                                      | 3.0 AC / .5 DC Standard Loads                                                                                                                                                                                              |

| Operating<br>temperature range                    | $10^{\circ}$ C to $40^{\circ}$ C ( $50^{\circ}$ F to $104^{\circ}$ F) with a temperature gradient of $20^{\circ}$ C/hour ( $36^{\circ}$ F/hour)                                                                            |

| Operating relative humidity range                 | 10% to 90% with a wet bulb temperature of $28^{\circ}$ C (82° F) and a minimum dew point of $2^{\circ}$ C (36° F)                                                                                                          |

| Operating altitude<br>range                       | Sea level to 2400 meters (8000 ft). Derate the maximum allowable operating temperature by 1.80 C/1000 meters (10 F/1000 feet) for operation above sea level                                                                |

| Mounting restrictions                             | Mounts in two quad-height QBUS SPC slots in the following mounting boxes: BA23 rackmount with H3490 BA11-S or BA11-N                                                                                                       |

| Bulkhead<br>Requirements                          | Two cutouts used to mount the SDI cable hardware. These cutouts are 2x3 on the H3490, but may be different sizes on other boxes. These other sizes must be adapted to the 2x3 size as described in the KDA50-Q USER GUIDE. |

- 1.2 RELATED DOCUMENTATION

DIGITAL customers may order the following KDA50-Q related manuals:

- KDA5Ø-Q USER GUIDE (EK-KDA5Q-UG)

- KDA5Ø-Q SERVICE MANUAL (EK-KDA5Q-SV)

- KDA5Ø-Q TECHNICAL DESCRIPTION (EK-KDA5Q-TD)

- KDA5Ø-Q FIELD MAINTENANCE PRINT SET (MP-Ø1423)

Internal DIGITAL Customers:

The <u>User Guide</u>, <u>Service Manual</u> and <u>Technical Description</u> may be ordered directly from Publication and Circulation Services, 10 Forbes Road, Nothboro, Massachusetts 01532 (RCS Code: NR12, Mail Code: NR03/W3).

The Field Maintenance Print Set may be ordered directly from the Software Distribution Center, 444 Whitney Street, Northboro, Massachusetts Ø1532 (RCS Code: MSDC, Mail Code: NRO2-1/J6).

Outside the United States, consult local DIGITAL offices.

#### 2.1 INTRODUCTION

The original LSI-11 bus has 16 bits of addressing, a 16-bit data word, and associated bus control signals. The addressing has been expanded to 18 bits (QBUS) and again to 22 bits (Q22 bus). The differences between these buses are:

- The available addressing.

- The 18- and 22-bit versions support Block mode transfers; the 16-bit version does not.

# 2.1.1 QBUS Master-Slave Relationship

Communication on the QBUS is asynchronous but remains interlocked because of the master-slave relationship. The bus master has control of the bus and is typically the processor or a DMA device. It initiates bus transactions, and the slave device responds by using bus protocol to acknowledge the transaction, receive data, or transmit data. Communication on the QBUS is interlocked because the slave device must respond to the control signals issued by the bus master before the transfer is complete.

If communications on the QBUS break down because the slave does not respond to the bus master, the master aborts the current bus cycle. On the KDA50-Q, a software timer initiates the abort within ten microseconds after the slave fails to respond.

## 2.2 QBUS SIGNAL FUNCTIONS

The QBUS signal lines are functionally divided as shown in Table 2-1.

Table 2-1 Summary Of Signal Line Functions

| Quantity | Function                                      | Bus Signal Mnemonic                    |

|----------|-----------------------------------------------|----------------------------------------|

| 16       | Data address lines                            | BDAL <15:0>                            |

|          | bata address Tilles                           |                                        |

| 2        | Memory<br>parity/address lines                | BDAL <17:16>                           |

| 4        | Address lines                                 | BDAL <21:18>                           |

| 6        | Address and data<br>transfer control<br>lines |                                        |

| 3        | Direct memory access (DMA) control lines      | BDMR, BDMG, BSACK                      |

| 5        | Interrupt control<br>lines                    | BIRQ4, BIRQ5, BIRQ6, BIRQ7,<br>BIAK    |

| 6        | System control lines                          | BPOK, BDCOK, BINIT, BHALT, BREF, BEVNT |

Address bits <15:00> and the 16 bits of data are time multiplexed over the address/data lines <15:00>. Two additional address bits and the memory parity bits are time multiplexed over address lines <17:16>.

Most signals on the QBUS are bi-directional and can be driven or received at any point along the signal line. When a bi-directional signal line is driven, the signal travels both from the driver to the near end bus terminator and from the driver to the far end bus terminator.

# 2.2.1 QBUS Priority Chains

The rest of the QBUS signal lines are unidirectional and travel in only one direction. These signals make up the interrupt and DMA grant daisy chains and are listed below:

- BIAKO L (Interrupt Acknowledge Out)

- BIAKI L (Interrupt Acknowledge In)

- BDMGO L (Direct Memory access Grant Out)

# • BDMGI L (Direct Memory access Grant In)

The interrupt acknowledge and direct memory access lines are connected in a daisy-chain fashion. The output of one device (BIAKO L or BDMGO L) connects to the input of the next device (BIAKI L or BDMGI L), and the processor asserts BIAK or BDMG in response to interrupt or direct memory access requests. Each of the output signals (BIAKO or BDMGO) is received on a device input pin (BIAKI or BDMGI) and conditionally retransmitted via the device output pin (BIAKO or BDMGO).

- 2.2.1.1 Interrupt Priority Chain As an example, assume a QBUS device asserts an interrupt request, but the request is not the highest priority interrupt pending. When the device receives BIAKI L, it retransmits (within 500 nanoseconds) BIAKO L to the next device in the daisy chain. If this QBUS device has the highest priority interrupt pending, it does not retransmit BIAKO L. Instead, the interrupt is accepted and proceeds according to the interrupt protocol described in section 2.3.2.

- 2.2.1.2 DMA Priority Chain The DMA priority daisy chain is similar to the interrupt priority daisy chain except that its priority is determined solely by its position on the bus. In other words, the DMA device electrically closest to the processor has the highest priority. For example, the processor transmits BDMGO in response to a DMA request (BDMR L). The nearest (highest priority) DMA device receives BDMGO on the input pin BDMGI. If this device did not issue the DMA request, it transmits BDMGO to the next device (next lower priority) in the daisy chain. The bus mastership protocol is explained in greater detail in section 2.3.3.

# 2.2.2 QBUS Signals Functional Description Table 2-2 describes all the QBUS signals and lists their associated bus pin. The signal mnemonic is also listed.

Table 2-2 QBUS Signal Functional Description

| Bus<br>Pin | Signal Mnemonic | Signal Function                    |

|------------|-----------------|------------------------------------|

| AAl        | BIRQ5 L         | Interrupt request priority level 5 |

| ABl        | BIRQ6 L         | Interrupt request priority level 6 |

Table 2-2 (cont.)

| Bus<br>Pin | Signal Mnemonic | Signal Function                                                                                                                                                                                                                                                                                                                                                     |

|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC1        | BDAL16 L        | Address line 16 during addressing protocol; memory error data line during data transfer protocol                                                                                                                                                                                                                                                                    |

| AD1        | BDAL17 L        | Address line 17 during addressing protocol; memory error enable during data transfer protocol                                                                                                                                                                                                                                                                       |

| AE1        | SSPARE1 OR +5B  | Special spare - This pin is not assigned or bused in DIGITAL cable or backplane assemblies. It is available for user connection. AEI may be used for +5V battery (+5B) backup power to keep critical circuits alive during power failures. A jumper is required on LSI-11 bus options to open (disconnect) the +5B circuit in systems that use this line as SSPARE1 |

| AF1        | SSPARE2 OR SRUN | Special spare - Not assigned or bused in DIGITAL cable or backplane assemblies. It is available for user connection. In the highest priority device slot, the processor may use this pin for a signal indicating the processor RUN state.                                                                                                                           |

| AH1        | SSPARE3         | Special spare - Not assigned or bused in DIGITAL cable or backplane assemblies. It is available for user connection.                                                                                                                                                                                                                                                |

| AJ1        | GND             | System signal reference and DC return.                                                                                                                                                                                                                                                                                                                              |

| AK1<br>AL1 | MSPAREA         | Maintenance spare - Normally connected together on the backplane at each option location (not a bused connection.)                                                                                                                                                                                                                                                  |

| AM1        | GND             | System signal reference and DC return.                                                                                                                                                                                                                                                                                                                              |

Table 2-2 (cont.)

| Bus<br>Pin | Signal Mnemonic | Signal Function                                                                                                                                                                                                                                                                                          |

|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANl        | BDMR L          | Direct Memory Access (DMA) request - A device asserts this signal to request bus mastership.                                                                                                                                                                                                             |

| APl        | BHALT L         | Processor Halt - When BHALT L is asserted, the processor responds by going into its halt state (generally console ODT mode.)                                                                                                                                                                             |

| ARl        | BREF L          | Memory refresh - Used during refresh protocol to override memory bank selection decoding and cause all banks to be selected.                                                                                                                                                                             |

|            |                 | During block mode transfers, the slave device asserts BREF L with BRPLY L to indicate it can accept another block mode DIN or DOUT cycle.                                                                                                                                                                |

| AS1        | +5B or +12B     | +12V or +5V battery backup to keep critical circuits alive during power failures. This signal is not bused to BS1 in all DIGITAL backplanes. A jumper is required on all LSI-ll Bus options to open (disconnect) the backup circuit from the bus in systems that use this line at the alternate voltage. |

| AT1        | GND             | System signal reference and DC return.                                                                                                                                                                                                                                                                   |

| AUl        | PSPARE1         | Power spare 1 - This pin is not assigned and customer usage is not recommended. If a backplane is busing -12 volts (on pin BB2) and a module is accidentally inserted upside down in the backplane, -12 volts appears on pin AU1. If AU1 is unused on the module, no damage will occur.                  |

| AV1        | +5B             | +5V. Battery backup power - To keep critical circuits alive during power failures.                                                                                                                                                                                                                       |

Table 2-2 (cont.)

| Bus<br>Pin               | Signal Mnemonic                                                                      | Signal Function                                                                                                                                                                                                           |

|--------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BA1                      | BDCOK H                                                                              | DC Power OK - The power supply generates this signal when sufficient DC voltage is available to sustain reliable system operation. It is part of the powerup, powerdown and boot protocol.                                |

| BB1                      | врок н                                                                               | AC Power OK - The power supply asserts this signal when primary power is normal. If negated during processor operation, a power fail trap sequence is initiated. It is part of the powerup, powerdown, and boot protocol. |

| BC1<br>BD1<br>BE1<br>BF1 | BDAL18 or SSPARE 4<br>BDAL19 or SSPARE 5<br>BDAL20 or SSPARE 6<br>BDAL21 or SSPARE 7 | Special spares <7:4> in older LSI-ll Bus Systems. Not assigned or bused in non-Q22 BUS cable and backplane assemblies. Address lines <21:18> in Q22 BUS backplane and cable assemblies.  CAUTION                          |

|                          | some DIGITAL or cu                                                                   | been used as test points in stomer options. These options designated incompatible with                                                                                                                                    |

| BH1                      | SSPARE 8                                                                             | Special spare - not assigned or bused in DIGITAL cable or backplane assemblies available for user connection.                                                                                                             |

| BJ1                      | GND                                                                                  | System signal reference and DC return.                                                                                                                                                                                    |

| BK1<br>BL1               | MSPAREB<br>MSPAREB                                                                   | Maintenance Spares - Normally connected together on the backplane at each option location (not a bused connection).                                                                                                       |

| BM1                      | GND                                                                                  | System signal reference and DC return.                                                                                                                                                                                    |

Table 2-2 (cont.)

| Bus<br>Pin | Signal Mnemonic | •                                                                                                                                                                                                                                                                                              |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BN1        | BSACK L         | A DMA device asserts this signal in response to the BDMGO L signal indicating it accepts bus mastership. The device remains bus master until it negates BSACK L.                                                                                                                               |

| BPl        | BIRQ7 L         | Interrupt request priority level 7.                                                                                                                                                                                                                                                            |

| BR1        | BEVNT L         | External Event Interrupt Request - The processor latches the leading edge and arbitrates as an interrupt. A typical use of this signal is a line time clock interrupt.                                                                                                                         |

| BS1        | +12B            | +12V DC battery backup power (not bused to AS1 in all DIGITAL backplanes)                                                                                                                                                                                                                      |

| BTl        | GND             | System signal reference and DC return.                                                                                                                                                                                                                                                         |

| BUl        | PSPARE2         | Power spare 2 - This signal is not assigned a function and is not recommended for use. If a backplane is busing -12 volts (on pin AB2) and a module is accidentally inserted upside down in the backplane, -12 volts appears on pin BU1. If BU1 is unused on the module, no damage will occur. |

| BVl        | +5V             | Normal +5V DC system power.                                                                                                                                                                                                                                                                    |

| AA2        | +5V             | Normal +5V DC system power.                                                                                                                                                                                                                                                                    |

| AB2        | -12V            | Optional -12V power for devices requiring this voltage.                                                                                                                                                                                                                                        |

| AC2        | GND             | System signal reference and DC return.                                                                                                                                                                                                                                                         |

| AD2        | +12V            | Normal +12V DC system power.                                                                                                                                                                                                                                                                   |

| m - 1. 1 |   | 2   | 1      | ١. |

|----------|---|-----|--------|----|

| 'l'ab I  | e | 2-2 | (cont. | )  |

| Bus<br>Pin | Signal Mnemonic                                                                                                                                                    | Signal Function                                                                                                                                                                                                                                       |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AE2        | BDOUT L                                                                                                                                                            | Data output - BDOUT, when asserted, implies that valid data is available on BDAL <15:00> L, and that an output transfer, with respect to the bus master device, is taking place.                                                                      |  |  |

| AF2        | BRPLY L                                                                                                                                                            | Slave devices assert BRPLY L in response to BDIN L or BDOUT L, indicating their ability to transfer data according to the appropriate protocol. BRPLY L is also asserted during interrupt acknowledge (IAK) transactions.                             |  |  |

| AH2        | BDIN L                                                                                                                                                             | Data Input - BDIN L is used for two types of bus operation:                                                                                                                                                                                           |  |  |

|            | input transfer wi                                                                                                                                                  | . When asserted during BSYNC L time, BDIN L implies an input transfer with respect to the current bus master and requires a response, BRPLY L, from the addressed slave.                                                                              |  |  |

|            | 2. The interrupt f service by assertin                                                                                                                             | ielding processor initiates interrupt g TDIN L followed by TIACK L.                                                                                                                                                                                   |  |  |

| AJ2        | BSYNC L                                                                                                                                                            | Synchronize - The bus master device asserts BSYNC L, indicating it has placed an address on the bus. The transfer is in process until the master negates BSYNC L. In block mode, BSYNC L remains asserted until the last transfer cycle is completed. |  |  |

| AK2        | BWTBT L                                                                                                                                                            | Write/Byte - BWTBT L is used in two ways to control a bus cycle:                                                                                                                                                                                      |  |  |

|            | <ol> <li>It is asserted during the address portion of a<br/>to indicate that an output cycle is to follow<br/>DATOB, DATBO) rather than an input cycle.</li> </ol> |                                                                                                                                                                                                                                                       |  |  |

|            |                                                                                                                                                                    | uring the Data portion of a DATOB or to indicate a byte rather than a work place.                                                                                                                                                                     |  |  |

| AL2        | BIRQ4 L                                                                                                                                                            | Interrupt request priority level 4.                                                                                                                                                                                                                   |  |  |

Table 2-2 (cont.)

| Bus<br>Pin   | Signal Mnemonic | Signal Function                                                                                                                                                                                                                                               |

|--------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AM 2<br>AN 2 | BIAKI<br>BIAKO  | Interrupt Acknowledge - The processor asserts BIAKO L to acknowledge an interrupt. The bus transmits this to BIAKI L of the next priority device (electrically closest to the processor). This device accepts the interrupt acknowledge under two conditions: |

- 1. The device requested the bus by asserting an interrupt, BIRQ(x) L.

- 2. The device had the highest priority interrupt request on the bus at the time of the preceding BDIN L assertion. If both of these conditions are not met, the device asserts BIAKO L to the next device on the bus. This process continues in a daisy-chain fashion until the device with the highest interrupt priority receives the Interrupt Acknowledge (IAK) signal and proceeds with Interrupt Protocol.

AP2 BBS7 L

Bank 7 select - When the bus master TADDR, it asserts signal to reference the I/O page (including that part of the I/O page reserved for nonexistent memory). I/O page address is placed on BDAL <12:00> L and the address bits from BDAL <13> on up are ignored. DATBI transfers, During the bus master asserts this signal with the first data transfer until the transfer indicates to the block mode slave that there will be subsequent transfers.

Table 2-2 (cont.)

| Bus<br>Pin | Signal Mnemonic | Signal Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AR2<br>AS2 | BDMGI<br>BDMGO  | Direct memory access grant - The bus arbitrator asserts this signal to grant bus mastership to a requesting device according to bus mastership protocol. The signal is passed in a daisy-chain from the arbitrator (as BDMGO L) along the bus to BDMGI L of the next priority device. This device accepts the grant only if it requested the bus (by assertion of BDMR L). If not, the device passes the grant (asserts BDMGO L) to the next device on the bus. This process continues until the requesting device acknowledges the grant by asserting BSACK L after BRPLY L and BSYNC L are both negated. |