# **Company Confidential**

# **PRISM System Reference Manual**

# **Second Draft**

**Digital Equipment Corporation - Confidential and Proprietary**

# Note

This document is the System Reference Manual for PRISM. THIS DOCUMENT IS CONFIDENTIAL.

Do not copy it, distribute it, or remove it from company property

**Revision No:**

1.0

**Document Copy:**

Date:

22-DEC-1985

104

# CONTENTS

| CHAPTER | 1                                                                                                                         | INTRODUCTION                                                                                                                                                                                                                                                                                                                                               |

|---------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1.1<br>1.2<br>1.3<br>1.3.1<br>1.3.2<br>1.4<br>1.5<br>1.5.1<br>1.5.2<br>1.6.1<br>1.6.2<br>1.6.3<br>1.6.4<br>1.6.5<br>1.6.5 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                               |

| CHAPTER | 2                                                                                                                         | BASIC ARCHITECTURE                                                                                                                                                                                                                                                                                                                                         |

|         | 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6<br>2.2.7                                                 | ADDRESSING                                                                                                                                                                                                                                                                                                                                                 |

| CHAPTER | 3                                                                                                                         | INSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                        |

|         | 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.2<br>3.2.1<br>3.2.2<br>3.3<br>3.3.1<br>3.3.2<br>3.3.3<br>3.3.3.1                      | PRISM REGISTERS  Scalar Registers  Vector Registers  Program Counter  NOTATION  Scalar Operand Values  Operators  INSTRUCTION FORMATS  Memory Instruction Format  Branch Instruction Format  Operate Instructions  Epicode Instruction Format  Coprocessor Instruction Format  Coprocessor Instruction Format  3-6 3-7 3-7 3-7 3-7 3-7 3-7 3-7 3-7 3-7 3-7 |

| CONTENTS                       | Company Confidential                                                                                                                                                                                                                                                                                                                                                                                                                                | Page iv                                                                                                                      |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 4                      | INSTRUCTION DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                              |

| 4.1<br>4.1.1<br>4.1.2<br>4.1.3 | INSTRUCTION SET OVERVIEW AND NOTATION Subsetting Rules                                                                                                                                                                                                                                                                                                                                                                                              | 4-2 4-3 4-3                                                                                                                  |

| 4.2                            | MEMORY LOAD/STORE INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                      | 4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-12<br>4-14                                                                            |

| 4.3                            | INTEGER ARITHMETIC INSTRUCTIONS Integer Add Integer Signed Compare Integer Unsigned Compare Integer Divide Integer Remainder Integer Multiply Integer Subtract Vector Integer Add Vector Integer Compare Vector Integer Divide Vector Integer Remainder Vector Integer Remainder Vector Integer Subtract                                                                                                                                            | 4-16<br>4-18<br>4-19<br>4-20<br>4-21<br>4-22<br>4-23<br>4-24<br>4-25<br>4-26<br>4-27<br>4-28<br>4-29                         |

| 4.4                            | LOGICAL AND SHIFT INSTRUCTIONS Logical Functions Shift Logical Shift Arithmetic Rotate Vector Logical Functions Vector Merge Vector Shift Logical                                                                                                                                                                                                                                                                                                   | 4-31<br>4-32<br>4-33<br>4-34<br>4-35<br>4-36                                                                                 |

| 4.5<br>4.5.1<br>4.5.2<br>4.5.3 | Literals Accuracy Floating-Point Exceptions Floating Add Floating Compare Convert F_Floating to G_Floating Convert Floating to Integer Convert Integer to Floating Floating Divide Floating Multiply Floating Subtract Vector Floating Compare Vector Convert F_Floating to G_Floating Vector Convert F_Floating to F_Floating Vector Convert F_Floating to F_Floating Vector Convert F_Floating to F_Floating Vector Convert F_Floating to Integer | 4-39<br>4-43<br>4-43<br>4-46<br>4-47<br>4-48<br>4-49<br>4-50<br>4-51<br>4-52<br>4-53<br>4-54<br>4-55<br>4-56<br>4-56<br>4-60 |

| CONTENTS | ;                                                                                                         | Company Confidential                                                                                                                                                                                                                                                                                                                      | Page v                                                                                 |

|----------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|          | 4.6                                                                                                       | Vector Convert Integer to Floating Vector Floating Divide                                                                                                                                                                                                                                                                                 | . 4-64<br>. 4-66<br>. 4-68<br>. 4-70<br>. 4-71                                         |

|          | 4.7                                                                                                       | Fault On Low Bit Set                                                                                                                                                                                                                                                                                                                      | <ul><li>4-73</li><li>4-74</li><li>4-75</li></ul>                                       |

|          |                                                                                                           | Drain Instruction Pipeline                                                                                                                                                                                                                                                                                                                | . 4-77<br>. 4-78<br>. 4-79<br>. 4-80<br>. 4-81<br>. 4-82<br>. 4-83<br>. 4-84<br>. 4-85 |

|          | 4.8                                                                                                       | PRIVILEGED INSTRUCTIONS  HALT  Move From Processor Register  Move To Processor Register  Read, Mask, Add Quadword, Interlocked, Physi Swap Privileged Context  Swap IPL                                                                                                                                                                   | . 4-88<br>. 4-89<br>. 4-90<br>. 4-91<br>cal 4-92<br>. 4-93                             |

|          | 4.9                                                                                                       | Flush Translation Buffer                                                                                                                                                                                                                                                                                                                  | . 4-98                                                                                 |

| CHAPTER  | 5                                                                                                         | MEMORY MANAGEMENT                                                                                                                                                                                                                                                                                                                         |                                                                                        |

|          | 5.1<br>5.2<br>5.2.1<br>5.3<br>5.4<br>5.5<br>5.5.1<br>5.6.1<br>5.6.2<br>5.6.3<br>5.7<br>5.8<br>5.9<br>5.10 | INTRODUCTION VIRTUAL ADDRESS SPACE Virtual Address Format PHYSICAL ADDRESS SPACE MEMORY MANAGEMENT CONTROL PAGE TABLE ENTRIES Changes To Page Table Entries MEMORY PROTECTION Processor Access Modes Protection Code Access Control Violation Fault ADDRESS TRANSLATION TRANSLATION BUFFER ADDRESS SPACE NUMBERS MEMORY MANAGEMENT FAULTS | 5-2<br>5-2<br>5-3<br>5-3<br>5-5<br>5-6<br>5-6<br>5-7<br>5-9<br>5-9<br>5-12             |

| CHAPTER  |                                                                                                           | EXCEPTIONS AND INTERRUPTS                                                                                                                                                                                                                                                                                                                 |                                                                                        |

|          | 6.1                                                                                                       | INTRODUCTION                                                                                                                                                                                                                                                                                                                              | 6-1                                                                                    |

| 6.1.1          | Processor Interrupt Priority Level (IPL)                              | . 6-1        |

|----------------|-----------------------------------------------------------------------|--------------|

| 6.1.2          | Interrupts                                                            | . 6-2        |

| 6.1.3          | Exceptions                                                            | . 6-2        |

| 6.1.4          | Contrast Between Exceptions And Interrupts                            | . 6-3        |

| 6.2            | PROCESSOR STATE                                                       | . 6-4        |

| 6.3            | INTERRUPTS                                                            | . 6-6        |

| 6.3.1          | Asynchronous System Trap (AST) - Level 1                              | . 6-7        |

| 6.3.2          | Software Generated Interrupts - Levels 1 To 3                         | . 6-7        |

| 6.3.2.1        | Software Interrupt Summary Register                                   | . 6-7        |

| 6.3.2.2        | Software Interrupt Request Register                                   | 6-7          |

| 6.3.3          | Console Interrupts - Level 4                                          | 6-8          |

| 6.3.3.1        | Console Interrupts - Level 4                                          | . 6-8        |

| 6.3.3.2        | Console Transmit Control Status                                       | 6-9          |

| 6.3.4          | Console Transmit Control Status I/O Port Controllers - Levels 4 And 5 | 6-9          |

| 6.3.5          | Interval Clock Interrupt - Level 5                                    | 6-0          |

| 6.3.5.1        | Interval Clock Interrupt Enable                                       | 6-0          |

| 6.3.6          | Urgent Interrupts - Levels 6 And 7                                    | 6-10         |

| 6.3.6.1        | Interprocessor Interrupt Enable Register                              |              |

| 6.3.6.2        | Interprocessor Interrupt Request Register                             |              |

| 6.4            | EXCEDITIONS                                                           | 6-11         |

|                | EXCEPTIONS                                                            | 6-11         |

| 6.4.1<br>6.4.2 | Arithmetic Traps                                                      | 6-12<br>6-15 |

|                | Data Alignment Exceptions                                             | 0-12         |

| 6.4.2.1        | Scalar Alignment Fault                                                | 6-15         |

| 6.4.2.2        | Vector Alignment Abort                                                | 6-16         |

| 6.4.3          | Faults Occurring As The Result Of An                                  |              |

|                | Instruction                                                           | 6-17         |

| 6.4.3.1        | Breakpoint Fault                                                      | 6-17         |

| 6.4.3.2        | Bug Check Fault                                                       | 6-18         |

| 6.4.3.3        | Fault On Bit                                                          | 6-18         |

| 6.4.4          | Illegal Operand Fault                                                 | 6-19         |

| 6.4.4.1        | Privileged Instruction                                                | 6-20         |

| 6.4.4.2        | Reserved Opcode Fault                                                 | 6-23         |

| 6.4.4.3        | Vector Enable                                                         | 6-22         |

| 6.4.5          | Memory Management Faults                                              | 6-23         |

| 6.4.5.1        | Access Violation                                                      | 6-24         |

| 6.4.5.2        | Translation Not Valid                                                 | 6-24         |

| 6.4.5.3        | Fault On Execute                                                      | 6-25         |

| 6.4.5.4        | Fault On Read                                                         | 6-25         |

| 6.4.5.5        | Fault On Write                                                        | 6-25         |

| 6.4.6          | Serious System Failures                                               | 6-25         |

| 6.4.6.1        | Kernel Stack Not Valid Halt                                           | 6-25         |

| 6.4.6.2        | Machine Check Abort                                                   |              |

| 6.4.7          | Stack Alignment Abort                                                 | 6-2          |

| 6.4.8          | Vector Exceptions                                                     | 6-2          |

| 6.4.8.1        | Vector Exception Continuation                                         | 6-3          |

| 6.5            | SERIALIZATION OF EXCEPTIONS AND INTERRUPTS                            | 6-3          |

| 6.6            |                                                                       | 6-3          |

| 6.7            |                                                                       | 6-3          |

|                | STACKS                                                                | 6-3          |

| 6.7.1          | Stack Writability                                                     |              |

| 6.7.2          | Stack Residency                                                       | 6-3          |

| 6.7.3          | Stack Alignment                                                       | 6-3          |

| 6.7.4          | Initiate Exception Or Interrupt                                       | 6-3          |

| 6.7.5          | Instruction Issue Model                                               | 6-3          |

| 6.7.6          | Epicode Interrupt Arbitration                                         | 6-4          |

| 6761           | MTDD AST Request Register                                             | 6-4          |

| CONTENTS |                                                   | Company Confidential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Page vii |                                                                                                                                                              |  |

|----------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          | 6.7.6.2<br>6.7.6.3<br>6.7.6.4<br>6.7.6.5<br>6.7.7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • •      | 6-41<br>6-41<br>6-41                                                                                                                                         |  |

| CHAPTER  | 7                                                 | PROCESS STRUCTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |                                                                                                                                                              |  |

|          | 7.1<br>7.2<br>7.3<br>7.3.1<br>7.4<br>7.4.1        | PROCESS DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | • •      | . 7-2<br>. 7-4<br>. 7-6                                                                                                                                      |  |

| CHAPTER  | 8                                                 | INTERNAL PROCESSOR REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |                                                                                                                                                              |  |

|          | 8.1                                               | Address Space Number (ASN)  AST Enable (ASTEN)  AST Request Register (ASTRR)  AST Summary Register (ASTSR)  Console Receive Control Status (CRCS)  Console Receive Data Buffer (CRDB)  Console Transmit Control Status (CTCS)  Console Transmit Data Buffer  Stack Pointer Registers (ESP, SSP, USP)  Interval Clock Interrupt Enable (ICIE)  Interprocessor Interrupt Enable (IPIE)  Interprocessor Interrupt Request (IPIR)  Privileged Context Block Base (PCBB)  Processor Base Register (PRBR)  Processor Serial Number (PRSN)  Page Table Base Register (PTBR)  System Control Block Base (SCBB)  System Identification (SID)  Software Interrupt Request Register (SIRR)  Software Interrupt Summary Register (SISR)  Translation Buffer Check (TBCHK)  Translation Buffer Invalidate By ASN (TBIAS)  Time Of Year (TOY)  Who-Am-I (WHAMI) |          | . 8-3<br>. 8-4<br>. 8-5<br>. 8-6<br>. 8-7<br>. 8-8<br>. 8-11<br>8-11<br>8-13<br>8-14<br>8-15<br>8-16<br>8-17<br>8-18<br>8-20<br>8-21<br>8-23<br>8-26<br>8-27 |  |

| CHAPTER  | 9                                                 | SYSTEM ARCHITECTURE AND PROGRAMMING IMPLICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ONS      | }                                                                                                                                                            |  |

|          | 9.1<br>9.2<br>9.3<br>9.4<br>9.5                   | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • •      | . 9-1<br>. 9-3<br>. 9-3                                                                                                                                      |  |

| CONTENTS                                                                                                                                                             | Company Confidential                                       | Page viii                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 10                                                                                                                                                           | EXTENDED PROCESSOR INSTRUCTION CODE                        |                                                                                                                                              |

| 10.1<br>10.2<br>10.3<br>10.4                                                                                                                                         | INTRODUCTION                                               | 10-2                                                                                                                                         |

| CHAPTER 11                                                                                                                                                           | SYSTEM BOOTSTRAPPING AND CONSOLE                           |                                                                                                                                              |

| 11.1<br>11.1.1<br>11.1.1<br>11.1.1<br>11.1.1<br>11.1.1<br>11.1.1<br>11.1.2<br>11.1.4<br>11.1.4<br>11.1.4<br>11.1.4<br>11.1.5<br>11.2.3<br>11.3.1<br>11.3.3<br>11.3.3 | Bootstrapping In A Uniprocessor Environment Memory Testing | nt . 11-1 11-2 11-2 11-7 11-7 11-8 11-8 11-8 11-10 11-11 11-11 11-12 11-12 11-14 11-14 11-14 11-15 11-15 11-16 11-17 11-18 11-20 11-25 11-26 |

| 12.1                                                                                                                                                                 | TO BE SUPPLIED                                             | 12-1                                                                                                                                         |

| APPENDIX A                                                                                                                                                           | INSTRUCTION SET SUMMARY                                    |                                                                                                                                              |

| A.1<br>A.2                                                                                                                                                           | ENCODING HINTS                                             | A-1                                                                                                                                          |

| CONTENTS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Company Confidential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                        |  |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|          | A.3<br>A.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MNEMONIC LISTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . A-10<br>. A-17                                                                                                                                                                       |  |  |  |  |  |

| APPENDIX | В                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 64-BIT ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                        |  |  |  |  |  |

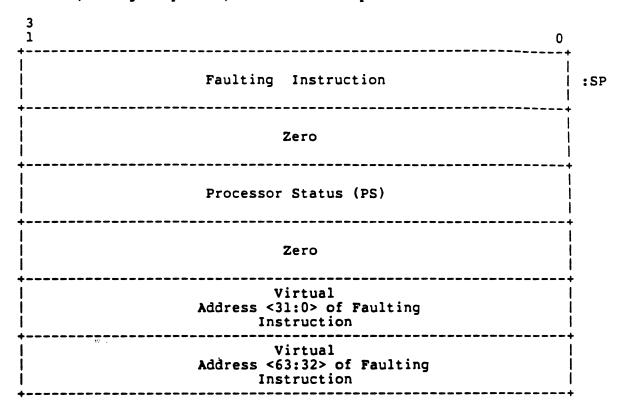

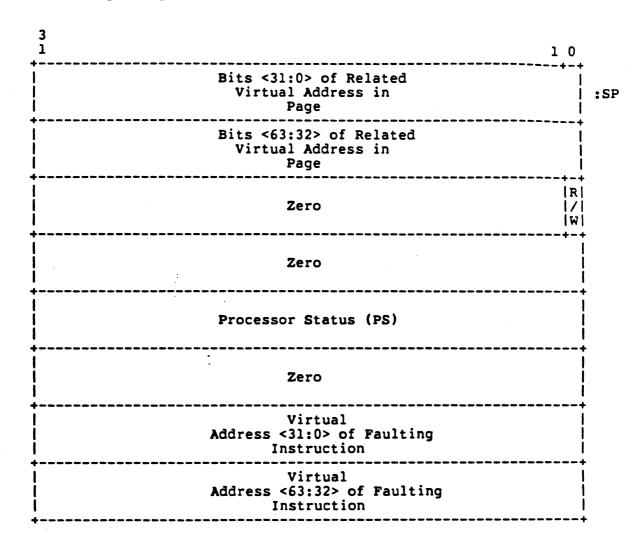

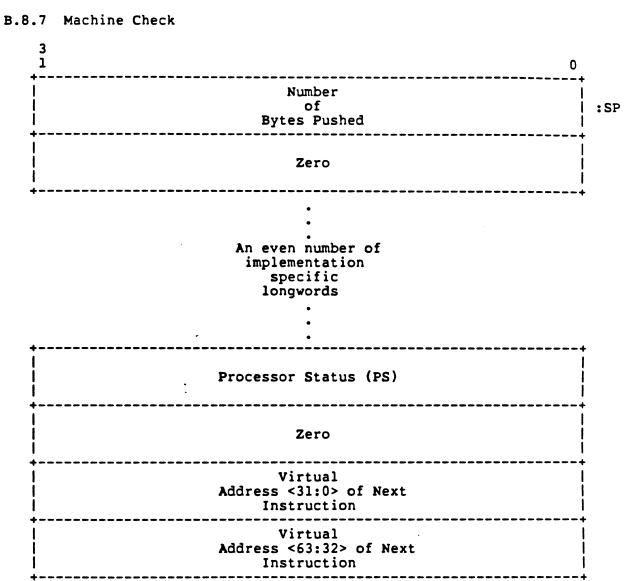

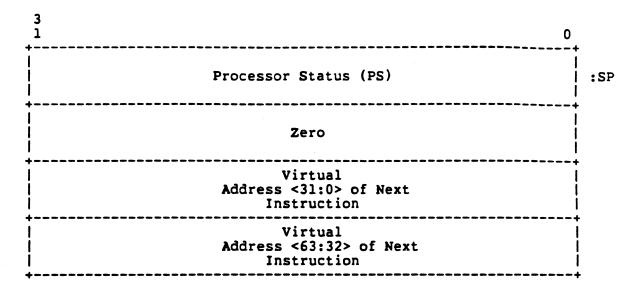

|          | B.1<br>B.3<br>B.3.1<br>B.3.3<br>B.5.3<br>B.5.5<br>B.5.5<br>B.5.5<br>B.5.5<br>B.6.6<br>B.6.3<br>B.6.3<br>B.8.3<br>B.8.4<br>B.8.5<br>B.8.5<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8.8<br>B.8. | GOALS AND NON-GOALS  DATA TYPES  REGISTERS  Scalar Registers  Vector Registers  Vector Registers  Program Counter  INSTRUCTION FORMATS  INSTRUCTION SET  MEMORY LOAD/STORE INSTRUCTIONS  INTEGER ARITHMETIC INSTRUCTIONS  LOGICAL AND SHIFT INSTRUCTIONS  CONTROL INSTRUCTIONS  CONTROL INSTRUCTIONS  MISCELLANEOUS INSTRUCTIONS  PRIVILEGED INSTRUCTIONS  MEMORY MANAGEMENT  Virtual Address Space  Virtual Address Space  Virtual Address Format  Physical Address Space  Address Translation  PROCESSOR STATE  EXCEPTION STACK FRAMES  Arithmetic Traps  Scalar Alignment Fault  Vector Alignment Fault  Vector Alignment Abort  BPT, BUGCHK, Vector Enable, And Privileged  Instruction Faults  FOB, Illegal Operand, And Reserved Opcode  Faults  Memory Management Faults  Machine Check  Stack Alignment Abort  Vector Exceptions  SCB Vectors  64-BIT MODE INTERNAL PROCESSOR REGISTERS | B-2<br>B-3<br>B-3<br>B-3<br>B-3<br>B-3<br>B-14<br>B-18<br>B-14<br>B-18<br>B-18<br>B-19<br>B-20<br>B-20<br>B-20<br>B-21<br>B-22<br>B-23<br>B-24<br>B-24<br>B-25<br>B-26<br>B-29<br>B-30 |  |  |  |  |  |

| INDEX    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        |  |  |  |  |  |

| FIGURES  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                        |  |  |  |  |  |

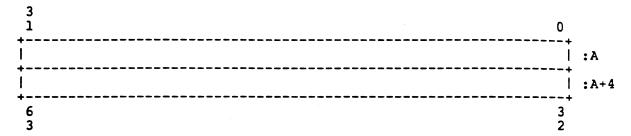

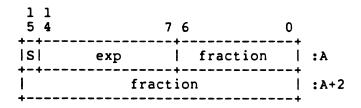

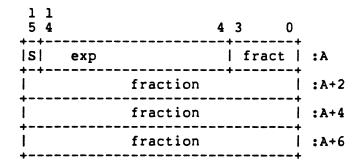

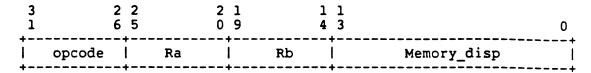

|          | 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>3-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Byte Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2-2<br>2-3<br>2-4<br>2-5<br>2-6                                                                                                                                                        |  |  |  |  |  |

| CONTENTS | Company Confidential                            |         |  |  |  |  |  |  |

|----------|-------------------------------------------------|---------|--|--|--|--|--|--|

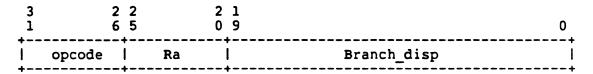

| 3-2      | Branch Instruction Format                       | 3-6     |  |  |  |  |  |  |

| 3-3      | Operate Instruction Format                      |         |  |  |  |  |  |  |

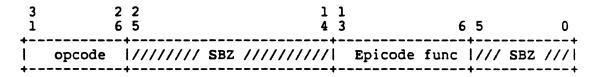

| 3-4      | Epicode Instruction Format                      | 3-8     |  |  |  |  |  |  |

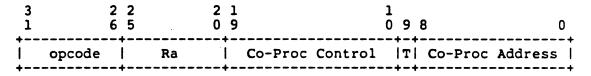

| 3-5      | Coprocessor Instruction Format                  | 3-9     |  |  |  |  |  |  |

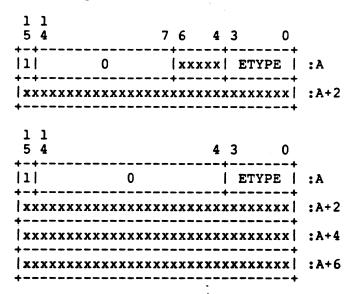

| 4-1      | F and G floating Exception Code Format          | 4-46    |  |  |  |  |  |  |

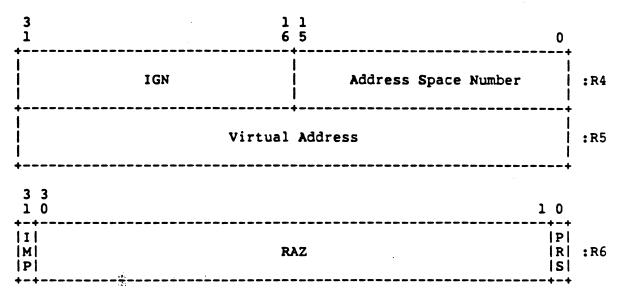

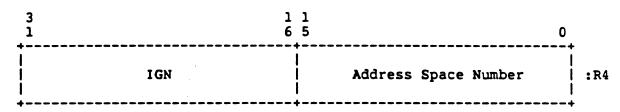

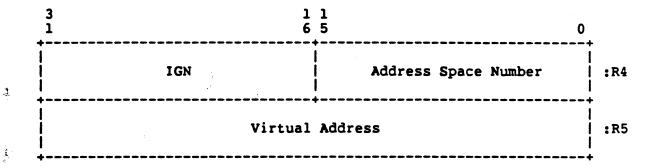

| 5-1      | Virtual Address Format                          |         |  |  |  |  |  |  |

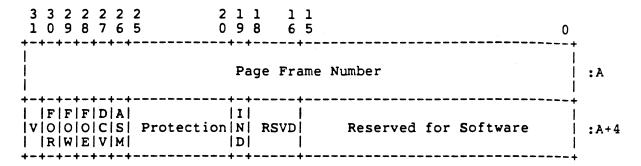

| 5-2      | Page Table Entry                                | 5-4     |  |  |  |  |  |  |

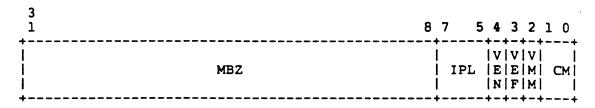

| 6-1      | Processor Status                                | 5-4     |  |  |  |  |  |  |

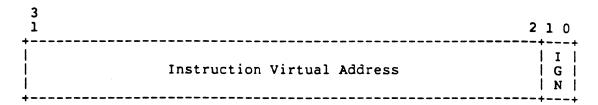

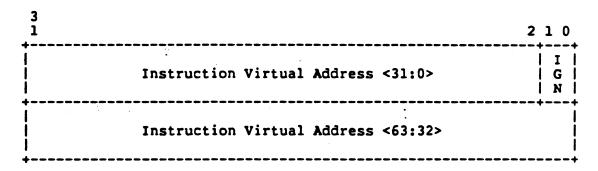

| 6-2      | Program Counter                                 | 6-5     |  |  |  |  |  |  |

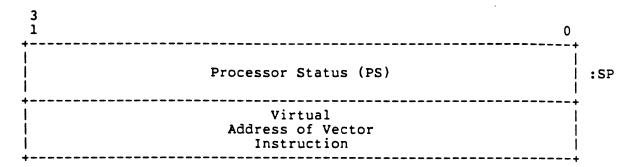

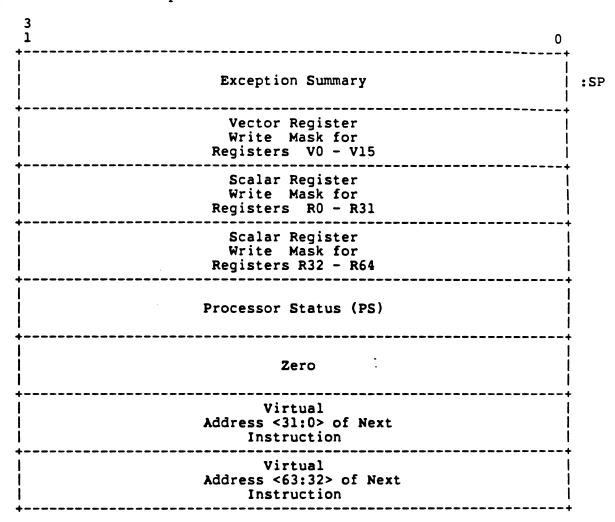

| 6-3      | Arithmetic Trap Exception Frame                 | 6-12    |  |  |  |  |  |  |

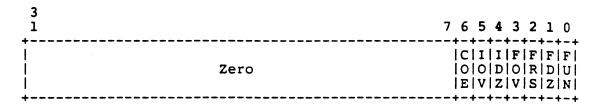

| 6-4      | Exception Summary                               | 6-14    |  |  |  |  |  |  |

| 6-5      | Exception Summary                               | . 6-14  |  |  |  |  |  |  |

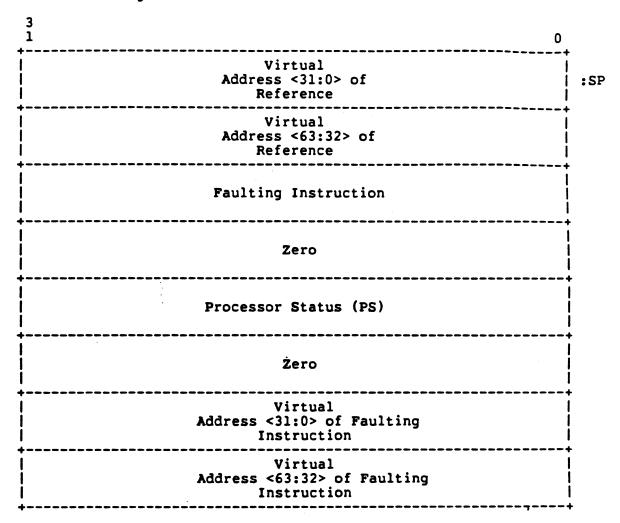

| 6-6      | Voctor Alignment About Exception Frame          | . 6-16  |  |  |  |  |  |  |

|          | Vector Alignment Abort Exception Frame          | . 6-1/  |  |  |  |  |  |  |

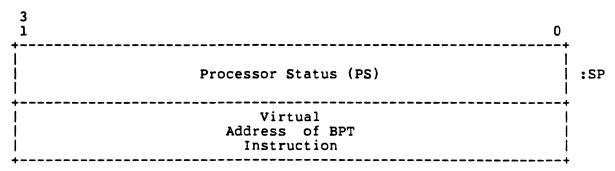

| 6-7      | Breakpoint Fault Exception Frame                |         |  |  |  |  |  |  |

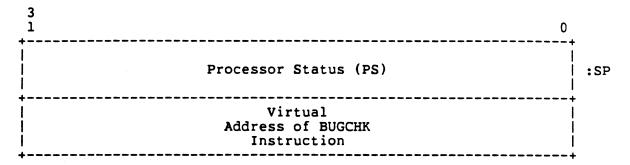

| 6-8      | Bug Check Fault Exception Frame                 |         |  |  |  |  |  |  |

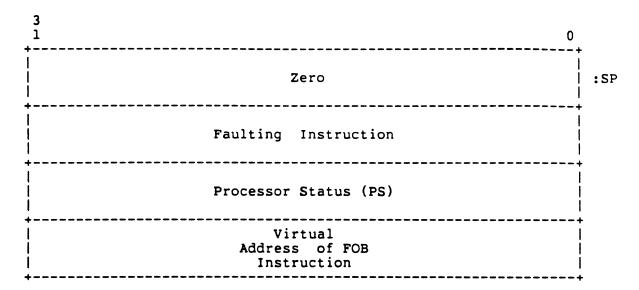

| 6-9      | Fault On Bit Fault Exception Frame              |         |  |  |  |  |  |  |

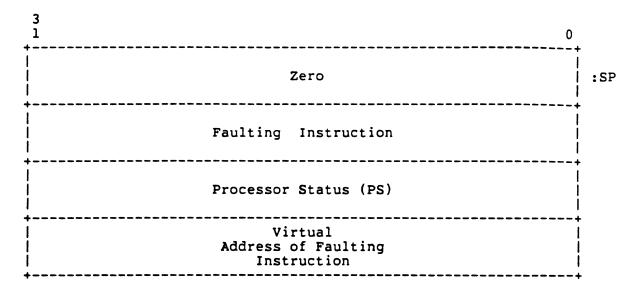

| 6-10     | Illegal Operand Fault Exception Frame           |         |  |  |  |  |  |  |

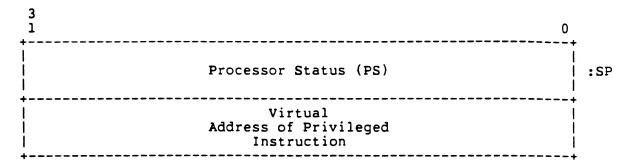

| 6-11     | Privileged Instruction Fault Exception Frame .  |         |  |  |  |  |  |  |

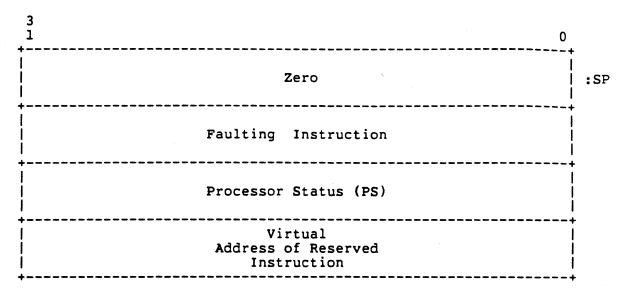

| 6-12     | Reserved Opcode Fault Exception Frame           | . 6-22  |  |  |  |  |  |  |

| 6-13     | Vector Enable Fault Exception Frame             |         |  |  |  |  |  |  |

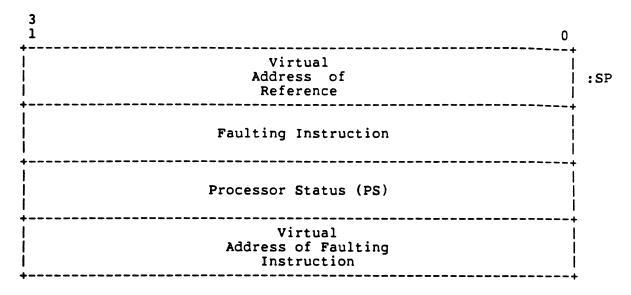

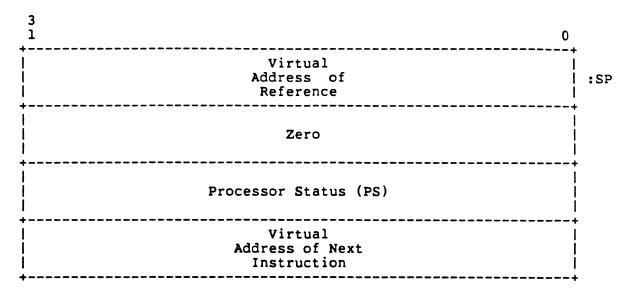

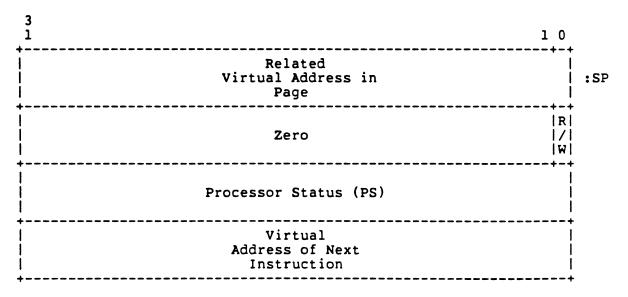

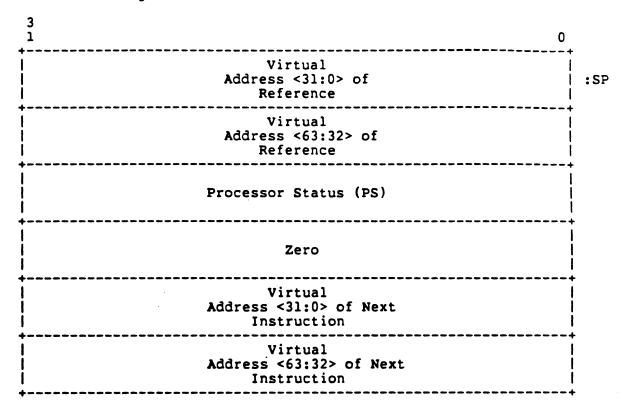

| 6-14     | Memory Management Fault Exception Frame         |         |  |  |  |  |  |  |

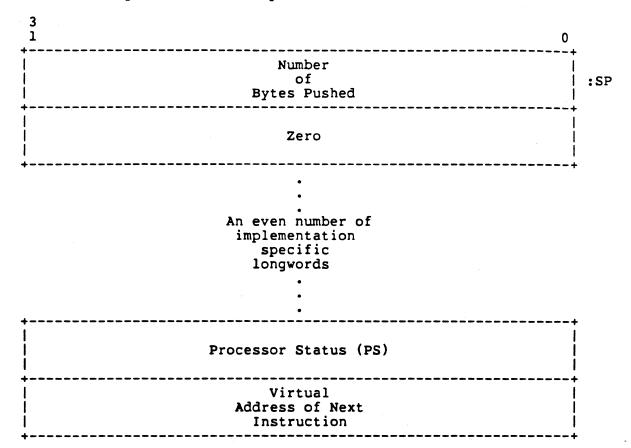

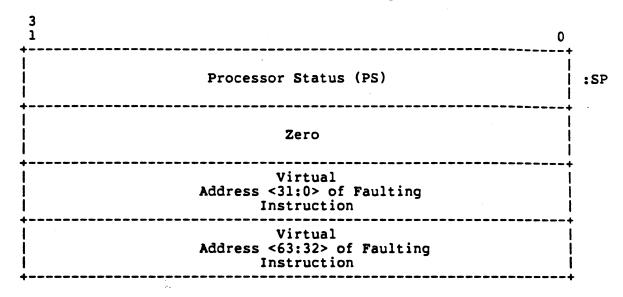

| 6-15     | Machine Check Abort Exception Frame             |         |  |  |  |  |  |  |

| 6-16     | Stack Alignment Abort Exception Frame           |         |  |  |  |  |  |  |

| 6-17     | Vector Exception Information Frame              | . 6-28  |  |  |  |  |  |  |

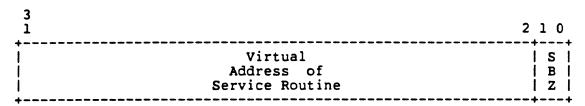

| 6-18     | System Control Block Vector                     | . 6-32  |  |  |  |  |  |  |

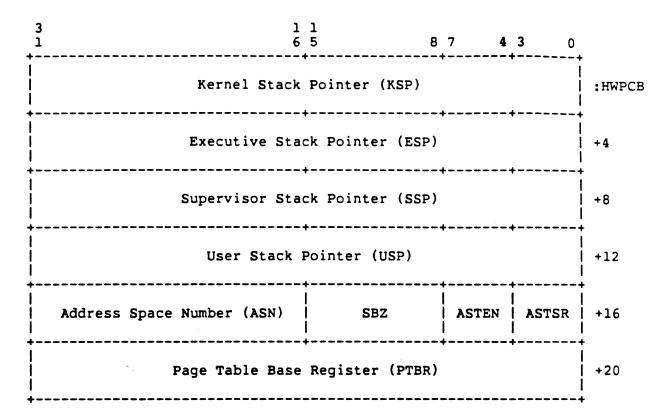

| 7-1      | Hardware Privileged Context Block               | 7-3     |  |  |  |  |  |  |

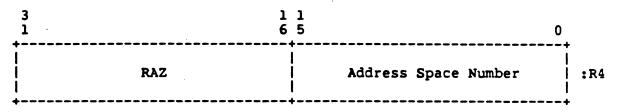

| 8-1      | Address Space Number Register (ASN)             | 8-3     |  |  |  |  |  |  |

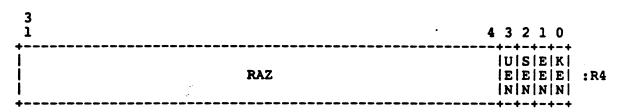

| 8-2      | AST Enable Register (ASTEN)                     | 8-4     |  |  |  |  |  |  |

| 8-3      | AST Request Register (ASTRR)                    | 8-5     |  |  |  |  |  |  |

| 8-4      | AST Summary Register (ASTSR)                    | 8-6     |  |  |  |  |  |  |

| 8-5      | Console Receive Control Status Register (CRCS)  | 8-7     |  |  |  |  |  |  |

| 8-6      | Console Receive Data Buffer Register (CRDB) .   | 8-8     |  |  |  |  |  |  |

| 8-7      | Console Transmit Control Status Register (CTCS) | . 8-9   |  |  |  |  |  |  |

| 8-8      | Console Transmit Data Buffer Register (CTDB) .  | . 8-10  |  |  |  |  |  |  |

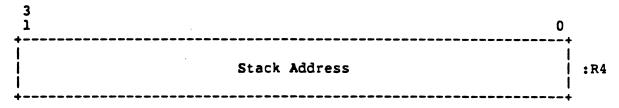

| 8-9      | Stack Pointer Registers (ESP, SSP, USP)         | . 8-11  |  |  |  |  |  |  |

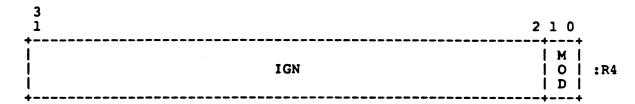

| 8-10     | Interval Clock Interrupt Enable Register (ICIE) | ) 8-12  |  |  |  |  |  |  |

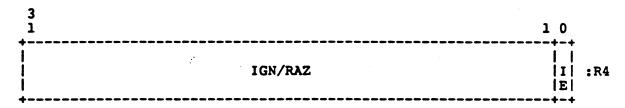

| 8-11     | Interprocessor Interrupt Enable Register (IPIE) | 8-13    |  |  |  |  |  |  |

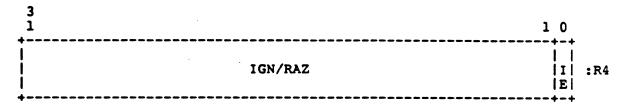

| 8-12     | Interprocessor Interrupt Request Register (IPII | R) 8-14 |  |  |  |  |  |  |

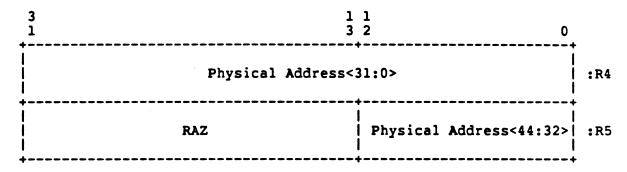

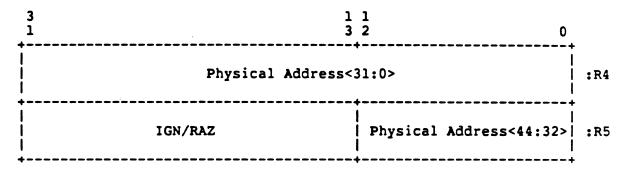

| 8-13     | Privileged Context Block Base Register (PCBB)   | . 8-15  |  |  |  |  |  |  |

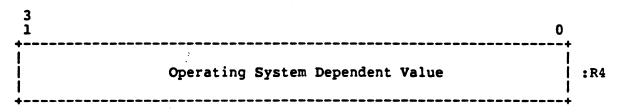

| 8-14     | Processor Base Register (PRBR)                  | . 8-16  |  |  |  |  |  |  |

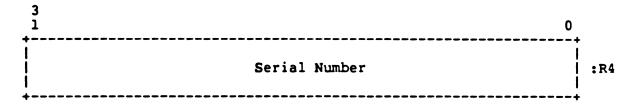

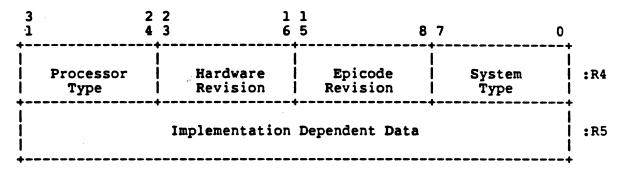

| 8-15     | Processor Serial Number Register (PRSN)         | . 8-17  |  |  |  |  |  |  |

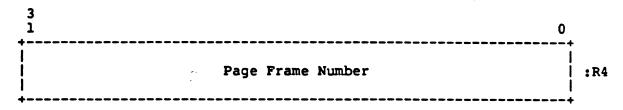

| 8-16     | Page Table Base Register (PTBR)                 | . 8-18  |  |  |  |  |  |  |

| 8-17     | System Control Block Base Register (SCBB)       | . 8-19  |  |  |  |  |  |  |

| 8-18     | System Identification Register (SID)            | . 8-20  |  |  |  |  |  |  |

| 8-19     | Software Interrupt Request Register (SIRR)      | 8-21    |  |  |  |  |  |  |

| 8-20     | Software Interrupt Summary Register (SISR)      |         |  |  |  |  |  |  |

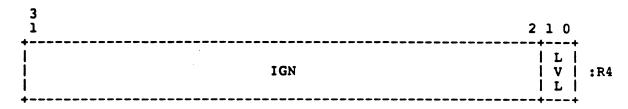

| 8-21     | Translation Buffer Check Register (TBCHK)       | 8-23    |  |  |  |  |  |  |

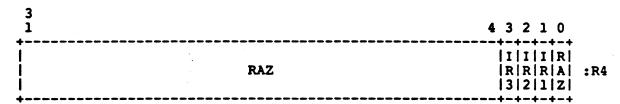

| 8-22     | Translation Buffer Invalidate by ASN Register   | . 0 20  |  |  |  |  |  |  |

| 0-22     |                                                 | . 8-25  |  |  |  |  |  |  |

| 8-23     | (TBIASN)                                        | . 6-25  |  |  |  |  |  |  |

| 0-23     |                                                 | . 8-26  |  |  |  |  |  |  |

| 0 04     | (TBIS)                                          |         |  |  |  |  |  |  |

| 8-24     | Time of Year Register (TOY)                     |         |  |  |  |  |  |  |

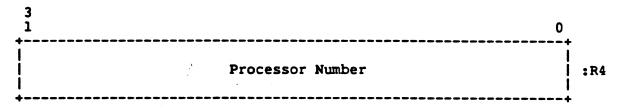

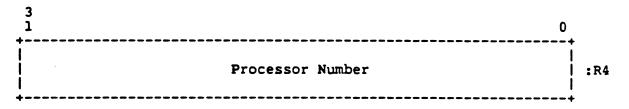

| 8-25     | Who-Am-I Register (WHAMI)                       | . 8-29  |  |  |  |  |  |  |

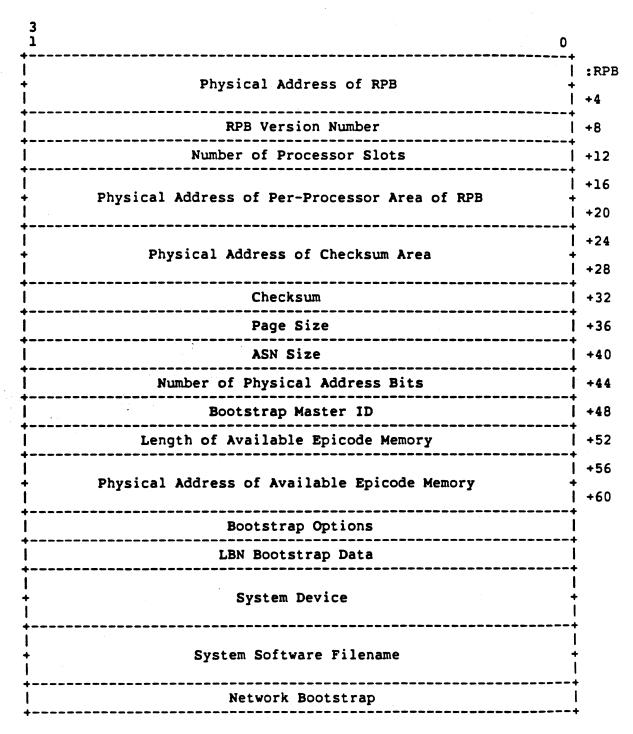

| 11-1     | Restart Parameter Block                         |         |  |  |  |  |  |  |

| 11-2     | Per-Processor Portion of RPB                    | . 11-5  |  |  |  |  |  |  |

11-5

| CONTENTS |                                                                      | Company Confidential                                                                                                                                                                                                                                                                                                            | Page xi                                                                          |

|----------|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

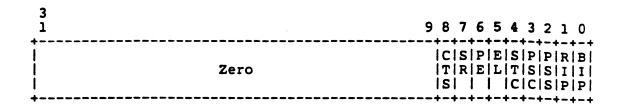

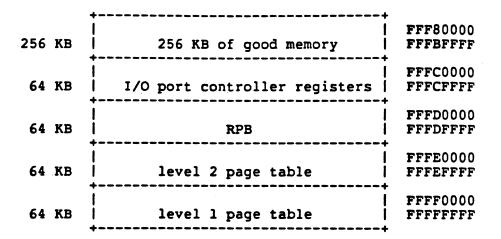

|          | 11-3<br>11-4<br>B-1<br>B-2<br>B-3<br>B-4<br>B-5<br>B-6<br>B-7        | State Longword Initial Virtual Memory Layout Virtual Address Format Processor Status Program Counter Arithmetic Trap Exception Frame Scalar Alignment Fault Exception Frame Vector Alignment Abort Exception Frame BPT, BUGCHK, and Privileged Instruction Fault Exception Frame FOB, Illegal Operand, and Reserved Opcode Faul | . 11-8<br>. B-18<br>. B-20<br>. B-20<br>. B-21<br>. B-22<br>. B-23               |

| TABLES   | B-9<br>B-10<br>B-11<br>B-12<br>B-13                                  | Exception Frame                                                                                                                                                                                                                                                                                                                 | <ul> <li>B-25</li> <li>B-26</li> <li>B-27</li> <li>B-28</li> <li>B-29</li> </ul> |

|          | 5-1<br>6-1<br>6-2<br>8-1<br>9-1<br>11-1<br>11-2<br>B-1<br>B-2<br>B-3 | PTE Protection Codes                                                                                                                                                                                                                                                                                                            | . 6-33<br>. 6-42<br>8-2<br>9-3<br>. 11-9<br>. 11-21<br>B-4                       |

|  | • |  |  |  |

|--|---|--|--|--|

|  |   |  |  |  |

|  |   |  |  |  |

|  |   |  |  |  |

#### **PREFACE**

Several competitors and new start-ups are introducing simplified architecture machines claiming superior price/performance over VAX. There are currently about a dozen such companies offering machines with vector processing (e.g., Convex, Scientific Computer Systems), symmetric multiprocessing (e.g., Flexible Computer, Sequent), and fine-grained parallel processing (e.g., Alliant) capabilities.

These competitors are mostly targeting the high end of the VAX market, which is our most profitable product space. However, we are also receiving increasing pressure at the low end of our product family where simplified architectures offer cheaper and faster custom implementations than VAX.

Several advanced development and research projects within DIGITAL, and projects elsewhere in the computer industry, have produced results substantiating our competitor's claims and questioning the viability of the VAX architecture to sustain DIGITAL through the 1990's.

In response to this challenge, a strategic effort has been initiated within the company to define a new architecture that will complement our current VAX/VMS and VAX/ULTRIX offerings and provide DIGITAL with a competitive architecture through the 1990's and beyond.

The following summarizes the assumptions, constraints, goals, and non-goals that have been set for the architecture.

# Assumptions:

- 1. Simplified architectures show promise for reducing complexity while improving cost/performance and making higher absolute performance possible when compared with VAX.

- Vector processing, multiprocessing, and parallel processing are well enough understood to make them a science (rather than a black art), and therefore, are essential to attaining a competitive architecture.

- 3. Neither DIGITAL nor its customers can afford the resources necessary to support an open architecture philosophy, but rather must be able to leverage software investments across an entire family of compatible products. This implies that any new architecture must be rigid and not allow the instruction set or privileged architecture to be changed from implementation to implementation.

- 4. The design work that must be performed is similar to the VAX architectural effort. An architectural document, at the same level of detail as produced for VAX, must be produced to guide implementations of the new architecture. It is required that this document receive wide review within the

technical community and the company in general. When completed and accepted, the architecture will be placed under ECO control and managed by a central architecture group.

- 5. The architecture will be compatibly extended over time, and will allow subsets. Each extension will be subsettable and become a permanent part of the architecture which all implementations must adhere to. Features of the architecture that are subsetted in a particular implementation must be emulated transparently in software.

- 6. VAX compatibility is very important, especially with respect to the way memory is addressed and data is stored. This can be achieved with a combination of software and hardware rather than with just a hardware structure itself.