# TU80 Tape Subsystem

**Technical Manual**

# TU80 Tape Subsystem

**Technical Manual**

Prepared by Educational Services of Digital Equipment Corporation lst Edition, March 1983

Copyright © 1983 by Digital Equipment Corporation. All Rights Reserved. Printed in U.S.A.

The reproduction of this material, in part or whole, is strictly prohibited. For copy information, contact the Educational Services Department, Digital Equipment Corporation, Maynard, Massachusetts Ø1754.

The information in this document is subject to change without notice. Digital Equipment Corporation assumes no responsibility for any errors that may appear in this document.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts.

| Digital log | o DECwriter | P/OS         | UNIBUS         |

|-------------|-------------|--------------|----------------|

| DEC         | DIGITAL     | Professional | VAX            |

| DECmate     | LA          | Rainbow      | VMS            |

| DECnet      | MASSBUS     | RSTS         | VT             |

| DECUS       | PDP         | RSX          | Work Processor |

### PREFACE

This manual contains information pertinent to the installation, operation, and maintenance of the TU80 Tape Subsystem. The subsystem is defined as the TU80 Tape Transport, I/O Interface, and the M7454 UNIBUS Adapter Module, and the 874 Power Controller.

Related documents are listed in Appendix C of this manual.

# RECORD OF REVISIONS

# REVISION COMMENTS

A Manual Released. This manual is current with series (2-16-83) code 10.

| PARA.                                               | TITLE                                                                                                                                                                                                                                                        | PAGE                                                                    |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

|                                                     | Section 1 - GENERAL DESCRIPTION                                                                                                                                                                                                                              |                                                                         |

| 1.1 1.2 1.2.1 1.3 1.3.1 1.3.2 1.3.3 1.4 1.4.1 1.4.2 | GENERAL<br>FUNCTIONAL DESCRIPTION<br>TU80 UNIBUS Adapter Module (M7454)<br>PHYSICAL DESCRIPTION<br>Tape Deck - Top<br>Tape Deck - Bottom<br>Control Panel (Front Door)<br>EQUIPMENT CONFIGURATION<br>Equipment ID Plate/Serial Tag<br>Field Change Order Log | 1-1<br>1-8<br>1-9<br>1-9<br>1-9<br>1-12<br>1-14<br>1-14<br>1-14<br>1-15 |

# Section 2 - INSIALLATION AND CHECKOUT

| 2.1<br>2.1.1 | SITE REQUIREMENTS<br>Space Requirements | 2-1<br>2-1 |

|--------------|-----------------------------------------|------------|

| 2.1.2        | Power Requirements                      | 2-1        |

| 2.1.3        | Environmental Requirements              | 2-1        |

| 2.2          | ACCEPTANCE OF DELIVERY                  | 2-1        |

| 2.3          | UNPACKAGING AND INSPECTION              | 2-3        |

| 2.3.1        | Floor Loading and Routing               | 2-3        |

| 2.3.2        | Unpackaging and Removal From Pallet     | 2-3        |

| 2.3.3        | Inspection                              | 2-6        |

| 2.4          | OPERATION PREPARATIONS                  | 2-6        |

| 2.4.1        | Mechanical Installation                 | 2-6        |

| 2.4.2        | Grounding                               | 2-12       |

| 2.4.3        |                                         | 2-13       |

| 2.5          | UNIBUS ADAPTER MODULE INSTALLATION/     |            |

|              | REPLACEMENT AND INTERFACE CABLING       | 2-14       |

| 2.5.1        | M7454 Preparation and Installation      | 2-14       |

| 2.5.2        | CPU Internal Cabling                    | 2-20       |

| 2.5.3        | TU80 External Cabling                   | 2-22       |

| 2.6          | TU80 Acceptance Diagnostic Tests        | 2-24       |

| 2.6.1        | TU80 Acceptance Test Listing            | 2-24       |

| 2.6.2        | TU80 Acceptance Test Procedure          | 2-25       |

|              |                                         |            |

# Section 3 - OPERATION

| 3.1   | GENERAL                     | 3-1          |

|-------|-----------------------------|--------------|

| 3.2   | CONTROL PANEL               | 3-1          |

| 3.3   | OPERATING PROCEDURE         | 3-4          |

| 3.3.1 | Inserting Write Enable Ring | 3-4          |

| 3.3.2 | Tape Threading and Loading  | 3-5          |

| 3.3.3 | Tape Unloading              | 3 <b>-</b> 7 |

| 3.4   | OPERATOR CORRECTIVE ACTIONS | 3-8          |

# TABLE OF CONTENTS (Cont'd)

PARA. TITLE

# PAGE

## Section 4 - THEORY

| 4.1    | GENERAL DESCRIPTION                          | 4-1  |

|--------|----------------------------------------------|------|

| 4.2    | PHYSICAL DESCRIPTION                         | 4-1  |

| 4.2.1  | Power Supply                                 | 4-3  |

| 4.2.2  | Tension/Speed Control                        | 4-3  |

| 4.2.3  | Magnetic Head                                | 4-3  |

| 4.2.4  | Format Control                               | 4-4  |

| 4.2.5  | Interface                                    | 4-4  |

| 4.3    | POWER SUPPLY                                 | 4-4  |

| 4.3.1  | General Description                          | 4-4  |

| 4.3.2  | Physical Description                         | 4-5  |

| 4.3.3  | Power Supply Functional Description          | 4-8  |

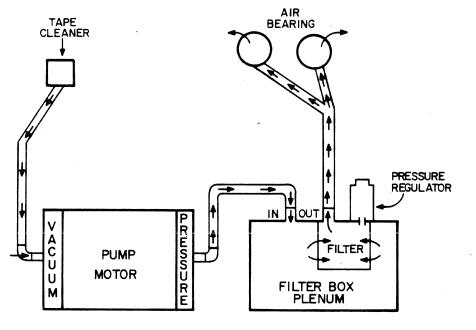

| 4.4    | PNEUMATIC SYSTEM                             | 4-16 |

| 4.4.1  | Functional Description                       | 4-16 |

| 4.4.2  | Pneumatic System Operational Description     | 4-17 |

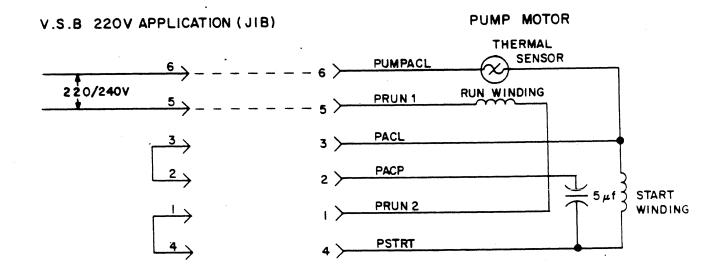

| 4.5    | READ/WRITE/SERVO MODULE FUNCTIONAL           | 4-19 |

|        | DESCRIPTION                                  |      |

| 4.5.1  | Introduction                                 | 4-19 |

| 4.5.2  | Microprocessor                               | 4-19 |

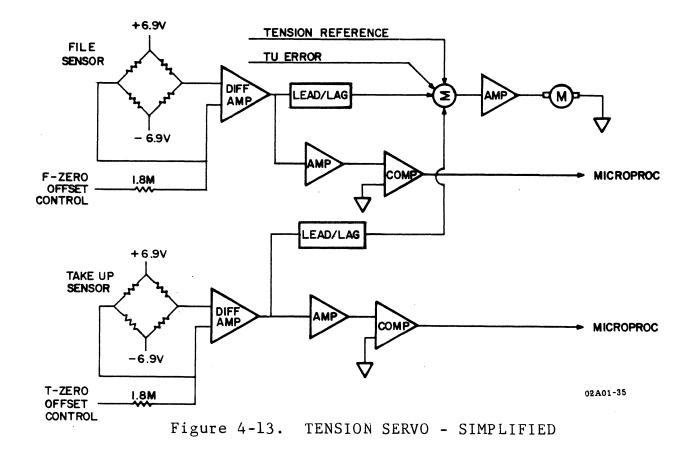

| 4.5.3  | Tension Servo                                | 4-23 |

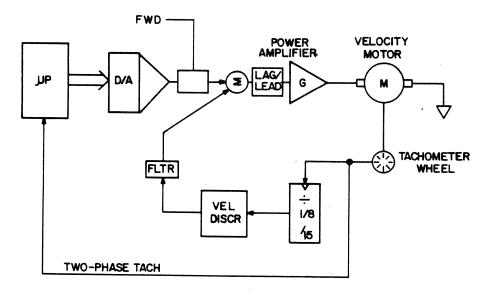

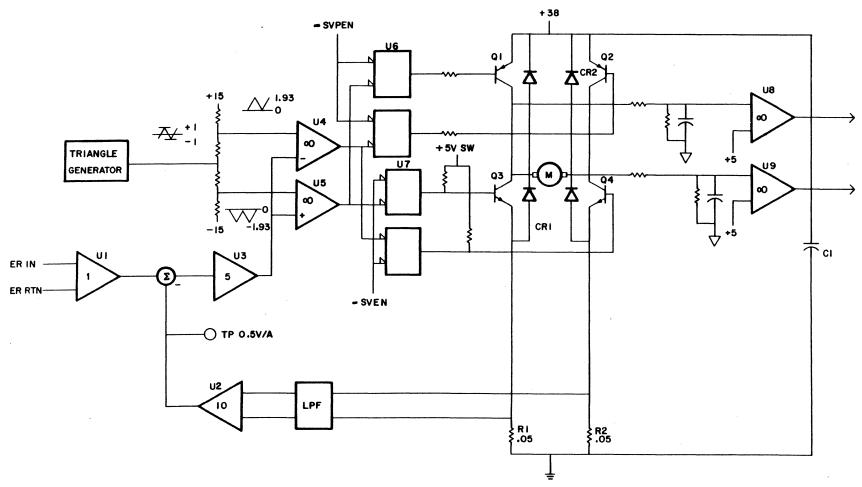

| 4.5.4  | Velocity Servo                               | 4-24 |

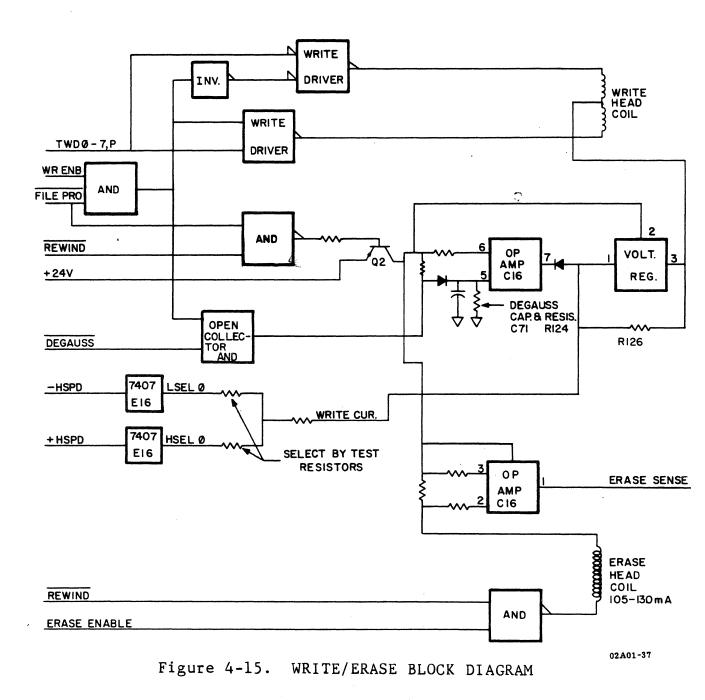

| 4.5.5  | Write Circuits                               | 4-26 |

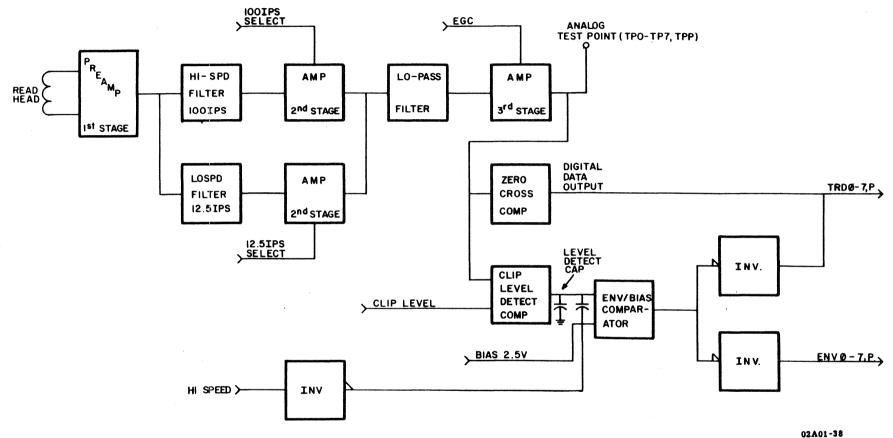

| 4.5.6  | Read Circuits                                | 4-29 |

| 4.6    | FORMATTER/CONTROL MODULE FUNCTIONAL          | 4-33 |

|        | DESCRIPTION                                  |      |

| 4.6.1  | Microprocessor                               | 4-33 |

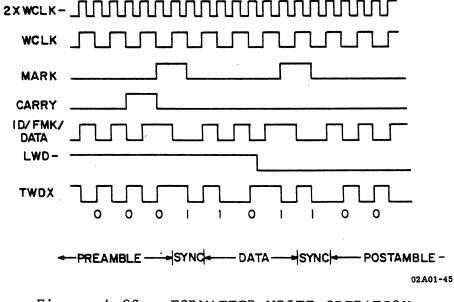

| 4.6.2  | Write Circuits                               | 4-38 |

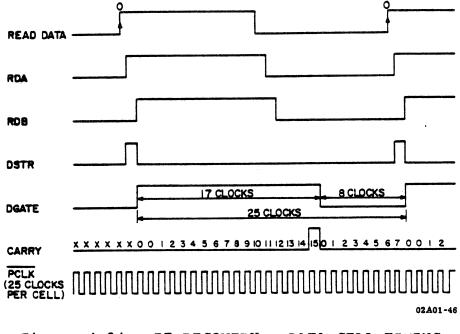

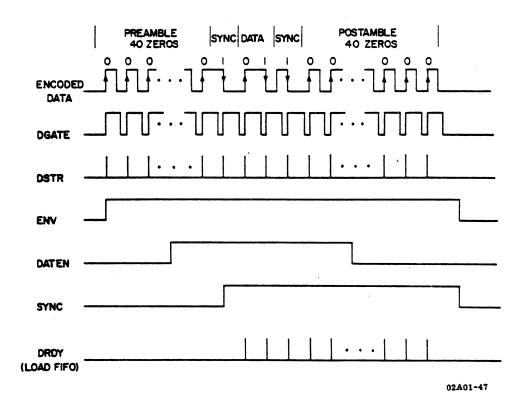

| 4.6.3  | Read Circuits                                | 4-39 |

| 4.7    | READ AMPLIFIER MODULE FUNCTIONAL DESCRIPTION | 4-41 |

| 4.8    | HEAD ASSEMBLY OPERATION                      | 4-45 |

| 4.8.1  | Recording Techniques and Formats             | 4-45 |

| 4.9    | TU80/TRANSPORT INTERFACE                     | 4-49 |

| 4.9.1  | Electrical Interface                         | 4-49 |

| 4.9.2  | Mechanical Interface                         | 4-49 |

| 4.9.3  | Formatter Interface Description              | 4-52 |

| 4.9.4  | Status and Sense Information                 | 4-55 |

| 4.9.5  | Signal Description                           | 4-63 |

| 4.10   | SYSTEM AND TIMING CONSIDERATIONS             | 4-68 |

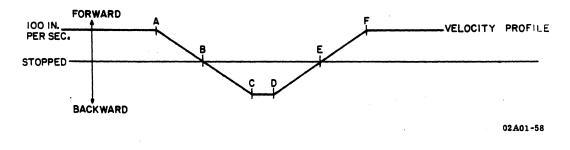

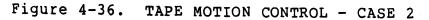

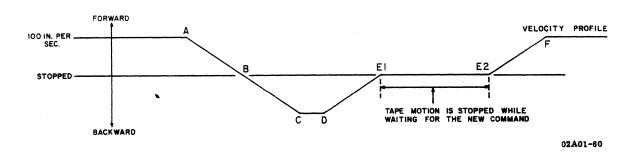

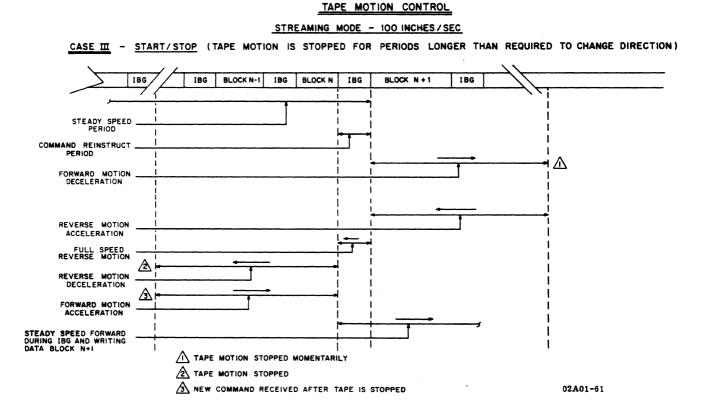

| 4.10.1 | Motion Characteristics                       | 4-68 |

| 4.10.2 | Command Classification                       | 4-78 |

# Section 5 - MAINTENANCE

| 5.1   | GENERAL                           | 5-1    |

|-------|-----------------------------------|--------|

| 5.2   | ACCESS TO COMPONENTS              | 5-1    |

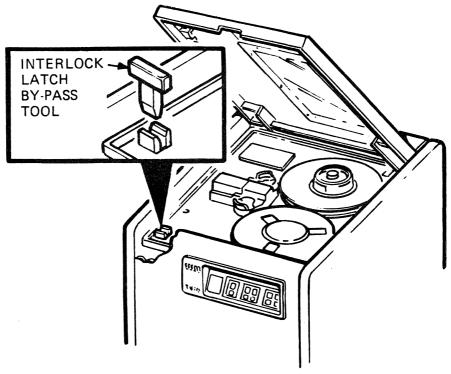

| 5.2.1 | Top Cover Interlock Switch Bypass | 5-2A/B |

# TABLE OF CONTENTS (Cont'd)

| PARA. | TITLE                                                   | PAGE |

|-------|---------------------------------------------------------|------|

|       | Section 5 (Cont'd)                                      |      |

| 5.3   | REMOVAL/REPLACEMENT PROCEDURES (See Table on page 5-3.) | 5-3  |

| 5.4   | TU80 DIAGNOSTICS AND TROUBLESHOOTING                    | 5-54 |

| 5.4.1 | General                                                 | 5-54 |

| 5.4.2 | Resident Diagnostics                                    | 5-54 |

| 5.4.3 | PDP-11 Based Diagnostics                                | 5-61 |

| 5.4.4 | VAX-Based Diagnostic                                    | 5-64 |

Appendix A - M7454 UNIBUS ADAPTER MODULE

| A.1.0    | GENERAL                                    | A-1  |

|----------|--------------------------------------------|------|

| A.1.1    | SYSTEM CONFIGURATION                       | A-1  |

| A.1.2    | M7454 MODULE PHYSICAL DESCRIPTION          | A-1  |

| A.2.0    | PHYSICAL INTERFACE                         | A-3  |

| A.3.0    | SUBSYSTEM FUNCTIONAL DESCRIPTION           | A-7  |

| A.3.1    | PACKET PROTOCOL                            | A-7  |

| A.3.2    | UNIBUS REGISTERS                           | A-9  |

| A.3.3    | TU80 SUBSYSTEM OPERATION                   | A-11 |

| Appendix | B - TAPE TRANSPORT CONFIGURATION SELECTION | B-1  |

| Appendix | С - | APPLICABLE | DOCUMENTATION | C | ;-1 |  |

|----------|-----|------------|---------------|---|-----|--|

|----------|-----|------------|---------------|---|-----|--|

LIST OF ILLUSTRATIONS

| FIGURE                                                                                                                                        | TITLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PAGE                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5                                                                                                               | TU80 Tape Subsystem<br>TU80 Tape Subsystem Block Diagram<br>Tape Deck Component Locations, Top View<br>Tape Deck Component Locations, Rear View<br>Equipment Identification Plate                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1-3<br>1-5<br>1-10<br>1-13<br>1-14                                                                                                                             |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11<br>2-12<br>2-13<br>2-14<br>2-15                                   | <pre>TU80 Space Requirements<br/>Unpacking The TU8<br/>Removing The TU80 From Shipping Pallet<br/>Cabinet Leveler Feet Assembly and Extension<br/>Stabilizer<br/>Leveler Feet Adjustments<br/>Cabinet Assembly<br/>Rear Stabilizer Installation<br/>874 Power Controller<br/>Interface Cabling<br/>Plug-to-Plug Interface Cable Connections<br/>DIP Switch On M7454 Module<br/>DIP Switch Setting In A Single TU80<br/>Configuration<br/>I/O Cabling Flowchart<br/>I/O Cable Installation<br/>Tape Deck In Maintenance Position (External</pre>                                                                   | 2-2<br>2-4<br>2-5<br>2-7<br>2-9<br>2-10<br>2-11<br>2-13<br>2-15<br>2-15<br>2-15<br>2-16<br>2-17<br>2-20<br>2-21                                                |

| 3-1<br>3-2                                                                                                                                    | I/O Cabling)<br>Control Panel<br>Write Enable Ring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2-23<br>3-1<br>3-5                                                                                                                                             |

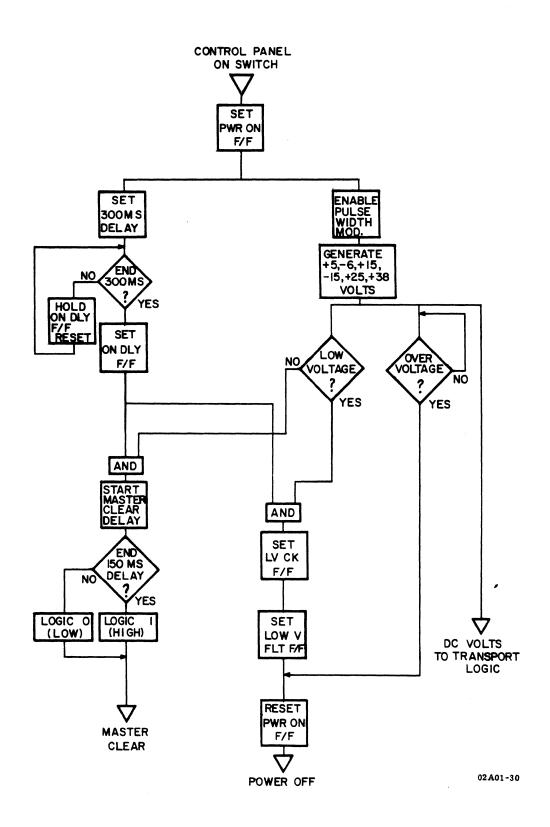

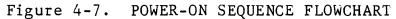

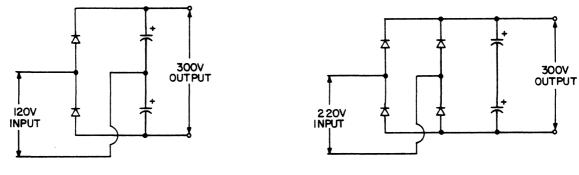

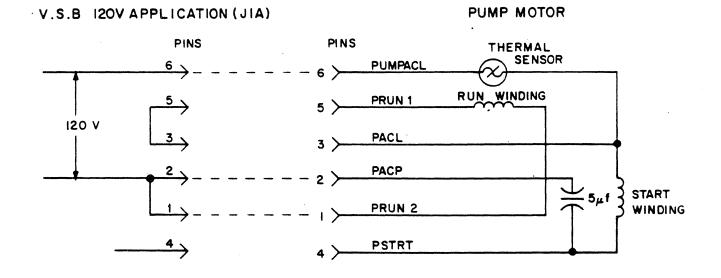

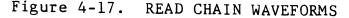

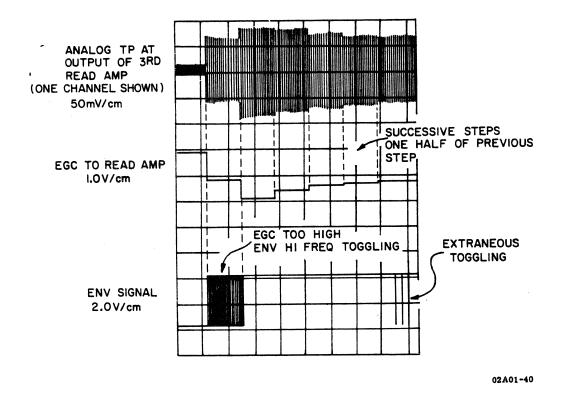

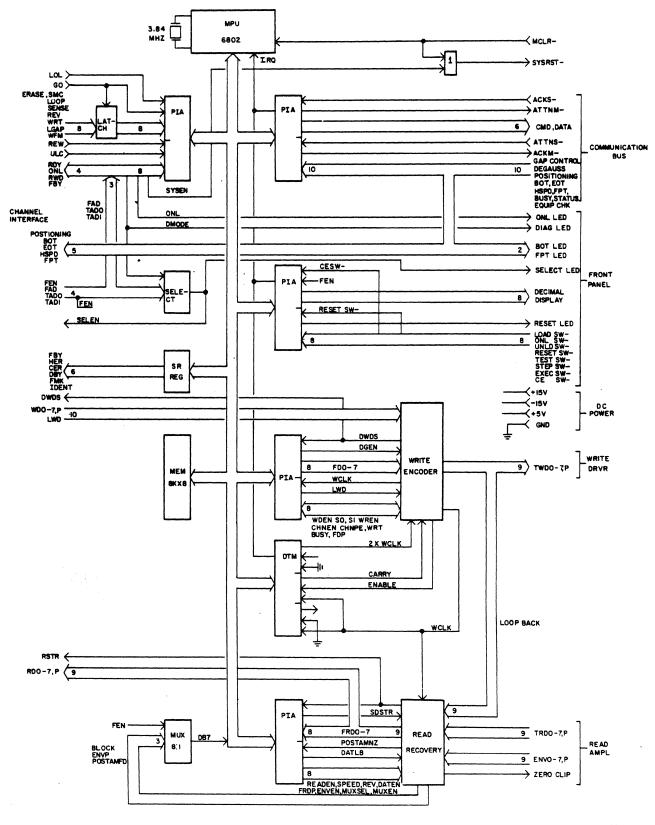

| 3-3 $4-1$ $4-2$ $4-3$ $4-4$ $4-5$ $4-6$ $4-7$ $4-8$ $4-9$ $4-10$ $4-11$ $4-12$ $4-13$ $4-14$ $4-15$ $4-14$ $4-15$ $4-16$ $4-17$ $4-18$ $4-19$ | Tape Path<br>TU80 Functional Block Diagram<br>Major Power Supply Components<br>Power Supply Block Diagram<br>Voltage Select PC Board<br>Cooling Fan Wiring<br>Stand-By Voltage Generation<br>Power-On Sequence Flowchart<br>High Voltage Generation<br>Switching Converter Circuit<br>Vacuum and Pressure Distribution<br>Pneumatic Pump Wiring<br>Read/Write/Servo Module Block Diagram<br>Tension Servo - Simplified<br>Velocity Servo - Simplified<br>Write/Erase Block Diagram<br>Read Circuits Block Diagram<br>Read Chain Waveforms<br>Electronic Gain Control Waveforms<br>Formatter/Control Block Diagram | 3-6<br>4-2<br>4-5<br>4-7<br>4-8<br>4-9<br>4-10<br>4-11<br>4-13<br>4-14<br>4-13<br>4-14<br>4-16<br>4-23<br>4-23<br>4-25<br>4-27<br>4-28<br>4-30<br>4-32<br>4-34 |

LIST OF ILLUSTRATIONS (Cont'd)

| FIGURE | TITLE                                                       | PAGE           |

|--------|-------------------------------------------------------------|----------------|

| 4-20   | PIA Communication Protocol                                  | 4-35           |

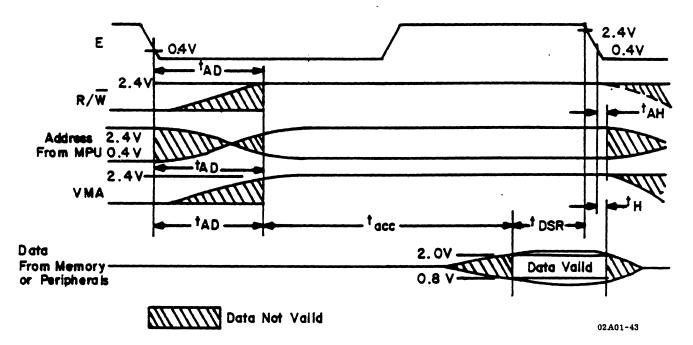

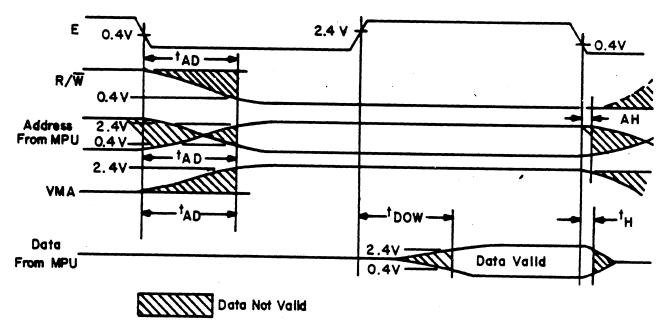

| 4-21   | Processor Read Operation                                    | 4-37           |

| 4-22   | Processor Write Operation                                   | 4-37           |

| 4-23   |                                                             | 4-38           |

| 4-24   | Formatter Write Operation                                   | 4-40           |

|        | PE Recovery - Data Cell Timing                              |                |

| 4-25   | PE Read Recovery Timing                                     | 4-40           |

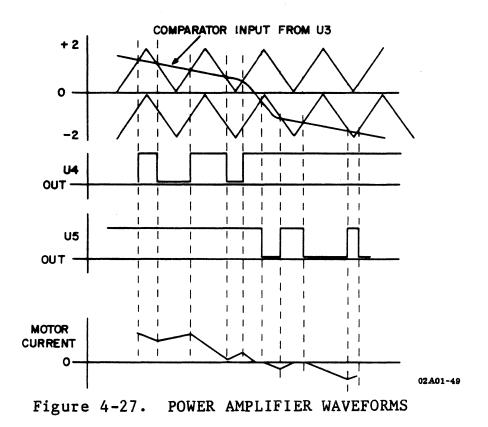

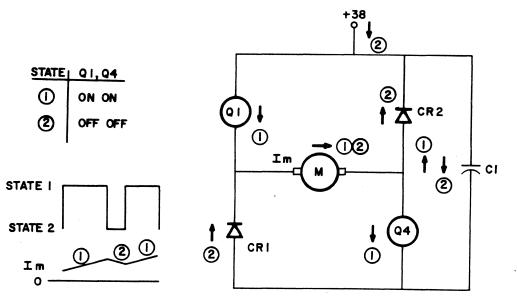

| 4-26   | Power Amplifier Block Diagram                               | 4-42           |

| 4-27   | Power Amplifier Waveforms                                   | 4-43           |

| 4-28   | H-Bridge Switching                                          | 4-43           |

| 4-29   | Switched +5 Volts                                           | 4-44           |

| 4-30   | PE Modulation Recording                                     | 4-46           |

| 4-31   | Phase Encoded Tape Format                                   | 4-48           |

| 4-32   | Interface Configuration                                     | 4-49           |

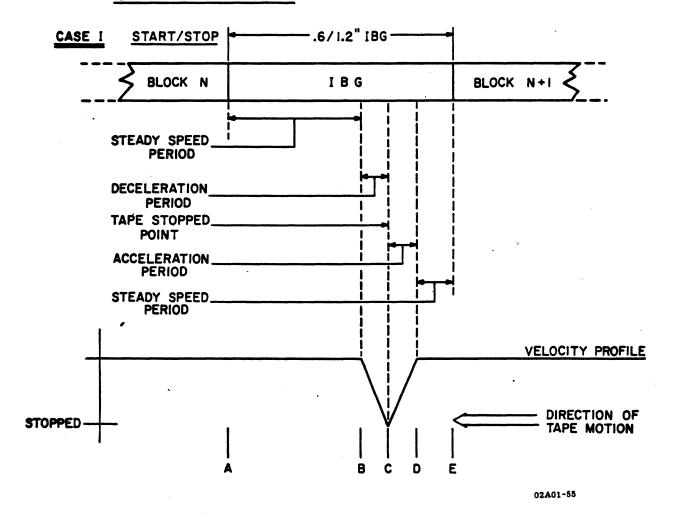

| 4-33   | Start/Stop Tape Motion Control                              | 4-71           |

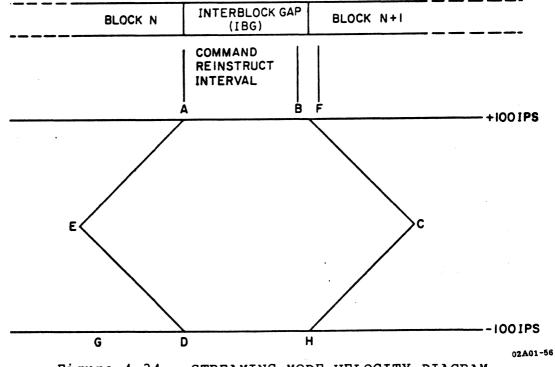

| 4-34   | Streaming Mode Velocity Diagram                             | 4-73           |

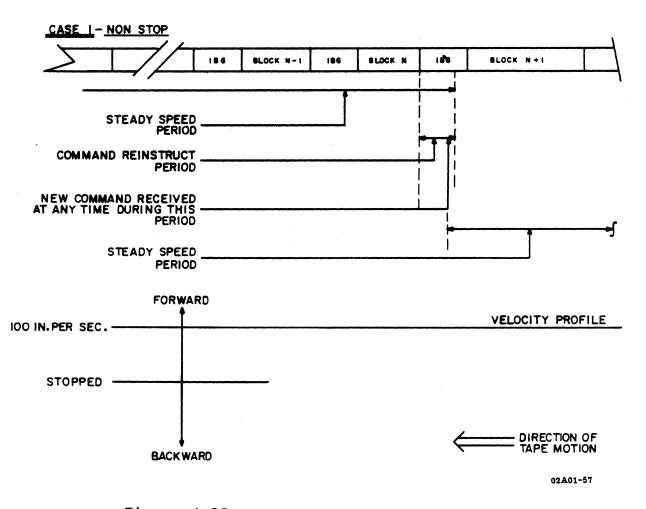

| 4-35   | Tape Motion Control - Case 1                                | 4-74           |

| 4-36   | Tape Motion Control - Case 2                                | 4-74           |

| 4-37   | Tape Motion Control - Case 2 (Cont'd)                       | 4-75           |

| 4-38   | Tape Motion Control - Case 3                                | 4-76           |

| 4-39   |                                                             |                |

|        | Tape Motion Control - Case 3 (Cont'd)                       | 4-77           |

| 4-40   | Start/Stop - New Command Received During                    | ( 70           |

| / / ]  | Reinstruct                                                  | 4-79           |

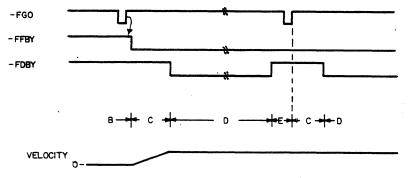

| 4-41   | Start/Stop - No New Command Received                        | 4-80           |

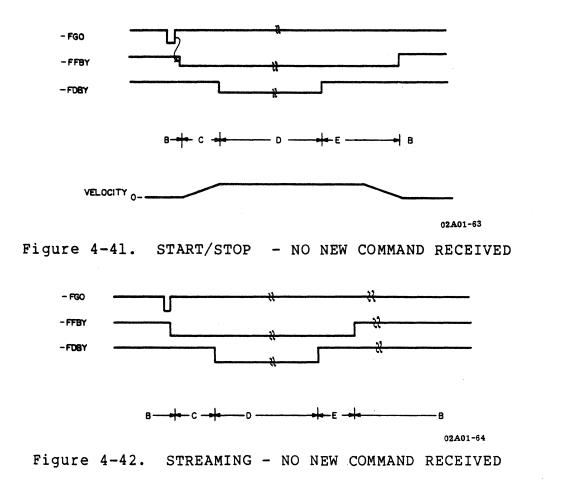

| 4-42   | Streaming - No New Command Received                         | 4-80           |

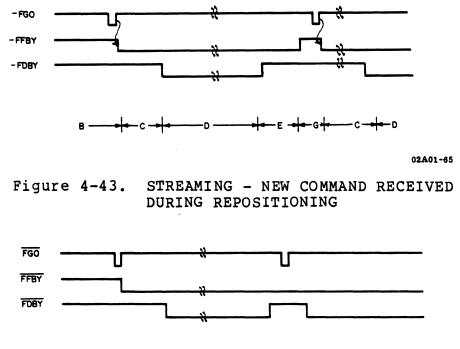

| 4-43   | Streaming - No New Command Received During<br>Repositioning | 4-81           |

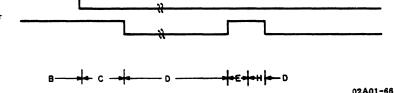

| 4-44   | Streaming - No New Command Received During                  |                |

|        | Reinstruct                                                  | 4-81           |

|        |                                                             |                |

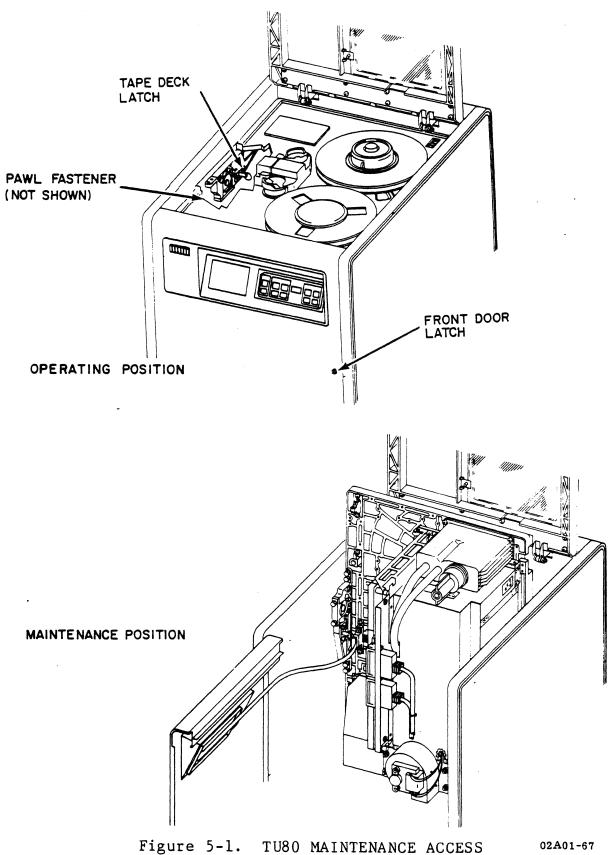

| 5-1    | TU80 Maintenance Access                                     | 5 <b>-</b> 2   |

| 5-1A   | Cover Interlock Bypass                                      | 5-2A/          |

|        |                                                             | 5 <b>-</b> 2 B |

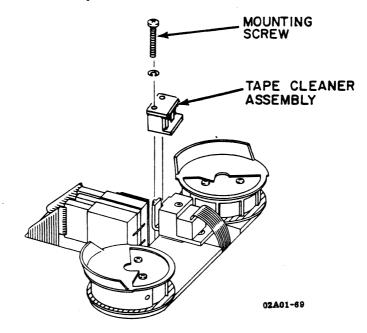

| 5-2    | Tape Cleaner                                                | 5-5            |

| 5-3    | Top Cover Interlock Switch                                  | 5-7            |

| 5-4    | File Protect Sensor Alignment                               | 5-8            |

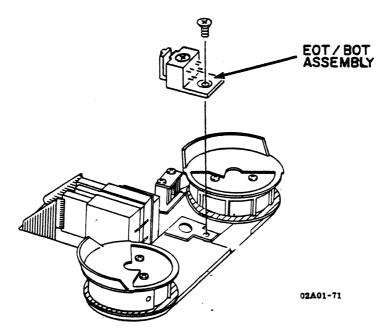

| 5-5    | EOT/BOT Sensor                                              | 5-10           |

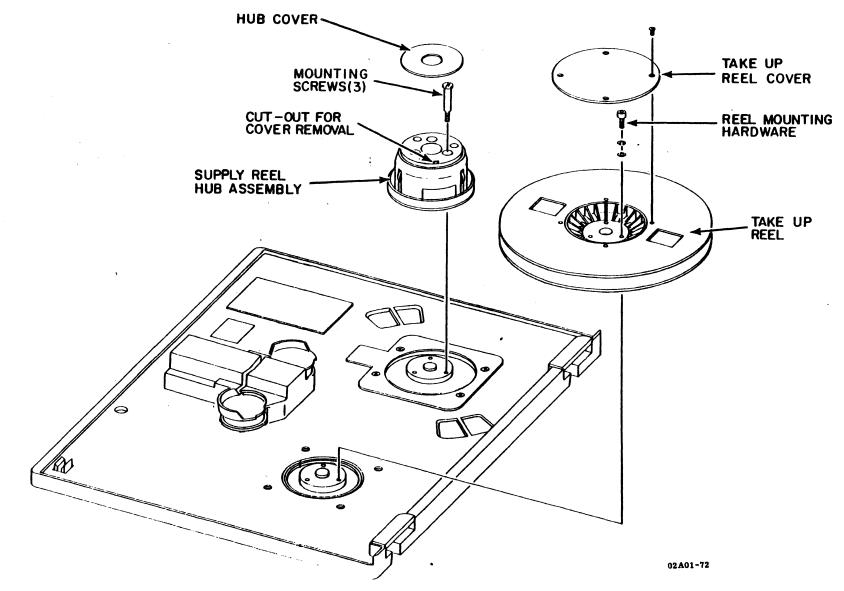

| 5-6    | Take-Up Reel/Supply Hub Assemblies                          | 5-13           |

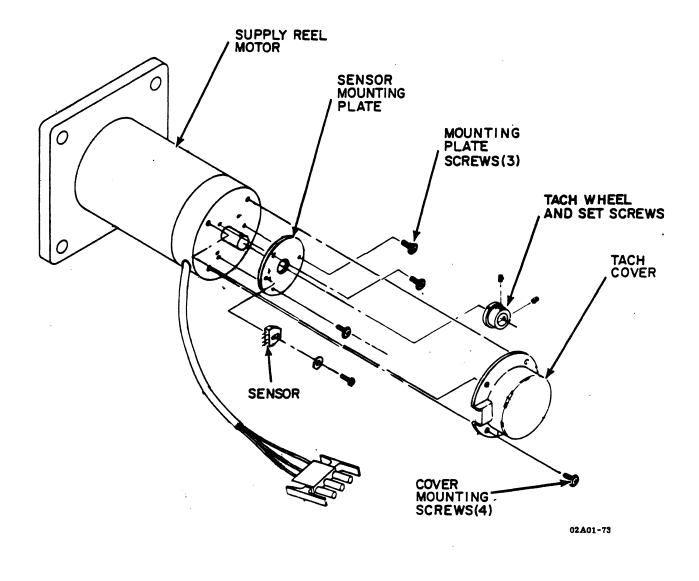

| 5-7    | Supply Motor Assembly                                       | 5-17           |

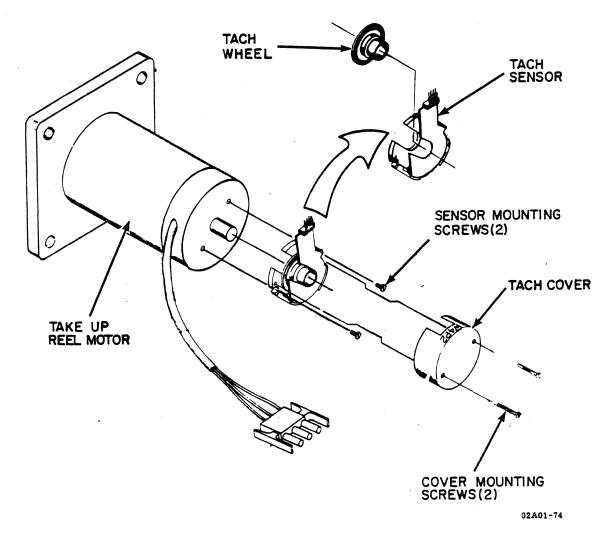

| 5-8    | Take-Up Reel Disassembly                                    | 5-18           |

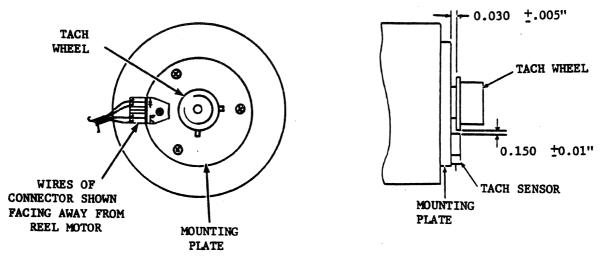

| 5-9    | Tach Wheel/Sensor Alignment                                 | 5-20           |

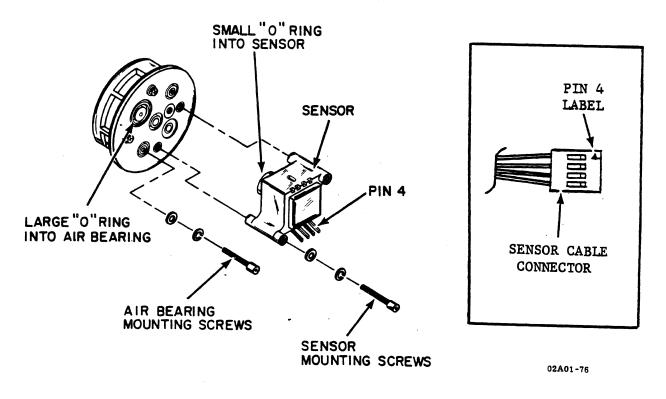

| 5-10   | Air Bearing Sensors                                         | 5-23           |

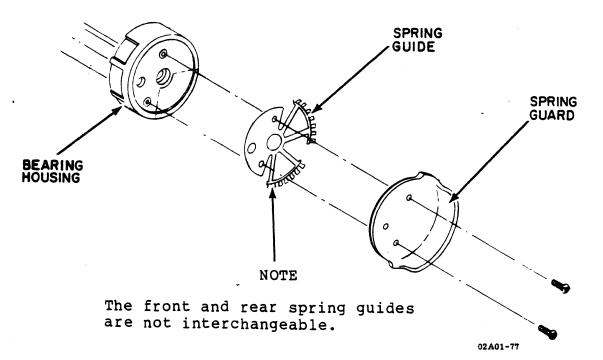

| 5-11   | Air Bearing Spring Guide                                    | 5-24           |

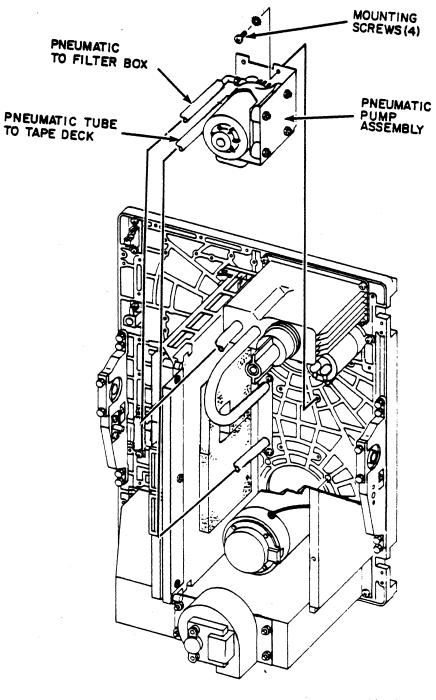

| 5-12   | Proumatic Dump Accombly                                     |                |

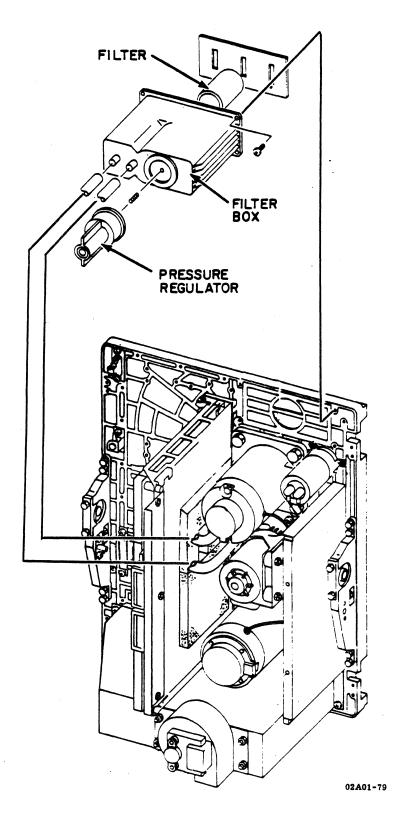

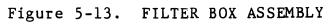

| 5-13   | Pneumatic Pump Assembly<br>Filter Box Assembly              | 5-27           |

|        | Filter Box Assembly                                         | 5-29           |

| 5 - 14 | Magnetic Head Assembly                                      | 5-31           |

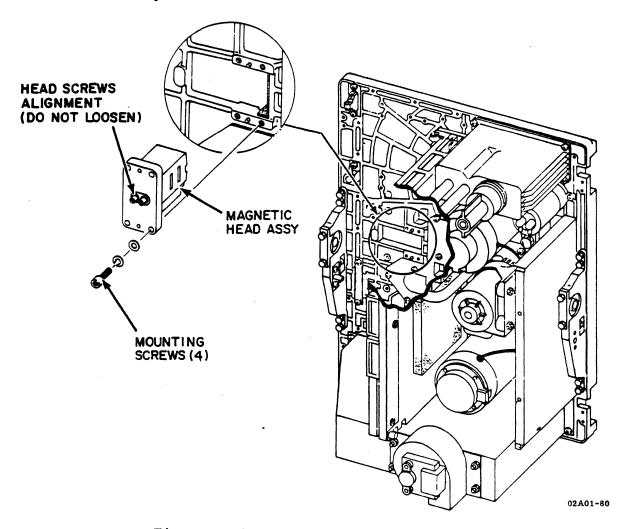

| 5-15   | Magnetic Head Connectors                                    | 5-33           |

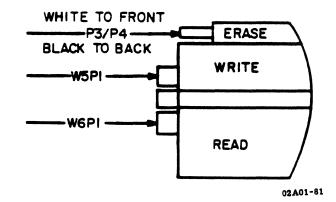

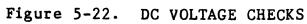

| 5-16   | Read/Write/Servo Module                                     | 5-34           |

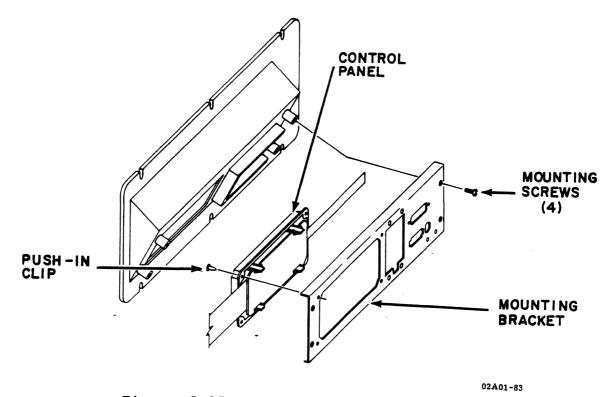

| 5-17   | Operator Panel Assembly                                     | 5-35           |

|        |                                                             |                |

# LIST OF ILLUSTRATIONS (Cont'd)

| FIGURE                                                                       | TITLE                                                                                                                                                                                                                                                                      | {    | PAGE                                                                 |

|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------------------------|

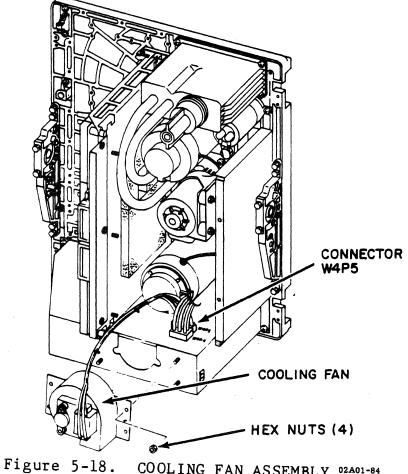

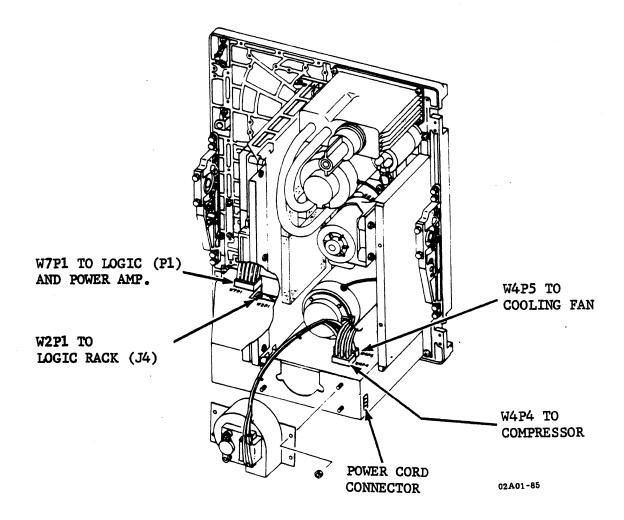

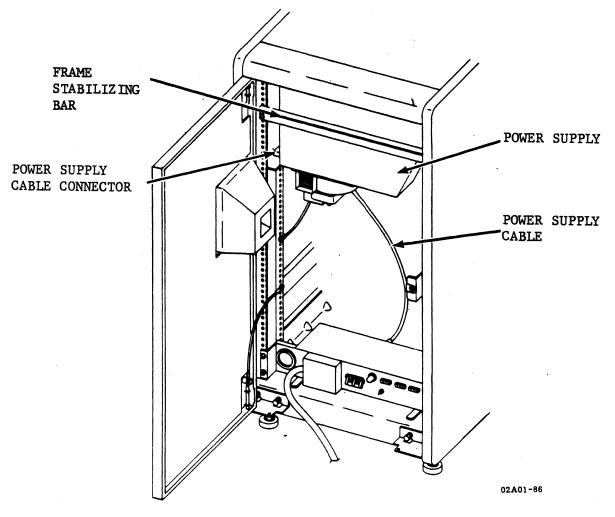

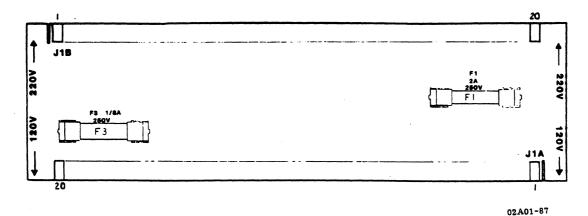

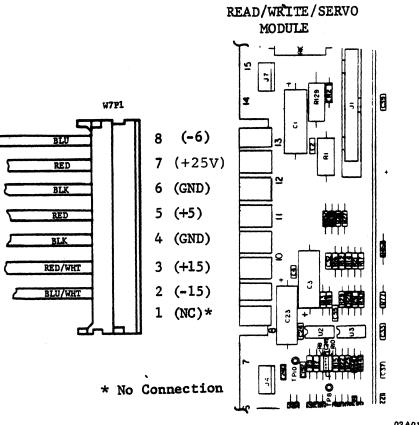

| 5-18<br>5-19<br>5-20<br>5-21<br>5-22<br>5-23<br>5-24<br>5-25<br>5-26<br>5-27 | Cooling Fan Assembly<br>Power Supply Connectors<br>Power Supply (Rear Cabinet View)<br>Voltage Select Card<br>DC Voltage Checks<br>Read/Write/Servo Module<br>Logic Module Removal/Replacement<br>Formatter Control Module<br>Power Amplifier Module<br>Capacitor Assembly |      | 5-37<br>5-38<br>5-40<br>5-42<br>5-44<br>5-46<br>5-48<br>5-51<br>5-52 |

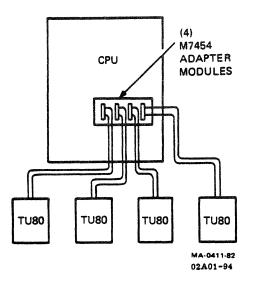

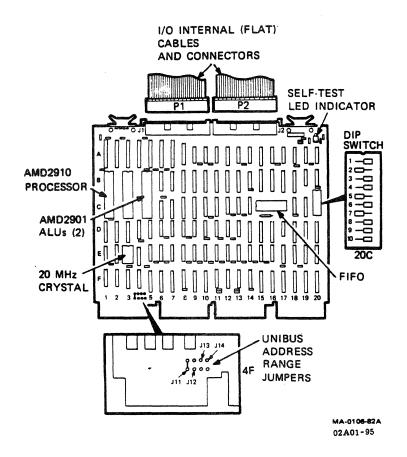

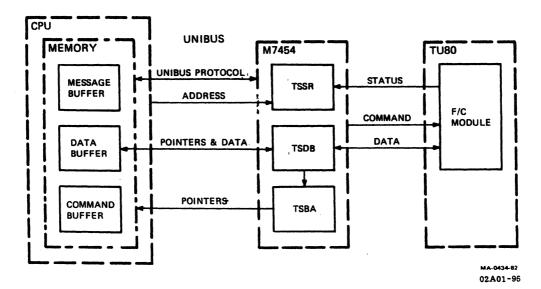

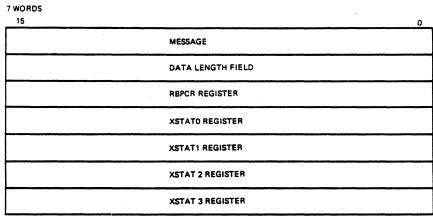

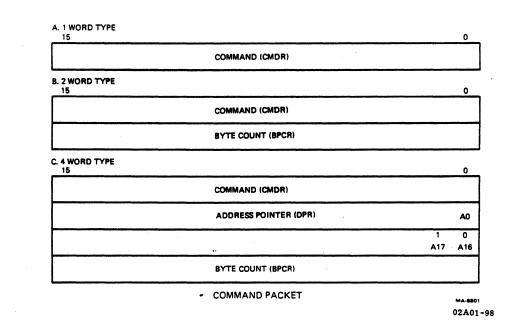

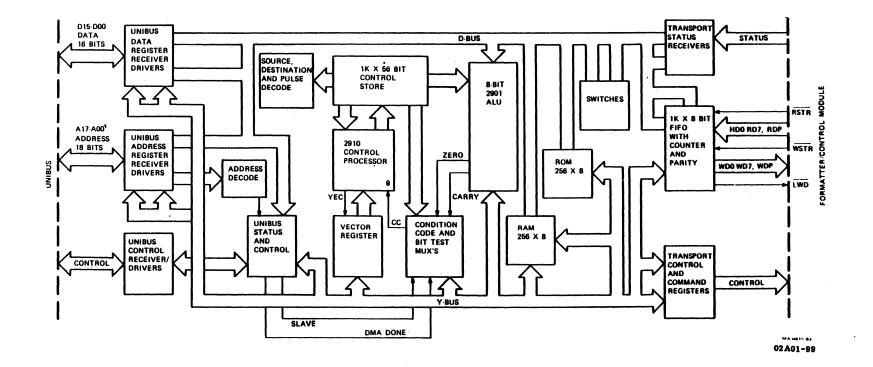

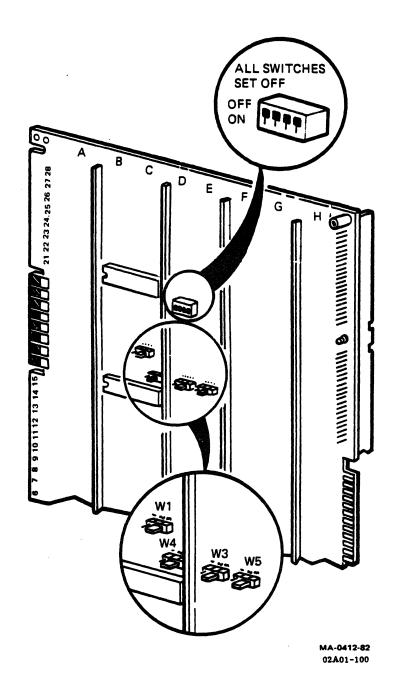

| A-1<br>A-2<br>A-3<br>A-4<br>A-5<br>A-6                                       | Maximum TU80 Configuration<br>M7454 UNIBUS Adapter Module<br>Packet Protocol Components<br>TU80 Register Summary<br>Example of Protocol Packets<br>M7454 Functional Block Diagram                                                                                          |      | A-2<br>A-2<br>A-8<br>A-9<br>A-11<br>A-13                             |

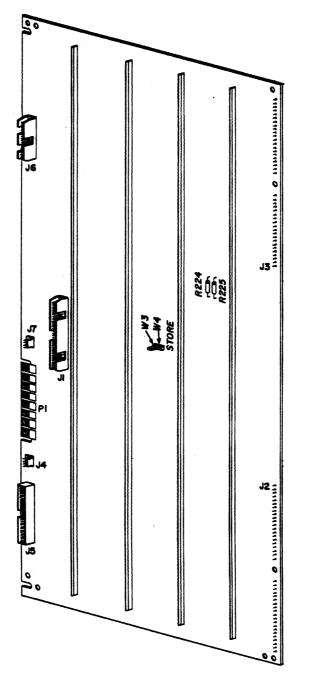

| B-1                                                                          | Formatter Module - Configuration Select<br>Components                                                                                                                                                                                                                      | tion | B-3                                                                  |

Х

# LIST OF TABLES

| TABLE | TITLE                                         | PAGE |

|-------|-----------------------------------------------|------|

| 1-1   | Mechanical and Electrical Characteristics     | 1-6  |

| 2-1   | Single - TU80 Address Selection               | 2-18 |

| 2-2   | Address Selection In Multi-TU80 Configuration | 2-19 |

| 3-1   | Operator Controls                             | 3-2  |

| 3-2   | Operator Corrective Actions                   | 3-8  |

| 4 -1  | Processor Read/Write Timing Constraints       | 4-33 |

| 4 -2  | TU80 Sense Byte Summary                       | 4-62 |

| 4 -3  | TU80 Formatter Interface Commands             | 4-65 |

| 4 -4  | Motion Characteristics                        | 4-69 |

| 4 -5  | Streaming Mode Motion Sequence Chart          | 4-73 |

| 5-1   | Removal/Replacement Index                     | 5-3  |

| 5-2   | Fault Code Matrix (Operator Test #01)         | 5-56 |

| A-1   | M7454 Controller/UNIBUS Interface Lines       | A-4  |

| A-2A  | M7454 Controller/Formatter Interface Lines    | A-5  |

| A-2B  | M7454 Controller/Formatter Interface Lines    | A-6  |

| A-3   | TU80 Assigned Command Modes                   | A-7  |

1.1 GENERAL

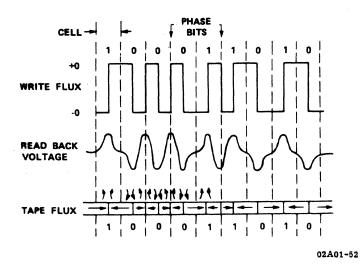

The TU80 Streaming Tape Unit is a microprocessor-based, electronic and mechanical assembly that includes all hardware and firmware necessary for the transfer of Phase Encoded (PE) data to and from half-inch wide magnetic tape.

The horizontally mounted TU80 is a fully integrated tape storage system packaged with its formatter and power controller in a standard H9643 cabinet.

Solid-state electronics replace many devices that were traditionally mechanical. Tape moves from reel to reel, maintaining its tension with an electronically controlled servo. This non-buffered approach allows performance equivalent to that of a conventional capstan-controlled drive in the start/stop operating mode. The TU80 contains no capstan motor drive, tension arms, vacuum columns, or associated components. Read/Write functions are accomplished in an ANSI-compatible format at 1600 CPI Phase Encoding.

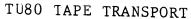

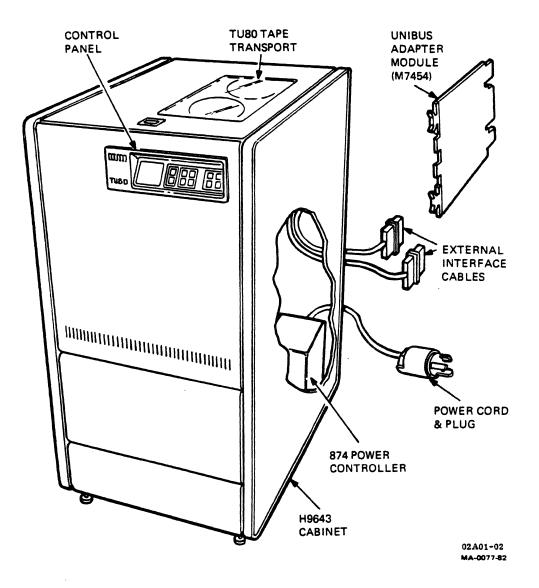

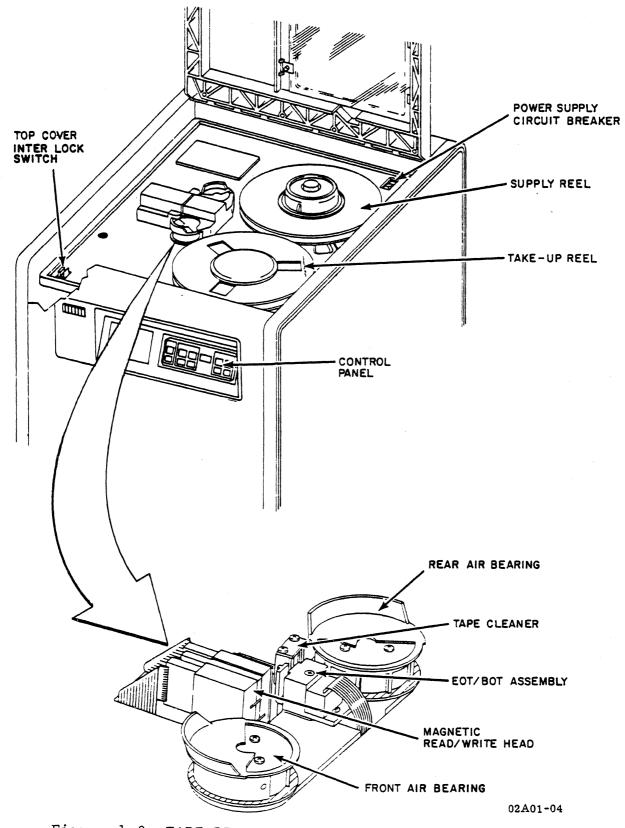

The TU80 Subsystem consists of the stand-alone Streaming Tape Unit, the 874 Power Controller, and a UNIBUS Adapter Module (Figure 1-1). This module is designed for the UNIBUS-oriented PDP-11 and VAX Processors. It plugs into a host computer's UNIBUS Small Peripheral Controller (SPC) slot and provides communication with the corresponding Streaming Tape Unit. Refer to Figure 1-2 for a block diagram of the TU80 Subsystem.

NOTE

The TU80 cabinet may hold an optional disk drive mounted under the tape transport at the bottom of the cabinet. Consult the User Guide of the appropriate disk drive for user information.

The TU80 tape transport includes a tape deck with a read/write head, reel hubs, servo motors, power supply and air bearings. Printed circuit modules contain the following electronic features: servo power amplifier, read/write, reel servo control, data encoding and decoding, and two microprocessors with their support devices (for transport control in both the operational and diagnostic modes). The device features a quick-release reel latch which, like its simplified tape threading path, is designed for ease of operation.

The unit has three operating modes: 25 ips Start/Stop, 25 ips streaming, and 100 ips streaming (refer to paragraph 4.10.1 for start/stop and streaming modes of operation). Dual data transfer rate capability is achieved by allowing selection of the 25 ips modes and 100 ips mode through the automatic speed control within the TU80 transport. The 25 ips modes operate at an instantaneous data rate of 40,000 bytes per second and the 100 ips mode operates at 160,000 bytes per second.

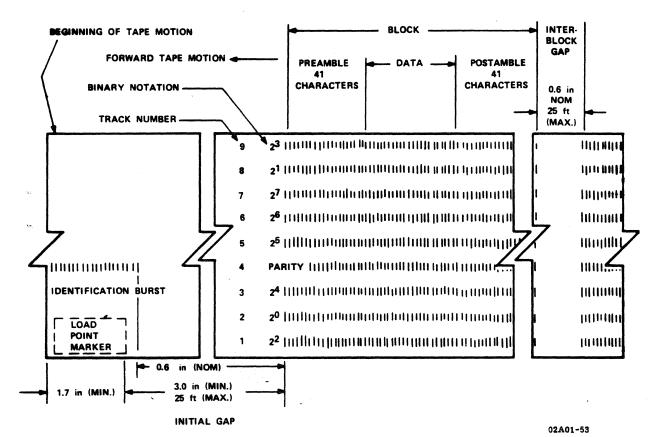

Selection of a normal Inter-block Gap (IBG) length of 0.6 inch or a long IBG length of 1.2 inches is available through the formatter. Optionally, in 100 ips streaming mode, long and short gaps can be selected to be variable lengths. All transport address and feature selections are required to be verified (and/or set) before TU80 initialization. These selections are performed through the jumpers on the Formatter/ Control Module as shown in Appendix B of this manual.

Figure 1-1. TU80 TAPE SUBSYSTEM

Off-line diagnostic routines are designed into the transport and are capable of isolating faults throughout its electronics. These diagnostic routines which are initiated via the operator's control panel, and consist of operator and field service diagnostics, are explained in detail in the TU80 Subsystem Diagnostic Test Documentation/Pathfinder (EK-OTU80-SV).

The host I/O controller is capable of monitoring the transport's status through the Status Transfer command. In addition to the off-line routines initiated by the control panel, Power-On Health Check is also an integral part of the TU80. The TU80 automatically performs a "power-on health check" sequence of host routines to check AC/DC power lines and the control panel each time power is applied.

Table 1-1 provides a list of mechanical and electrical characteristics for the TU80.

On-line diagnostics are performed under the host CPU control and are listed in the applicable system's diagnostic listings.

#### NOTE

Appendix C provides the listing of the TU80 documents available to the user.

Figure 1-2. TU80 TAPE SUBSYSTEM BLOCK DIAGRAM

#### FUNCTIONAL CHARACTERISTICS:

Tape Speed (Nominal) Low Speed Start/Stop Mode 25 in/sec Low Speed Streaming Mode 25 in/sec High Speed Streaming Mode 100 in/secTape Capacity (Maximum) 40 Mbytes Data Transfer Rate (Burst) Low Speed Mode 40 Kbyte/sec High Speed Streaming Mode 160 Kbyte/sec Data Format/Recording 9 track, phase encoding, 1600 bit/inch 2.5 minutes Rewind Time (Nominal) 15 seconds Load Time (Maximum) **PHYSICAL CHARACTERISTICS:** Electronics Solid-state Tape Width 12.65 mm (0.5 in) Tape Thickness 38.1 micron (1.5 mil) Tape Tension 2.23 N (8.0 oz) Reel Diameter 26.7 cm (10.5 in) \* Reel Capacity 732 m (2400 ft) \* 105.7 cm (H) x 54.6 cm (W) x Transport Dimensions 76.2 cm (D) 41.6 in (H) x 21.5 in (W) x 30.0 in (D) Transport Weight (In Cabinet) 280 lbs (127 kg) UNIBUS Adapter Standard quad-size module **OPERATIONAL CHARACTERISTICS:** Power Requirements Voltage 93 to 128 VAC, 120 VAC nominal, 60 Hz, single phase 187 to 256 VAC, 220 or 240 VAC nominal, 50 Hz, single phase \* Smaller tape reels are also allowed.

Table 1-1. MECHANICAL & ELECTRICAL CHARACTERISTICS (Cont'd)

Power Requirements (Cont'd) Average Input Current 2.0A rms at Current 100 ips 300 VA - Standby and Loaded Power Consumption 550 VA maximum - Start/Stop Power Controller Model 874B, 50 Hz, 240V, 12A Model 874D, 60 Hz, 120V, 24A 3-wire, #12 AWG, 16 foot long Power Cord plug - NEMA 6-15P (50 Hz) - NEMA 5-30 (60 Hz) Model Variations Model TU80-AA, 120V, 60 Hz Model TU80-AB, 240V, 50 Hz 10°C (50°F) to 40°C (104°F) Operating Temperature \*\* Storage Temperature --10°C (14°F) to 50°C (122°F) Relative Humidity 20% to 80% (10% to 90% in storage Altitude Up to 3048 m (10,000 ft) or 688 millibars (9.98 psi) 580 BTU/hour Heat Dissipation (Average) Acoustical Noise 51 dba for open office environment Data Reliability Recoverable Write Error  $1 \text{ in } 10^8 \text{ bits}$ Recoverable Read Forward  $1 \text{ in } 10^9 \text{ bits}$ Error Recoverable Read Reverse 1 in  $10^8$  bits 1 in  $10^{10}$  bits Error Unrecoverable Read Error Unrecoverable Write Error Not Allowed \*\* Restricted by the operating temperature of the media.

#### 1.2 FUNCTIONAL DESCRIPTION

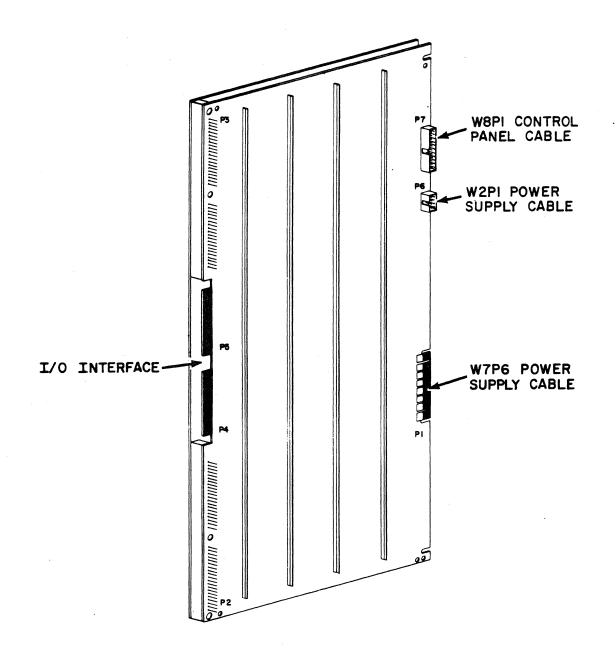

The TU80 is interfaced to the host Central Processing Unit (CPU) via the UNIBUS Adapter Module (M7454). This module is plugged into a UNIBUS SPC slot in the CPU. The module processes data using the packet processing protocol. The Adapter Module-TU80 communication link is accomplished via a parallel interface cable set which connects the M7454 Module to the transport's control system.

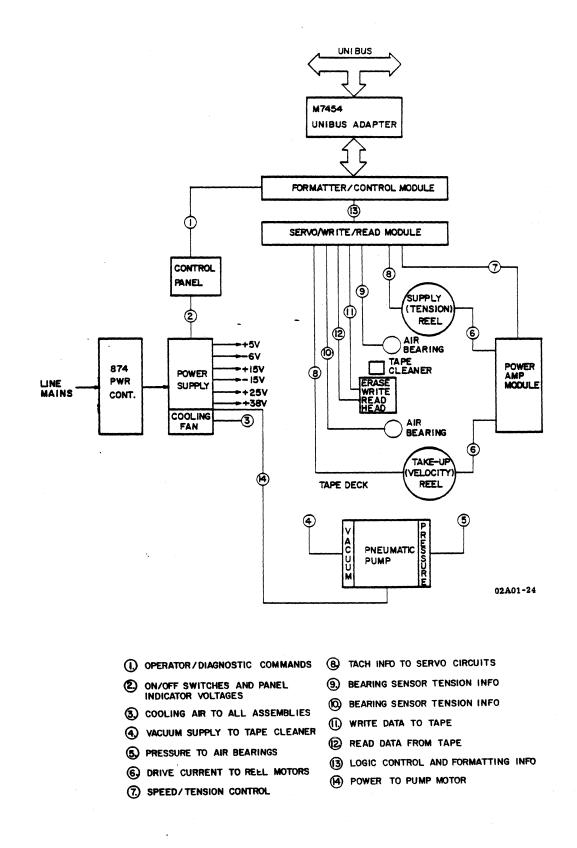

The TU80 Control System (Figure 1-2) comprises two logic modules and a power amplifier module. The two logic modules are functionally partitioned and each module contains a microprocessor for control of all module functions.

One module is the Formatter/Control PC board. The Formatter/ Control Module provides high speed data interchange between the transport and host system, including such functions as data fetching and formatting and read/write operation. It also handles a single track, "on-the-fly" data error error correction, and initiates and monitors the built-in diagnostic routines.

The other control module is the Read/Write/Servo PC board which controls the tape drive mechanism operation.

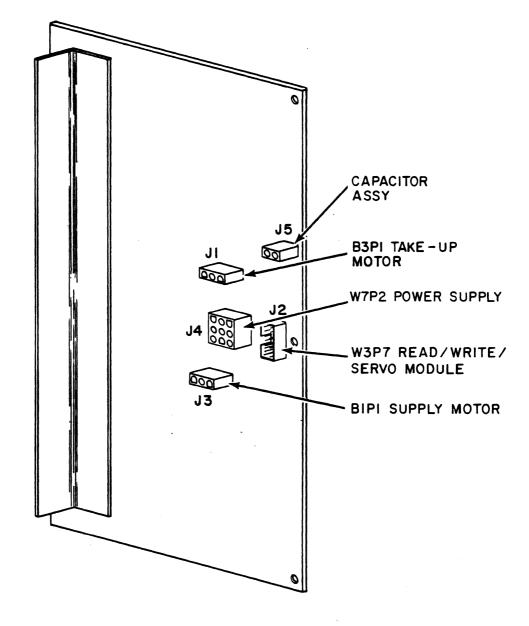

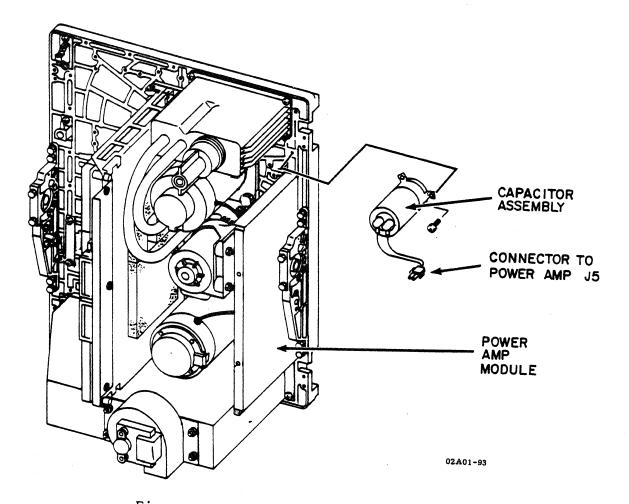

The power amplifier module receives low voltage analog signals from the logic modules and outputs a higher voltage, higher current signals to the reel motors.

A power supply module mounted behind the tape deck provides all required AC/DC voltages to the transport modules and mechanisms.

The TU80 logic is compactly mounted in a metal cage underneath the tape deck.

1.2.1 TU80 UNIBUS Adapter Module (M7454) The UNIBUS Adapter Module provides a functional interface between the TU80 and PDP-11/VAX Computers. This interface module handles streaming and start/stop mass storage back-up with large volume data transfers and information interchange through ANSI- compatible tape media. The M7454 controls command decoding, data fetching and storing, and data transmission to/from the TU80.

The quad-size M7454 module plugs directly into any Small Peripheral Controller (SPC) slot of the DIGITAL host CPU. A set of internal (ribbon) and external (shielded) cables connect the adapter module to the tape transport. External interface cable length is 3.66 m (12 feet). Effective external cabling length is 2.7 m (9 feet).

#### NOTE

Refer to Appendix A for detailed information on the M7454 UNIBUS Adapter.

1.3 PHYSICAL DESCRIPTION

The TU80 is a cabinet-enclosed, horizontally mounted unit designed to provide front access for both operator and maintenance functions. Operator access for tape mounting is via the hinged top cover. Maintenance access to the underside of the tape deck is achieved by opening the top cover and front door and releasing the deck latch located at the left underside of the tape deck. Releasing this latch allows the tape deck to pivot such that the underside of the deck is positioned to the front of the cabinet in a vertical position.

The input power cord and interface cables enter the cabinet at the rear bottom of the unit. Access to this area is via a hinged rear door.

1.3.1 Tape Deck - Top Refer to Figure 1-3 for component locations. The following components are located on the front of the transport. A brief description of the components and their function is provided as follows.

Figure 1-3. TAPE DECK COMPONENT LOCATIONS, TOP VIEW

1.3.1.1 Supply Reel - The supply (rear) reel is mounted on a manual mechanical-latching hub. The supply hub is latched by pressing the periphery of the hub face while the supply reel is positioned against the bottom flange of the hub. The reel is released by pressing the center button on the hub face.

1.3.1.2 Take-Up Reel - The take-up (front) reel is a permanently mounted reel secured to the take-up motor shaft.

1.3.1.3 Air Bearings - The air bearing/tension sensor assembly is used to sense and control air pressure across the air bearings, thus reducing tape friction and providing constant (8 ounce) tape tension by the corresponding action of the supply reel motor. The air bearings also guide tape across the magnetic heads.

1.3.1.4 Magnetic Head Assembly - The magnetic head is a dual-gap read/write unit designed to perform the read/write functions in a 9-track PE mode. The dual-gap head allows a write-to-tape operation, read-only operation or read-after-write operation. A full-width erase head is also provided to erase the tape by DC saturation in the forward direction before passing over the write head.

1.3.1.5 Tape Cleaner - The tape cleaner assembly consists of two blades and a vacuum port to attract tape to the cleaner surfaces. The cleaners are designed so that one cleaner cleans tape in the forward direction and the second cleans tape in reverse direction. The vacuum system directs the stripped particles through a screen and into a filter.

1.3.1.6 BOT/EOT/AOT Assembly - Load Point/End of Tape is detected optically. Photo-transistors detect light reflected from BOT and EOT markers on tape. A no-tape-present condition is detected when both BOT and EOT photo-transistors detect a reflective marker normally blocked by the presence of tape.

1.3.1.7 File Protect - The file protect assembly consists of a 360° reflecting ring around the supply hub and a photo-transistor mounted adjacent to the reflecting ring. If a write enable ring is installed in the supply reel, the reflecting ring is in direct line with the photo-transistor. If a write enable ring is not present, then the reflecting ring is out of the path of the photo-transistor.

1.3.1.8 Power Switch - The main power switch (circuit breaker) is located at the top rear corner of the tape deck. In the OFF position (0 side depressed), input power is removed from the power supply. This circuit breaker must be ON (1 side depressed) in order to perform the Subsystem Power-On operation from the control panel.

1.3.1.9 Top Cover Interlock - The transport is equipped with an interlock switch/top cover latch located at the lower left corner of the tape deck. This interlock is basically a safety device to prevent reel motion, unless the front cover is closed and secured.

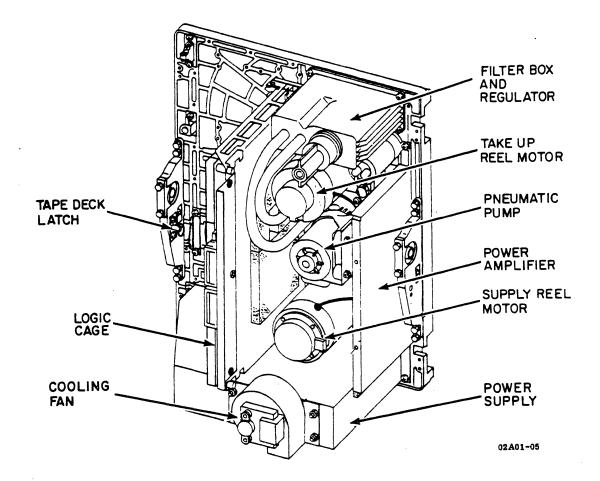

1.3.2 Tape Deck - Bottom Refer to Figure 1-4 for component locations. The following components are located on the bottom of the tape deck. A brief description of the components and their function is provided as follows.

1.3.2.1 Tape Deck Latch - This latch enables the tape deck to be placed in the maintenance position for access to the bottom tape deck assemblies.

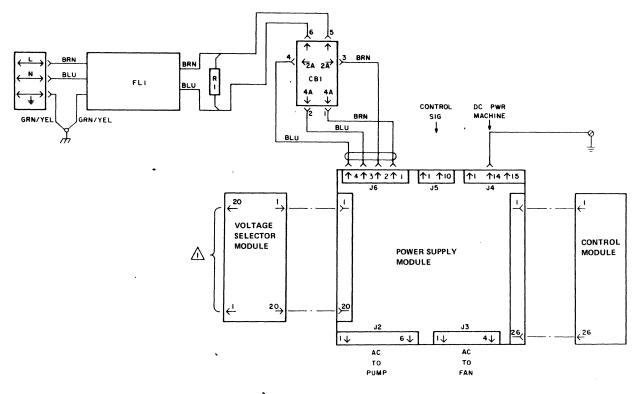

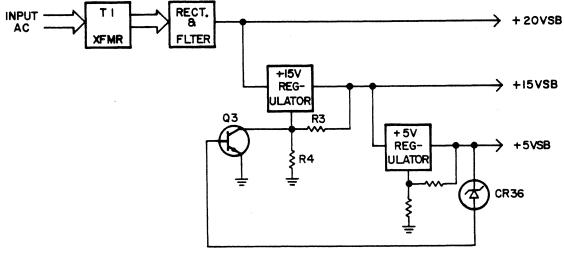

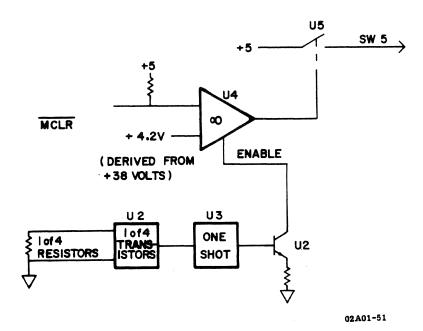

1.3.2.2 Power Supply - The power supply accepts the input AC voltage and converts it to six (+5, -6, +15, -15, +25, +38) DC output voltages. The supply contains a line filter, unit circuit protectors, on/off circuit breaker, logic master clear circuit, pneumatic pump motor control, cooling blower control, and voltage and current monitors.

1.3.2.3 Pneumatic Pump and Filter/Regulator System - The pneumatic pump is a 120V (60 HZ) or 220/240V (50 HZ) AC inductor motor with a 4-blade, carbon vane pump. The compressor output air is routed to a filter where any carbon particles are removed before distribution to tape deck components. Mounted directly onto the filter is a piston-type pressure regulator which maintains a constant 2.0 PSI output to the upper and lower air bearings. The vacuum portion of the pump draws air from the tape cleaner.

1.3.2.4 Power Amplifier Module - The power amplifier module receives the low voltage analog signals from the control logic and outputs a higher voltage, high current to the reel motors. Outputs are dependent on the requirements of the velocity and tension servo systems.

Figure 1-4. TAPE DECK COMPONENT LOCATIONS, REAR VIEW (ACOUSTIC COVER REMOVED)

1.3.2.5 Cooling Fan Assembly - The cooling fan is a squirrel-cage type assembly located at the rear of the power supply. Cooling air is drawn across the rear deck assemblies and through the power supply. The fan motor is compatible with either 120 or 240 volt operation.

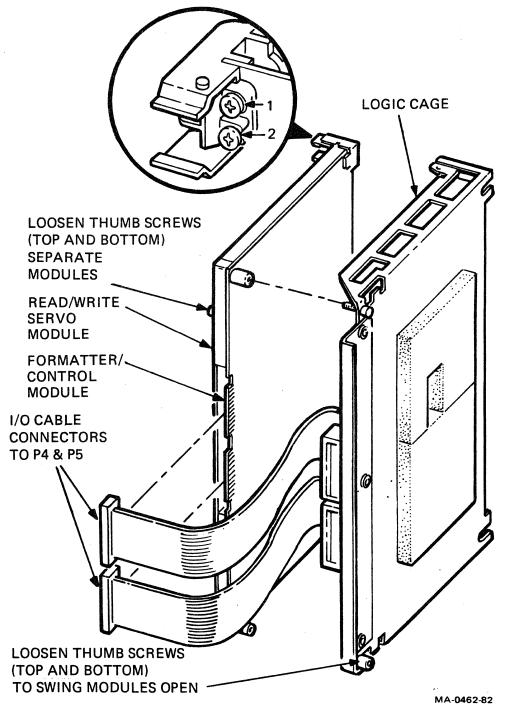

1.3.2.6 Logic Cage - The logic cage consists of a logic bracket assembly and the Read/Write/Servo and Formatter/Control Modules. The modules are inserted into top and bottom hinges at the rear of the bracket assembly and are secured with thumb screws in the normally closed position. Releasing the thumb screws allows the hinged modules to be positioned for access to components.

1.3.2.7 Reel Motors - The reel motors are conventional, permanent-magnet DC motors. The supply reel motor works in conjunction with the upper and lower air bearings to control tape tension across the recording surface of the magnetic head. The air bearings sense the proximity of tape via air pressure and, in effect, activate the pressure sensors. The sensors cause the servo to maintain a constant tension by action of the supply reel motor. The take-up reel motor has a 1000-segment tachometer attached which provides velocity control.

#### 1.3.3 Control Panel (Front Door)

The control panel includes a set of operational control switches, indicators, and a display located at the top right of the front door. These controls enable the operator to initiate and monitor TU80 operations and the off-line diagnostic routines.

#### 1.4 EQUIPMENT CONFIGURATION

The equipment configuration of the transport is determined by the equipment identification plate plus the FCO log that must be present with every transport. A description of the ID plate and the FCO log is given in the following paragraphs.

1.4.1 Equipment ID Plate/Serial Tag The ID plate/serial tag is located on the inside of the hinged front door. Refer to Figure 1-5 for the following items contained on the plate.

| digital             |                | TU80 | -AA | MADE IN<br>U.S.A. | 3 |

|---------------------|----------------|------|-----|-------------------|---|

| Hz 60 V~<br>W 500 A | • 120<br>24/PH |      |     | 1 PH<br>1 W+N+G   |   |

02A01-06

## Figure 1-5. EQUIPMENT IDENTIFICATION PLATE

- MODEL Indicates the model designation and model variation for the unit.

- SN Indicates the serial number which is unique for each transport and is assigned sequentially by the manufacturer.

- HZ Indicates the frequency parameters (cycles per second) of the input voltage.

- W Indicates the total operating power consumption of the transport.

- V Indicates the input voltage requirement of the transport.

- A/Ph Indicates the maximum ampere requirement per phase.

- Ph Indicates the phase requirement of the transport.

- W+N+G Indicates the configuration of the input power line cord (active wire + neutral + ground).

1.4.2 Field Change Order Log

A Field Change Order is a change to the transport after it has been shipped from the manufacturing facility. It is important that the FCO log is kept current by the person installing the FCO, so that the exact configuration of the transport can be referenced.

#### Section 2 - INSTALLATION AND CHECKOUT

#### 2.1 SITE REQUIREMENTS

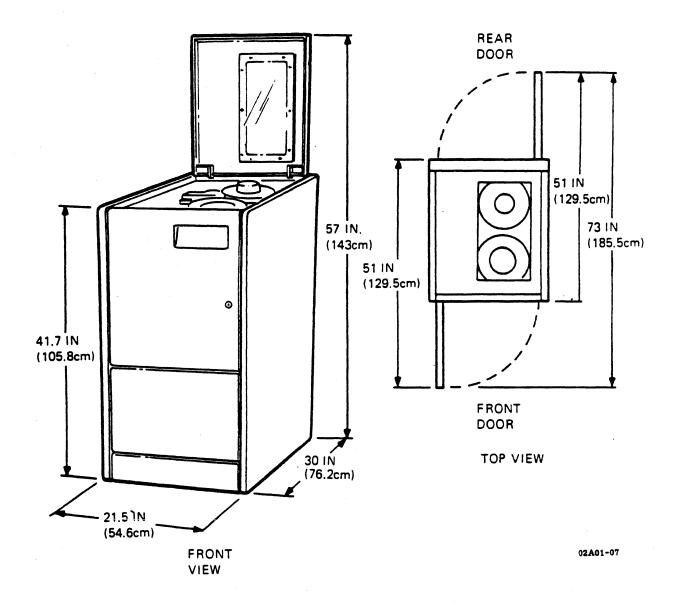

2.1.1 Space Requirements Space requirements for operator and maintenance access via the top, front, and rear hinged doors are shown in Figure 2-1.

2.1.2 Power Requirements Power requirements for the TU80 are listed in Table 1-1. The appropriate power plugs, receptacles, and circuit breakers are an integral part of the TU80.

The UNIBUS Adapter Module (M7454) typically draws 4.0A at +5 VDC. The power for the module is derived from the host CPU through the dedicated pins of the CPU backplane.

2.1.3 Environmental Requirements The TU80 transport should be located in an area free of excessive dust, dirt, and corrosive fumes and vapors. The bottom of the cabinet and air vents on the doors must not be obstructed. The operating environment requirements are:

|          | o Temperature:<br>o Relative Humidity: |                      | 10°C (50°F) to 40°C (104°F)<br>20% to 80% |                               |                          |              |  |  |  |

|----------|----------------------------------------|----------------------|-------------------------------------------|-------------------------------|--------------------------|--------------|--|--|--|

| <b>0</b> | Altitude:                              | Up<br>[baro<br>milli | to<br>ometric<br>lbars                    | 3048M<br>c press<br>(9.98 PSI | (10,000<br>sure of<br>)] | feet)<br>688 |  |  |  |

#### 2.2 ACCEPTANCE OF DELIVERY

Carefully inspect the shipping container on all sides, including top and bottom, for severe gouges, cuts, abrasive tears, or badly smashed corners or edges. Damage of this type indicates mishandling in shipment, and the unit may have been damaged. Record all details of damage, and have the carrier's representative sign it before accepting delivery.

Figure 2-1. TU80 SPACE REQUIREMENTS

## 2.3 UNPACKAGING AND INSPECTION

2.3.1 Floor Loading and Routing

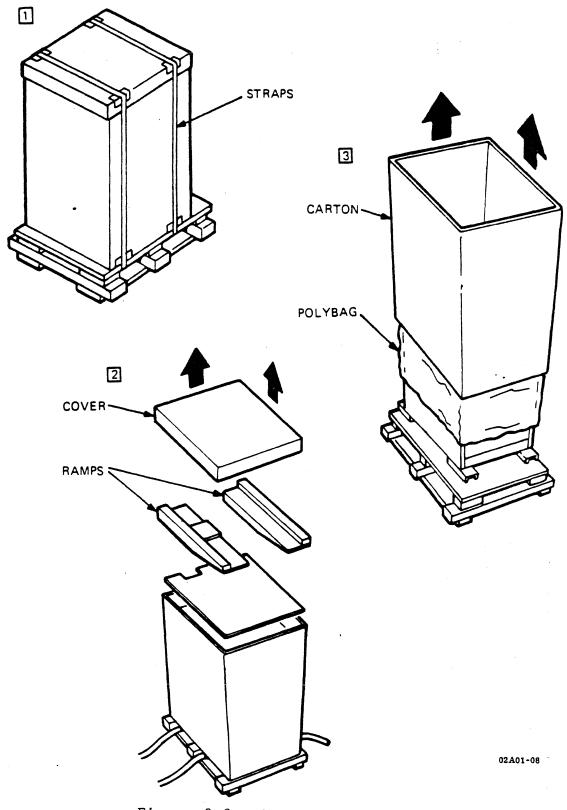

The TU80 transport is shipped in a cardboard container mounted on a wooden pallet. The shipping weight is 330 pounds (149 kg). The container dimensions are 51 inches high, 29 inches wide, and 41.5 inches deep. Check the route that the unit will travel to the installation site to ensure problem-free delivery. Net weight (unpackaged) of the transport is 280 pounds (127 kg).

2.3.2 Unpackaging and Removal From Pallet

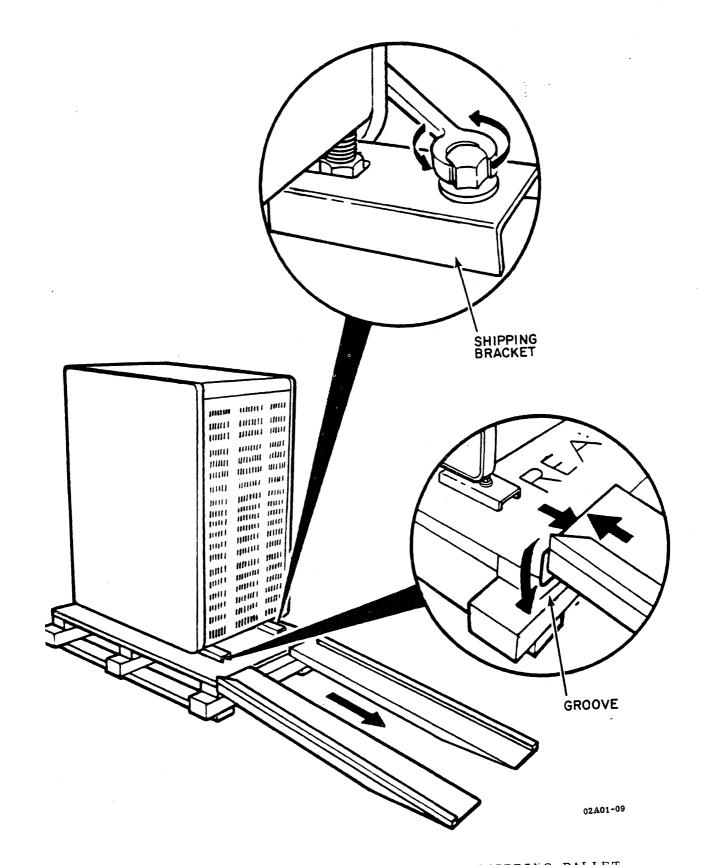

The unpacking and removal procedures are illustrated in Figure 2-2. Numbers on the illustrations correspond to the numbers referenced in the following procedures.

- 1. Cut and remove straps holding stabilizer to cardboard container and remove stabilizer.

- 2. Cut and remove the shipping straps around cardboard container (1).

- 3. Lift and remove top container cover (2).

- 4. Carefully lift and remove the two ramps from top of cabinet. Set them aside for future use.

- 5. Lift and remove protective carton (3).

- 6. Remove top pad and polybag (4).

- 7. Referring to Figure 2-3, attach the two ramps to the pallet, noting the LEFT and RIGHT markings on the ramps.

- 8. Unbolt and remove the four black shipping brackets.

#### WARNING

This is a two-person procedure. Take extreme care to prevent the TU80 from rolling uncontrolled down the ramps or off either side of the pallet when releasing the leveling bolts.

9. While holding the TU80 on the pallet, turn each leveling bolt so that each wheel makes contact with the pallet to allow the cabinet to roll free.

Figure 2-3. REMOVING THE TU80 FROM SHIPPING PALLET

- 10. With one person on each side of the cabinet, carefully roll it down the ramps onto the floor.

- 11. Remove the ramps. Store the pallet, ramps, and carton for future use.

2.3.3 Inspection

After removing the TU80 from its container and shipping pallet, perform a visual inspection as described in the following steps. Report any damage to the responsible shipper and the local DIGITAL Sales Office.

- 1. Inspect all panels, doors, door latches, and control panel for any obvious damage.

- 2. Using a 5/32 inch Allen wrench, open front and rear doors and inspect cabinet interior for any foreign material and loose or damaged components or cables.

- 3. Pull top cover latch and lift top cover. Inspect tape deck for broken glass, damaged magnetic head components, and damaged reels.

- 4. Check for any foreign materials that may have lodged in tape reels. Rotate supply and take-up reels.

- 5. Check tape path for any sharp edges. Close top cover and the front and rear doors.

#### 2.4 OPERATION PREPARATIONS

The TU80 transport should be placed in a location not further than 2.7M (9 feet) from the host CPU and with adequate space clearances for air circulation and servicing.

TU80 preparations for operation are performed as follows.

- 2.4.1 Mechanical Installation

- 1. Roll transport to its correct location.

- 2. Open rear door and remove cardboard box with the TU80 Accessory Kit (TU80K-AC).

### If there is a disk drive in the TU80 cabinet, proceed as follows:

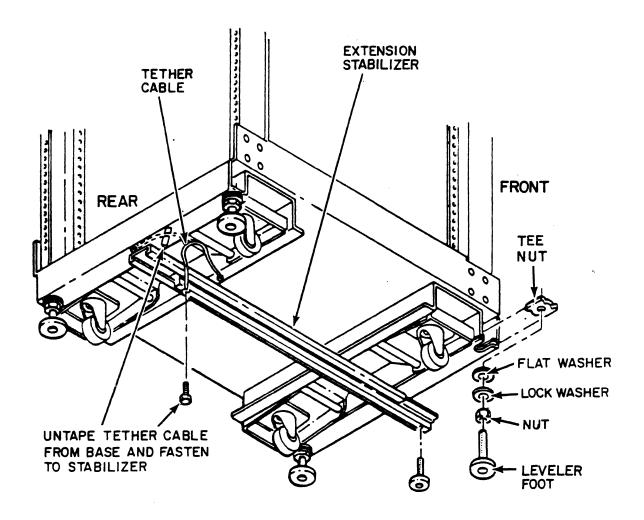

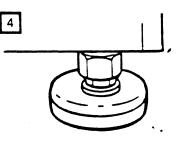

1. Install the extension stabilizer P/N H9544-HC (Figure 2-4).

- Unwrap the stabilizer and mounting hardware.

- Slide the stabilizer in place from the rear of cabinet.

- Fasten the tether cable to the stabilizer using the supplied hex head screw.

- Thread on the stabilizer's leveling foot.

Figure 2-4. CABINET LEVELER FEET ASSEMBLY AND EXTENSION STABILIZER

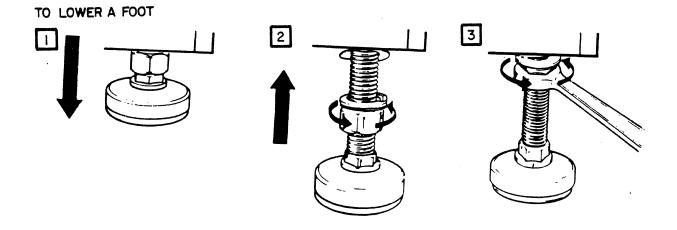

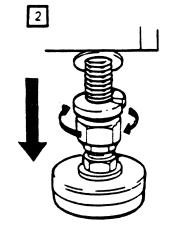

- 2. Lower four leveler feet as shown in Figure 2-5.

- Lower the leveler foot to contact the floor.

- Using a 3/4 inch open-end wrench, turn the top nut up to the top and tighten.

- Repeat for the remaining feet to stabilize the unit.

- 3. Proceed to paragraph 2.4.2 Electrical Connection.

If there is no disk drive in the TU80 cabinet, proceed as follows:

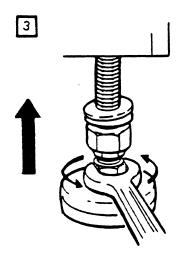

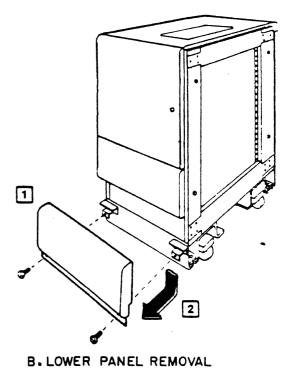

- 1. Remove two end (side) panels and the rear door as shown on Figure 2-6.

- Pull up the spring pins and remove the rear door (Figure 2-6A). Remove the ground strap using a 5/16 inch flat-blade screwdriver.

- Remove the door hinge brackets located in the rear bottom left and right corners of the cabinet using a 7/16 inch open-end wrench (Figure 2-6B).

- Remove the end panels by lifting them up and away from the unit.

- Remove the ground straps from the side (end) panels using a 5/16 inch flat-blade screwdriver.

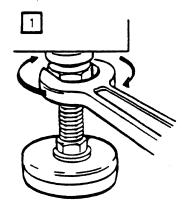

- 2. Remove two rear leveler feet (Figures 2-4 and 2-5).

- Using a 3/4 inch open-end wrench, loosen and lower the top nut on a foot.

- Place a 9/16 inch open-end wrench on the bottom nut on a foot and turn the nut upward.

- Back the foot off the floor, then pull it outward to remove.

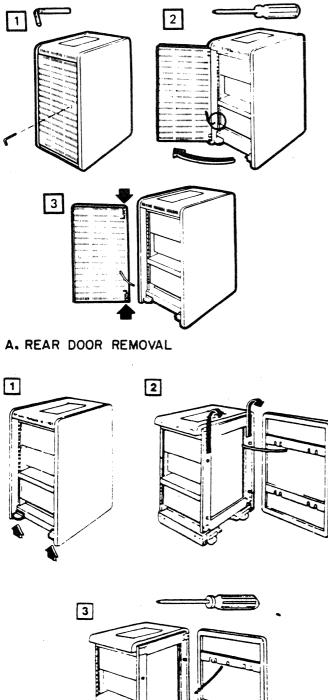

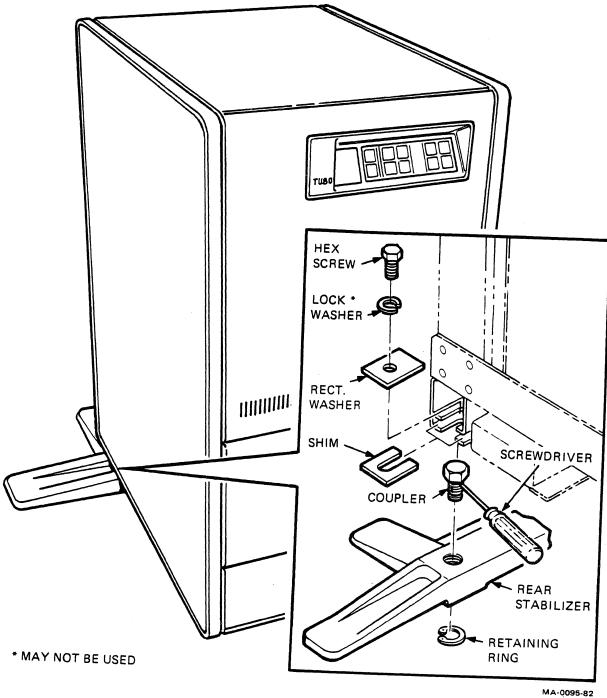

- 3. Install the rear stabilizer P/N H9455-MJ (Figure 2-7).

- Install two couplers in the stabilizer base.

TO RAISE A FOOT

02A01-10

Figure 2-5. LEVELER FEET ADJUSTMENTS

02A01-11

C. END (SIDE) PANEL REMOVAL

Figure 2-6. CABINET ASSEMBLY

02A01-12

# Figure 2-7. REAR STABILIZER INSTALLATION

- Slide the stabilizer under the rear bottom of the cabinet so that the couplers are directly under the mounting slots.

- Install the rectangular washers, retaining washers, and hex screws. Do not tighten the screw yet.

- Level the cabinet by adjusting the couplers. Use a screwdriver inserted into a hole in the coupler to jack it.

To raise the cabinet, turn the coupler counterclockwise; to lower cabinet, turn the coupler clockwise.

- Slide the shims in place in the mounting slots.

- Tighten the hex screws using a 3/4 inch box wrench and #2 Phillips screwdriver.

- Adjust the leveler feet to completely stabilize the cabinet (Figure 2-5) using the 3/4 inch and 9/16 inch open-end wrenches.

- 5. Replace the end panels and rear door on the cabinet and reattach the ground straps.

#### NOTE

If you need to move the transport to another location within the room, raise the leveler feet. Release the nuts on the feet using the 3/4 inch and 9/16 inch open-end wrenches (Figure 2-5), then pull each foot up to the top.

2.4.2 Grounding

Grounding can be done mechanically when the TU80 cabinet is bolted to another system unit cabinet, or electrically by the central grounding line from the last CPU connected to the existing ground stud on the cabinet rack.

Check TU80 Equipment Identification (ID) plate for power specifications. Make sure that local line voltage and frequency are compatible with the transport power specifications.

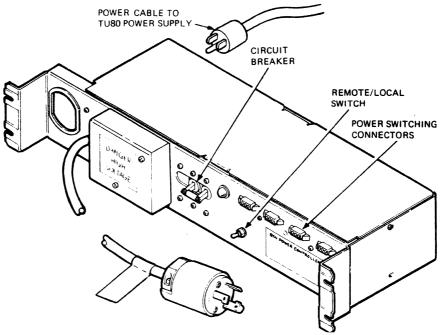

- 1. Check that the power ON/OFF circuit breaker on the 874 Power Controller is in ON position and the REMOTE/LOCAL switch is set to REMOTE position (Figure 2-8).

- 2. Connect the remote power switching wire from the TU80 Power Controller (any of the four connectors) to the CPU Power Controller.

- 3. Check that the power cable from the transport power supply is plugged into the AC connector in the rear of the power controller.

- 4. Plug power cable into a local power outlet.

- 5. Open the TU80 top cover and set the power switch to the ON (1 depressed) position. Turn CPU power on. The LOGIC OFF indicator on the TU80 control panel should illuminate.

Figure 2-8. 874 POWER CONTROLLER MA-0096-82 02A01-13

When installed, the TU80 should be in remote power-on mode controlled by the CPU.

5. Turn the CPU power off. Now proceed with the M7454 UNIBUS Adapter installation and interfacing the TU80 with the CPU.

2.5 UNIBUS ADAPTER MODULE INSTALLATION/REPLACEMENT AND INTERFACE CABLING

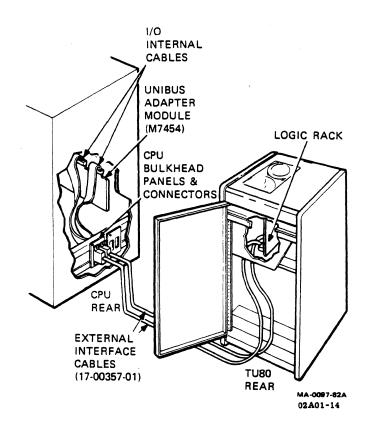

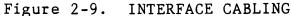

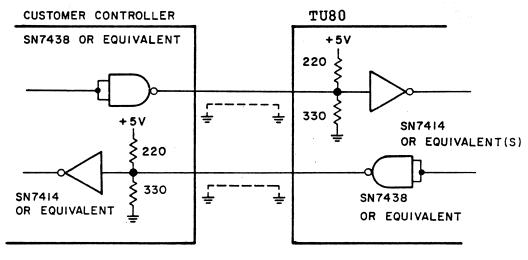

The M7454 UNIBUS Adapter Module is a standard quad-height module and is positioned in a Small Peripheral Controller (SPC) slot of the host computer backplane. The M7454 is connected to the TU80 transport by a set of internal and external interface cables (Figures 2-9 and 2-10).

When the M7454 has to be installed in the CPU (at the time of subsystem installation or module replacement), the installation procedure includes M7454 preparation (adress switch checking or setting), M7454 installation in the SPC slot, and interface cabling. Refer to the following paragraphs and figures for required information.

If the M7454 is already installed in the CPU (the turn-key system configuration), proceed directly to the TU80 External Cabling (paragraph 2.5.3).

2.5.1 M7454 Preparation and Installation

#### NOTE

#### Use the CPU Kit (TU80K-CP).

- Remove M7454 module, cables, bulkhead connectors, and mounting brackets from CPU kit shipping container. Unwrap them and examine for any physical damage.

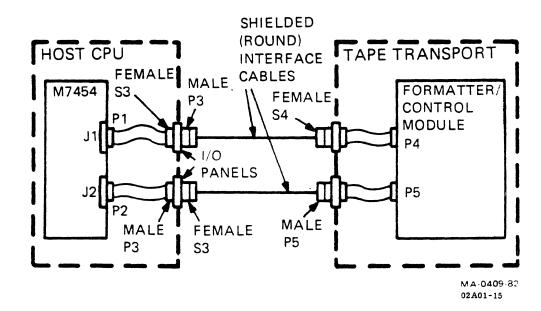

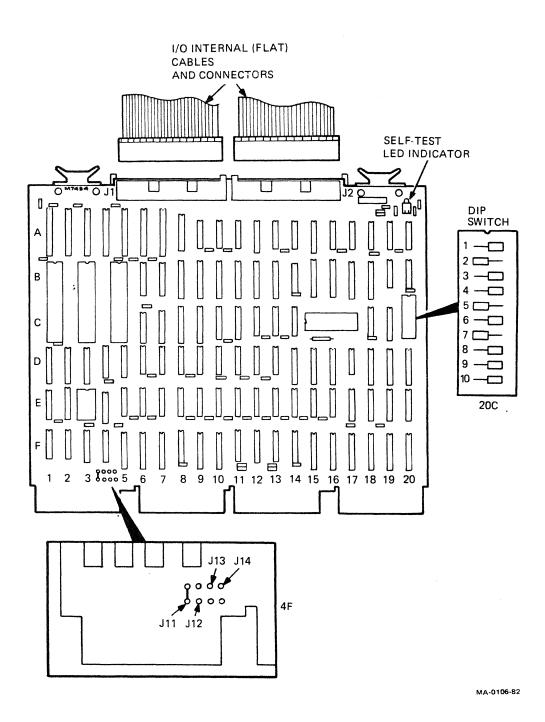

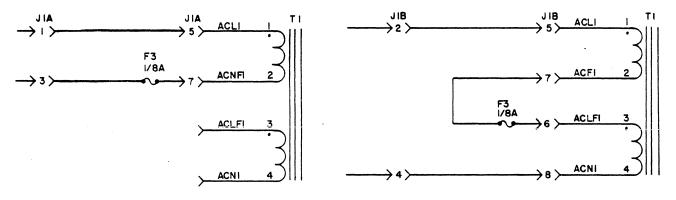

- On M7454 adapter module, check (and if necessary, select) the proper UNIBUS address, interrupt vector, and word burst on a single, 10-position DIP switch in location 20C (Figures 2-11 and 2-12).

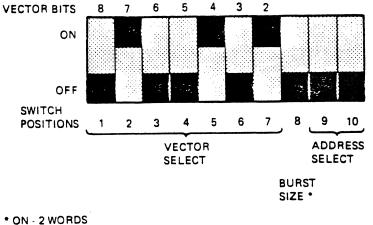

Figure 2-10. PLUG-TO-PLUG INTERFACE CABLE CONNECTIONS

Figure 2-11. DIP SWITCH ON M7454 MODULE

OFF - 4 WORDS

MA-0107-82 02A01-17

Figure 2-12. DIP SWITCH SETTING IN A SINGLE TU80 CONFIGURATION

#### NOTES

1. The typical UNIBUS Address and Vector for a single TU80 Subsystem configuration are specified in Table 2-1.

When more than one (up to four) of the TU80 Subsystems are installed with the host system, the UNIBUS Addresses and Vectors are selected according to Table 2-2.

2. Switch positions 1 thru 7 are used to select vector bits 8 thru 2. Switch position 8 is used to select 2-word or 4-word burst size. Two-word burst size is used for UNIBUS operation. Switch positions 9 and 10 are used to determine a transport number and corresponding UNIBUS Address.

#### CAUTION

Check the jumpers in location 4F on the module. Jumpers Jll thru Jl4 are used to select the UNIBUS Address Range. The standard position (Jll is in) is shown in Figure 2-11. The standard starting address is 7725228.

JUMPERS ARE FACTORY-SET. DO NOT MOVE THEM WHEN IN VAC OR PDP CONFIGURATION. These jumpers must be moved if the address range has to be moved.

- 3. Plug two internal ribbon cables (NOT KEYED CONNECTORS) into J1 and J2 edge connectors on M7454 module (Figure 2-10). Plug cable with male external connector into J2 and cable with female external connector into J1 on board.

- Remove G727 bus grant card from desired SPC slot. Remove Non-Processor Grant (NPG) jumper (cut CAl to CBl) in SPC slot.

- 5. Carefully insert M7454 module into SPC slot.

| UNIT<br>NO. | ADDRESS           | VECTOR       | SW.9 | SW.10 |

|-------------|-------------------|--------------|------|-------|

| 0           | 1725228<br>F52216 | 2248<br>9416 | ON   | ON    |

Table 2-1. SINGLE-TU80 ADDRESS SELECTION

| TRANSPORT | UNIT<br>NO. | ADDRESS                                   | VECTOR       | SW.9 | SW.10 | CONFIGURATION         |

|-----------|-------------|-------------------------------------------|--------------|------|-------|-----------------------|

| 1         | 0           | 172522 <sub>8</sub><br>F552 <sub>16</sub> | 2248<br>9416 | ON   | ON    | (Unit O)              |

| 2         | 1           | 172526 <sub>8</sub><br>F556 <sub>16</sub> | float*       | ON   | OFF   | 1 (Units 0,1)         |

| 3         | 2           | 172532 <sub>8</sub><br>F55A <sub>16</sub> | float*       | OFF  | ON    | 3 (Units 0,<br>1,2)   |

| 4         | 3           | 172536 <sub>8</sub><br>F55E <sub>16</sub> | float*       | OFF  | OFF   | 4 (Units 0,<br>1,2,3) |

Table 2-2. ADDRESS SELECTION IN MULTI-TU80 CONFIGURATION

\* Floating Vector: 300 to 7008

#### 2.5.2 CPU Internal Cabling

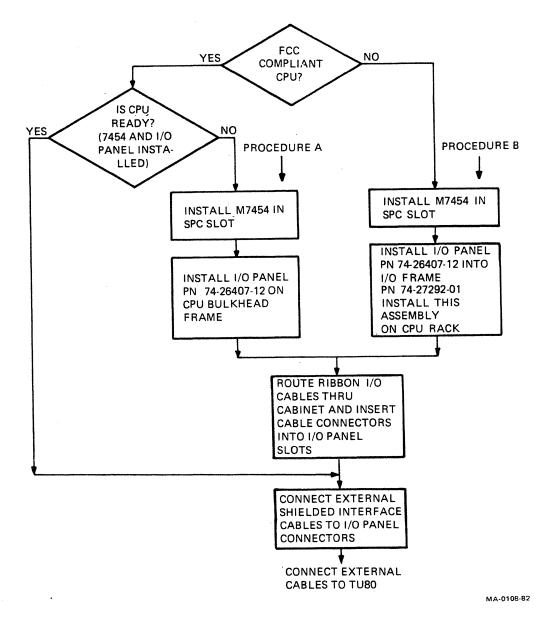

Examine the CPU for compliance with the FCC installation specifications. According to the FCC requirements, the CPU should have the I/O bulkhead connector frame at the rear bottom of its cabinet. Then follow the flowchart (Figure 2-13) and use the applicable procedures.

#### 2.5.2.1 Procedure A

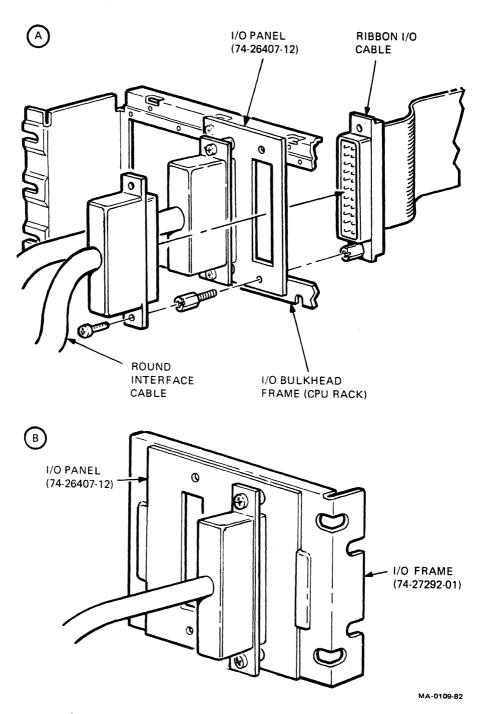

Install the I/O panel (P/N 74-26907-12) on the CPU's I/O bulkhead frame at the bottom of the CPU cabinet (Figure 2-14A). Secure the I/O panel with two screws.

Figure 2-13. I/O CABLING FLOWCHART

Figure 2-14. I/O CABLE INSTALLATION

- 2. Route the internal I/O ribbon cables from the M7454 module through the CPU cabinet to the CPU frame and insert the cable connectors into the slots on the I/O panel.

- 3. Proceed with external interface cabling.

Use care not to chafe the internal cables against other modules and chassis parts.

#### 2.5.2.2 Procedure B

- 1. Mount the I/O panel (P/N 74-26407-12) on I/O frame (P/N 74-27292-01) and secure with two screws (Figure 2-14).

- 2. Install the I/O frame (with I/O panel) on the CPU rack. Find the best location in the CPU rack to accommodate internal and external interface cabling.

#### NOTE

Most recommended location for the I/O frame is at the rear bottom of the CPU cabinet.

- 3. Repeat steps 2 and 3 above.

- 2.5.3 TU80 External Cabling

#### NOTE

Use the Accessory Kit TU80K-AC.

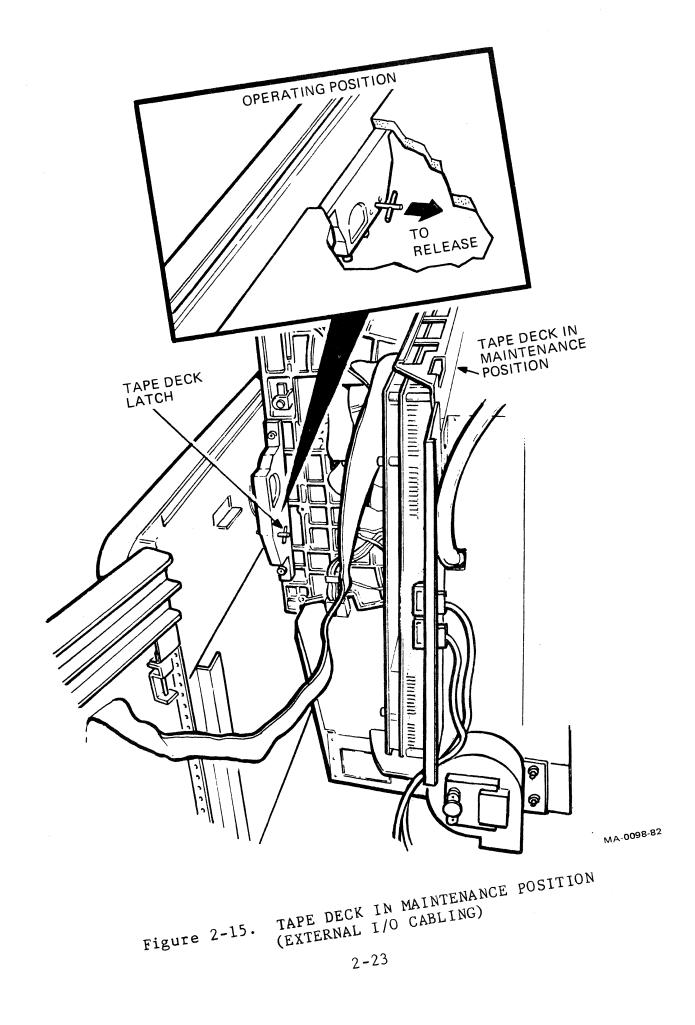

- 1. On the TU80 transport, open top cover. Use a screwdriver to loosen pawl fastener on left side of tape deck near magnetic head assembly.

- 2. Open front door using an allen wrench.

- 3. Locate service lock (deck latch) (Figure 2-15) under tape deck on left side of cabinet. Pull on service lock handle to release it. Keep it in this position.

- 4. Tilt tape deck upward until it is in vertical (service) position.

#### NOTE

Listen for a click indicating that tape deck is locked in this position.

#### CAUTION

Be sure not to snag control panel cable on any other cables within TU80 cabinet.

- 5. Open TU80 rear door. Route external shielded interface cables (P/N 17-00357-01) from CPU back-to-front of cabinet (Figure 2-9).

- 6. Insert cables into respectively keyed bracket connectors on logic rack mounting plate (refer to Figure 2-10 for plug-to-plug cable connections). Secure each plug with two flat-head screws.

- 7. On the CPU side, insert interface cables into respectively keyed bulkhead connectors on CPU I/O frame (or bracket). Secure each plug with two screws (Figure 2-14).

- 8. Release tape deck latch and tilt tape deck downward to horizontal position.

- 9. Close front and rear doors.

2.6 TU80 ACCEPTANCE DIAGNOSTIC TESTS This chapter lists all tests necessary to perform to properly check and accept the TU80 Tape Subsystem after its installation.

2.6.1 TU80 Acceptance Test Listing

2.6.1.1 Resident Diagnostics

- 1. Power-Up Health Check

- 2. Basic Operator Diagnostic Test (Test 01)

- 3. UNIBUS Adapter Module Internal Diagnostic

2.6.1.2 Host Diagnostics

- 1. PDP-11 Front End Diagnostic

- 2. PDP-11 Data Reliability Diagnostic

- 3. VAX Front End Diagnostic

- 4. VAX Data Reliability Diagnostic

Refer to the Diagnostic Documentation of the installed DEC computer for the applicable information on how to run and interpret the Host Diagnostics.

Chapter 5.4 in the Maintenance Section of this manual provides detailed information of the TU80 Diagnostics. Follow the instructions in this chapter on how to initiate and run the TU80 Diagnostic Tests.

2.6.2 TU80 Acceptance Test Procedure TU80 acceptance testing starts with the off-line resident diagnostic to check the tape transport performance and continues with the on-line diagnostic to test the TU80 Tape Subsystem. The acceptance Testing must be performed in the following steps:

2.6.2.1 Power-On Health Check - This self-test diagnostic checks ac power and functionality of the control panel and major logic modules of the TU80 Tape Transport. To start the health check, press the LOGIC-ON pushbutton (assume that the power switch is on).

2.6.2.2 Basic Operator Test Ol - This test checks basic transport functions and tape motions including BOT/EOT tape motion, read data, and write data. A write enabled, known good quality tape should be used for this test. This test runs to completion in approximately 10 minutes (with a 2400 foot long tape).

2.6.2.3 M7454 UNIBUS Motion Self-Test - The M7454 module performs the built-in self-test at the host system power-up. To run this diagnostic test, the host CPU must be turned off/ turned on. The M7454 self-diagnostic checks the M7454's microprocessor, sequencer data paths, and buffer area. Successful test completion is indicated by the illuminated LED indicator on the module.

2.6.2.4 Host Diagnostics - Depending on the host system's model, either PDP11 or VAX Diagnostics should be performed to chekc the TU80 on-line performance.

3.1 GENERAL

This section contains an explanation of the TU80 Control Panel and instructions on the tape loading and unloading procedures. Instructions are also provided for operator corrective actions for specific malfunctions indicated by the fault code display panel.

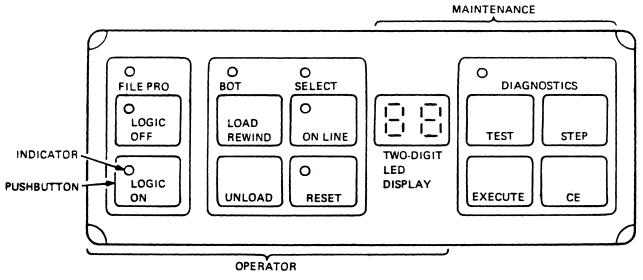

#### 3.2 CONTROL PANEL

Figure 3-1 shows the TU80 control panel switches and status indicators. The left side of the control panel contains operator switches/indicators. The 2-digit display is used to indicate a fault code related to an abnormal operating condition or a test code when in the diagnostic mode. The right side of the panel contains the switches for running the internal diagnostic tests.

MA-0083-82 02A01-21

Figure 3-1. CONTROL PANEL

### Table 3-1. OPERATOR CONTROLS

| SWITCH/INDICATOR | FUNCTION                                                                                                                                                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LOGIC OFF        | Switch - When depressed, power will be<br>removed from transport logic circuitry<br>and LOGIC OFF indicator turns on.                                                                                                                                                                                                             |

|                  | Indicator - When illuminated, indicates a<br>standby power condition exists (power<br>supply is on, cooling fan starts turning,<br>and transport logic is off).                                                                                                                                                                   |

|                  | If indicator is off with no other<br>indicators on, then POWER switch (circuit<br>breaker) is off (0) or there is a power<br>supply problem. If this indicator is off<br>and LOGIC ON indicator is on, all<br>transport circuitry is in power-on<br>condition and ready for use.                                                  |

| LOGIC ON         | Switch - If depressed when POWER switch<br>(circuit breaker) is on (1), the<br>transport logic and control system is<br>powered up.                                                                                                                                                                                               |

|                  | Indicator - When on, indicates transport circuitry is powered up.                                                                                                                                                                                                                                                                 |

| BOT              | Indicator - When on, indicates tape is<br>positioned at beginning-of-tape (BOT)<br>marker.                                                                                                                                                                                                                                        |

| LOAD/REWIND      | Switch - If transport is powered on and<br>tape is threaded, depressing this switch<br>causes a load operation to be performed.<br>If tape is loaded, depressing the switch<br>causes a rewind operation to BOT.                                                                                                                  |

| UNLOAD           | Switch - If tape is loaded at BOT,<br>depressing this switch causes tape to<br>unload from take-up reel and tape path<br>onto supply reel. If is tape is loaded<br>beyond BOT, it rewinds to BOT. If tape<br>is threaded, but no loaded, depressing<br>the switch will cause transport to slowly<br>unload tape onto supply reel. |

|                  |                                                                                                                                                                                                                                                                                                                                   |

### Table 3-1. OPERATOR CONTROLS (Cont'd)

| SWITCH/INDICATOR    | FUNCTION                                                                                                                                                                                                                                               |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON-LINE             | Switch - If tape is loaded, depressing<br>this switch causes TU80 to go on-line and<br>become accessible by the host system.<br>Depress RESET switch to take TU80<br>off-line.                                                                         |

|                     | Indicator - When on, it indicates that<br>TU80 is in on-line mode. All switches<br>except RESET and LOGIC OFF are inhibited.                                                                                                                           |

| FILE PRO            | Indicator - When on, indicates absence of<br>a write enable ring in supply reel and a<br>write operation is inhibited. Otherwise,<br>a write operation is allowed.                                                                                     |

| SELECT              | Indicator - When on, indicates that TU80<br>is selected by host system for read/write<br>operation.                                                                                                                                                    |

| RESET               | Switch - When depressed, this switch<br>places transport off-line, stops tape<br>motion, and clears error status. The<br>switch can stop a load or rewind<br>operation. It also turns off RESET<br>indicator and clears diagnostic test<br>conditions. |

|                     | Indicator - When on, indicates that TU80<br>is in a fault or diagnostic status. A<br>2-digit display may contain a fault or<br>diagnostic code.                                                                                                        |

| Diagnostic Controls |                                                                                                                                                                                                                                                        |

| DIAGNOSTIC          | Indicator - When on, indicates that TU80<br>is in diagnostic/test mode. The<br>indicator remains on until RESET switch<br>is depressed.                                                                                                                |

| TEST                | Switch - If tape is threaded, but not<br>loaded, depressing this switch places<br>unit in diagnostic/test mode.                                                                                                                                        |

| STEP                | Switch - In the diagnostic/test mode,<br>depressing this switch causes diagnostic/<br>test sequence numbers in 2-digit display<br>to be incrmented to digit required.                                                                                  |

#### Table 3-1. OPERATOR CONTROLS (Cont'd)

| SWITCH/INDICATOR | FUNCTION                                                                                                                                                                                                                                    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXECUTE          | Switch - In the diagnostic/test mode (and<br>test number displayed), depressing this<br>switch initiates the diagnostic test.                                                                                                               |

| CE               | Switch - If TU80 is in diagnostic/test<br>mode, simultaneously depressing the CE<br>(Customer Engineer) switch and TEST<br>switch recalls an internal diagnostic<br>routine (Field Service Tests) to aid a<br>Field Service Representative. |

#### Operator Hints

- 1. When LOGIC ON indicator is on, all control panel switches and indicators are functional except LOGIC OFF indicator.

- 2. The ON-LINE switch can be depressed while tape is loading. The TU80 goes on-line immediately when loaded.

- 3. When RESET indicator is on, the control panel is not operable except for LOGIC OFF and RESET switches. To turn indicator off, press RESET switch.

- 4. Tape unloading is performed at low speed. If there is a lot of tape on take-up reel, and you wish to do it more quickly, you can do it faster by depressing LOAD/REWIND first and then UNLOAD.

#### 3.3 OPERATING PROCEDURE

The operating procedure includes preparing and loading the tape reel, powering on the transport, placing it on-line to the host computer, and checking its operational status. If a fault code appears on the 2-digit display during loading or routine operation, refer to section 3.4, Operator Corrective Actions.

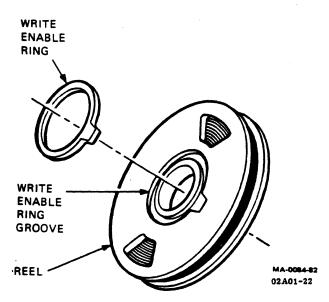

3.3.1 Inserting Write Enable Ring Before mounting the reel of tape onto the supply hub, determine whether or not the tape is to be recorded (write operation performed). If write operations are to be performed, place a write enable ring into the bottom recessed portion of the reel (Figure 3-2).

Figure 3-2. WRITE ENABLE RING

3.3.2 Tape Threading and Loading Perform this procedure to thread and load tape.

1. Pull cover latch towards the front and lift top access cover. Check that power switch is in ON position (1 depressed). The LOGIC OFF indicator should be on.

#### NOTE

The power switch can be in the ON position all the time to enable the TU80 transport to be powered on under CPU control.

2. Depress the LOGIC ON switch. The power-up health check is initiated. The LOGIC OFF indicator goes off and all other indicator momentarily go on. The LOGIC ON and FILE PRO indicators should remain on.

#### NOTE

Depressing the LOGIC ON switch enables the transport power amplifier module, control logic, and support circuits. If a fault code is displayed at this time, depress the RESET and LOGIC OFF switches and then LOGIC ON switch again to repeat the check. If the fault code persists, call Field Service.

- 3. Depress inner button on the face of supply reel hub.

- 4. Mount supply reel onto hub so that reel is seated on bottom flange. Secure reel by depressing the periphery of the hub face to latch the reel.

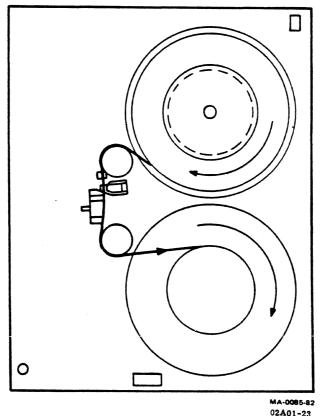

- 5. Thread magnetic tape through tape path as shown in Figure 3-3.

- 6. Wrap tape leader (a length of tape before BOT marker) onto take-up reel for several turns.

#### CAUTION

Make sure that tape is positioned correctly over all tape path components, otherwise, tape damage may occur.

7. Close and latch top cover.

Figure 3-3. TAPE PATH

8. Depress LOAD/REWIND switch. In 1 second, air pressure builds at air bearings and tape starts moving in forward direction. This motion stops when BOT marker on tape is detected. If tape was over-threaded and BOT marker was positioned after sensor, forward tape motion continues for approximately 40 feet. Then the transport initiates reverse tape motion until BOT marker is detected. At this moment, tape motion stops and BOT indicator is on.

#### NOTE

If LOAD fails and tape does not move to BOT, check for BOT marker on tape.

9. Depress ON-LINE switch to place unit on-line to the host system. The switch may be depressed while load operation is in progress. On completion of a load operation, the transport indicates ON-LINE status by turning ON-LINE indicator on. (If the transport is ready for a write operation, the FILE PRO indicator goes off.) Now the transport is ready for use.

3.3.3 Tape Unloading

The following are procedures for unloading tape manually or in on-line mode.

3.3.3.1 Manual Mode - Perform this procedure to unload tape manually.

- 1. Depress RESET switch to place transport off-line.

- 2. Depress UNLOAD switch. Tape moves in reverse direction (rewind) sently winding onto supply reel reel until it clears take-up reel and tape path.

#### NOTE

If loaded beyond the BOT marker, tape rewinds to BOT.

- 3. Open top cover and depress center button of supply reel hub. The hub unlatches and supply reel can be removed.

- 4. Close top cover to prevent dust accumulation on tape deck components.

3.3.3.2 On-Line Mode - When on-line to the host CPU, the unload operation can be performed under CPU control.

#### 3.4 OPERATOR CORRECTIVE ACTIONS

If a fault condition is indicated on the control panel (RESET indicator is on and a fault code is indicated on the digital display), refer to the Fault Recovery Table on the inside of the top cover (also Table 3-2 below) and to the Fault Code Matrix, Table 5-2, in section 5.4 of this manual.

#### Table 3-2. OPERATOR CORRECTIVE ACTIONS

| FAULT CODE | CORRECTIVE ACTION                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------|

| 01 - 09    | Clean magnetic head and tape path.                                                                         |

| 10         | Ensure cover door is securely closed.                                                                      |

| 11         | Thread tape.                                                                                               |

| 12         | Latch supply reel hub.                                                                                     |

| 13         | Thread tape correctly as shown on tape threading diagram.                                                  |

| 14         | Check for BOT marker on tape. Attach BOT/EOT marker.                                                       |

| 15         | Indicates RESET switch depressed inadvertently by operator. Reinitiate test.                               |

| 16         | Check for presence of write enable ring in supply tape reel. Install the ring if not present.              |

| 17         | Check for presence of EOT marker. Attach EOT marker.                                                       |

| 18         | Initiates that tape was loaded when test was<br>initiated. Thread tape, but DO NOT depress LOAD<br>switch. |

| 20 - 29    | Mount a tape of known good quality.                                                                        |

| All Others | Attempt to run Diagnostic Test Ol (refer to section 5.4).                                                  |

#### Section 4 - THEORY

4.1 GENERAL DESCRIPTION

This section of the manual discusses the principles of operation of the TU80 Tape Unit. Descriptions are provided for all functions of the TU80 on a major component basis. Major areas of discussion are as follows:

- o Power Generation and Distribution

- o Pneumatic System

- o Read/Write/Servo Board Functions

- o Formatter/Control Functions

- o Power Amplifier Operation

- o Head Operation/Recording

- o Interface and Timing Considerations

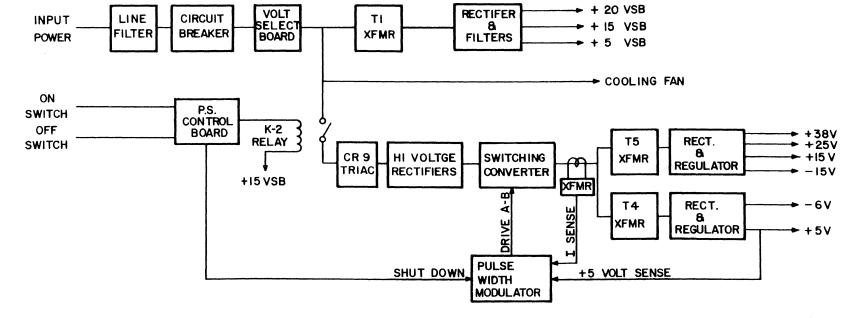

Text is supported by diagrams, flowcharts and timing charts, where required, to simplify understanding of the description. Diagrams contained herein are condensed and simplified and, in no way, should they be used for TU80 troubleshooting. Logic diagrams and schematics contained in the Field Service Print Set take preference over any diagrams contained in the theory of operation. Refer to Figure 4-1 for a block diagram of the TU80.

A brief functional description of major areas of the TU80 Tape Unit is given in succeeding paragraphs. A more detailed circuit description is then discussed with accompanying block diagrams and flowcharts.

#### NOTE

The TU80 Subsystem description and operation is presented in Appendix A of this manual along with the description of the M7454 UNIBUS Adapter Module.

4.2 PHYSICAL DESCRIPTION

The TU80 is a manual load, reel-to-reel tape drive unit requiring no capstan drive, tension arms or vacuum columns. Tape is transported directly under electronic control, with no tape buffers required. Tension is sensed electronically by tension sensors built directly into the tape path. The five major equipment components or subsystems are Formatter/Control logic, Servo circuits, Read/Write Head assembly and circuits,

Figure 4-1. TU80 FUNCTIONAL BLOCK DIAGRAM

Pneumatics/Cooling systems, and the Power Supply and Distribution circuitry. The following paragraphs give a brief description of the overall TU80 functions.

#### 4.2.1 Power Supply

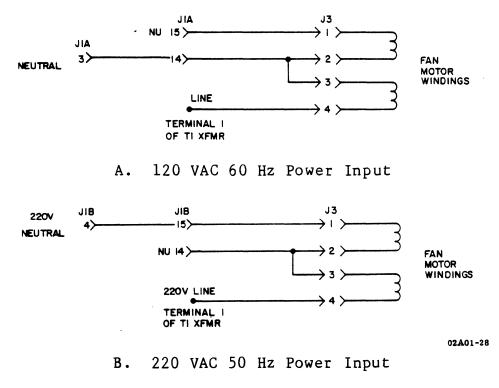

The power supply is activated when the ON/OFF power switch (main circuit breaker) is in the ON position. This allows the LOGIC OFF indicator on the control panel to illuminate, and also supplies the AC power to operate the cooling fan motor.

Pressing the LOGIC ON switch generates all the necessary DC voltages used throughout the TU80 logic circuits, as well as initiating a MASTER CLEAR pulse. This pulse is used to steer the control logic functions to a starting or known state prior to starting a Load operation.

#### 4.2.2 Tension/Speed Control

The Load function is initiated by the LOAD switch on the control panel. The pneumatic pump is activated at this time, causing air pressure to be gated to the air bearings. Air pressure gated through holes in the bearings actually senses the tension of the tape through sensors physically located on the air bearings. The sensor output signals are applied to a tension servo circuit, whereby, the supply (file) reel is directed to drive so that a constant tension of approximately 8 ounces is maintained across the tape path at all times.