# NCR ARCNET® CONTROLLER/TRANSCEIVER

#### **FEATURES**

- Supports Buffer Chaining in external SRAM

- Fully controls 8K bytes of external SRAM containing host messages

- Requires only half the number of wait states as NCR90C26 to release the host bus

- Supports three Reset Options

- Power-On-Reset (no external signal required)

- · External Reset

- Software Generated Reset

- 20 MHz On-chip Oscillator

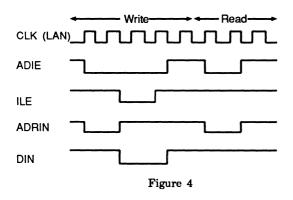

- ADRIN & DIN signals are provided to multiplex address and data

- Flexible microprocessor interface

- Supports broadcast messages to all nodes on LAN

- Token Passing Protocol provides predictable transfer intervals

- Network supports up to 255 nodes

- Maximum distance between active elements is 650 meters, total system distance 6500 meters.

- Data transferred at 2.5 Megabits per second

- Automatically reconfigures when the number of nodes change

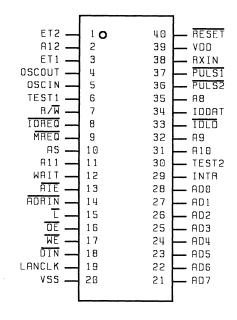

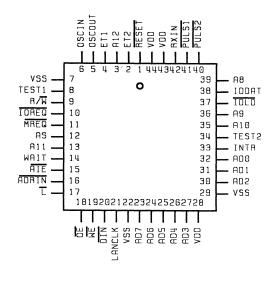

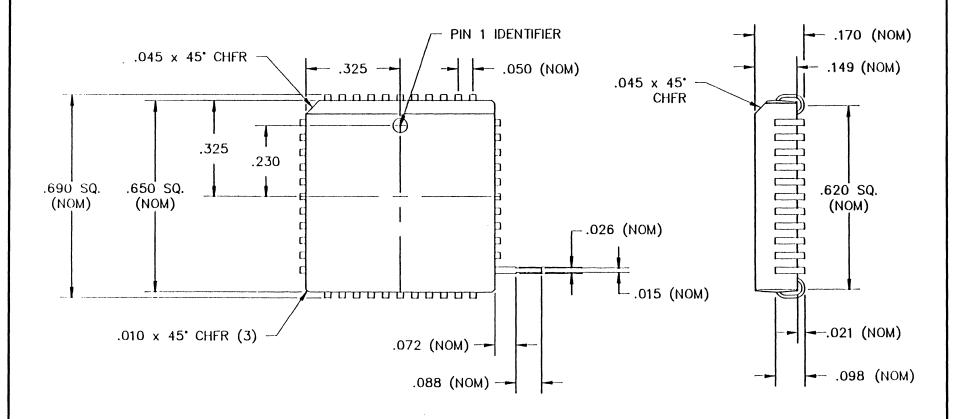

- Available in 40-pin DIP and 44-pin PLCC

44-pin PLCC

Figure 1 40-pin DIP and 44-pin PLCC

ARCNET is a Registered Trademark of Datapoint Corporation

Pin Out Summary

| Pin Out Summ            |        |            | Ī           |                                         |  |

|-------------------------|--------|------------|-------------|-----------------------------------------|--|

| Signal Name             | Туре   | 40-pin DIP | 44-pin PLCC |                                         |  |

| RESET                   | Input  | 40         | 1           | Reset                                   |  |

| ET2                     | Input  | 1          | 2           | Extended timeout functions              |  |

| A12                     | Output | 2          | 3           | Page Select                             |  |

| ET1                     | Input  | 3          | 4           | Extended timeout functions              |  |

| OSCOUT                  | Output | 4          | 5           | Output from internal OSC                |  |

| OSCIN                   | Output | 5          | 6           | Input to internal OSC or external clock |  |

| $V_{\rm SS}$            | Ground | -          | 7           | Ground                                  |  |

| TEST1                   | Input  | 6          | 8           | Test pin 1                              |  |

| R∕₩                     | Input  | 7          | 9           | Read/Write                              |  |

| <b>IOREQ</b>            | Input  | 8          | 10          | I/O request                             |  |

| $\overline{	ext{MREQ}}$ | Input  | 9          | 11          | Memory request                          |  |

| AS                      | Input  | 10         | 12          | Address Strobe                          |  |

| A11                     | Output | 11         | 13          | Page select                             |  |

| WAIT                    | Output | 12         | 14          | Wait                                    |  |

| ĀĪĒ                     | Output | 13         | 15          | Address input enable                    |  |

| ADRIN                   | Output | 14         | 16          | Address/data input enable               |  |

| Ī                       | Output | 15         | 17          | Latch                                   |  |

| ŌĒ                      | Output | 16         | 18          | Output enable                           |  |

| WE                      | Output | 17         | 19          | Write enable                            |  |

| DIN                     | Output | 18         | 20          | Data input latch signal                 |  |

| LANCLK                  | Output | 19         | 21          | Network clock                           |  |

| Vss                     | Ground | 20         | 22          | Ground                                  |  |

| AD7                     | In/Out | 21         | 23          | Address/data bus pin                    |  |

| AD6                     | In/Out | 22         | 24          | Address/data bus pin                    |  |

| AD5                     | In/Out | 23         | 25          | Address/data bus pin                    |  |

| AD4                     | In/Out | 24         | 26          | Address/data bus pin                    |  |

| AD3                     | In/Out | 25         | 27          | Address/data bus pin                    |  |

| $V_{ m DD}$             | Power  | -          | 28          | +5 volt supply                          |  |

| Vss                     | Ground | 20         | 29          | Ground                                  |  |

| AD2                     | In/Out | 26         | 30          | Address/data bus pin                    |  |

| AD1                     | In/Out | 27         | 31          | Address/data bus pin                    |  |

| ADO                     | In/Out | 28         | 32          | Interrupt                               |  |

| INTR                    | Output | 29         | 33          | Test pin 2                              |  |

| TEST2                   | Input  | 30         | 34          | Page select                             |  |

| A10                     | Output | 31         | 35          | Page select                             |  |

| A9                      | Output | 32         | 36          | ID load                                 |  |

| ĪDLD                    | Output | 33         | 37          | ID load                                 |  |

| IDDAT                   | Input  | 34         | 38          | ID data in                              |  |

| A8                      | Output | 35         | 39          | Address line 8                          |  |

| PULS2                   | Output | 36         | 40          | Pulse 2 (transmitter out)               |  |

| PULS1                   | Output | 37         | 41          | Pulse 1 (transmitter out)               |  |

| RXIN                    | Input  | 38         | 42          | Receive data in                         |  |

| V <sub>DD</sub>         | Power  | 39         | 43          | +5 volt supply                          |  |

| $V_{ m DD}$             | Power  | -          | 44          | +5 volt supply                          |  |

| עט ז                    | TOMEI  |            | 77          | I to told supply                        |  |

#### **GENERAL DESCRIPTION**

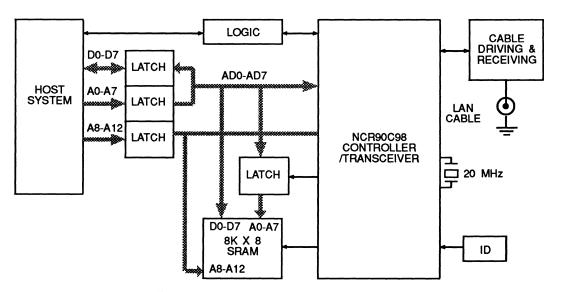

The NCR90C98 Controller/Transceiver includes all logical functions of an ARCNET RIM (Resource Interface Module - see Figure 2). CMOS technology makes it ideal for low-power applications. ARCNET is a popular token-passing Local Area Network (LAN) scheme developed by Datapoint Corp. The NCR90C98 handles all tasks for transferring data between the node and the LAN. It reads and writes Message Buffers in an external RAM, it initiates and responds to valid ARCNET transmissions, and passes control between itself

and the other RIMs on the network. The NCR90C98 also contains the interface to the cable-driving circuitry that hooks up to the physical LAN media.

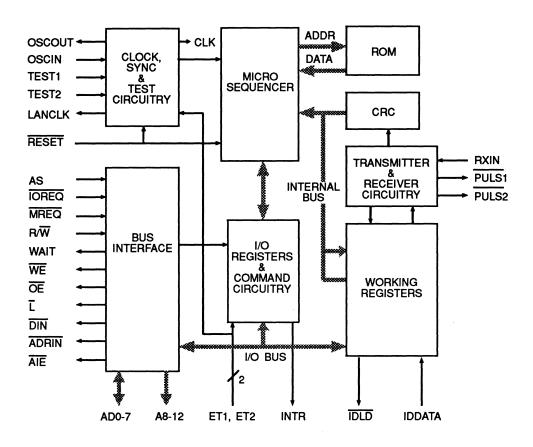

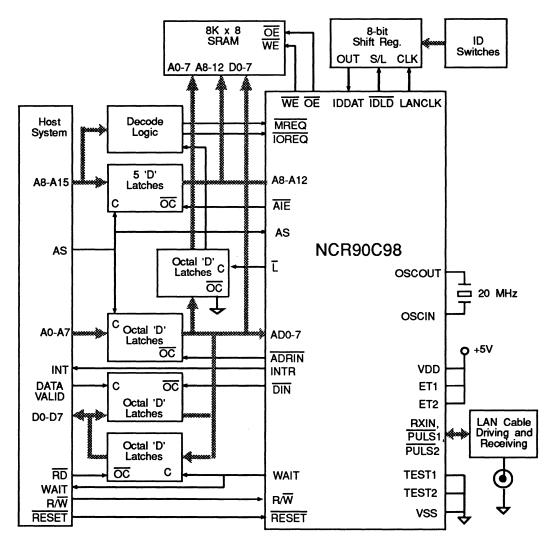

The NCR90C98 is an enhanced single-ichip version of the NCR90C26 and NCR90C32 combining the ARCNET controller and transceiver functions. A few of the enhancements include increased buffer size, buffer chaining, and an on-chip POR cell and oscillator. (See Figure 3.)

Figure 2 RIM Simplified Block Diagram

Figure 3 Chip block diagram

#### **NEW FEATURES**

The new features on the NCR90C98 make ARCNET interfaces easier to implement. The new features are:

- Buffer Chaining. Buffer Chaining lessens the overhead required by the host when receiving or transmitting multiple message packets. This increases throughput, especially in server applications.

- On-chip Power-On-Reset (POR) cell. The POR

Cell reduces the number of external components required by putting all Power On

Reset circuitry on-chip.

- On-chip Oscillator. The on-chip oscillator permits the replacement of the external crystal oscillator with a crystal.

- Reduces the wait states during host accesses.

The arbitration circuitry services host access requests in half the time required by the NCR90C26.

- Increased Buffer Size. The NCR90C98 is now capable of supporting 8K of buffer RAM. This allows the system to support multiple transmit and receive buffers.

Simplified Interface control Lines. The ADRIN and DIN signals simplify the circuitry for controlling Address and Data on the bus.

# PINOUT DIFFERENCES BETWEEN THE NCR90C26 AND THE NCR90C98

The Integration of the NCR90C26 and NCR90C32 into a single chip eliminated the following signals:

- CA

- TX

- DSYNC

In addition the following signals were eliminated because they now have little or no value to the system designer.

- DWR

- REQ

- CKSEL

- TTLCLK

- BLNK

- INHTX

The following new pins were added because of the on-chip oscillator and the expanded RAM buffer address space.

- OSCIN

- OSCOUT

- A11

- A12

The following signals have changed logically to accommodate non-multiplexed address and data bus.

- ADIE to ADRIN

- ILE to DIN

#### **ARCNET OVERVIEW**

#### LINE PROTOCOL

The NCR90C98 implements an asynchronous line protocol, with each Information Symbol Unit (ISU) consisting of the following:

- 2 clock units of mark (logic 1),

- 1 clock unit of space (logic 0), and

- 8 clock units of data (the ISU).

A single clock unit is 400 nanoseconds in duration, so a byte of data is transmitted every 4.4 (400 ns x 11 clock units) microseconds. Thus, the time to transmit any message can be determined exactly. All transmissions start with an ALERT BURST, which is 6 clock units of mark. The line idles in a spacing condition. The five types of ARCNET transmissions follow:

#### Invitations To Transmit

An ALERT BURST followed by three ISUs: one EOT (End of Transmission) and two repeated DID (Destination IDentification) ISUs. This message passes control (the "token") from one node to another

#### Free Buffer Enquiries

An ALERT BURST followed by three ISUs: one ENQ (ENQuiry) and two repeated DID ISUs. This message asks another node if it is able to accept a message packet.

#### **Packets**

An ALERT BURST followed by 8 to 260 ISUs:

- one SOH (Start Of Header) ISU

- one SID (Source IDentification) ISU

- two repeated DID ISUs

- an inverse COUNT ISU = 256-N, for N data ISUs to be sent

- from 1 to 253 data ISUs

- two CRC (Cyclic Redundancy Check) ISUs

#### Acknowledgments

An ALERT BURST followed by a single ACK (ACKnowledgment) ISU. This message is used as a positive response to FREE BUFFER ENQUIRIES, and also to acknowledge the valid reception of a PACKET.

#### Negative Acknowledgments

An ALERT BURST followed by a single NAK (Negative Acknowledgment) ISU. This message gives a negative response to FREE BUFFER ENQUIRIES.

#### Line Protocol Notes:

- The codes (all in HEX) for the special ISUs mentioned above follow.

- EOT 04

- ENQ 85

- SOH 01

- ACK 86

- NAK 15

- The COUNT ISU for PACKETS may be equal to (512 N) if a "long packet" is being sent. The CRC polynomial used for data packets is: X<sup>16</sup> + X<sup>15</sup> + X<sup>2</sup> + 1.

- As a receiving node, the NCR90C98 will verify all incoming transmissions by checking for:

- At least one mark and exactly one space preceding each ISU.

- A valid EOT, ENQ, SOH, ACK, or NAK following the ALERT BURST.

- Proper CRC for data packets.

- Correct number of ISUs, depending on the transmission

#### **NETWORK CONTROL**

All nodes in an ARCNET system are distinguished by a unique 8 bit ID (IDentification) value. This value is configurable with DIP switches associated with each NCR90C98 chip. An ID of '0' may not be

assigned to any node, since that ID indicates a BROADCAST to all nodes. Control of the Local Area Network (LAN) is based on token passing. In order to send a message a node must first receive the token. The token is received in an INVITATION TO TRANSMIT message containing its own ID. To send a message, the host processor loads the message data and the destination ID into its NCR90C98's buffer RAM. Then the host writes an "Enable Transmit" command to the NCR90C98. The NCR90C98 will know it has a message to send if the TA (Transmitter Available) bit in its Status Register is LOW. When the NCR90C98 has the token, it then transmits a FREE BUFFER ENQUIRY to the destination ID to see if it is able to receive the message. If the destination is able to receive, it transmits an ACK back to the controlling node. The controlling node then transmits the PACKET, complete with a 16-bit CRC. If there is no activity after sending this message, a "time out" (74.7 µs) occurs (see Timecheck Function Section). Upon Timeout, the NCR90C98 sets its TA bit, and passes the token. When an NCR90C98 receives the token, but its TA bit is high (it has no message to send), it sends an INVITATION TO TRANSMIT to pass the token.

When an NCR90C98 is sent a FREE BUFFER ENQUIRY, it will poll its RI (Receiver Inhibited) Status bit. If the RI bit is set, the NCR90C98 will transmit a NAK, and the controlling node will then pass the token. If an NCR90C98 with a packet to send gets a NAK, then it will pass the token and re-transmit a FREE BUFFER ENQUIRY the next time it receives the token. If there is no activity on the line within 74.7 µs of transmitting a FREE BUFFER ENQUIRY a time out occurs (see Timecheck Function Section). The NCR90C98 increments its NID (Next ID) pointer and tries again. After it has sent a PACKET, an NCR90C98 waits a specified response time. If within that time, it receives an ACK, it sets both the TMA (Transmit Message Acknowledged) and the TA Status bits and passes the token. If it does not receive an ACK in time, it only sets TA and then passes the token.

All nodes recognize a PACKET when they see the SOH ISU, and all NCR90C98s will write the SID into their Receive Buffers. If an NCR90C98 perceives the first DID as its own, or the PACKET is a Broadcast message (see the Reconfiguration and Broadcast section), the chip will write the second DID and the rest of the message into its Receive Buffer. Otherwise, the NCR90C98 will ignore the rest of the PACKET. After the PACKET has been fully received, it must pass three conditions to be considered a valid message:

- the CRC comparison

- correct length of ISUs, and

- valid DID in byte 0 of the Receive Buffer.

Valid DIDs are either '0' (indicating Broadcast), or the NCR90C98's own ID. An ACK is sent if a message is valid by these conditions and addressed to the NCR90C98's own ID. However if the message is a broadcast message no ACK will be sent. The NCR90C98 sets its RI status bit after receiving a valid message if no more receive buffers are available. In the buffer chaining mode, the Received Packet (RP) status bit is set when a valid message is received addressed to the NCR90C98's own ID. If any of the conditions fail, the NCR90C98 ignores the message and will write over it with future PACKETS.

#### RECONFIGURATION AND BROADCAST

There are two activities that involve all nodes on the ARCNET system. These are Reconfiguration of the system and Broadcasts to the system.

A Reconfiguration of the network is performed any time a node is removed from, or added to the system. Specifically, an NCR90C98 will instigate a Reconfiguration when it is first powered on, or when it has not received an INVITATION TO TRANSMIT within 840 milliseconds. It does this by transmitting a RECONFIGURATION BURST: 8 marks and 1 space repeated 765 times. This burst has the effect of terminating all activity on the network. This burst is longer than all the other types of transmissions. Thus, it will interfere with the next INVITATION TO TRANSMIT, destroying the token and no other node will take control of the line. The RECONFIGURATION BURST also provides enough line activity so the NCR90C98 that just sent the token will also release control of the network.

When any NCR90C98 sees the line idle for 78 µs it begins a network reconfiguration cycle. It sets the internal NID (Next ID) register to its own ID. The NID is normally the DID sent with an INVITATION TO TRANSMIT. Besides resetting the NID, the NCR90C98 also starts a timeout of 146 µs times the quantity 255 minus its own ID [146 µs x (255-ID #)]. If this timeout expires with no other line activity the NCR90C98 will start transmitting INVITATIONS TO TRANSMIT, with the DID pointing to itself. Only the NCR90C98 with the largest ID value will actually timeout, however.

After sending an INVITATION TO TRANSMIT, the NCR90C98 will look for any line activity, indicating that the DID is a valid node. If the sending NCR90C98 detects no activity after 74.7 us, it increments its NID, and sends another INVITATION. Eventually, the NCR90C98 with the ID that is next, will see its ID in the INVITATION, and take control of the line. The previous NCR90C98 will then have its NID set correctly. The process repeats, with the end result that each NCR90C98 will have an NID stored representing an active node to pass the token. No time is wasted trying to send the token to nonexistent nodes. If a node is removed from an active network, then the previous node will time out when passing the token. The previous NCR90C98 goes through a cycle of incrementing its NID and transmitting INVITATIONS TO TRANSMIT until it finds the next valid node. The total time to perform a Reconfiguration will vary depending on the system configuration, but is typically between 24 and 61

A Broadcast Packet is the second operation that pertains to all the nodes in the network. A PACKET is considered to be Broadcast if the DID is a value of '0'. No regular node may be assigned the Broadcast ID. Nodes are set up to receive Broadcasts by issuing a "Write Configuration" command with the most significant bit of the command set to '1'. All the NCR90C98 commands are described in the Command Register sections.

#### TIMECHECK FUNCTIONS

A standard baseband system using RG-62 coax cable (the ARCNET standard) can take up to 31  $\mu s$  for a one-way propagation. This corresponds to a distance of about 4 miles. The maximum turnaround time that any NCR90C98 takes to respond to an incoming message is 12  $\mu s$  A maximum Response Time for any transmission is 31 + 31 + 12 = 74  $\mu s$  To allow a margin, the NCR90C98 uses 74.7  $\mu s$  as its basic Response timeout. This is the interval a controlling node expects to perceive any line activity after it makes a transmission.

An IDLE Timeout is the interval that transpires at the onset of a Reconfiguration. After the RECONFIGURATION BURST, all the nodes commence the Reconfiguration process when they detect no line activity for the Idle timeout. In a standard network, the Idle timeout is 78.2 µs The TRANSFER timeout is the ID-dependent interval that is also associated with Reconfiguration. This

timeout is given by 146 µs x (255-ID), and it transpires only for the node with the highest ID on the network. The last timeout is the interval that instigates a Reconfiguration. In a standard network, if any node has not received an INVITATION TO TRANSMIT within a Reconfiguration timeout of 840 ms, it issues a RECONFIGURATION BURST and starts a network Reconfiguration.

Table 1 Timeout Response and Reconfiguration Settings

| ET2 | ET1 | Response<br>Timeout | Reconfiguration<br>Timeout |

|-----|-----|---------------------|----------------------------|

| 1   | 1   | 74.7 μs             | 0.84 seconds               |

| 1   | 0   | 283.4 μs            | 1.68 seconds               |

| 0   | 1   | 561.8 μs            | 1.68 seconds               |

| 0   | 0   | 1118.6 μs           | 1.68 seconds               |

The timeout values in Table 1 apply to a standard, or "basic" network with no 2 nodes farther apart than 4 miles. The network may operate over longer distances by appropriate setting of the ET1 and ET2 inputs. Table 1 shows the effect of ET1 and ET2 on two of the more pertinent timeouts. It is important that ET1 and ET2 be set to the same value for all nodes on the network.

#### **HOST INTERFACE OVERVIEW**

The host accesses the NCR90C98 and associated buffer RAM over a multiplexed address/data bus. 'D'-type latches provide the interface between the host's bus and the multiplexed address/data bus. The NCR90C98 controls the activity on this bus with arbitration logic. By controlling the multiplexed bus the NCR90C98 makes sure it has access to the buffer RAM for incoming data. See Figure 2.

The host controls the ARCNET node by reading and writing the I/O registers in the NCR90C98. The host transfers all its message data with the buffer RAM. The NCR90C98 was designed to allow efficient data transfers between the host and the LAN. Buffer Chaining allows multiple packets to be transferred before service is required by the host. Simultaneous access to packet information in the buffer RAM is possible because of the arbitration logic on the NCR90C98. A dual port RAM implementation using a standard RAM is accomplished by the RAM arbitration circuitry on the NCR90C98. Since the host makes its access at arbitrary times, the NCR90C98 synchronizes the host by asserting WAIT at every access attempt by the host. In addition to passing messages, the host uses the Address-Data bus and latches to access the NCR90C98 directly. A low level on the  $\overline{IOREQ}$  at the falling edge of AS identifies I/O cycles. These are used to read the NCR90C98's status, or to write commands. A low level on the  $\overline{MREQ}$  at the falling edge of AS identifies memory cycles. These are used to read or write the buffer RAM. See Host Interface Description Section.

#### **FUNCTIONAL DESCRIPTION**

#### **BUFFER CHAINING**

This feature relieves the host from the task of enabling a new receive buffer for each packet received. It also lets the host transmit multiple packets per transmit command.

#### Packet Reception

In the receive buffer chaining mode, the NCR90C98 automatically fills all the pages that are assigned to the receive buffer. If the Circular mode is enabled, the NCR90C98 automatically restarts at the beginning of the receive buffer when the end has been reached. The NCR90C98 keeps track of available buffers and stops receiving when there are no more buffers available. The host must update the pointer that keeps track of the packets that have been read.

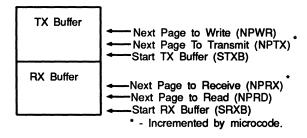

The pointers associated with the receive buffer are the Next Page to Receive (NPRX), Next Page to Read (NPRD) and Start of RX Buffer (SRXB). When a packet has been received successfully, the NCR90C98 increments the NPRX pointer and sets the RP bit which generates an interrupt. The host, after determining the source of the interrupt, reads the NPRX pointer which clears RP, reads the packet and then increments the NPRD pointer.

#### Packet Transmission

In the transmit buffer chaining mode the NCR90C98 transmits all the packets the host wrote into the transmit buffer. It is the responsibility of the host to update the pointer that points to the last packet to be transmitted. The NCR90C98 will keep track of which packets to send and when to stop. If the Circular mode has been enabled, the NCR90C98 automatically restarts at the beginning of the transmit buffer when the end has been reached.

The pointers associated with the transmit buffer are the Next Page to Write (NPWR), Next Page to Transmit (NPTX) and Start of TX Buffer (STXB). When the host wants to transmit a packet, it must write the packet into the page pointed to by the NPWR pointer. If the host wants to transmit multiple packets, it must write the packets into the subsequent pages. Then move the NPWR pointer to the page that follows the last written page. The NCR90C98 will start to transmit one packet per token when the enable transmit or enable chain transmit commands are executed. Upon a successful transmission the TA and TMA bit will be set.

See Figure 5 for a diagram depicting the relative function of each pointer. Following are brief descriptions of each pointer.

#### Next Page to Write (NPWR).

The NPWR pointer contains the page address (in the buffer RAM) for the host to write the next packet of data to be transmitted.

#### Next Page to Transmit (NPTX).

The NPTX pointer contains the page address for the next packet to be transmitted.

#### Start TX Buffer (STXB).

The STXB pointer contains the starting page address of the transmit buffer RAM. The transmit buffer memory ranges from this address to the end of memory.

#### Next Page to Receive (NPRX).

The NPRX pointer contains the page address of the next packet to be received.

#### Next Page to Read (NPRD).

The NPRD pointer contains the page address (in the buffer RAM) of the next packet to be read.

#### Start RX Buffer (SRXB).

The SRXB pointer contains the starting page address of the receive buffer RAM. The receive buffer memory ranges from this address up to the STXB page address.

Figure 5 Buffer RAM Pointer Diagram

#### PIN DESCRIPTION

#### AD0-AD7: Address/Data Bus.

These pins serve as the multiplexed eight-bit address and data bus for the NCR90C98.

During host accesses with the NCR90C98, this bus carries the data and lower address bits. During host writes data is input to the NCR90C98 over this bus. During host reads the NCR90C98 outputs data over this bus. During these accesses the lower eight address bits are input to the NCR90C98 from this bus.

During buffer RAM accesses by the NCR90C98, this bus carries the data and lower address bits. Data is output from the NCR90C98 during writes and input to the NCR90C98 during reads. The lower eight address bits are output from the NCR90C98 during both reads and writes.

During buffer RAM accesses by the host, the NCR90C98 keeps these lines at a high impedance state.

#### A8-A12: Page Select.

These outputs are the five most significant address bits to the buffer RAM. They supply the page address when the NCR90C98 accesses the RAM. These outputs are in the high impedance state when the NCR90C98 is not accessing the buffer RAM.

#### ADRIN: Address Input Enable.

The NCR90C98 uses this signal to control the host's lower address lines. When the NCR90C98 drives this signal low the host's address bus latch drives the Address-Data bus. When driven high the lower address lines driving the Address-Data bus are assumed to be in a high impedance state.

#### AIE: Address Input Enable.

The NCR90C98 uses this signal to control the host's upper address lines. When the NCR90C98 drives this signal low the host's upper address lines drive the RAM. When driven high the upper address lines to the buffer RAM are assumed to be in a high impedance state.

#### AS: Address Strobe.

On the falling edge of AS the NCR90C98 latches the state of  $R/\overline{W}$ ,  $\overline{MREQ}$ , and  $\overline{IOREQ}$ . This initiates arbitration of the Address-Data bus.

#### DIN: Data Input Enable.

The NCR90C98 uses this signal to control the host's data bus. When the NCR90C98 drives this signal low the host's data bus latch drives the Address-Data bus. When  $\overline{\text{DIN}}$  is driven high the host's data bus latch is assumed to be in a high impedance state.

#### ET1, ET2: Extended Timeout Functions.

These signals are used to select the timeout durations of the NCR90C98. This is primarily used in checking responses from the other nodes on the LAN. These pins should be tied high for normal operation. See Table 1.

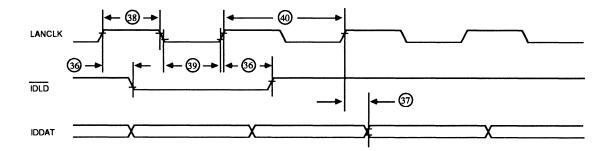

#### IDDAT: ID Data In.

This input is used to serially shift the node ID into the NCR90C98. Each bit of the data is latched into the NCR90C98 on the falling edge of LANCLK. The shift register is clocked by the rising edge of LANCLK. The ID data is shifted into the NCR90C98 MSB first, with a high level representing a logic 1. (See IDLD).

#### IDLD: ID Load.

This output is used to synchronously load the state of the ID switches into an external shift register. (See IDDAT).

#### INTR: Interrupt.

The NCR90C98 drives this signal high to indicate to the host that an enabled interrupt condition has occurred. INTR will return low after clearing the interrupt status condition or the corresponding mask bit.

#### **IOREQ**: I/O Request.

This signal is sampled by the NCR90C98 on the falling edge of AS. When this signal goes low, it indicates that the host wishes to communicate with the NCR90C98.

#### L: Latch.

The NCR90C98 uses this signal to control the lower address lines driving the RAM. When the NCR90C98 drives this signal low the lower address lines driving the RAM are latched until the RAM access is finished.

#### LANCLK: Network Clock.

A free running 5 MHz clock used for clocking the ID shift register.

#### MREQ: Memory Request.

This signal is sampled by the NCR90C98 on the falling edge of AS. When low it indicates that the host wishes to transfer data with the buffer RAM. OE: Output Enable.

The NCR90C98 drives this control line low on all RAM read cycles, enabling the buffer RAM to output data over the Address-Data bus.

OSCIN, OSCOUT: Oscillator Input & Output.

This input and output pin connect an external 20 MHz crystal to the internal oscillator. The OSCIN pin may also be used to drive the NCR90C98 with an external clock. OSCOUT is left floating in this case.

#### RESET: Reset.

This input pin when driven low resets the state of the NCR90C98. Upon Power Up the internal power on reset cell will reset the chip. During reset the NCR90C98 sequence counter is set to zero and the Reset status bit is set to a 1. See Table 2.

#### PULS1. PULS2: Pulse 1 & Pulse 2.

These outputs are non-overlapping negative going pulses that drive the cable circuitry. The output signals correspond to the data being transmitted over the LAN from this node. Pulse1 is the first and Pulse2 is the second pulse in this dual-pulse process.

#### R/W: Read/Write.

This input line indicates to the NCR90C98 that the pending host access request is either a read or a write cycle.  $R/\overline{W}$  is sampled on the falling edge of AS.

RXIN: Receive Data In.

This input pin receives serial data from the LAN cable circuitry.

VDD: Power.

Connect this pin to +5 Volts.

VSS: Ground.

Connect this pin to ground.

#### WAIT: Wait.

This output signal is driven high by the NCR90C98 at the beginning of host access requests. It indicates that the bus arbitration has started. WAIT is returned low when the NCR90C98 is ready for the host to complete its access.

#### $\overline{\text{WE}}$ : Write Enable.

The NCR90C98 drives this control line low on all RAM write cycles. This enables the buffer RAM to clock in data from the Address-Data bus. Data is clocked into the RAM on the rising edge of WE.

Table 2 NCR90C98 Reset State

| Name                         | State                |

|------------------------------|----------------------|

| Registers and Pointers       | msb lsb              |

| Status Register 1*           | 1 x x 1 0 0 0 1      |

| Status Register 2            | x x x x x x 1 0      |

| Interrupt Mask               | 00000000             |

| Next Page to Write (NPWR)    | x x x 1 1 1 1 1      |

| Next Page to Transmit (NPTX) | x x x 1 1 1 1 1      |

| Start TX Buffer (STXB)       | x x x 1 1 1 1 1      |

| Next Page to Receive (NPRX)  | x x x 0 0 0 0 0      |

| Next Page to Read (NPRD)     | x x x 0 0 0 0 0      |

| Start RX Buffer (SRXB)       | x x x 0 0 0 0 0      |

| Output Pins                  |                      |

| ADO-AD7, A8-A12              | H i g h<br>Impedance |

| Control Lines:               | Inactive             |

| ADRIN, AIE, DIN, L, IDLD     | 1 (high)             |

| WE, OE                       | 1 (high)             |

| WAIT, INTR                   | 0 (low)              |

| PULS1, PULS2                 | Inactive (high)      |

\*In Status Register 1, bits 5 & 6 reflect the state of the ETS1 & ETS2 pins.

#### REGISTER DESCRIPTIONS

The registers of the NCR90C98 occupy six addresses in a Memory or I/O Map. The host system has access to eight registers which are:

- Command Registers 1 & 2,

- Interrupt Mask Register,

- Status Registers 1 & 2,

- · NPRX Pointer Register,

- · NPTX Pointer Register, and the

- RESET Command Register.

The registers are decoded with the AD0-AD3 signals and the  $R\overline{W}$  line on the falling edge of AS. See Table 3.

Table 3 Register Addresses

|         | Table o Register A | 1441 CBBCB        |  |  |

|---------|--------------------|-------------------|--|--|

| AD      | WRITE              | READ              |  |  |

| 3210    |                    |                   |  |  |

| 0000    | Interrupt Mask     | Status Register 1 |  |  |

| 0 0 0 1 | Command Reg. 1     | Reserved          |  |  |

| 0011    | Command Reg. 2     | NPRX Pointer      |  |  |

| 0011    | Reserved           | NPTX Pointer      |  |  |

| 0 1 0 0 | Reserved           | Status Register 2 |  |  |

| 1000    | Reset Chip         | Reserved          |  |  |

#### **Command Registers Description**

Command Registers 1 & 2 are write only registers accessed by writing to addresses 01 or 02 respectively. Eight-bit commands are written to transfer control information to the NCR90C98. The commands recognized by Command Registers 1 & 2 are described below.

Command Register 1

**Data**

**Function**

msb lsb

0 0 0 0 0 0 1 Disable Transmitter: Causes the NCR90C98 to cancel any pending transmit command. The TA bit is set the next time the NCR90C98 receives the token.

0 0 0 0 0 1 0 Disable Receiver: Causes a pending receive command to be cancelled. This command causes the RI bit to be set the next time the NCR90C98 receives the token. If a PACKET has already started to arrive, then this command will have no effect.

nnnn nnn nnn nnnn: Transmit from page nnnnn: Transmit a packet out of buffer RAM nnnnn upon receipt of the token. This command clears TA and TMA. The TA bit is set to a logic '1' at the completion of the transmission. TMA is set to a logic '1' when an ACK is received from the destination node.

nnnn100 Enable Receive to page nnnnn:

Allows the NCR90C98 to receive

packets into buffer RAM starting

at page nnnnn. This command sets

the pointers SRXB, NPRD and

NPRX to nnnnn and clear the RI

bit. RI is set when no more buffers

are available.

p 0 0 s s 1 0 1 Size Definition: Tells the NCR90C98 the size of its buffer RAM and whether it can receive long or short packets.

| SS | RAM | р | Packet    |

|----|-----|---|-----------|

| 00 | 1K  | 0 | 256 bytes |

| 01 | 2K  | 1 | 512 bytes |

| 10 | 4K  |   |           |

| 11 | 8K  |   |           |

0 0 0 r p 1 1 0 Clear Flags: Resets the RECON status bit if r=1 and/or the Reset status bits if p=1.

Command Register 2

Data

**Function**

msb isb

n n n n n 0 0 1 Write Next Page to Write Pointer (NPWR): Initializes the NPWR pointer to page nnnnn.

n n n n n 0 1 0 Write Next Page to Read (NPRD)

pointer: Initializes the NPRD

pointer to page nnnnn.

nnnno 11 Initialize Transmit pointers:

Initializes Next Page to Transmit

(NPTX), Next Page to Write

(NPWR) and Start Transmit

Buffer (STXB) pointers to page

nnnnn.

0 0 0 0 0 1 0 0 Enable Chain Transmit: Tells the NCR90C98 to start transmitting from the page pointed to by the STXB pointer. It stops when the NPTX pointer has reached the NPWR pointer.

brc00101 Write Configuration: Tells the NCR90C98 what mode it is in. When b=1 broadcast messages will be accepted. When r=1 chain receive is enabled. When c=1 circular buffer chaining is enabled.

#### **Status Register Description**

Status Registers 1 & 2 are read only registers that allow the host to monitor the status of the LAN. Status Register 1 is read from address 00 and Status Register 2 is read from address 04.

| Status Register 1 |                |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                   |                                     |          |                                                                                                                                                                                   |                                                                                           |                                                                                                                         |                                                                                                                   |

|-------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

|                   | 7              | 6                                                                                                                                                                                                                                                                                                                                                                                                     | 5                                                                                                                                                                                                                                                                                                                 | 4                                   | 3        |                                                                                                                                                                                   | 2                                                                                         | 1                                                                                                                       | 0                                                                                                                 |

|                   | RI             | ETS2                                                                                                                                                                                                                                                                                                                                                                                                  | ETS1                                                                                                                                                                                                                                                                                                              | Reset                               | TE       | ST                                                                                                                                                                                | RECON                                                                                     | TMA                                                                                                                     | TA                                                                                                                |

| Bits<br>0         | Name<br>TA     | Per Description  Transmitter Available: When TA is set to a '1' the node is available to carry out a transmit sequence. It also indicates any previous ENABLE TRANSMIT process has been completed. TA is cleared by the Enable Transmit and Enable Chain Transmit commands. TA is set after packet(s) have been transmitted and ACK'ed. TA is also set if there is no ACK and the node has timed out. |                                                                                                                                                                                                                                                                                                                   |                                     |          | node is available to ransmit sequence. It 4 Reset Reset 1' the reset not and Enable Chain nands. TA is set after been transmitted and also set if there is no node has timed out. |                                                                                           |                                                                                                                         |                                                                                                                   |

| 1                 | TMA            | When TMA sage sent fro TRANSMIT nowledged TMA is clo Transmit Transmit co after packet                                                                                                                                                                                                                                                                                                                | Transmit Message Acknowledged: When TMA is set to a '1' the message sent from a previous ENABLE TRANSMIT command was acknowledged by the receiving node. TMA is cleared by the Enable Transmit and Enable Chain Transmit commands. TMA is set after packet(s) have been transmit- ted and ACK'ed by the receiving |                                     |          | ETS1<br>ETS2                                                                                                                                                                      | execu<br>cleare<br>mand<br>, Extended<br>The state<br>the logic<br>pins. Und<br>tions ETS | Reset commanded. The Reserved by the Clear                                                                              | t status bit is ar Flags com-<br>atus 1 & 2: e bits reflects<br>TTS1 & ETS2 erating condi-<br>rill be '1'.        |

| 2<br>Statu        | RECON          | RECON is<br>Reconfigurate<br>the expirati<br>RECON is<br>FLAGS com                                                                                                                                                                                                                                                                                                                                    | ration Fla<br>set to a '1'<br>tion took pla<br>on of an Idl<br>reset by th<br>mand.                                                                                                                                                                                                                               | a system<br>ce due to<br>e timeout. |          |                                                                                                                                                                                   | to a '1' the ing any notes of RI is cleat command been made Chain mothes been notes more  | e NCR90C98 nessages from red by the Er and when a de available i de. RI is set w received or wl buffers avai nain mode. | is not receiv-<br>other nodes.<br>nable Receive<br>a buffer has<br>n the Buffer<br>when a packet<br>hen there are |

| Statu             | is negisi<br>7 | er 2<br>6                                                                                                                                                                                                                                                                                                                                                                                             | 5                                                                                                                                                                                                                                                                                                                 | 4                                   | 3        | 3                                                                                                                                                                                 | 2                                                                                         | 1                                                                                                                       | 0                                                                                                                 |

|                   | X              | X                                                                                                                                                                                                                                                                                                                                                                                                     | X                                                                                                                                                                                                                                                                                                                 | X                                   | X        |                                                                                                                                                                                   | X                                                                                         | CD                                                                                                                      | RP                                                                                                                |

| Bits<br>0         | Name<br>RP     | a '1' a packe<br>the Buffer                                                                                                                                                                                                                                                                                                                                                                           | cket: When Ret has been in Chain mod the read N                                                                                                                                                                                                                                                                   | eceived in<br>le. RP is             | 1<br>2-7 |                                                                                                                                                                                   | '1' the N<br>activity of<br>cleared w                                                     | etect: When C<br>NCR90C98 i<br>on the RXIN<br>hen the NCR<br>e mode is en                                               | CD is set to a<br>s detecting<br>pin. CD is<br>90C98 trans-                                                       |

#### Interrupt Mask Register

The Interrupt Mask Register is a read only register that determines which of the five conditions will cause an interrupt. The status bits TMA, ETS1, ETS2 and CD have no corresponding mask bits and do not cause interrupts. The five maskable status bits are outlined in the following diagram.

| 7                  | 4     | 3    | 2                | 0                        |

|--------------------|-------|------|------------------|--------------------------|

| RECEIVE<br>INHIBIT | Reset | TEST | RECON<br>TIMEOUT | TRANSMITTER<br>AVAILABLE |

Setting any of these bits to a "1" will cause the INTR signal to be asserted high whenever any of the corresponding status bits go high. The other three bits in the Interrupt Mask register are don't cares. (See Host Interrupt section for more details).

## Next Page to Receive (NPRX) Pointer Register

The Next Page to Receive (NPRX) pointer is read from address 02. The format of the data with the register follows.

X X X A12 A11 A10 A9 A8 - Read NPRX pointer. By executing this read the RP bit will be reset.

#### Next Page to Transmit Pointer Register

The Next Page to Transmit Pointer is read from address 03. The format of the data with the register follows.

X X X A12 A11 A10 A9 A8 - Read NPTX pointer.

#### **Reset Register Description**

When the following value is written to this register at address 08 the NCR90C98 is reset. This provides the host a means for resetting the NCR90C98 from software.

0 0 0 0 0 0 0 1 - RESET. Resets the NCR90C98.

#### RESET OPTIONS

There are three reset options for the NCR90C98. When power is applied to the chip, the POR cell senses this and generates an internal signal to reset the chip. Another option resets the chip when a low signal is applied to the Reset pin for a minimum of 200 ns. It is also possible to reset the chip by writing a reset command to I/O location 08.

The NCR90C98 executes a reset routine that writes 53H to address 0 in buffer RAM and reads the node ID.

#### SOFTWARE CONSIDERATIONS

The standard method for the host to transmit a packet(s) of information in the buffer chaining mode follows.

- 1. Initialize transmit pointers.

- 2. Write the packet(s) to the page.

- 3. Write the NPWR pointer.

- 4. Write Enable Chain Transmit.

- 5. When NPWR=NPTX TA & TMA is set as described in the Status Register Description.

- 6. If more packets are ready to go, repeat step 3,4.

- 7. If not, repeat steps 2,3,4.

The standard method for the host to Receive a packet(s) of information in the buffer chaining mode follows.

- 1. Write Enable Receive.

- 2. When the RP interrupt occurs, read the NPRX pointer. This resets the RP flag.

- 3. Read the packet(s). Write the NPRD pointer.

- 4. If NPRX indicated missed interrupts, repeat step 3.

- 5. If not, go back to 2.

When any register with reserved bits is read, the state of the reserved bits is not guaranteed.

The buffer memory can be reconfigured at any time. However, the receiver and transmitter must be disabled and all packets read/transmitted to insure that no packets are lost.

#### **HOST INTERRUPTS**

The NCR90C98 generates an interrupt on the INTR pin in response to several of the conditions that set status bits. The Interrupt Mask Register determines which of the five conditions will cause an interrupt. The status bits TMA, ETS1, ETS2 and CD have no corresponding mask bits and do not cause interrupts. The five maskable status bits are outlined in the following diagram.

| 7                  | 4     | 3    | 2                | 0                        |

|--------------------|-------|------|------------------|--------------------------|

| RECEIVE<br>INHIBIT | Reset | TEST | RECON<br>TIMEOUT | TRANSMITTER<br>AVAILABLE |

Setting any of these bits to a "1" will enable the INTR signal to be asserted high when the corresponding status bits go high. The other three bits in the Interrupt Mask register are don't cares. Once the INTR signal is high, it can be cleared by clearing the corresponding bit in the Status Register or the Mask Register.

RP generates a non-maskable interrupt. It is cleared by reading NPRX.

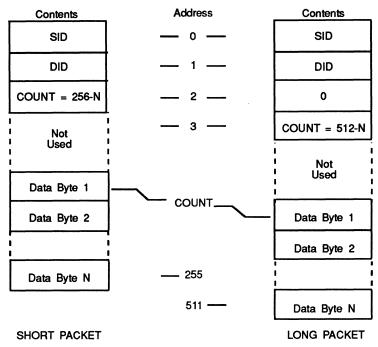

NOTE: Addresses shown are relative to a Page, not absolute. SID = Source ID (not written in Transmit Packets). DID = Destination ID (set = 0 for Broadcasts). N = Message Length. "Not Used" bytes imply message is less than maximum length. These bytes would be written for Max. Messages: SHORT = 253 bytes, LONG = 508.

Figure 6 RAM Buffer Map

#### RAM BUFFER MEMORY MAP

Figure 6 shows the locations of the major components for both Short (up to 256 bytes) and Long (up to 512 bytes) PACKETS.

## HOST INTERFACE DESCRIPTION

The Typical System Block Diagram (Figure 7) illustrates the hardware aspects of a host processor interface to the NCR90C98. The block on the left contains the signals of a generic processor with an eight-bit data bus and a 16-bit address bus. The upper address bits are used to decode whether a pending host access is to/from the buffer RAM (MREQ), or the NCR90C98 (IOREQ). The buffer RAM in Figure 7, an 8K x 8 Static RAM, can hold 16 pages with 512 bytes per page or 32 pages with 256 bytes per page. Entire PACKETS are stored in

a page in the buffer RAM. A 512 byte page corresponds to a Long Packet and a 256 byte page to a Short Packet. The 'D' Latches with the output control signal (OC) driven by  $\overline{AIE}$ , latch the Host's Upper Address Bus (A8-A15) signals for buffer RAM accesses by the host. The 'D' Latches with OC driven by L, latch the lower address bus for buffer RAM accesses, by both the NCR90C98 and the host. For host access cycles (read and write) to the NCR90C98 or to the buffer RAM, the latches with OC driven by ADRIN, latch the incoming lower addresses (A0-A7) from the host system. For host access write cycles to the NCR90C98 or to the buffer RAM, the latches with OC driven by  $\overline{DIN}$ , latch the data (D0-D7) from the host system. For host access read cycles to the NCR90C98 or to the buffer RAM, the latches with OC driven by RD, latch the data (D0-D7) from the NCR90C98 or buffer RAM. A typical device for these latches is the '373.

Figure 7 Typical system block diagram

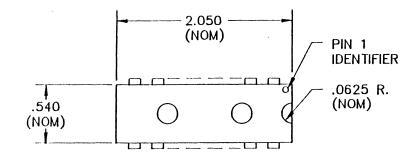

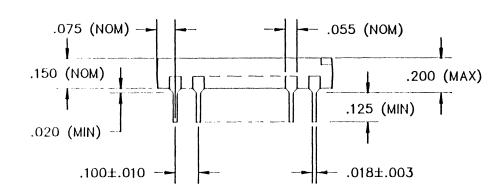

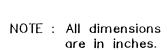

# MECHANICAL SPECIFICATIONS

### NCR90C98PD

#### NCR90C98PP

NOTE: All dimensions are in inches.

#### **ORDERING INFORMATION**

The NCR90C98 is available in two different package types, the 40-pin Dual Inline Package (DIP) and the 44-pin Plastic Leaded Chip Carrier (PLCC). The following part numbers should be used to order the desired package.

| Package Type | Part Number |

|--------------|-------------|

| 40-pin DIP   | NCR90C98PD  |

| 44-pin PLCC  | NCR90C98PP  |

#### **ELECTRICAL CHARACTERISTICS**

#### **Absolute Maximums**

| Symbol   | Parameter                                   | Minimum | Maximum        | Units |

|----------|---------------------------------------------|---------|----------------|-------|

| TA       | Ambient Temperature                         | 0       | 70             | °C    |

| Ts       | Storage Temperature                         | -55     | 150            | °C    |

| $V_{DD}$ | Supply Voltage                              | -0.5    | 7.0            | Volts |

| Vin      | Input Voltage                               | -0.5    | $V_{DD} + 0.5$ | Volts |

| Vour     | Output Voltage,                             | -0.5    | $V_{DD} + 0.5$ | Volts |

| $T_{L}$  | Lead Temperature (Soldering 10 seconds max) | -       | 250            | °C    |

## DC Characteristics (V<sub>DD</sub> = 4.5V to 5.5V, V<sub>SS</sub> = 0V, T<sub>A</sub> =0C to 70°C.)

| Symbol          | Parameter                                                                    | Minimum    | Maximum               | Units |  |  |  |

|-----------------|------------------------------------------------------------------------------|------------|-----------------------|-------|--|--|--|

| $V_{\text{1L}}$ | Input Voltage, Low                                                           | ₩ss - 0.5  | 0.8                   | Volts |  |  |  |

| Vін             | Input Voltage, High                                                          | <b>2.0</b> | V <sub>DD</sub>       | Volts |  |  |  |

| Vн CLK          | Clock Input Voltage (OSCIN pin) Output Voltage, High (IoH = 4mA, VDD = 4.5V) | VDD - 0.5  | V <sub>DD</sub> + 0.5 | Volts |  |  |  |

| Vон             | Output Voltage, High (IoH = 4mA, VDD = 4.5V)                                 | 2.4        |                       | Volts |  |  |  |

| Vol             | Output Voltage, Low (IoL = 4mA)                                              |            | 0.4                   | Volts |  |  |  |

| Cin             | Input Capacitance                                                            |            | 10                    | pF    |  |  |  |

| Iı              | Input Leakage Current                                                        |            | ± 10                  | μА    |  |  |  |

| IDD             | Power Supply Current ( $V_{DD} = 5.5V$ )                                     |            | 30                    | mA    |  |  |  |

|                 |                                                                              |            |                       |       |  |  |  |

# AC Characteristics (V<sub>DD</sub> = 4.5V to 5.5V, V<sub>SS</sub> = 0V, T<sub>A</sub> = 0C to 70°C.)

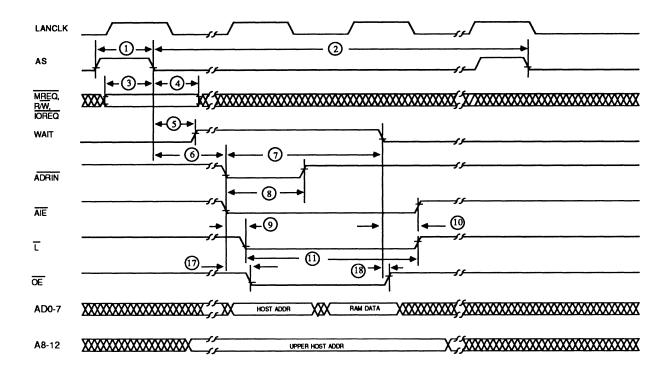

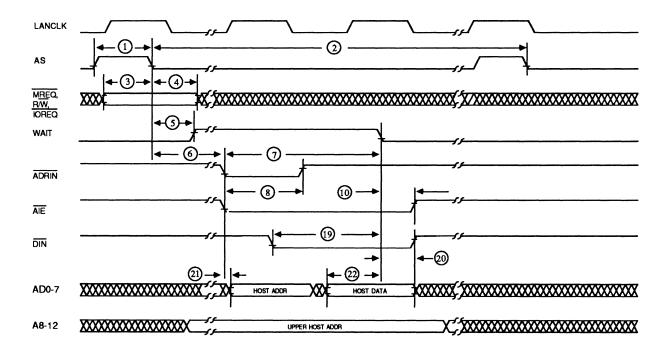

| #  | Description                 | Min | Тур | Max | Units | Comments              |

|----|-----------------------------|-----|-----|-----|-------|-----------------------|

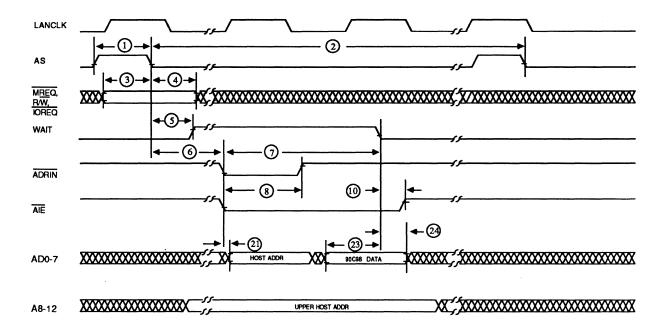

| 1  | AS pulse width              | 50  |     |     | ns    |                       |

| 2  | Period of AS                | 900 |     |     | ns    | incl. bus arbitration |

| 3  | Control valid before AS low | 50  |     |     | ns    |                       |

| 4  | Control valid after AS low  | 50  |     |     | ns    |                       |

| 5  | AS low to WAIT high         | 5   |     | 30  | ns    |                       |

| 6  | Processor cycle delay       | 100 |     | 650 | ns    |                       |

| 7  | ADRIN to WAIT low           | 230 |     | 270 | ns    |                       |

| 8  | ADRIN pulse width           | 90  |     | 110 | ns    |                       |

| 9  | Delay from ADRIN to L       | 45  |     | 55  | ns    |                       |

| 10 | Delay from WAIT to AIE      | 45  |     | 65  | ns    |                       |

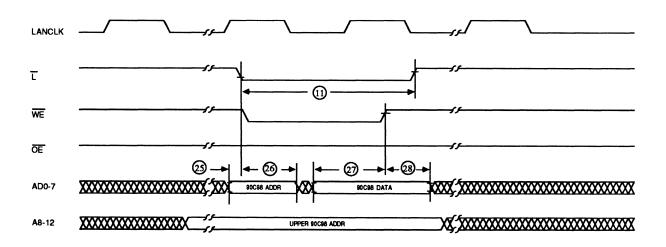

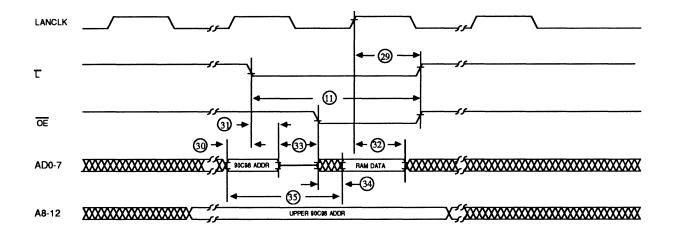

| 11 | L pulse width               | 225 |     | 275 | ns    |                       |

| 12 | Delay ADRIN to DIN          | 100 |     | 140 | ns    |                       |

| 13 | Delay WE to AIE             | 45  |     | 60  | ns    |                       |

| 14 | WE hold to DIN              | 50  |     | 80  | ns    |                       |

| 15 | Delay ADRIN to WE           | 90  |     | 110 | ns    |                       |

| 16 | WE pulse width              | 130 |     | 165 | ns    |                       |

| 17 | Delay ADRIN to OE           | 135 |     | 180 | ns    |                       |

| 18 | OE hold after WAIT          | 50  |     | 80  | ns    |                       |

| 19 | DIN low to WAIT low         | 110 |     | 155 | ns    |                       |

| 20 | Delay WAIT to DIN           | 50  |     | 85  | ns    |                       |

| 21 | ADRIN delay to valid data   |     |     | 60  | ns    |                       |

AC Characteristics ( $V_{DD} = 4.5V$  to 5.5V,  $V_{SS} = 0V$ ,  $T_A = 0C$  to  $70^{\circ}C$ .)

| #  | Description                         | Min | Тур  | Max        | Units | Comments |

|----|-------------------------------------|-----|------|------------|-------|----------|

| 22 | Data setup before WAIT (write)      | 25  |      |            | ns    |          |

| 23 | Data setup before WAIT (read)       | 50  |      |            | ns    |          |

| 24 | Data hold after WAIT                | 45  |      |            | ns    |          |

| 25 | L to data valid                     | 70  |      |            | ns    |          |

| 26 | L to data invalid                   | 45  |      |            | ns    |          |

| 27 | Data setup before WE                | 115 |      |            | ns    |          |

| 28 | Data hold after WE                  | 90  |      |            | ns    |          |

| 29 | L turnoff delay from LANCLK high    | 50  |      | 80         | ns    |          |

| 30 | ADD valid to L                      | 85  |      |            | ns    |          |

| 31 | ADD hold to $\overline{\mathbf{L}}$ | 45  |      |            | ns    |          |

| 32 | RAM data hold for AC                | 50  |      | 1011111111 | ns    |          |

| 33 | Addr./Data bus Hi-Z before OE       | 0   |      |            | ns    |          |

| 34 | RAM data delay after OE             | 0   |      | 140        | ns    |          |

| 35 | Address valid before data           | 300 |      |            | ns    |          |

| 36 | IDLD valid from LANCLK              | 0   | ¥.,_ | 120        | ns    |          |

| 37 | IDDAT valid from LANCLK             | 0   |      |            | ns    |          |

| 38 | LANCLK pulse high                   | 95  |      |            | ns    |          |

| 39 | LANCLK pulse low                    | 95  |      |            | ns    |          |

| 40 | LANCLK period                       | 190 | 200  | 210        | ns    |          |

Figure 10 Write RAM by Host Timing Diagram

Figure 11 Read RAM by Host Timing Diagram

Figure 12 Write NCR90C98 by Host Timing Diagram

Figure 13 Read NCR90C98 by Host Timing Diagram

Figure 14 Write RAM by NCR90C98 Timing Diagram

Figure 15 Read RAM by NCR90C98 Timing Diagram

Figure 16 Clock and ID Signal Timing Diagram

#### **SALES INFORMATION**

For more information on the NCR90C98, or any other Communications Group device, please call the NCR hotline at

1 - 800 - 334 - 5454

or contact your local NCR Sales Representative or one of the following NCR Sales Offices.

#### NCR MICROELECTRONICS REGIONAL SALES OFFICES

| NORTHEAST                   | NORTH CENTRAL           | NORTHWEST              |

|-----------------------------|-------------------------|------------------------|

| NCR Microelectronics        | NCR Microelectronics    | NCR Microelectronics   |

| Suite 2750                  | Suite 4080              | Suite 209              |

| 400 West Cummings Park      | 33 West Higgins Road    | 3130 De La Cruz Blvd.  |

| Woburn, MA 01801            | S. Barrington, IL 60010 | Santa Clara, CA 95054  |

| (617) 933-0778              | (312) 426-4600          | (408) 727-6575         |

| SOUTHEAST                   | SOUTH CENTRAL           | SOUTHWEST              |

| NCR Microelectronics        | NCR Microelectronics    | NCR Microelectronics   |

| Suite 250                   | Suite 100               | 1940 Century Park East |

| 700 Old Roswell Lakes Pkwy. | 400 Chisholm Place      | Los Angeles, CA 90067  |

| Roswell, GA 30076           | Plano, TX 75075         | (213) 556-5396         |

| (404) 587-3136              | (214) 578-9113          |                        |

NCR Microelectronics

Communications Group MS 550A

2001 Danfield Ct.

Fort Collins, CO 80525

(303) 226-9500

NCR reserves the right to make any changes or discontinue altogether without notice any hardware or software product or the technical content herein.

24