# ARCNET® Transceiver Chip

## **FEATURES**

- Works with NCR90C26 to transfer data at 2.5 Megabits per second

- Outputs the special clock signals required by the NCR90C26

- Generates output in NRZ format from incoming LAN data

- Provides two general purpose 4 MHz clock outputs for CPU interface

- Generates dual-pulse output signals for data transmission out to LAN

- Provides special 5 MHz clocks required by the Controller chip

#### INTRODUCTION

The NCR90C32 AT (ARCNET Transceiver) is a flexible data handling device that interfaces an NCR90C26 ARCNET Controller chip to special cable driving and receiving circuitry. Directed by a host microprocessor, these components comprise a node in an ARCNET Local Area Network. The main function of the NCR90C32 is to convert data between a NRZ format on the host side and dual-pulse on the cable side. The only additional component required by the AT is a 20 MHz clock oscillator.

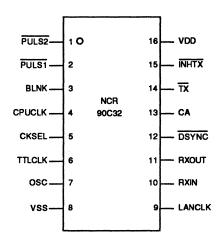

Figure 1 16-pin DIP and 28-pin PLCC

ARCNET is a registered trademark of DATAPOINT CORPORATION

| Symbol | ymbol Pin No. |             | 1/0 | Name and Function                                                                                                                                                                                                                                              |

|--------|---------------|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 16-pin DIP    | 28-pin PLCC |     |                                                                                                                                                                                                                                                                |

| OSC    | 7             | 14          | I   | OSCILLATOR: 20 MHz input signal.                                                                                                                                                                                                                               |

| CKSEL  | 5             | 9           | I   | CLOCK SELECT: Chooses the clock options for the extra TTLCLK and CPUCLK pins. When CKSEL is high, the two extra clocks both output a constant four MHz derived from the OSC signal. When CKSEL is low, then CPUCLK outputs the inverse of the input on TTLCLK. |

| LANCLK | 9             | 16          | 0   | NETWORK CLOCK: A free-running 5 MHz clock used for timing of 90C26 bus cycles and other functions.                                                                                                                                                             |

| CA     | 13            | 24          | 0   | AUXILIARY CLOCK: A gated 5 MHz clock used to control data transfers of the NCR90C26. CA is periodically halted by DSYNC and restarted by RX.                                                                                                                   |

| TTLCLK | 6             | 13          | I/O | TTL CLOCK: May be either input or output. See description for CKSEL above.                                                                                                                                                                                     |

| CPUCLK | 4             | 6           | 0   | CPU CLOCK: An additional clock output. See description for CKSEL.                                                                                                                                                                                              |

| TX     | 14            | 26          | I   | TRANSMIT DATA: Serial data input to the AT for conversion and transmission over the LAN.                                                                                                                                                                       |

| PULS1, | 2,            | 2,          | 0   | PULSE1 & PULSE2: These outputs are nonoverlapping negative going pulses that are asserted to the                                                                                                                                                               |

| PULS2  | 1             | 1           |     | cable circuitry for every active pulse detected at TX. PULSE1 is the first, and PULSE2 is the second pulse in this dual-pulse process.                                                                                                                         |

| RXIN   | 10            | 17          | I   | RECEIVE DATA IN: Serial input data from the LAN.                                                                                                                                                                                                               |

| DYSNC  | 12            | 21          | I   | DELAYED SYNC: This signal is asserted by the NCR90C26 to cause the AT to halt the CA clock.                                                                                                                                                                    |

| RXOUT  | 11            | 18          | 0   | RECEIVED DATA OUT: An NRZ form of the serial data input at the RXIN pin.                                                                                                                                                                                       |

| INHTX  | 15            | 27          | I   | TRANSMIT INHIBIT: A Power-Reset input. INHTX active forces PULS1 and PULS2 high and BLNK low. These actions block the TX input from causing transmissions on the LAN.                                                                                          |

| BLNK   | 3             | 3           | 0   | BLANK: A delayed and shortened version of $\overline{TX}$ . This signal should be left unconnected when used in a typical circuit such as that on page 3.                                                                                                      |

| VDD    | 16            | 28          |     | +5 VOLT SUPPLY                                                                                                                                                                                                                                                 |

| VSS    | 8             | 15          |     | GROUND                                                                                                                                                                                                                                                         |

## **DESCRIPTION**

The primary job of the NCR90C32 AT is to format data and synchronize transfers over the ARCNET node to which it is attached. The LANCLK output to the NCR90C26 Controller device assures that all transactions between the two chips are synchronous. The analog cable circuit converts all dipulses (logic ones) received on the LAN to single positive pulses on the RXIN pin into the AT. This data, after some delay, is converted into NRZ format and sent to the NCR90C26 device. After a full byte has been transferred, the NCR90C26 will

assert DSYNC, which halts the CA clock. When the AT detects the first bit of the next byte, it will restart CA. The CA signal is used by the NCR90C26 to sample the levels on RXOUT at the times indicated in the timing diagrams. For outward transmissions, the NCR90C26 puts active-low pulses 200ns in duration on TX for every logic one it sends. Each of these active-low pulses is converted to two 100ns wide, nonoverlappping, active-low pulses on the PULS1 & PULS2 outputs. These signals will drive the cable circuitry to create the dipulse that signifies logic one on the LAN cable itself.

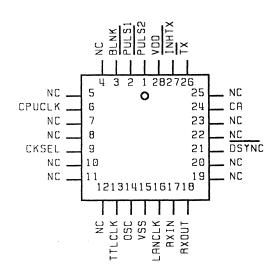

Figure 2 Typical NCR90C32 Hookup

3

# **ELECTRICAL SPECIFICATIONS**

#### ABSOLUTE MAXIMUM STRESS RATINGS

Voltage on VDD pin with respect to Vss.....-0.3 to +7.0V

Voltage on any signal pin.....-0.3 to  $V_{\text{DD}}$  +0.3

Power Dissipation.....53 mW

Operating Temperature Range......0°C to 70°C

Storage Temperature Range.....-65°C to +150°C

The values listed above are absolute maximums which, if exceeded, could cause permanent damage to the device. Voltages are with respect to circuit ground.

# DC Characteristics

| Symbol      | Parameter                                                                                  | Min                                     | Max                  | Units |

|-------------|--------------------------------------------------------------------------------------------|-----------------------------------------|----------------------|-------|

| Vıl         | Input Voltage, Low (all inputs)                                                            | -0.3                                    | 0.8                  | V     |

| Vн          | Input Voltage, High (all inputs)                                                           | 2.7                                     | V <sub>DD</sub> +0.3 | V     |

| Іонх        | Transfer Output High Current (@ VOH max=0.4V) for: PULS1, PULS2, RXOUT, and TTLCLK outputs |                                         | -400                 | μА    |

| Iolx        | Transfer Output Low Current (@ VOL max=0.4V) for: PULS1, PULS2, RXOUT, and TTLCLK outputs  |                                         | +4.0                 | mA    |

| Іонк        | Clock Output High Current (@ VOH min=VDD-0.5) for: CA, LANCLK, and CPUCLK                  |                                         | -100                 | μА    |

| Іоцк        | Clock Output Low Current (@ VOL max=0.4V) for: CA and LANCLK                               |                                         | +400                 | μА    |

| Iorn        | Output Low Current (@ VOL max=0.4V) for: CPUCLK                                            |                                         | +100                 | μA    |

| Cin         | Input Capacitance                                                                          |                                         | 30                   | pF    |

| Irr         | Input Leakage Current (TTLCLK pin as Input)                                                |                                         | ±50                  | μΑ    |

| Ir          | Input Leakage Current (all other inputs)                                                   | 250000000000000000000000000000000000000 | ±10                  | μΑ    |

| $I_{ m DD}$ | Power Supply Current (VDD=5.25V)                                                           |                                         | 10                   | mA    |

Notes: All parameters are assured over the 0°C to 70°C temperature range and with 4.75≤V<sub>DD</sub>≤5.25 Volts. All voltages are with respect to circuit ground (Vss).

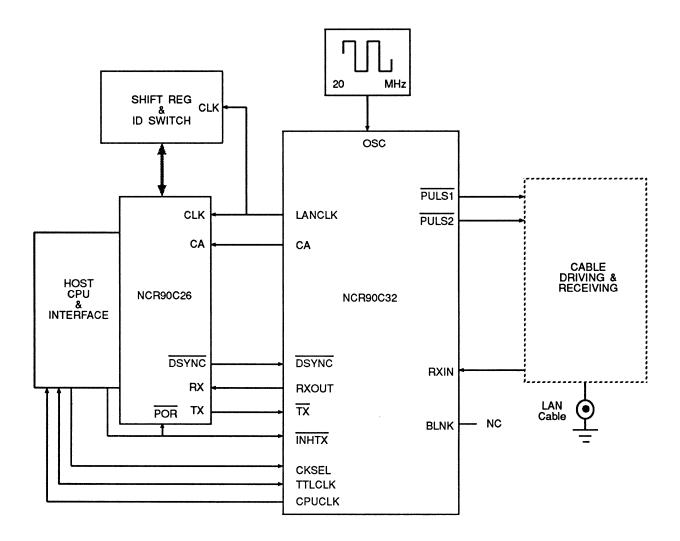

Figure 3 Clock Timing Parameters

| NAME             | DESCRIPTION                      | MIN | TYP | MAX | UNITS |

|------------------|----------------------------------|-----|-----|-----|-------|

| tсн              | High Duration of OSC             | 20  |     |     | ns    |

| tcı              | Low Duration of OSC              | 20  |     |     | ns    |

| tcr              | Period of OSC                    |     | 50  |     | ns    |

| tснı             | High Duration of NCR90C26 Clocks | 75  |     | `   | ns    |

| tcli             | Low Duration of NCR90C26 Clocks  | 75  |     |     | ns    |

| tcyı             | Period of NCR90C26 Clocks        |     | 200 |     | ns    |

| t <sub>R1</sub>  | Rise Time of NCR90C26 Clocks     |     |     | 20  | ns    |

| t <sub>F1</sub>  | Fall Time of NCR90C26 Clocks     |     |     | 20  | ns    |

| t <sub>CH2</sub> | High Duration of Extra Clocks    | 110 |     |     | ns    |

| tc12             | Low Duration of Extra Clocks     | 110 |     |     | ns    |

| tc <sub>Y2</sub> | Period of Extra Clocks           |     | 250 |     | ns    |

| t <sub>R2</sub>  | Rise Time of Extra Clocks        |     |     | 30  | ns    |

| tr2              | Fall Time of Extra Clocks        |     |     | 30  | ns    |

| tоск             | CPUCLK Delay from TTLCLK Edges   |     |     | 45  | ns    |

Note: All timings in this specification are taken from the 10% & 90% points with respect to the specified VOL & VOH of the waveforms.

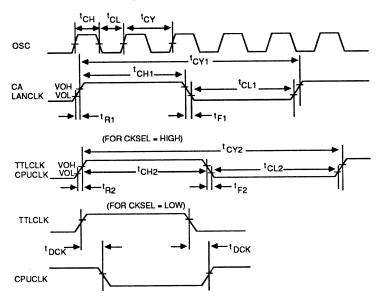

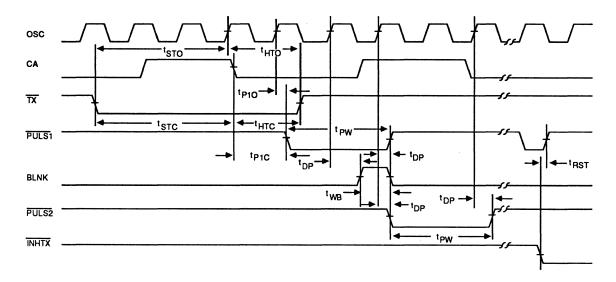

Figure 4 Transmit Timing

| NAME             | DESCRIPTION                                    | MIN | TYP  | MAX | UNITS |

|------------------|------------------------------------------------|-----|------|-----|-------|

| tsrc             | TX Setup to CA Falling Edge                    |     | 10   |     | ns    |

| tsto             | TX Setup to OSC Rising Edge                    | 10  |      |     | ns    |

| turc             | TX Hold after CA Falling Edge                  |     | 10   |     | ns    |

| tнто             | TX Hold after OSC Rising Edge                  | 10  |      |     | ns    |

| t <sub>P1C</sub> | PULS1 Delay after CA Falling Edge              | 60  |      |     | ns    |

| t <sub>P10</sub> | PULS1 Delay after OSC Rising Edge              |     |      | 60  | ns    |

| top              | PULSE & BLNK Edge Delays after OSC Rising Edge |     |      | 60  | ns    |

| tpw              | Duration of the two PULSE Signals              |     | 2tcy |     | ns    |

| twв              | Pulse Duration for BLNK                        |     | tcy  |     | ns    |

| trst             | PULS1 Turnoff from INHTX Falling Edge          |     |      | 40  | ns    |

6

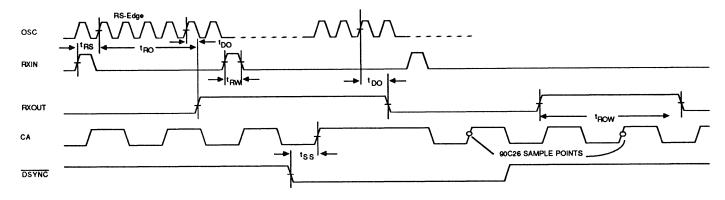

Figure 5 Receive Timing

| NAME | DESCRIPTION                      | MIN | TYP       | MAX | UNITS |

|------|----------------------------------|-----|-----------|-----|-------|

| trs  | RXIN Setup to RS-Edge            | 10  |           |     | ns    |

| trw  | RXIN Active Duration             | 10  |           |     | ns    |

| tpo  | RXOUT Delay from OSC Rising Edge |     |           | 70  | ns    |

| tro  | RXOUT Active after RS-Edge       |     | 5tcy +tpo |     | ns    |

| tss  | CA Turnoff after DSYNC           | 10  | 20        |     | ns    |

| trow | RXOUT Isolated '1' Duration      |     | 400       |     | ns    |

7

## **SALES INFORMATION**

For more information on the NCR92C32, or any other Communications Group device, please call the NCR hotline at

1 - 800 - 334 - 5454

or contact your local NCR Sales Representative or one of the following NCR Sales Offices.

## NCR MICROELECTRONICS REGIONAL SALES OFFICES

Gustav-Heinemann-Ring 133

8000 Munchen 83

(49) 89 - 63 22 02

West Germany

| NORTHEAST                                                                                               | NORTH CENTRAL                                                                                           | NORTHWEST                                                                                             |

|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| NCR Microelectronics<br>Suite 2750<br>400 West Cummings Park<br>Woburn, MA 01801<br>(617) 933-0778      | NCR Microelectronics<br>Suite 4050<br>33 West Higgins Road<br>S. Barrington, IL 60010<br>(312) 426-4600 | NCR Microelectronics<br>Suite 209<br>3130 De La Cruz Blvd.<br>Santa Clara, CA 95054<br>(408) 727-6575 |

| SOUTHEAST                                                                                               | SOUTH CENTRAL                                                                                           | SOUTHWEST                                                                                             |

| NCR Microelectronics<br>Suite 250<br>700 Old Roswell Lakes Pkwy.<br>Roswell, GA 30076<br>(404) 587-3136 | NCR Microelectronics<br>Suite 100<br>400 Chisholm Place<br>Plano, TX 75075<br>(214) 578-9113            | NCR Microelectronics<br>1940 Century Park East<br>Los Angeles, CA 90067<br>(213) 556-5396             |

| EUROPE                                                                                                  | ASIA                                                                                                    | SOUTHWEST                                                                                             |

| NCR GMBH<br>NCR Microelectronics Europe                                                                 | NCR Asia/Pacific<br>2501 Vicwood Plaza                                                                  | NCR Microelectronics<br>3300 Irvine Ave., Suite 25                                                    |

199 Des Voeux Rd.

Central Hong Kong

5 859 6888

Newport Beach, CA 92660

(714) 474-7095

NCR Microelectronics

Communications Group MS 550A

2001 Danfield Ct.

Fort Collins, CO 80525

(303) 226-9500

NCR reserves the right to make any changes or discontinue without notice any hardware or software product or the technical content herein.

8 T03892N