CONTROL DATA 6600

TRAINING MANUAL

CONTROL DATA 6600 TRAINING MANUAL

| 60147400  | Record of Revisions                                |

|-----------|----------------------------------------------------|

| REVISION  | NOTES                                              |

| A         | Pages 3-11, E-10, E-11, E-12, E-13 and A-2 through |

| (6-17-65) | A-14 revised, A-15, A-16 and A-17 added.           |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

|           |                                                    |

CONTROL DATA 6600

TRAINING MANUAL

This manual is intended primarily for training use. It obsoletes Pub. No. 60127400. The information contained herein is subject to correction and change. Corrections and suggestions should be brought to the attention of the supervisor of computer training, Control Data Institute.

## CONTENTS

Section I: Central Processor Address Control

Introduction

Stunt Box

Exchange Jump

Peripheral Read/Write

Central Read/Write

Exit 'lole

Section II: Central Processor Instruction Issue Control

Introduction

Instruction Stack

Instruction Registers

Inch Counter

L Counter

Issue Control

Stop Instruction Issue

Proceed Instruction Issue

Section III: Central Processor Scoreboard

Introduction

Placing Reservations

Set Read Flags

Request Release

Data Trunk Priority

Go Store/Go Read

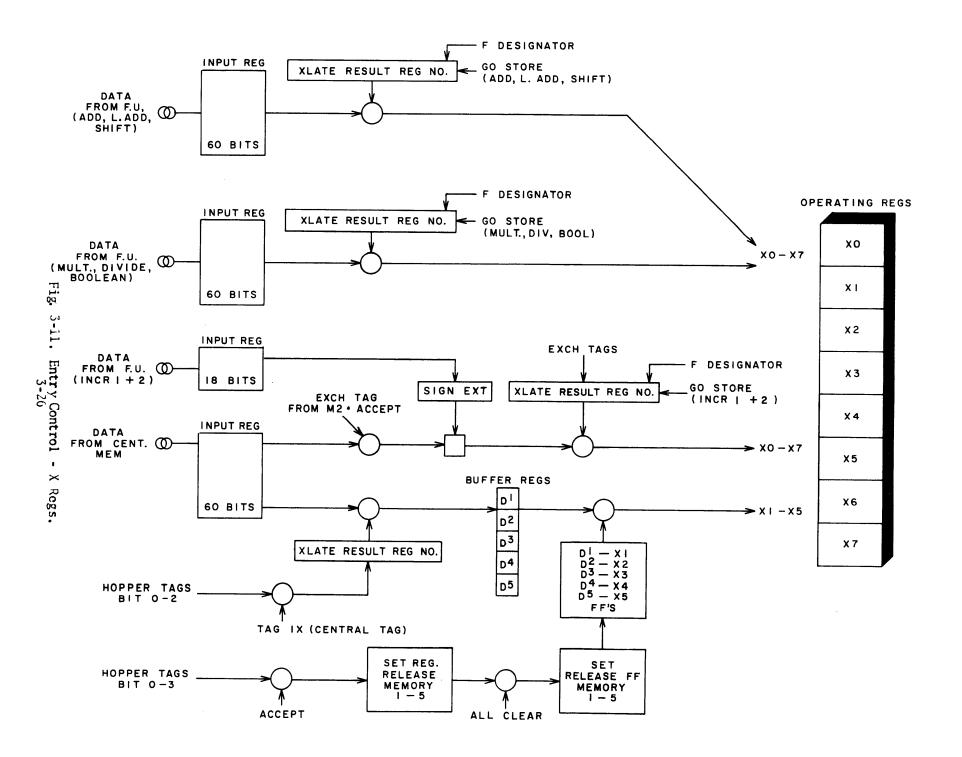

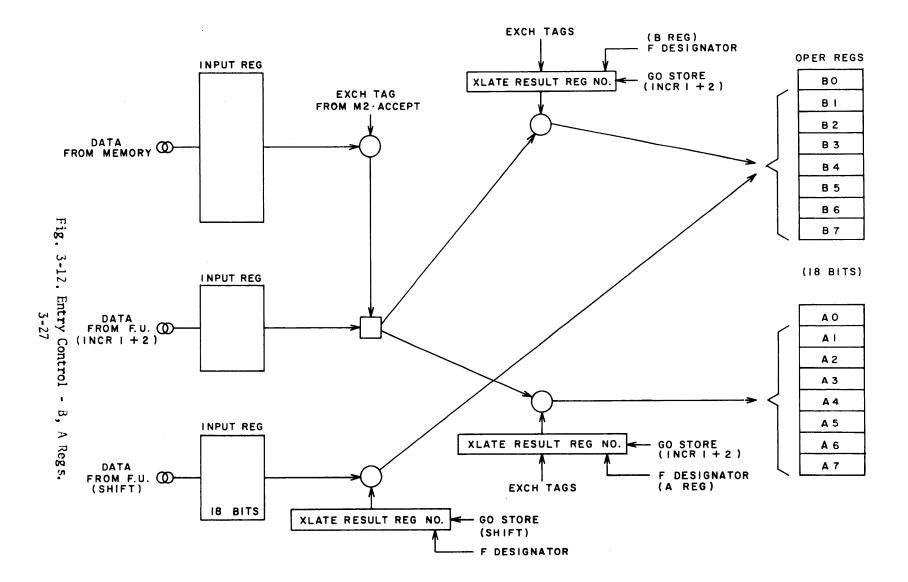

Entry Control

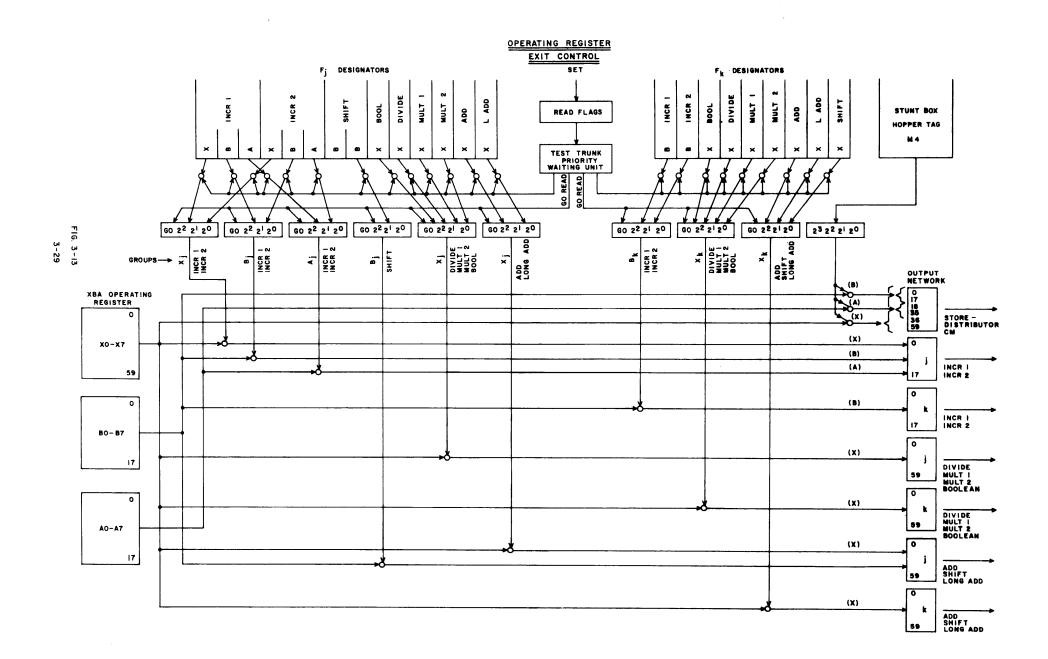

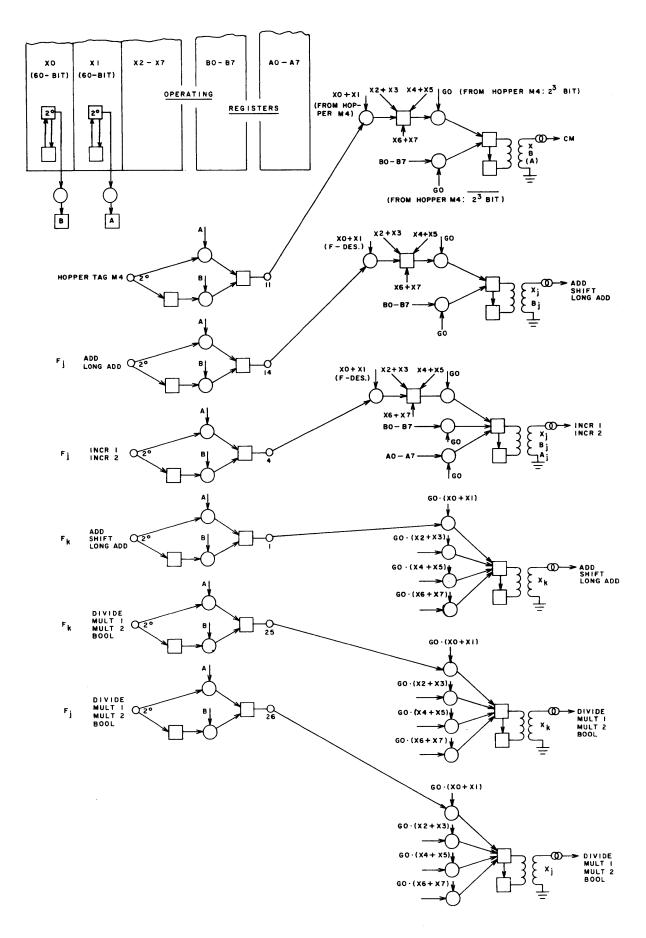

Exit Control

Data Trunks

CPU Timing Notes

Register Reservation Control

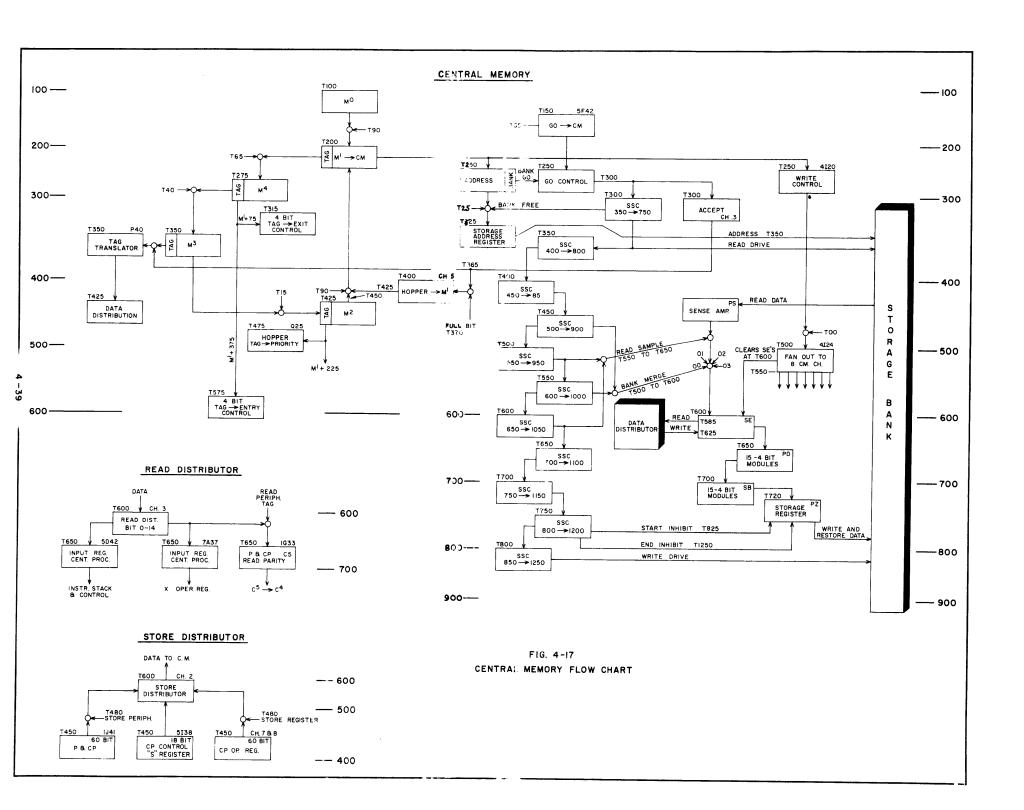

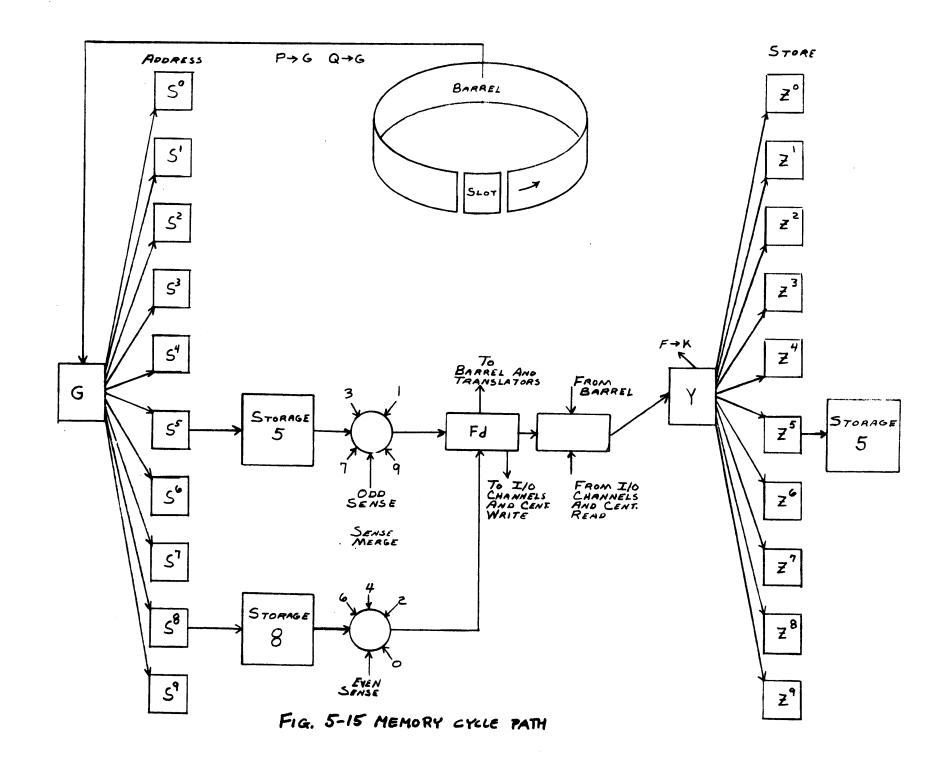

Section IV: Central Memory

Introduction

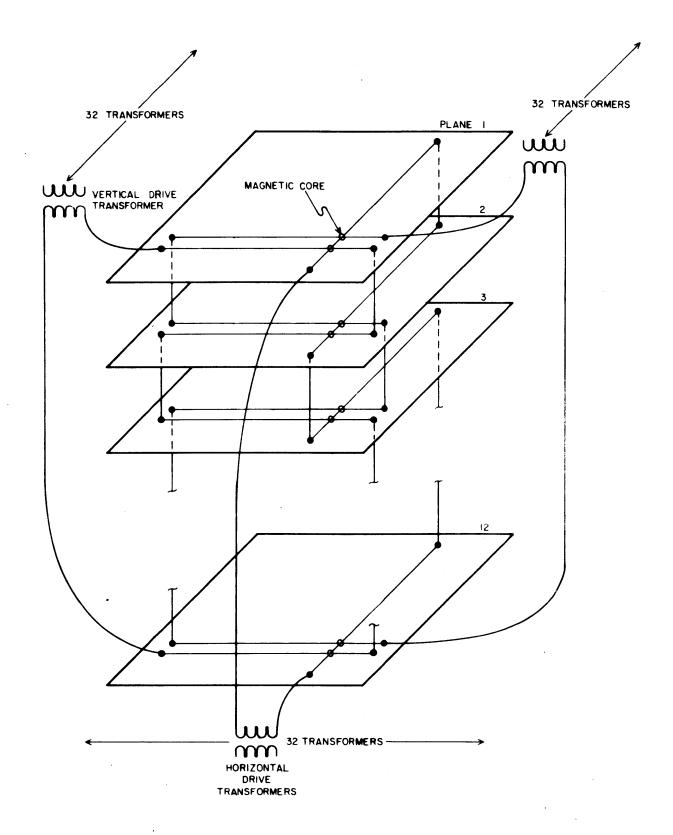

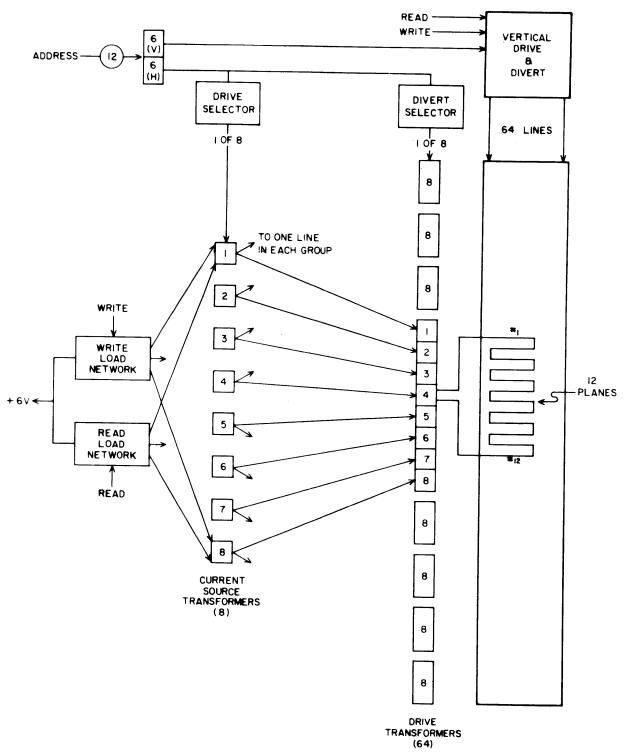

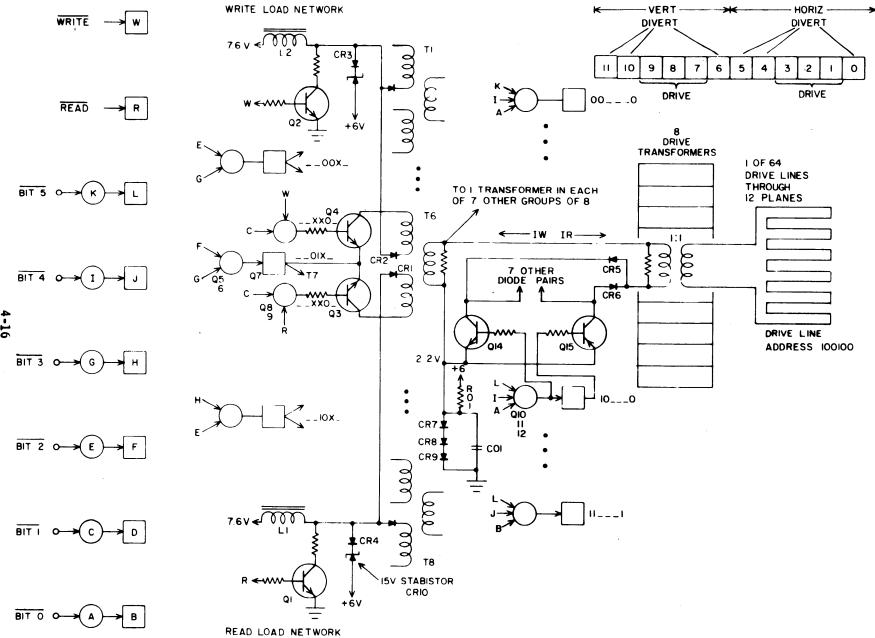

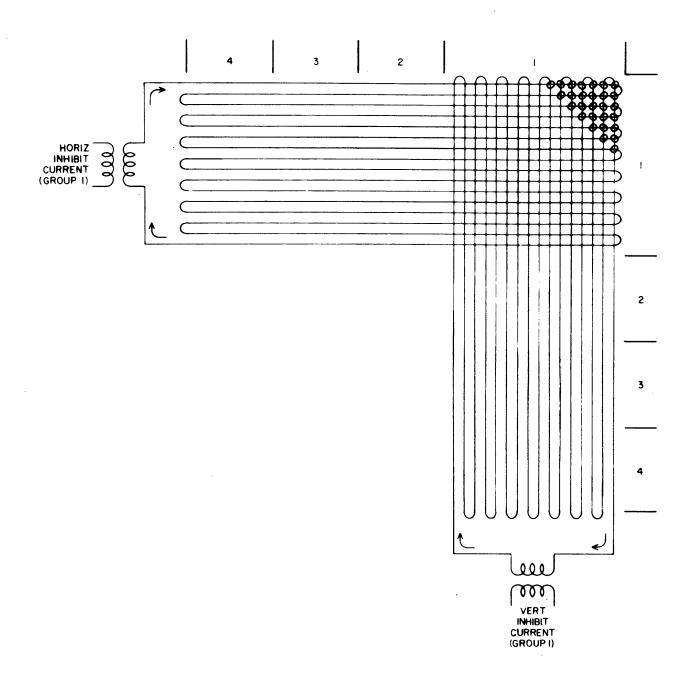

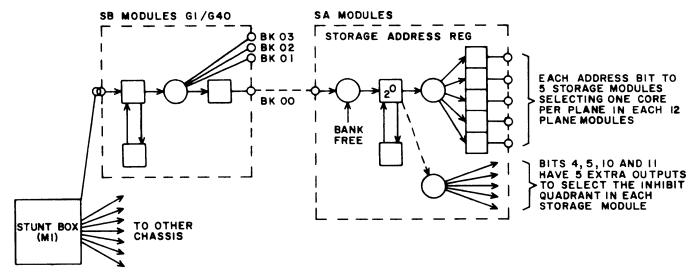

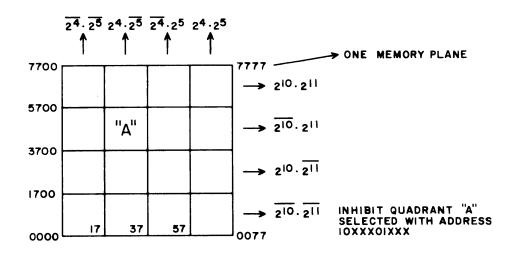

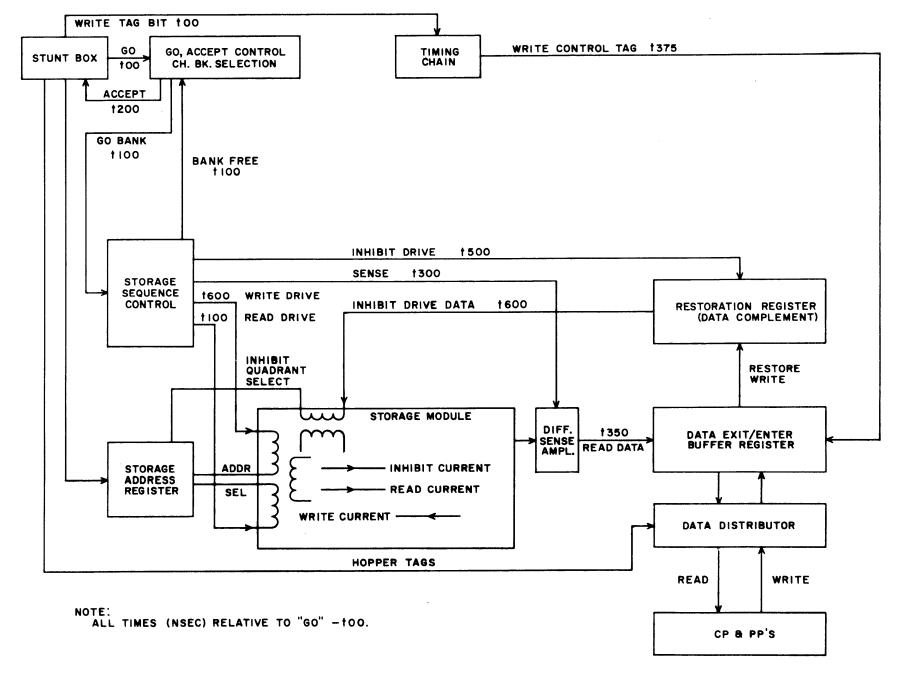

Storage Modules

Memory Reference Request

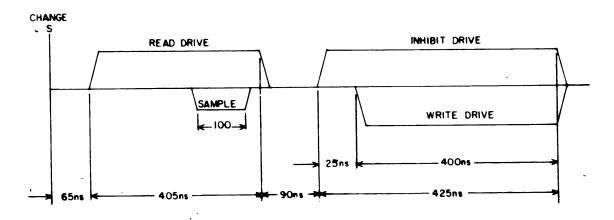

Storage Cycle

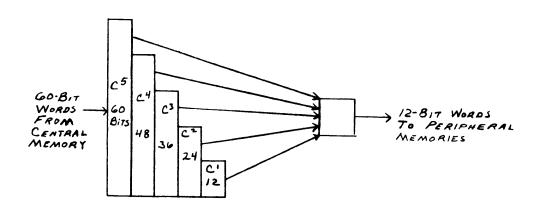

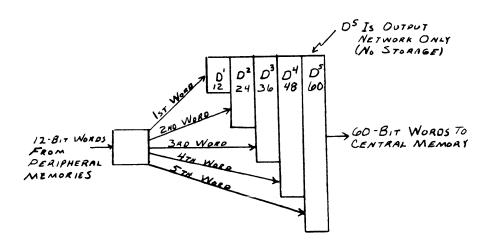

Data Distribution

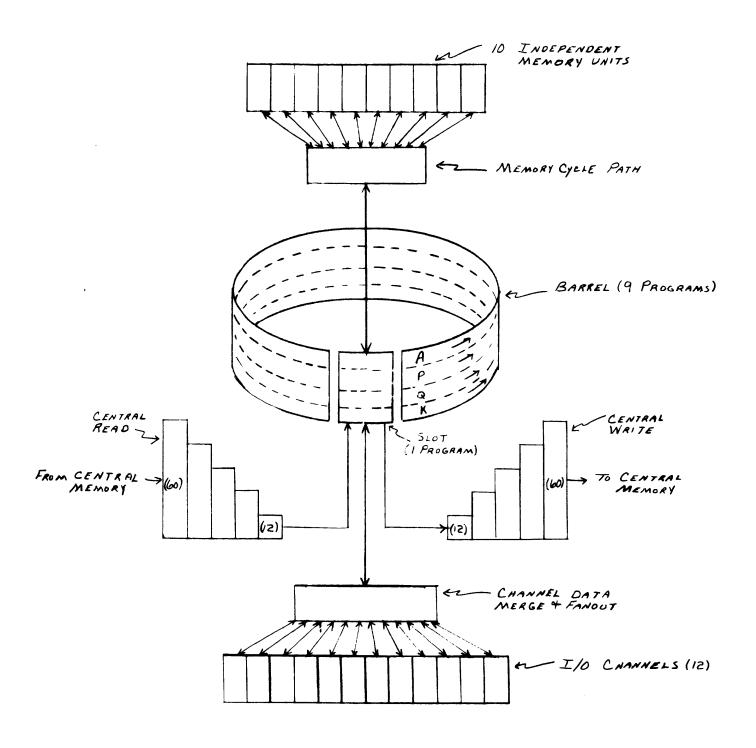

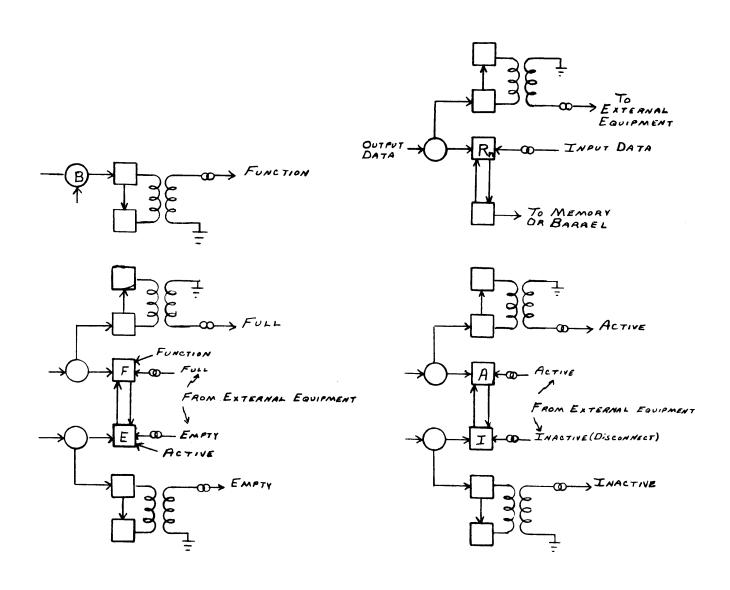

Section V: Peripheral and Control Processors

Introduction

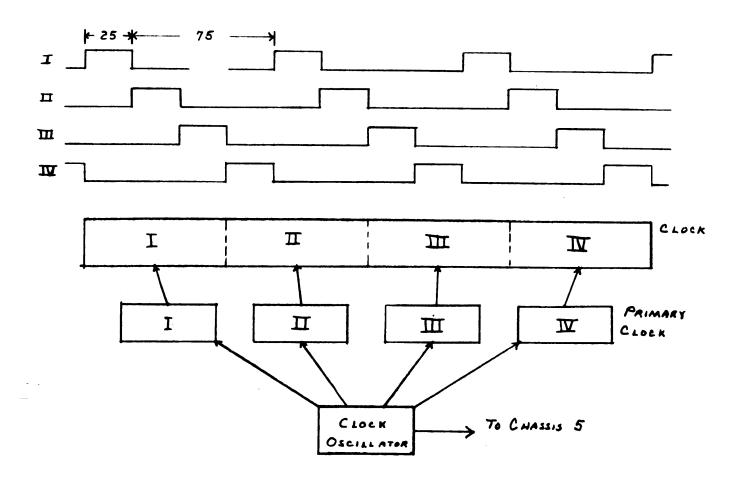

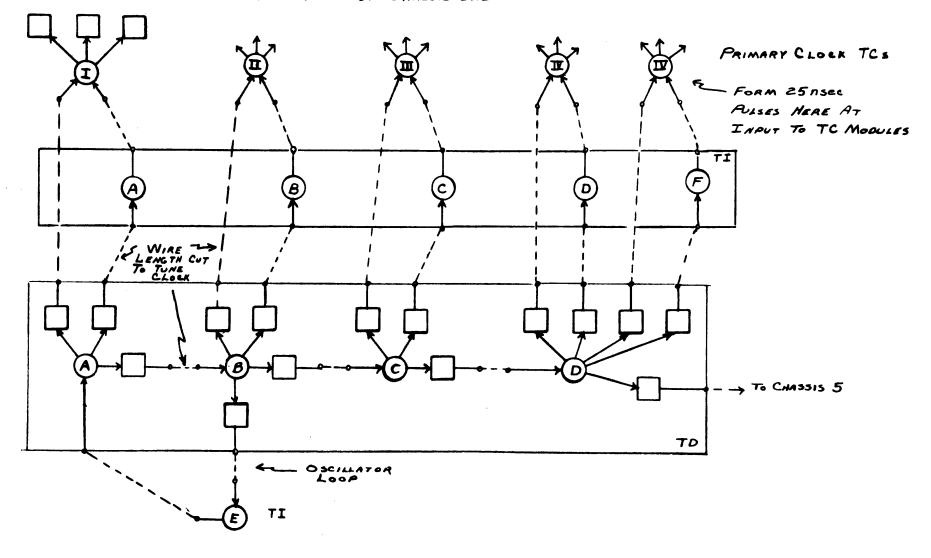

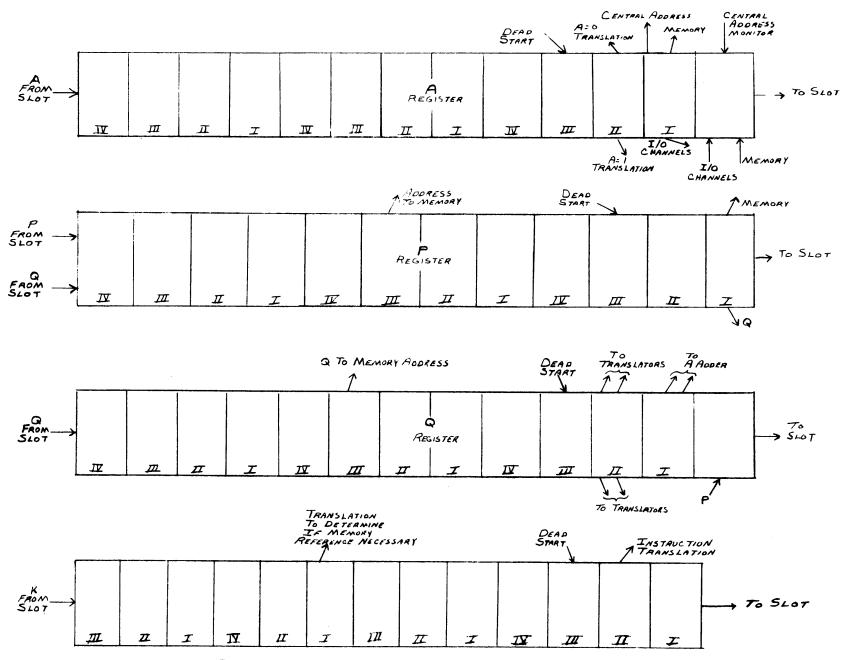

Timing

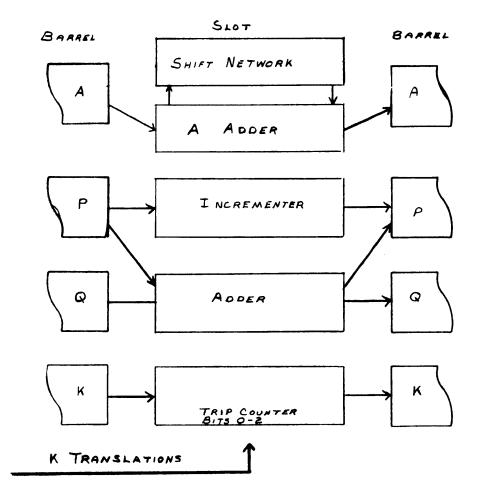

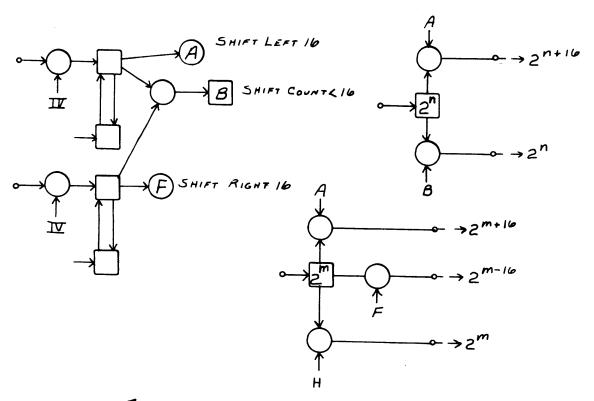

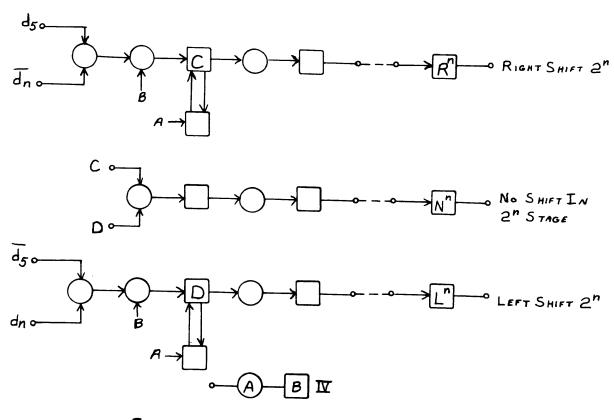

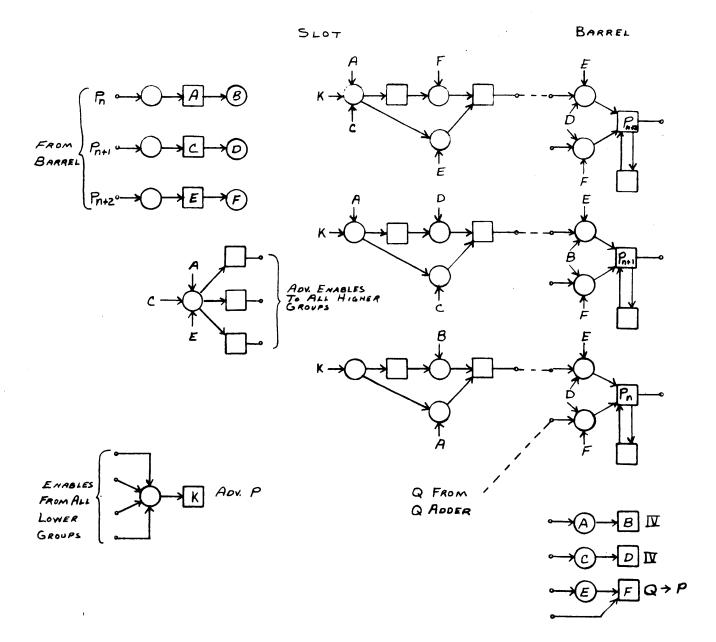

Barre1

Slot

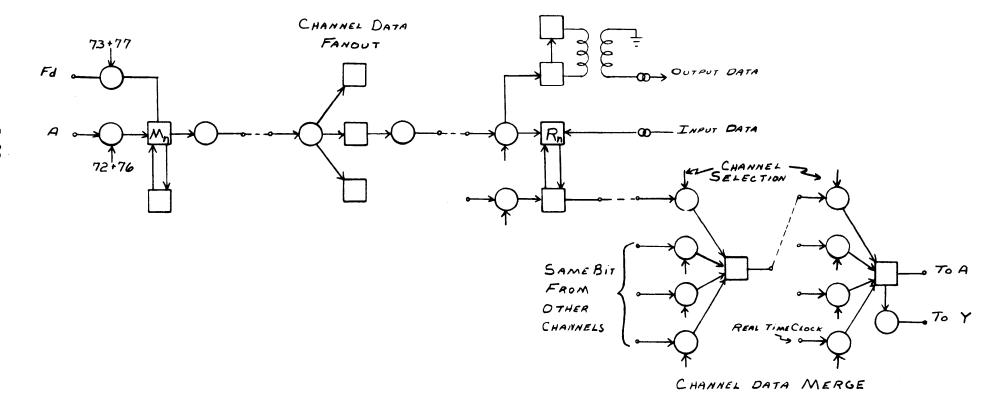

Memory

Input/Output

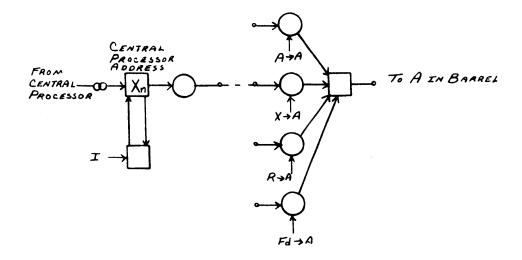

Communication with Central Memory and Central Processor

Dead Start

## **APPENDICES**

- A. Card Placement

- B. Circuits

- C. Peripheral Command Timing

- D. Infinite/Indefinite Forms

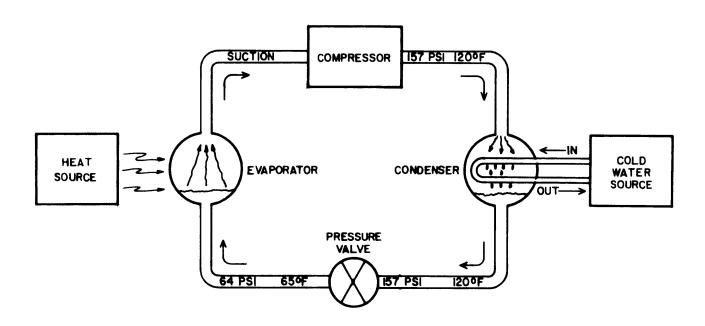

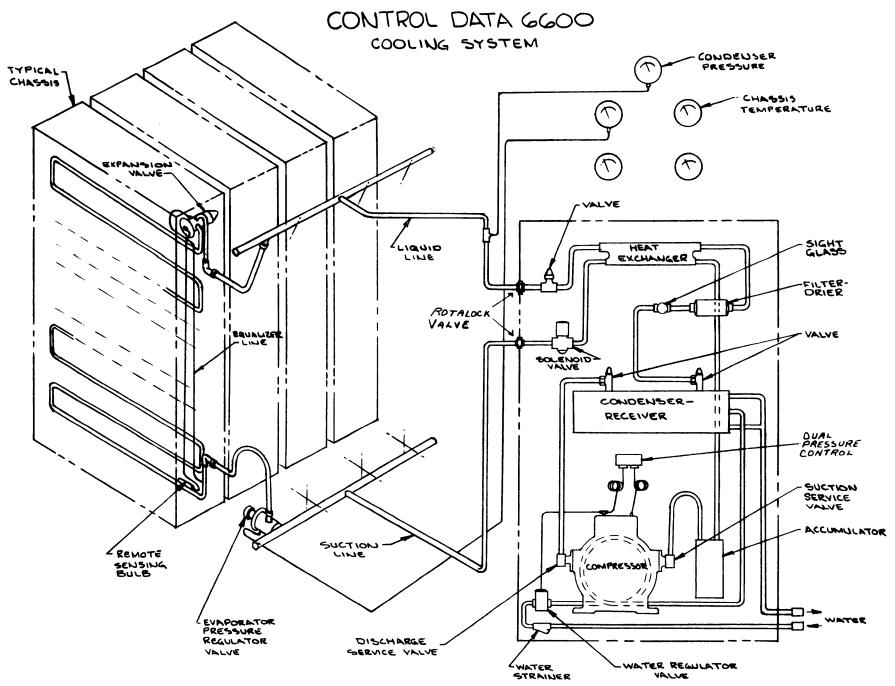

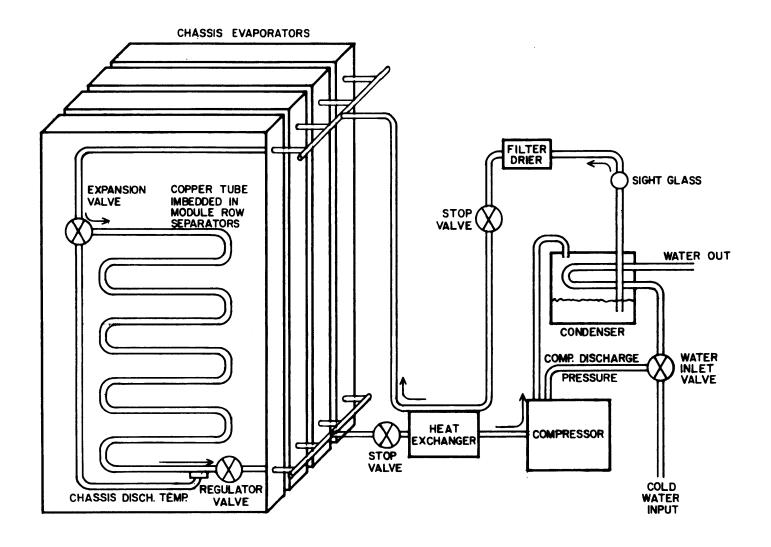

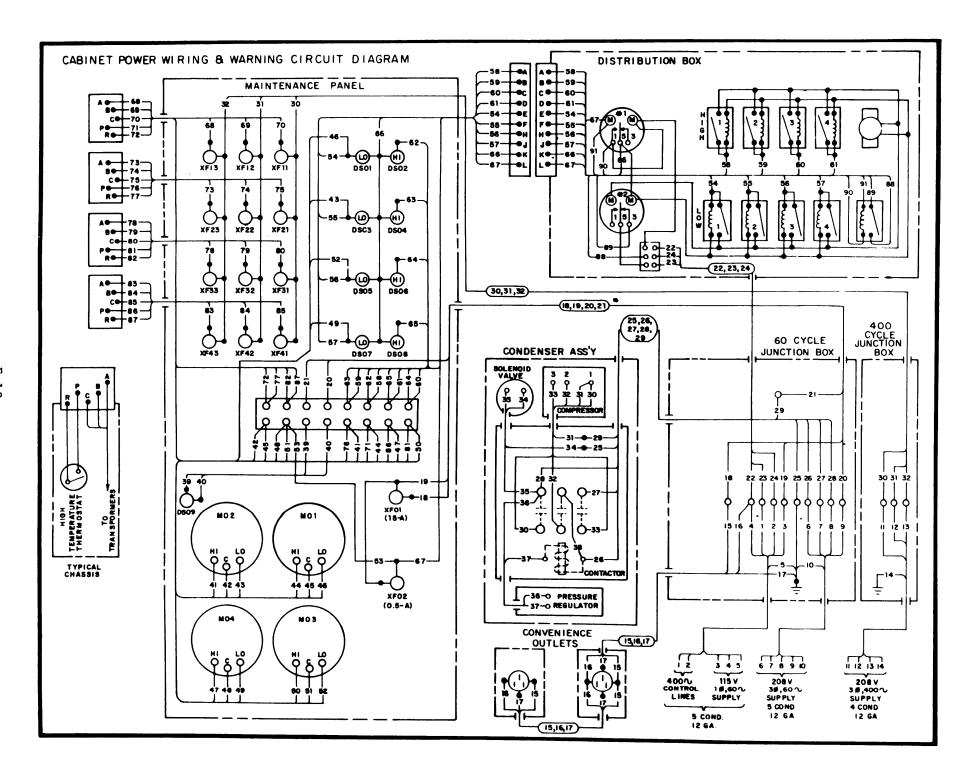

- E. Refrigeration System

# SECTION I

Central Processor Address Control

## ADDRESS CONTROL

## INTRODUCTION

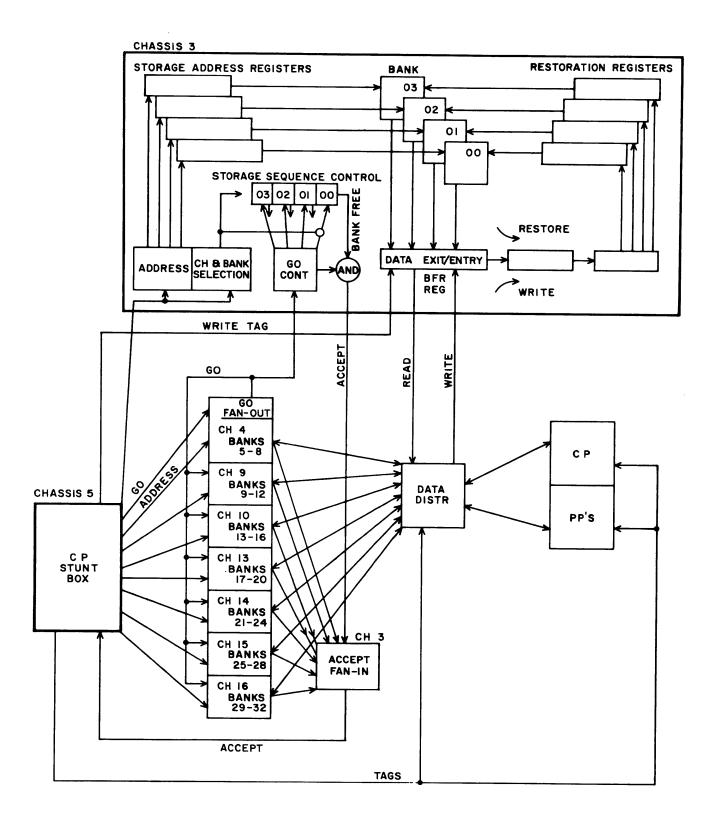

The basic concept of the 6600 computer is parallelism. In the central processor many parallel operations are in progress. One of these operations is accessing central memory. In many cases the peripheral processors will be attempting communications with central memory simultaneously with the central processor. This is a simplification of possibilities but points out that some method of orderly distributing requests for central memory time must be available.

#### IMPLEMENTATION

Central Memory is divided into 32 independent banks that can be accessed sequentially in an overlapping fashion. This allows memory references every 100 name-seconds. In order to make full use of central memory and also be able to fulfill the parallelism concept, there is an area of the central processor known as the STUNT BOX. It is to this area of circuitry that all references to central memory must first come. The job, therefore, of the stunt box is to collect requests for central memory access and to distribute these requests in an orderly fashion.

#### CON DI TI ONS

The 6600 has ten peripheral processors that can request reading or writing in central memory. The peripheral processors can also execute an exchange jump which requires central memory access. The central processor can reference memory for an instruction word or an operand.

Consequently the peripheral and central processors can send requests to the stunt box simultaneously. This presents the necessity for some means of priority within the stunt box and also some method of naming each of the memory requests in order that the data, once acquired, will know where it must go. Another factor that must be considered is some means of remembering addresses when the first attempted access is rejected because of a memory conflict. SUMMARY

In general, the stunt box:

- a) allows several simultaneous memory requests.

- b) establishes a priority for the issue of these addresses to central memory.

- c) issues the addresses to memory at a rate that will make maximum use of the 32 independent banks.

- d) remembers addresses that have not been accepted by the memory and must be re-issued.

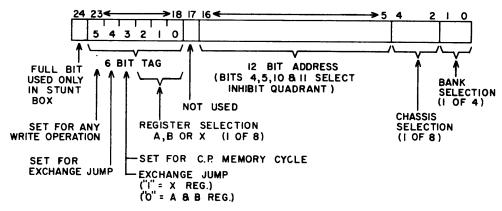

- e) adds a tag to the addresses to correctly distribute the data.

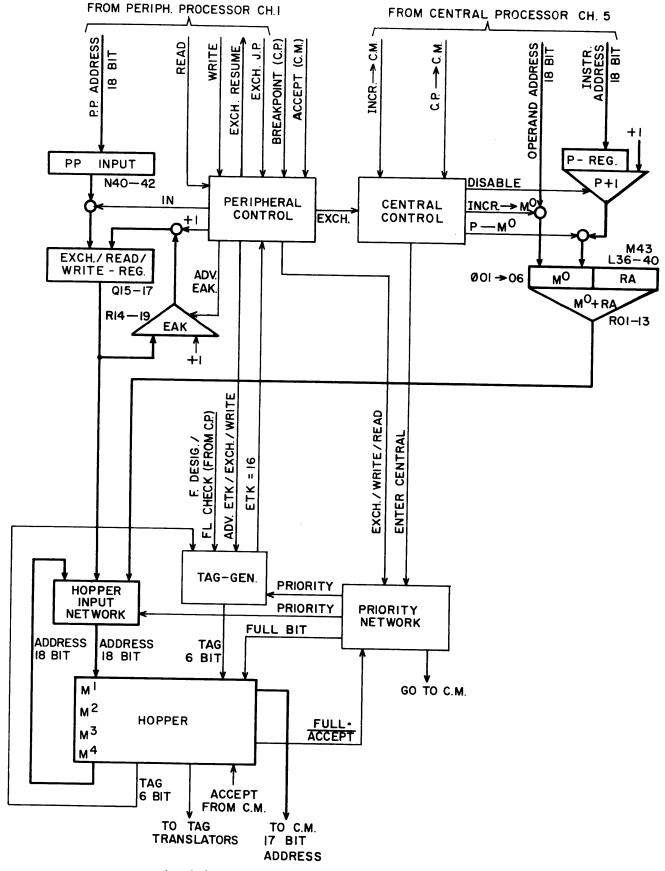

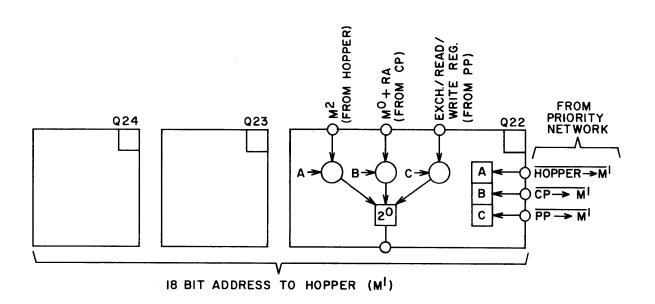

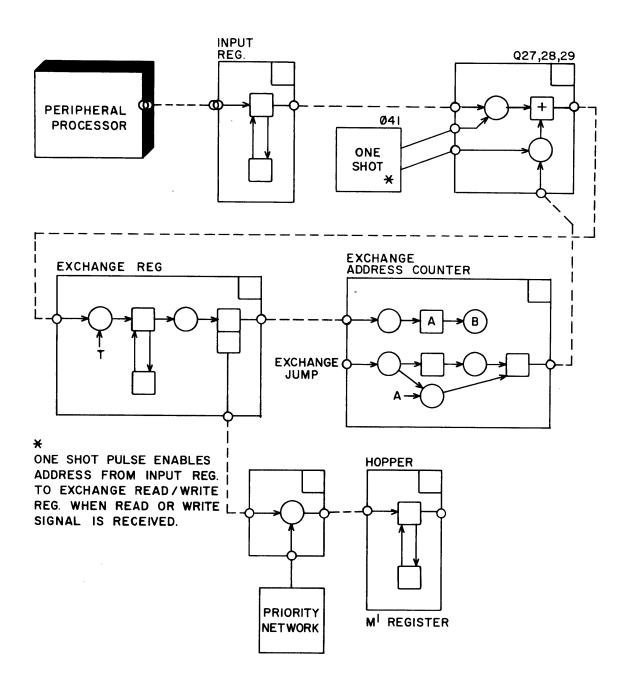

Fig. 1-1. Stunt Box Block Diagram

#### STUNT BOX

#### DESCRIPTION:

There are two main address flow paths to the hopper  $(M_1)$  and to Central Memory (CM): (Refer to fig. 1-1.)

- 1) The PPs supply CM with the write and read addresses for the dataexchange between PPs and CP. The exchange jump addresses are also sent over this line.

- 2) The central processor supplies CM with either operand or instruction addresses. Addresses comming through this path are always added to the content of the Reference Address (RA) Register.

A priority network controls the entry into the hopper (M<sub>1</sub>) from which the addresses are sent to CM. These addresses are also stored and circultaed in the hopper, from which, in case of bank conflict, they are re-issued to CM after 300 ns.

#### **OPERATION**

## Peripheral Control

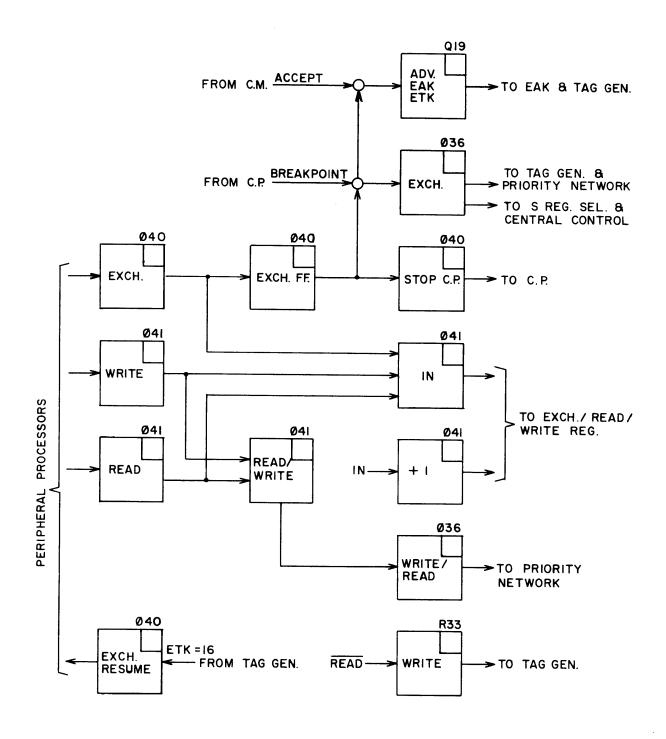

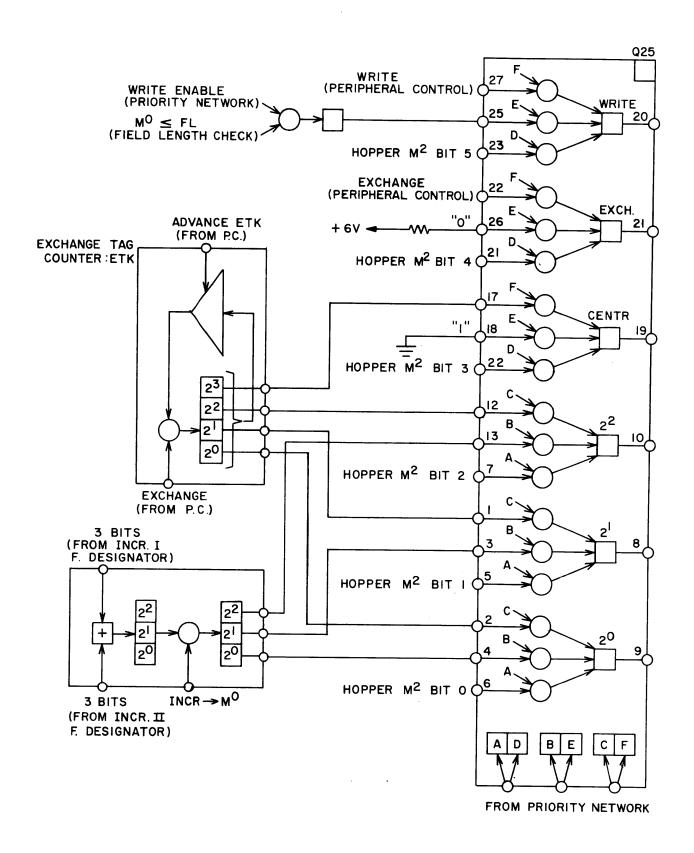

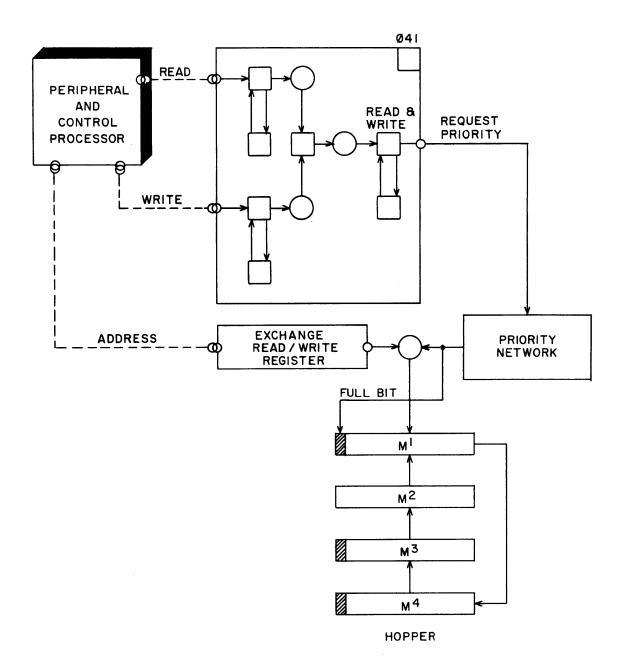

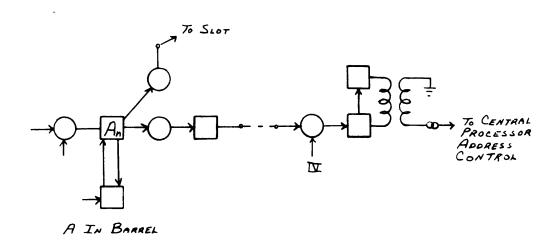

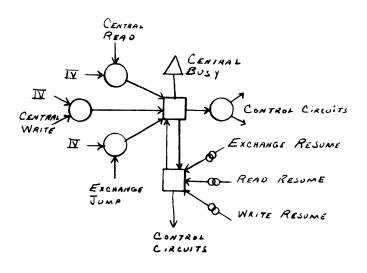

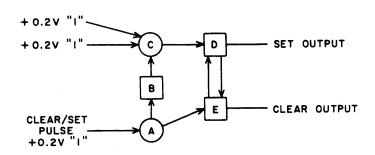

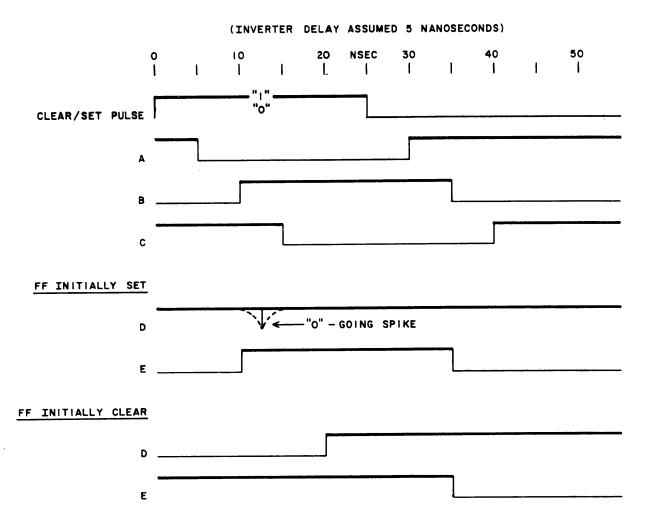

Peripheral Control, for the purposes of this discussion, is a term applied to that section of the central processor that handles addresses and signals from the peripheral processors requesting storage access. (Refer to the block diagram in fig. 1-2.)

When the peripheral processors send an address to the stunt box, an accompanying signal informs Peripheral Control whether it is a Read, a Write, or an Exchange Jump address. Peripheral Control (PC) then transfers this information to the tag generator to enable the IN-path to the EXCH/READ/WRITE Register. In

Fig. 1-2. Peripheral Control Block Diagram

an Exchange Jump, this signal also stops the central processor; when the "Breakpoint" signal indicates the central processor and central memory have stopped, it starts Exchange Address (EAK) and Exchange Tag Counters (ETK). The Exchange Address Counter then updates the address in the EXCII/READ/WRITE register for each step of the Exchange process upon receipt of the "accept" from central memory. When the Exchange Tag Counter = 16, Peripheral Control sends an "Exchange Resume" back to the peripheral processors (Write Resume is sent back from central memory chassis 2, and Read Resume from chassis 4).

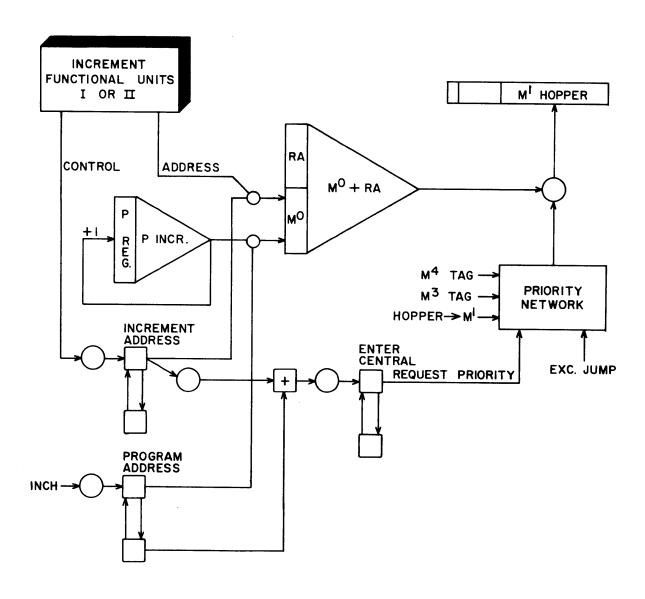

Central Control

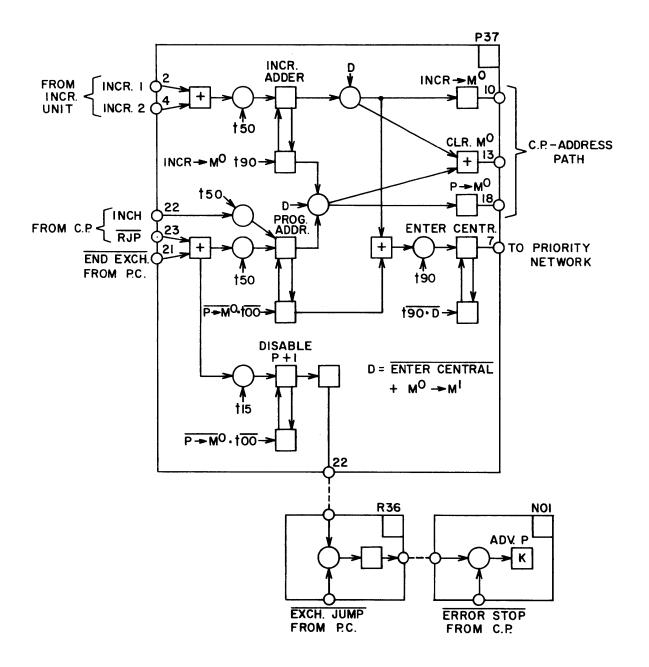

Central Control, for the purposes of this discussion, is a term applied to that section of the central processor that handles addresses from the central processor requesting access to central memory for instructions or operands. Central Control controls entry into  $M^{\circ}$  and requests entry (via the priority network) into  $M^{1}$ . (Refer to fig. 1-3.)

When an <u>operand address</u> is sent by one of the two increment units, the INCREMENT ADDRESS FF on P37 will set and the entry signal into  $M_0$  is enabled as soon as  $M_0$  is empty. Simultaneously, the ENTER CENTRAL FF sets indicating to the priority network that a central processor address is waiting to enter central memory.

When a <u>program address</u> is ready in P, the PROGRAM ADDRESS FF sets, enabling the P  $\rightarrow$  M0 signal if M0 is empty and if no operand address is waiting. This signal also sets the ENTER CENTRAL FF.

If a Return Jump instruction or an End Exchange signal occurs, the DISABLE P + 1 FF sets and the program address in P passes through the P-incrementor without being incremented. This does not affect the ADVANCE P gates on N37-N39.

Fig. 1-3. Simplified Central Control Network

## Priority Network

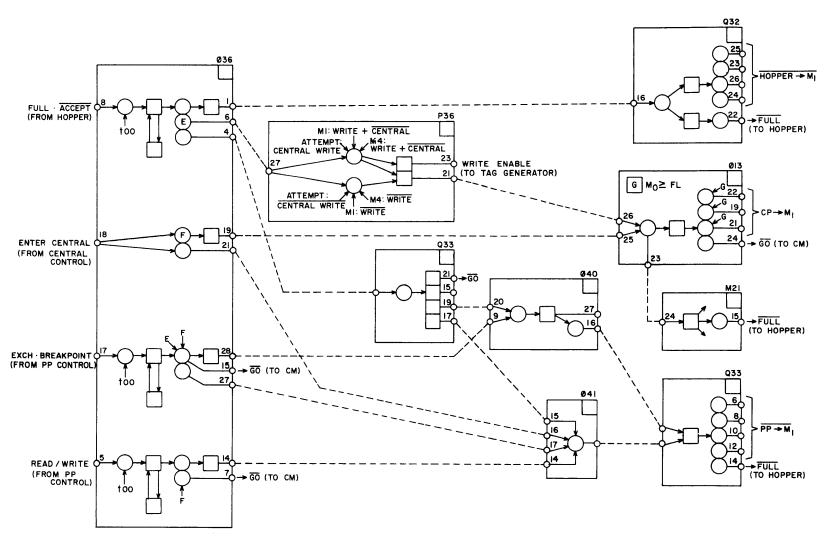

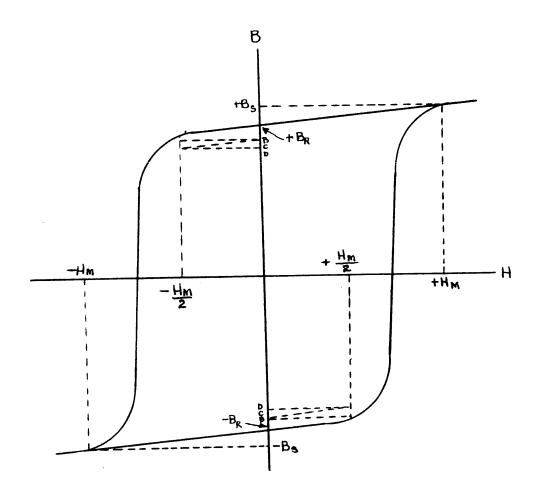

The priority network (fig. 1-4) controls inputs to the hopper by sequencing entry to the hopper when more than one address attempts to enter at the same time.

The fixed order of priority is as follows:

- 1) Address from Hopper

- 2) Addresses from the Central Processor

- 3) Addresses from the Peripheral Processors

An address from the hopper is given first priority since it is an un-accepted address due to a central memory bank conflict.

Addresses with second priority are from the central processor (i.e., M<sup>0</sup>). Since, for the central processor, storage modes cannot be mixed in the hopper, the Read or Write tags are examined before priority is granted. In attempting a Read, no Write address is allowed in M<sup>1</sup> or M<sup>4</sup>. In attempting a Write, no Read address is allowed in M<sup>1</sup> or M<sup>4</sup>. If modes are mixed, priority is not granted and entry of the address into the hopper is delayed until central memory has accepted those addresses and modes are no longer mixed.

Addresses from the peripheral processors are assigned lowest priority.

Thus, peripheral read and write operations from and to central memory may have to wait for hopper and central processor addresses. An important exception occurs during an Exchange Jump. An Exchange Jump a) stops the central processor, and b) inhibits communications between the peripheral processors and central memory. In this case, therefore, exchange jump addresses are the only addresses entering the hopper.

FIG. 1-4 PRIORITY NETWORK

With each address sent to the hopper, a Full bit is generated (to indicate the hopper register contains a usable address) and a Go signal is sent, along with the address, from M<sup>1</sup> to central memory.

The hopper input network is diagrammed in fig. 1-5. Three gates for each of the 18 address bits accommodate the three possible input paths to the hopper. Entry via these gates is controlled by the priority network.

Fig. 1-5. Hopper Input Network

## Tag Generator

When an address enters the hopper, a six-bit tag is appended to control the address and data flow. Depending on the source of the addresses, these tags are generated from three sources: (Refer to fig. 1-6.)

- An un-accepted address due to a bank conflict retains its tag that was generated when the address first entered the hopper.

- 2) An operand or instruction address from the central processor gets its tag from the translation of the F- designators of the increment units or from the central processor (in case of exit mode stops or return jumps) and from the priority network.

- 3) Addresses from the peripheral processors obtain their tags from

Peripheral Control. The Exchange Tag Counter (ETK), which controls

the execution of the exchange jump, generates the tags for all

addresses of the exchange jump package.

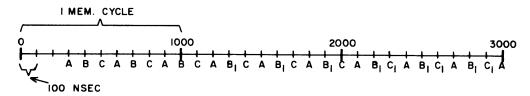

## Hopper

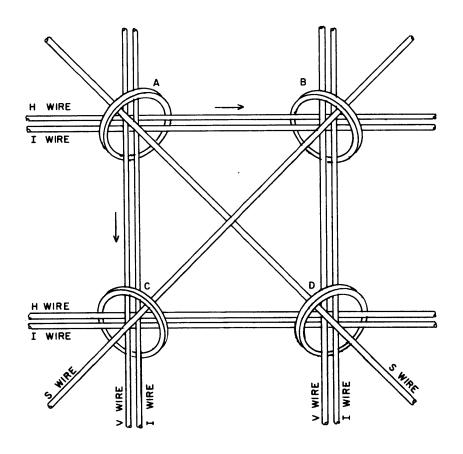

In general, the hopper consists of four registers (M<sup>1</sup>, M<sup>2</sup>, M<sup>3</sup>, and M<sup>4</sup>), each capable of holding an 18-bit address, a 6-bit tag, and a single Full bit.

(M<sup>2</sup> is an exception and does not have a Full bit). (A block diagram of the hopper is diagrammed in fig. 1-8.)

An address is sent to central memory from hopper register  $M^2$ . Hopper registers  $M^2$  -  $M^4$  store the address in case it must be re-issued because of a bank conflict. If the address is accepted by central memory, it drops out of  $M^2$ .

In the case of bank conflict, the priority network gates the un-accepted address from  $M^2$  back into  $M^1$  every 300 nanoseconds, until it is accepted by

Fig. 1-6. Tag Generator

central memory. An address can be accepted only if the specified bank is free at the time the address is in M<sup>1</sup>. Otherwise, it's possible for another address to request access to the same bank and tie it up for a memory cycle. Fig. 1-7 shows possible waiting times in the hopper for worst cases of bank conflict.

The six tag bits travel through the hopper with each address. (The hopper serves as a delay line for the tag.) This line is extended by two additional registers (see fig. 1-8). In each step, the tag controls address and data flow.

Hopper registers M<sup>1</sup>, M<sup>4</sup>, and M<sup>3</sup> have Full bits associated with the address. The purpose of the Full bit is to indicate to the priority network that the address must be reissued to central memory if no accept is returned.

Note that the Full bits also are sampled to stop the central processor (fig. 1-8).

Fig. 1-7. Hopper Waiting Time for Bank Conflicts

The Hopper can have a max. of 3 addresses. An address must be in M1 at the time when the memory cycle for its bank just finished so that it can be accepted by memory, otherwise bank conflict. The longest time an address will have to wait to be accepted in memory is when the address enters M1 300 ns after the memory cycle started.

Example: Let us say all 3 addresses in the Hopper need the same bank, then at t=1000, address B is accepted and a new address B<sub>1</sub> can enter the Hopper, at t=2000 address C and at t=3000 address A will be accepted.

(See timing diagram.)

Fig. 1-8, Hopper

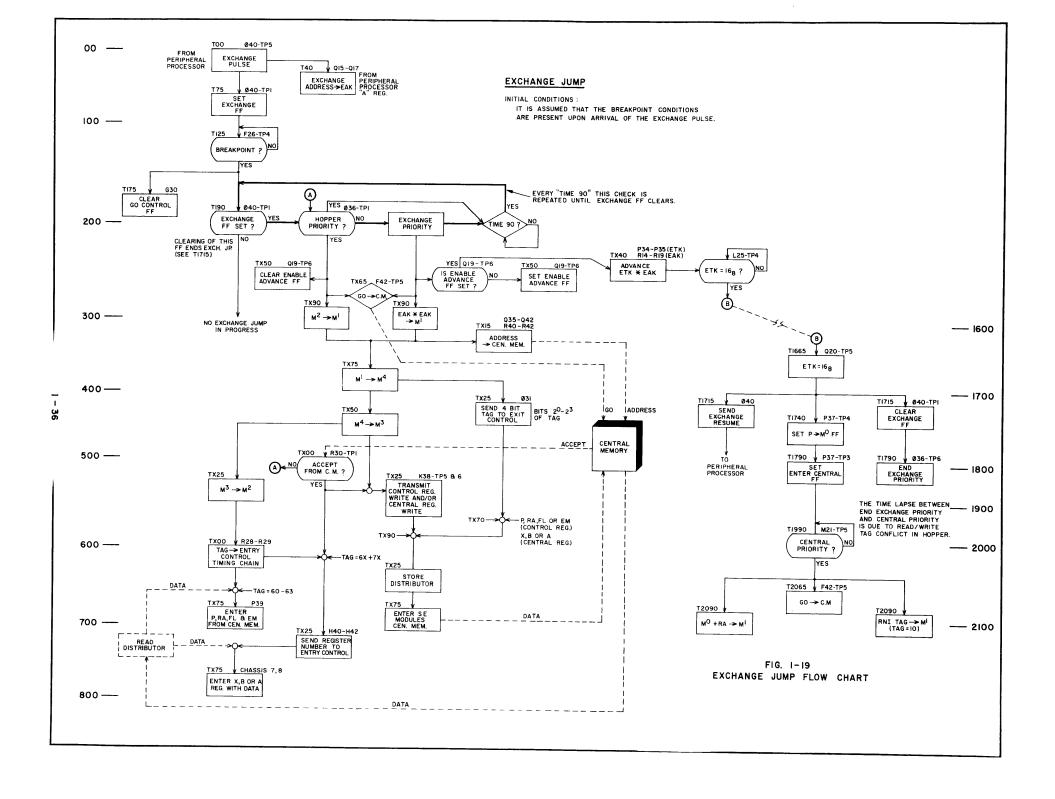

## Exchange Jump

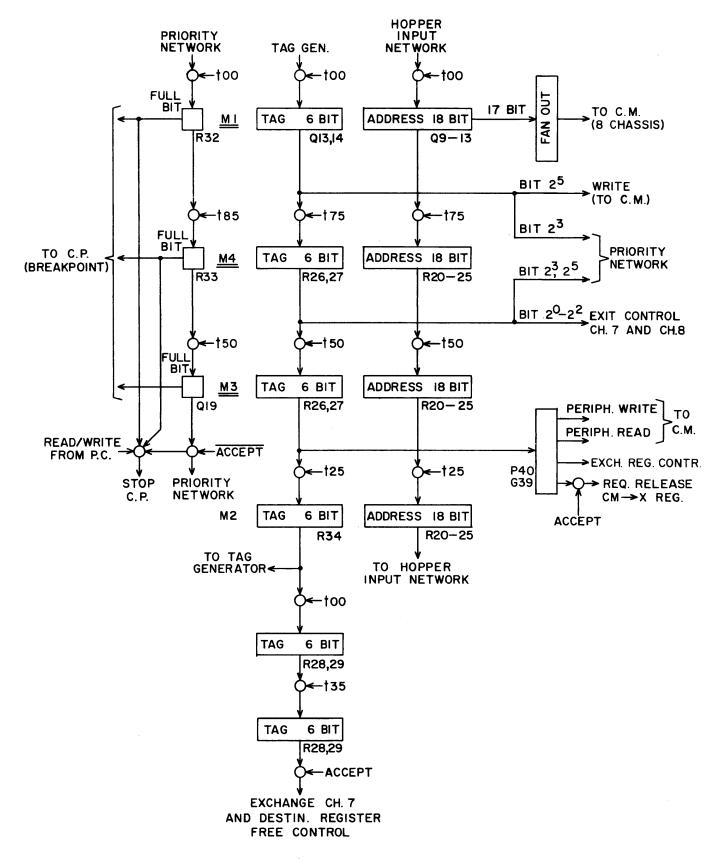

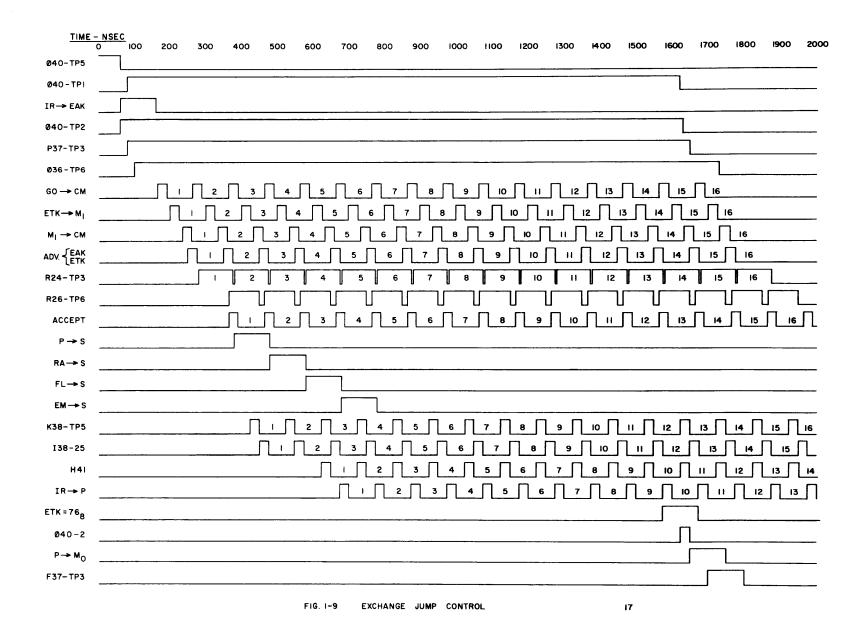

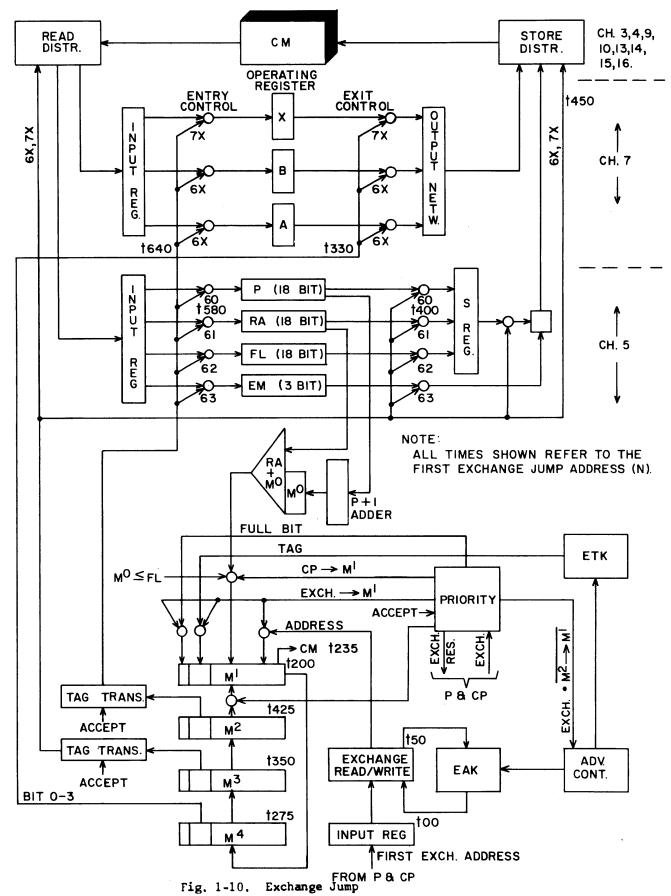

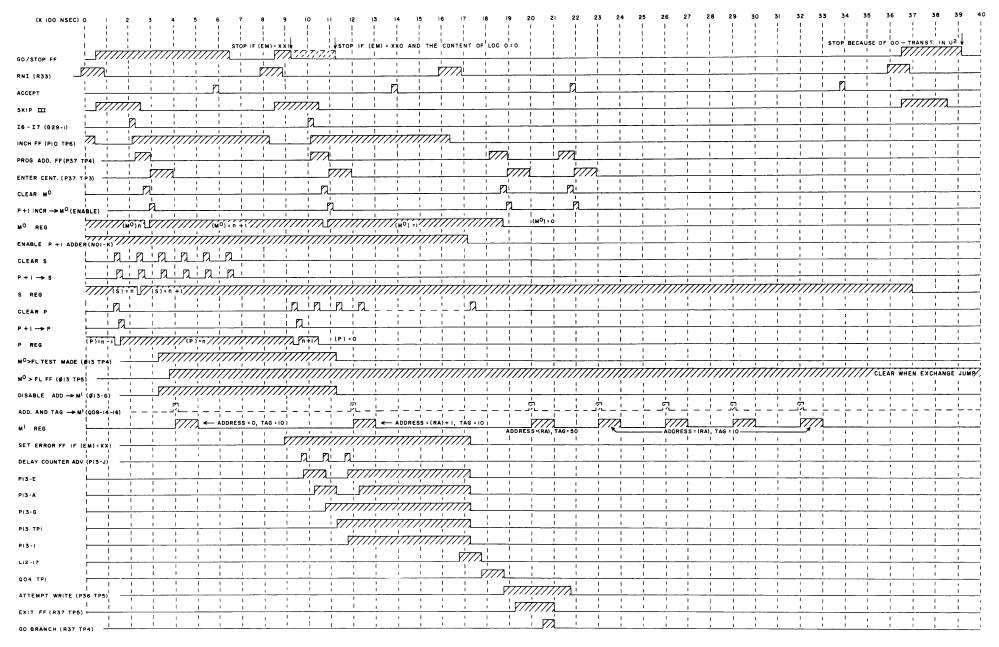

As an aid in following the somewhat detailed discussion which follows, refer to the central processor diagrams, the timing diagram in fig. 1-9, and the Exchange Jump diagram in fig. 1-10.

The following discussion assumes the Exchange Jump Package (see Reference Manual) is stored in Central Memory starting at address N. To start the Exchange Jump, a Peripheral & Control Processor will send an Exchange Jump pulse together with the 18 bit address N to the Stunt Box.

The address will be received by the Input Register (N40, 41, 42) and the Exchange pulse sets FF 040/TP5 at starting time 00. The "0" out of 640/P19 enables the A gates on Q27, 28, 29. At time 50 the contents of the Input Register are transferred to the Exchange/Read/Write Register Q15, 16, 17.

At t65, 040/TP2 will be set, setting F37/TP3. If the computer is not running when we start our Exchange Jump, we cannot make the AND gate next to F37/TP3 because we don't have an Issue. However, a "0" from F37/P24 entering I01/P21 and a "1" into I01/P26 are AND'ed giving a "0" into F37/P8 and therefore a "1" from F37/P7. If the computer is running the AND gate at the output of F37/TP3 is not made until an Issue signal occurs and the parcel counter = 1. The output of pin 10 then becomes a "0". This "0" clears the GO FF on G30, stopping the Central Processor. The "1" from F37/P7 will be passed on to F26/P12. If the Hopper is empty and no Branch or REgister reservations are up we will get a "1" into F26/P10 makes the AND gate and sets F26/TP4, placing a "0" into 040/P10. With the t75 pulse, 040/TP1 sets, disabling the A gates on Q27, 28, 29.

This enables a "1" from 040/Pl3 to set the Initiate Exchange FF on 036/TP6

at t100. A "0" from 036/P15 and a t165 pulse sends a GO signal to central memory to prepare the path for the address being sent. Also at t200 a 60 tag from Q25 of the Exchange Tag Counter is sent to  $M^{1}$ .

The Initiate Exchange FF also sends a "1" to priority control, which, in turn, enables the C gates on Q22, 23, 24, 25. At t200, the contents of the Exchange/Read/Write Register are transferred to M<sup>1</sup> in the Hopper. During the time the address waits to enter M<sup>1</sup>, a path from the Exchange/Read/Write Register thru the Exchange Address Counter allows the address to circulate without being incremented until it can be accepted by M<sup>1</sup>.

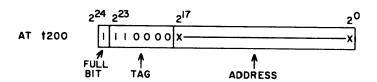

A bit called the Full bit is sent from the priority control to  $M^1$ . This bit is only used in the Hopper to indicate that the Hopper contains a usable address. The  $M^1$  Register should now contain the following bits:

At t235, the address is sent from M<sup>1</sup> to all banks of central memory. As the largest possible address in central memory can be specified by 17 bits, the bit position 2<sup>17</sup> in M<sup>1</sup> is not sent to central memory. At t275, all 25 bits of M<sup>1</sup> start their cycle thru the Hopper (M<sup>1</sup> to M<sup>4</sup> to M<sup>3</sup> to M<sup>2</sup>). Once our address has been accepted by central memory, an accept signal is sent back (130 ns after sending out M<sup>1</sup> to central memory) preventing out address from reentering M<sup>1</sup>. From M<sup>4</sup>, M<sup>3</sup> and M<sup>2</sup> the tag bits are extracted and sent to the Exit control of the Operating Registers and to the Tag Translators.

This completes the process of sending the first address of the Exchange

Jump Package from the Stunt Box to central memory. Since the Exchange Jump

Package occupies 16 sequential addresses in central memory, the next 15

addresses must be generated in the central processor. The Exchange Address

Counter increments the first address and subsequent addresses to provide these

fifteen sequential addresses. From the Exchange Address Counter, they will be

sent to central memory at a maximum rate of one every 100 nanoseconds.

The Exchange Address Counter is advanced as follows:

At t160, Q19/TP6 was set and remains set throughout the Exchange Jump. The "1" from Q19/P26 provides a "1" from "K" on R14 (t200) which advances the counter. The B gates on Q27, 28, 29 were enabled at t115 and also remain enabled throughout the Exchange Jump. At t250, the new address (N+1) enters the Exchange/Read/Write register.

At the same time, the Exchange Tag Counter increments the tag by one and sends it to M<sup>1</sup> along with the new address. When the Exchange Tag Counter reaches 76<sub>8</sub>, a "0" into 040/P6 sends an Exchange Resume (t1630) back to the Peripheral 8 Control Processor and also clears FF TP1 and FF TP2 (t1630). This drops the advance pulses for the Exchange Address and Exchange Tag Counters. However, the counters still have time to reach N+17<sub>8</sub> and 17<sub>8</sub> respectively, completing the Exchange Jump in the Stunt Box.

#### Operation

The previous section described the controls for an Exchange Jump. This section attempts to explain the sequential operation of the exchange jump in the central processor.

The purpose of an exchange jump is to exchange the controls for one program with new controls for a second program. In the 6600 central processor the controls for any program presently running will be found in the 24 operating registers A, X, B and in the control registers P (program address), RA (reference address), FL (field length) and EM (exit mode). Before the exchange jump was executed, values for the above listed registers were loaded into an area of central memory and called the exchange jump package. The starting point of this area in memory was defined by the address N when we executed the exchange jump.

When the first address of the exchange jump entered the hopper, a tag was added. This tag, when translated, provides the gates necessary to exchange the P register and the A<sub>o</sub> register with the contents of address N of the exchange jump package.

## P -> Address N

A tag translation of 60 and an accept signal enables a "0" from P40/P1 at t400, which goes to the S register to enable the contents of the P register into the S register. Then at t465, (P) are sent to the Store Distributor. From M<sup>3</sup>, the 6-bit tag is extracted (t380) and transferred to the tag translator, P40. Together with an accept it will provide a "0" out of P40/P20 (6X and accept) which is fed through 041/P26 to K38/P20. At t450 a Central Register

Write signal is sent to the Store Distributor allowing the P register to be written into address N, bit positions 36-53 of central memory.

## Address $N \longrightarrow P$

During the same memory cycle, we read P (the contents of P stored in the Exchange Jump Package) from address N and send it via the Read Distributor to the Input Register (B42, A41, 42, C41 on Ch. 5). A 60 tag from P39/P1 and an accept enables the contents of the Input Register into the P register at t580.

## Ao -> Address N

The lower 4 bits of the 60 tag are extracted from M4 and sent to G02 (Ch. 8) and H26 (Ch. 7) of the Exit Control. The 23 bit (the "GO" bit) is a "O" which indicates that an A or B register can be transferred into memory. The lower 3 bits are also "0"'s, indicating the register number is 0. As the  $B_0$  register is not connected to memory, we can only send the Ao register to memory. The "l" from H26/P3 (Ch. 7) is AND'ed with t30 on E31 to give a "0" output from E31/P18. This "0" goes into F32, 33, 34, 35/P10 and E26, 27/P10 allowing the 18 bits of the Ao register to be sent to address N, bit positions 18-35, of central memory. Address N --- Aa

From R29 thru P19 and O33 (Ch. 5) a GO bit is sent to Chassis 7, G37/P15. This GO bit passes thru C36,A35 and enables the C gates in the Input Register B40, 41, 42 etc. on Chassis 7. The output of P39/P27 on Ch. 5 (a "0") is fed through H42/Pl0 into Chassis 7, H27/Pl1, setting the G0 FF. This provides a "O" output from H27/12 thru C20, E28 and into C27/Pl6. This GO bit enables the transfer of the Input register thru C27, 28 etc. into the Ao register G15, 16 etc. This concludes the exchange for P and A<sub>0</sub> of address N. As the second address N+1 is sent to memory, the tags will be set to 61, enabling the exchange of RA, Al and Bl. When the Exchange Tag Counter reaches  $76_8$  the Enter Central FF on P37/TP3 is set. This forces a 10 tag (RNI) and a full bit into M<sup>1</sup>.

After all the 16 addresses have exchanged their contents, the new program address in P will be sent to M<sup>1</sup> together with the 10 tag and full bit to start the execution of the new program.

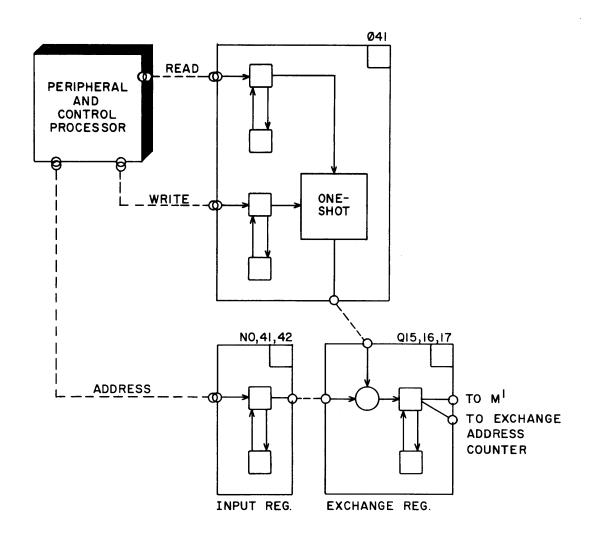

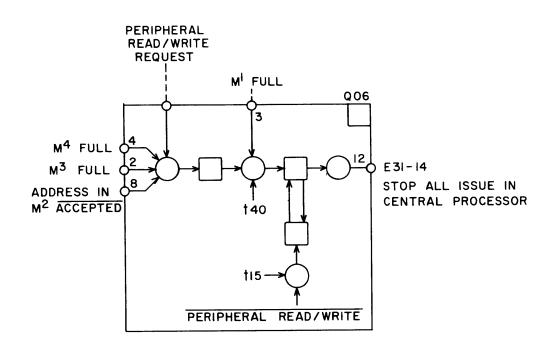

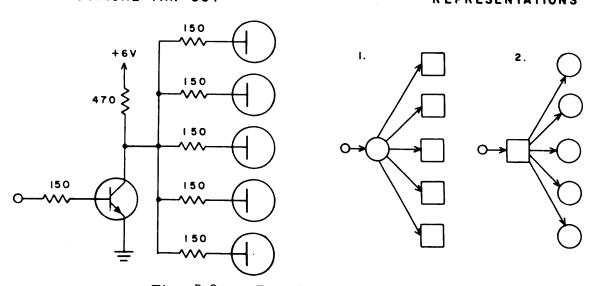

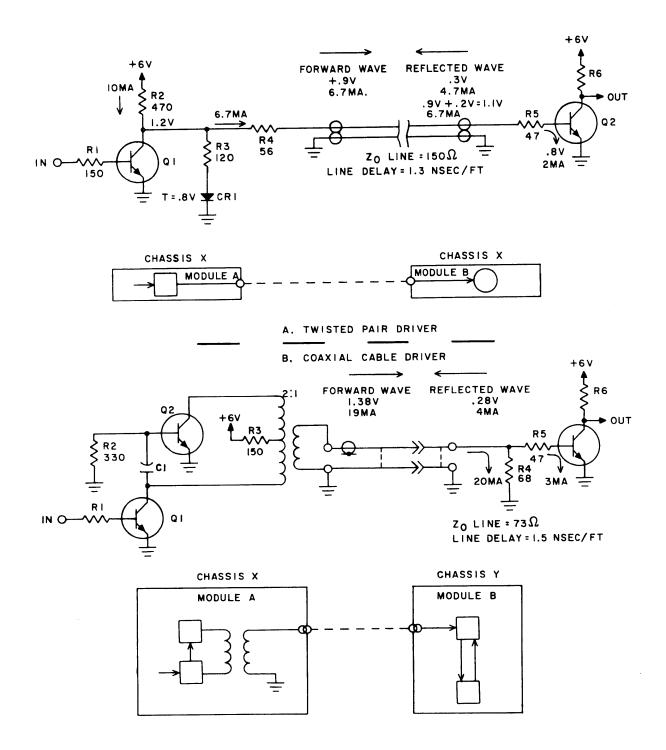

## Peripheral Read/Write

When a peripheral processor requests access to central memory for a read or write, the peripheral processor sends the appropriate signal to the stunt box. The signal is received at time 00 on chassis 5, module 041. The peripheral processor also sends the central memory address from its "A" register. The address is received in the input register in chassis 5 at time 00 on modules N40, N41, N42. The appropriate read or write signal received at 041 generates a 50 nanosecond one-shot pulse on pins 2, 4, 8 8, to gate the address from the input register to the Exchange/Read/Write register located on modules Q15, Q16, Q17. (Refer to fig. 1-11.)

At this time, the controls on 041 attempt to gain priority to enter the hopper. (signal on pin 10) Since priority to enter the hopper may not necessarily be available, the address in the exchange register is retained until it can be transferred to the hopper. To accomplish this the address circulates through the exchange address counter located on modules R14 thru R19. The address is not advanced, however, since the advance pulse is only enabled during an exchange jump. (Refer to fig. 1-12.)

When the peripheral address is attempting to gain priority in the stunt box, the "Central Busy" flip-flop in the peripheral processor is set. This prevents any other peripheral processor from attempting a central memory reference. The "Central Busy" flip-flop will only be cleared after the latest address has been accepted by central memory.

Fig. 1-11.

Fig. 1-12.

To avoid the situation where the central processor ties up the hopper such that a peripheral processor request for memory cannot be honored, the circuitry stops the central processor, honors the peripheral request, and then restarts the central processor. Conditions for stopping the central processor are:

- 1. Address in M<sup>2</sup> not accepted.

- 2. M<sup>3</sup> full

- 3. M<sup>4</sup> full

- 4. Peripheral read or write request.

## Full Bits and Tags

When priority for the peripheral read or write address has been established, the priority network enables the gating of the address into the hopper (gates on Q25, Q26, Q27). At this time a tag and Full bit will be appended to the address.

## Full Bit

Appending the Full bit is accomplished by setting flip-flop R33/TP1 with the address to  $M^1$  enable. (Refer to fig. 1-14.)

The tag for a peripheral read is <u>00</u>; the tag for a peripheral write is <u>40</u>.

One of these two tags must be appended to the address in the hopper when a peripheral sead/write is attempted. When priority has been granted for gating the peripheral address to M, the "enable peripheral to M" term on 033/TPl makes the "C" and "F" gates for the fan-in on Q25. This fan-in permits entry of the proper tag into M<sup>1</sup>. In a peripheral read, all the inputs to the fan-in will be zero.

Fig. 1-13.

Fig. 1-14

In a peripheral write, the write bit (2<sup>5</sup>) will be a "1" since the R33/TP2 FF is set. Once the peripheral address is in the hopper, the address will be issued to central memory until it can be accepted. When the address has been accepted, the tag is translated from the hopper and sent to memory control to allow memory to send the data and resume signals to the peripheral processor.

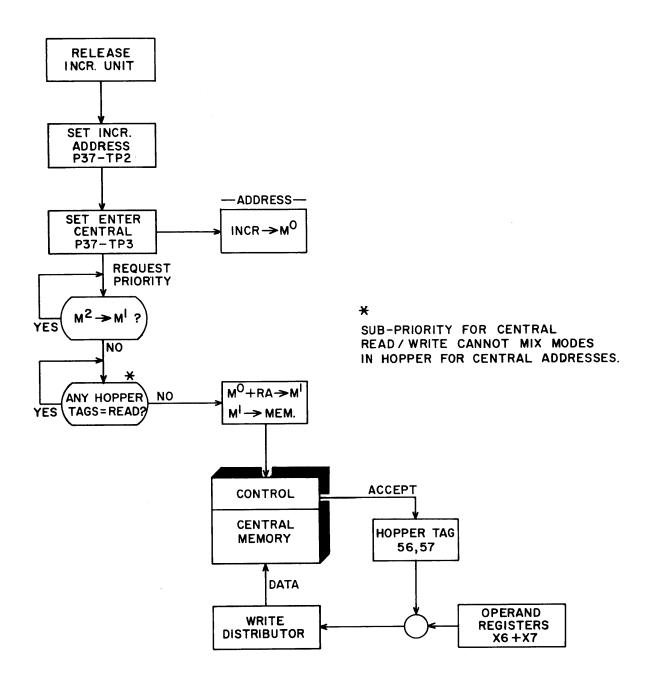

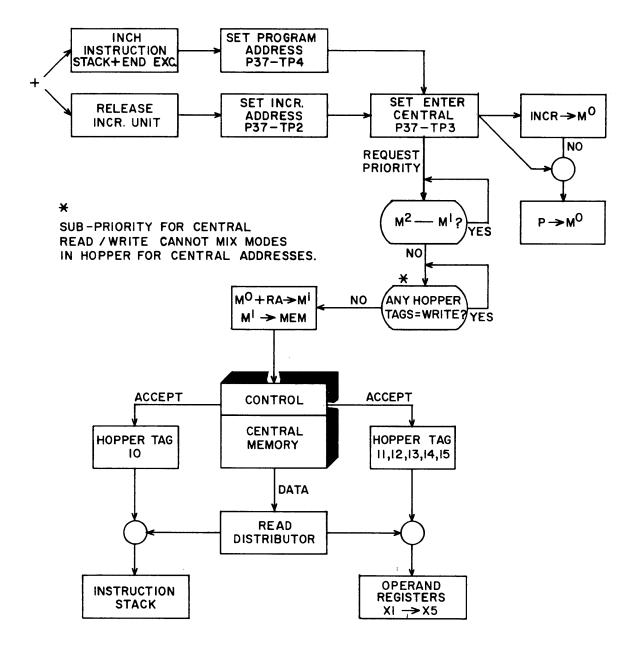

#### Central Read/Write

When the central processor attempts a central memory read or write operation, the address originates from one of two basic sources:

- from the Program Address, P, register when the memory request is for an instruction word, and

- 2) from one of the Increment functional units when the memory request is for an operand.

As diagrammed in fig. 1-13, either the Increment Address FF or the Program Address FF sets the Enter Central FF. Setting the Enter Central FF initiates action to request priority for the address to enter the hopper.

The address, in either case, is gated to a common register ( $M^{\circ}$ ). The contents of  $M^{\circ}$  are added to the reference address (RA) and this address is gated to hopper register  $M^{\circ}$  when priority has been granted and  $M_{\circ} \leq FL$ .

#### Program Address

The central processor Program Address register, P, and its incrementor network always hold the address of the last instruction word read from memory. When the next instruction word is needed, an "Inch" signal sets the Program Address FF. This gates the contents of the P register + 1 to the M<sup>O</sup> register, providing M<sup>O</sup> is not holding an address that has not yet entered the hopper. In addition, if there are addresses comming to M<sup>O</sup> simultaneously (i.e., from P and from the Increment units), the Increment address has priority over P+1 for entry into M<sup>O</sup>.

## Increment Address

When an instruction that causes a change in the A registers one through seven (Al - A7) is executed in the Increment units, the address developed is sent to the

Fig. 1-15. Central Read/Write

Stunt Box to make the necessary memory reference for loading or storing operating registers  $x^1 - x^7$ .

An increment instruction (51 - 57), when nearing completion, sets the Increment Address FF. Subsequent events are as outlined above.

Figs. 1-16 and 1-17 diagram the sequence of events for central memory read and write operations.

## CENTRAL WRITE

Fig, 1-16

## CENTRAL READ

Fig. 1-17.

Fig. 1-18.

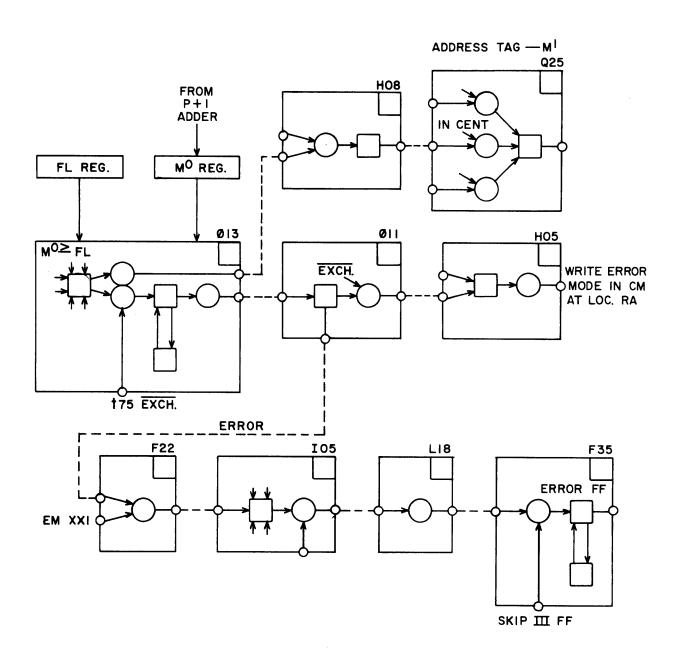

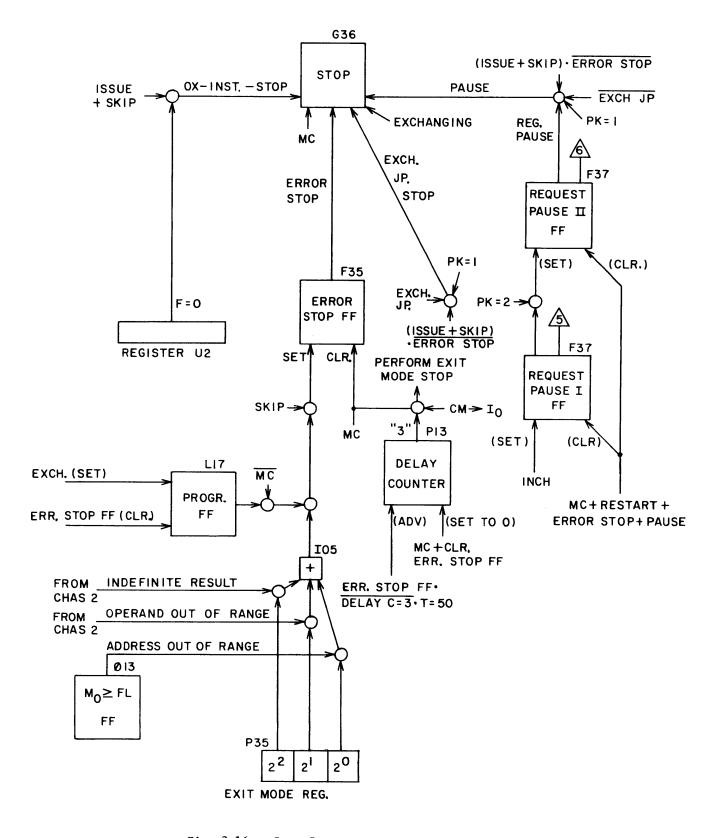

#### EXIT MODE

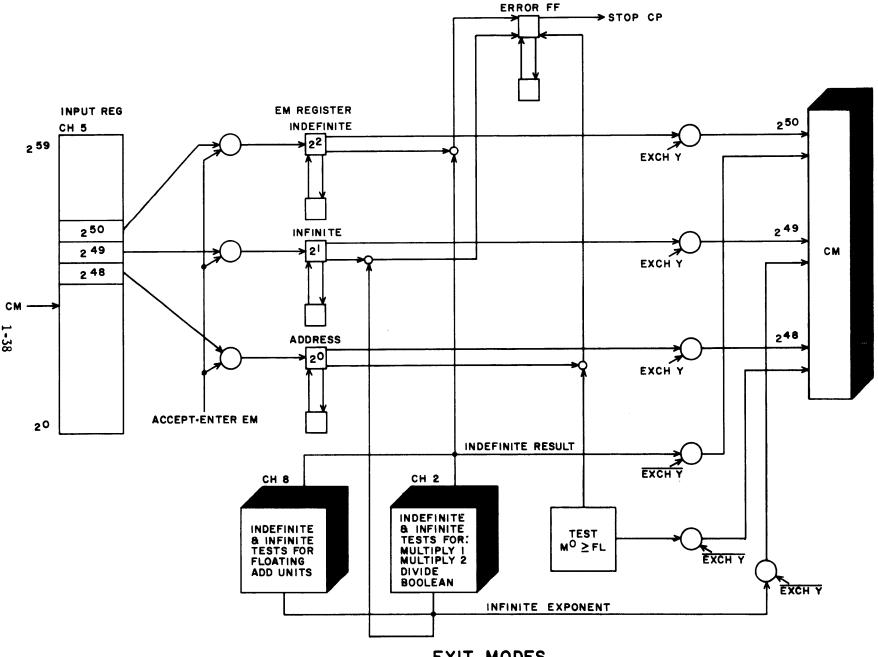

The exit mode feature allows the programmer to choose the exit or stop condition of the central processor. Exit selections are stored in the EM-register, and the exit mode occurs as soon as it is sensed. The various exit conditions are:

- 1. Normal stop

- 2. Address out of bounds (M° > FL)

- 3. Operand out of range (infinite)

- 4. Indefinite operand

The address RA (and hence P = 0) is reserved for recording program exit conditions.

## 1. Normal Stop

The translation of a normal stop instruction (fm = 00) in the  $U^2$  translator together with a SCBD ISSUE will set the STOP FF(G30 TP1). The P register will be cleared, so that the contents of the P register is 0. The peripheral and control processor searches for a central processor P = 0 conditions (instruction 27) to determine that the CP has stopped.

## 2. Address out of bounds

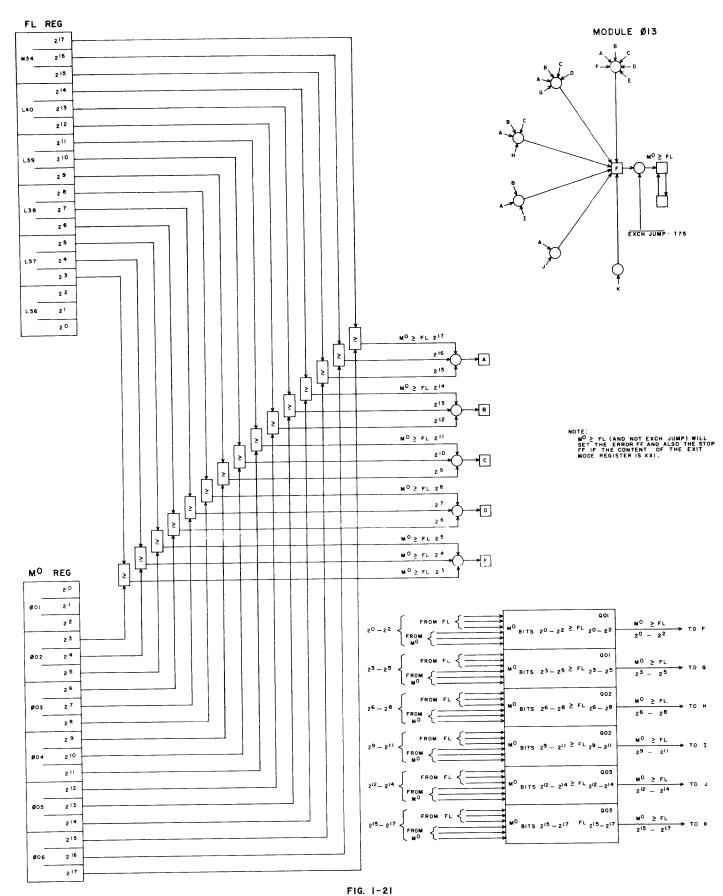

## M° ≥ FL test

The contents of the M° register is continuously compared with the contents of the FL register as follows:

a. A bit by bit comparison of bits  $2^3 + 2^{17}$  (M°  $\geq$  FL) and three results of these comparisons are comprised in one group (anded together). If one bit of M° is less than the corresponding bit of FL the group output is "0".

EXIT MODES

MO - FL COMPARISON

b. Each of the 6 octal digits of  $M^{\circ}$  is compared with the corresponding octal digit of FL. If  $M^{\circ} \geq$  FL the output will be a "l".

The output of (a) and (b) are anded together to decide if  $M^{\circ} \geq FL$ . If  $M^{\circ} \geq FL$  and we are not in an Exchange Jump the  $M^{\circ} \geq FL$  FF (013 TP5) will be set. Supposing the contents of the EM register is XX1 and the Skip III FF is set, the  $M^{\circ} \geq FL$  will set the ERROR FF.

The output of the comparison network will also inhibit sending the write bit of the hopper tag to the hopper and does not allow the value of  $M^{\circ}$  + RA to be sent to  $M^{\circ}$  if  $M^{\circ} \geq FL$ .

## Address out of bounds, exit mode not selected (EM) = XX0

When the central processor attempts to reference a memory location out of bounds, an out of bounds exit mode is <u>not</u> selected. If out of bounds is selected the central processor will stop at the Reference Address.

#### RNI OUT OF BOUNDS

If the program counter (P register) attempts to send an address that is out of bounds (this would be the RNI situation), the  $M^{\circ} \geq FL$  check circuit will inhibit sending the intended address to the hopper. Instead an address of all zeros and the proper RNI tag will be sent to the hopper. This will result in the reading of memory address absolute zero as well as the data going to the instruction stack and the U register translating networks. If absolute address zero had contained an all zero data word the results would be to stop the central processor, because of the translation of a stop (00) at absolute address zero.

# EXIT MODE STOP (RNI OUT OF BOUNDS) M<sup>O</sup>≥FL? -> NORMAL OPERATION YES SET MI = ADDRESS = O TAG = 10 SET MO≥FL FF SKIP III Y (EM) = XXI READ LOC = 0 -0 **ERROR FF** BLOCK P->S SET STOP FF CLEAR P DK = 3 START DELAY COUNTER BLOCK P+1 → P DK = 3 INCH (PIO TP6) CLEAR ERROR FF SET QO4 TPI DISABLE P+1 ADDER CLEAR DELAY COUNTER ATTEMPT WRITE P36 PROG ADD. FF ENTER CENT. FF SET EXIT FF SET GO BRANCH (P37 TP4) SET M = ADDRESS = (RA) TAG = 50 PROG ADD FF WRITE IN LOC (RA) OO XX XXXXXX 0-0 ENTER CENT. FF SET MI = ADDRESS = (RA) TAG = 10 READ LOC (RA) **PROCEED** RNI, PROCEED CLEAR STOP FF cm -> IO TRANSL FM = 00 IN U2 SCBD ISSUE

1-41

Fig. 1-22

SET STOP FF

## READ OPERAND OUT OF BOUNDS

If the increment unit changes Al-A5 (read memory to X) with an address that is out of bounds, again the  $M^{\circ} \geq FL$  check circuits will inhibit the sending of the address to the hopper. Instead an all zeros address will be sent to the hopper with a 10 tag. This will result in referencing memory location absolute zero and the contents of this location will go to the indicated X register. No affect on the running program will be seen except that the contents of the X registers will not be what is expected.

## WRITE OPERAND OUT OF BOUNDS

If the increment unit changes A6+A7 (store X6+X7) with an address that is out of bounds, the  $M^{\circ} \geq FL$  check circuit will inhibit the sending of the out of bounds address to the hopper. Instead an address of all zeros will be sent to the hopper. Usually the tag for a store X6+X7 is a 56+57, but if the address is out of bounds the tag will be changed to a 16+17, this tag will inhibit sending the central register write tag to the store distributor. The results of this zero address and 16+17 tag in the hopper is the referencing of address absolute zero. When the data gets to the data distributor however, the lack of any tag will cause the data to be lost. There will be no effect on the running program, nor on the X6+X7 registers. The X6+X7 register would not be stored.

## Address out of bounds, exit mode selected (EM)=XX1

(Refer to timing diagram of Exit Mode Stop)

If the  $M^{\circ} \geq FL$  comparison network detects an address out of bounds it will inhibit the sending of the intended address to the hopper and will also set the  $M^{\circ} \geq FL$  FF. Instead an address of all zeros and a 10 tag will be sent to

the hopper. A 10 tag in the hopper tag timing chain and an ACCEPT signal will set the RNI FF and a PROCEED signal is sent to the ISSUE CONTROL. As soon as the SKIP III FF is set the ERROR FF is also set. This in turn will start the DELAY COUNTER (P13) and also set the STOP FF. After 200 nsecs. the output of the counter is 1, but the INCH FF (P10 TP6) must be cleared in order that the Delay counter can clear the FF at 004-TP1. This FF will enable the setting of the PROGRAM ADDRESS FF and with a  $P + M^{\circ}$  signal will also set the ATTEMPT WRITE FF. Now the address RA and a 50 tag will be sent to the hopper (M) and the following data will be written into CM at location RA:

At the same time the ATTEMPT WRITE FF and FF at P10 TP1 was set. The latter will set the EXIT FF and this will set the GO BRANCH FF allowing a jump to P = 0 and hence RA. 300 ns after the address RA and a 50 tag was sent to the hopper the same address with a 10 tag will be sent to  $M^1$ . When the address is accepted by CM the contents of address RA (now 00 XX XXXXXXX 0000000000) will be transferred to the Instruction Stack and to the U registers (because of the RNI and Proceed signals). The translation of fm = 0X in the  $U^2$  translator and a SCBD Issue will set the STOP FF again.

## 3. Infinite or indefinite operands

The functional units using floating point arithmetic will always test the exponents for infinity (greater than 3777) and for indefinite results (see Appendix D). If any of the above conditions exists, a bit is sent to Chassis 5, anded together with the resp. FF's of the EXIT MODE register and in turn sets the ERROR FF if the particular EM FF was set. As soon as the ERROR FF is set the timing diagram of Exit Mode Stop (RNI out of bounds) can be used.

## SECTION II

Central Processor Instruction Issue Control

#### INSTRUCTION ISSUE CONTROL

#### INSTRUCTION STACK

## INTRODUCTION

The 6600 central processor, designed for very high speed computing, uses parallel functional units and overlapping memory references to reduce program running time. Another method of reducing time consumed during execution of a program eliminates unnecessary memory references. The following example of a portion of a typical scientific program illustrates the desirability of minimizing memory references:

#### EXAMPLE:

| ADDRESS | OPERATION                            |

|---------|--------------------------------------|

| 100     | Load operand A modified by B1        |

| 101     | Multiply by operand C                |

| 102     | Subtract operand D                   |

| 103     | Jump if sign of results are negative |

| 104     | Store results in X modified by B1    |

| 105     | Update B1                            |

| 106     | Jump to address 100                  |

The above loop example shows that memory references to obtain the same group of instructions are necessary for each pass through the loop. To avoid unnecessary memory waiting time, the central processor uses an instruction stack to hold short loops.

#### DESCRIPTION

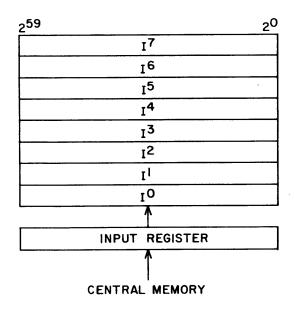

The central processor instruction stack is made up of eight 60-bit instruction registers, labeled IO, II, I2 . . . . . I7. An additional 60-bit register known as the Input Register serves as an input buffer between central memory and the instruction stack.

Fig. 2-1. Instruction Stack

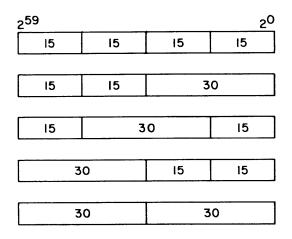

Instruction formats for any 60-bit instruction word in the stack may be 15-bit and 30-bit instructions in any of the combinations diagrammed in fig . 2-2.

Fig. 2-2. Possible Instruction Word Formats

The maximum capacity of the instruction stack is, then, thirty-two 15-bit instructions. A program loop that can be contained within the stack can be executed as many times as necessary without making any memory references

for instruction words. Note that an iterative loop cannot be 32 instructions and remain in the stack since: a.) the jump instruction comprising part of the loop is a 30-bit instruction, and b.) a jump cannot be executed from IO (the bottom register of the stack.)

#### **OPERATION**

The instruction stack is loaded one instruction word at a time as the instruction words are read from central memory to be executed. Each instruction is loaded into I0, sent to the translating networks, and then moved to I1. As each instruction word enters I0 and is moved upward in the stack, the complete stack contents must move upward to make room for the new instruction word. This upward movement of stack contents is called <u>inching</u>. As the stack contents are inched, the top instruction word (in I7) is discarded.

#### NOTE

Throughout the descriptive material which follows, references are made to specific FFs, logical networks, etc. To aid in understanding the text, refer to text diagrams and to 6600 Central Processor diagrams.

#### Inch

The process of inching the instructions in the stack is controlled by the inch counter. This counter is a 2 rank, 2 bit, binary counter initiated by the following conditions:

- a) next instruction word is in IO, and

- b) first instruction from IO is being issued to the translating networks (U registers).

Once the inch counter is started, it continues counting until the entire stack has been moved up. During the inching process, the instruction word in I7 is discarded.

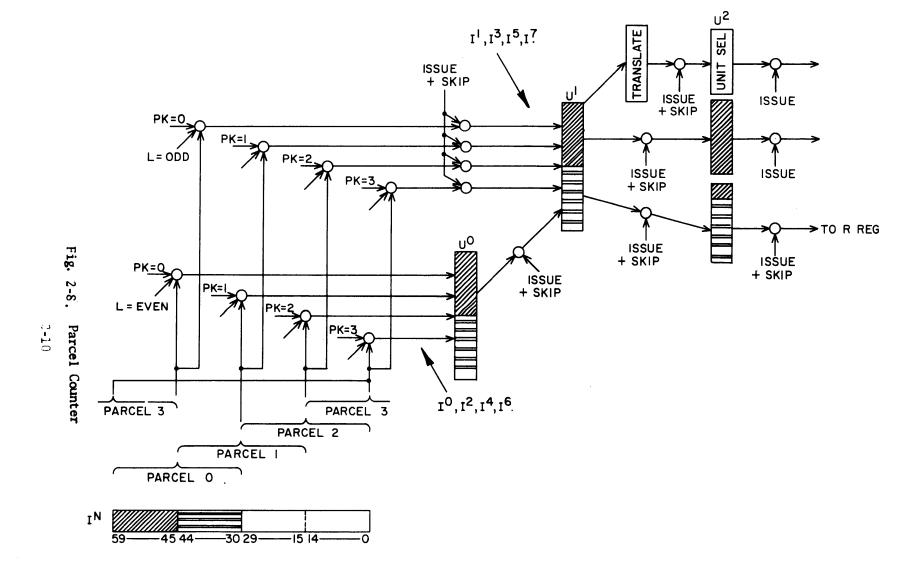

#### Parcelling

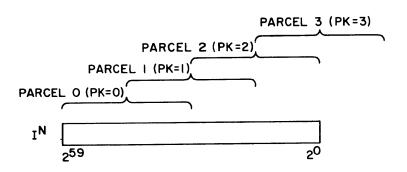

Since there are 15 and 30-bit instructions which can be combined in an instruction word in any order, the problem of extracting instructions from the ranks of the stack is encountered. The scheme used to extract instructions is called parcelling and is controlled by a 2 rank, 2 bit, binary counter called the parcel counter (PK). A 60-bit instruction word is partitioned into 4 parcels, designated 0, 1, 2, and 3. (Refer to fig. 2-3.) Each parcel is 30 bits in size to ensure

Fig. 2-3. Instruction Word Parcels

getting a complete instruction when extracting a parcel from the word. In many cases (e.g., a 15-bit instruction in a parcel), unusable information is extracted along with the meaningful. In these cases, unusable information is discarded as the instruction is placed in the U registers.

## Locator

In most cases, instructions that are sent to the U registers come from the lowest rank of the stack (IO). However, an instruction word inched up into the stack can still be issued to the U registers for execution. Thus, if inching occurs before an entire instruction word is issued (parcelled) to the U registers, the next instructions will come from some stack register other than IO. A Locator network (L) keeps track of the register in the stack holding unissued instructions (i.e., the register from which the next instruction will come).

#### Issue Control

The movement of instructions from the stack and through the U registers is controlled by a circuit called Issue Control. There are two basic signals associated with Issue Control:

- a) U1 issue (i.e.,  $U^1 \rightarrow U^2$ )

- b) scoreboard issue (i.e., U<sup>2</sup> → Scoreboard)

The Issue Control circuit controls the operations of the parcel and inch counters, the L network and instruction issue and movement from the instruction stack to

the scoreboard. The availability of functional units and operating registers, and information on instruction translations is monitored by Issue Control to assist this circuit in its functions.

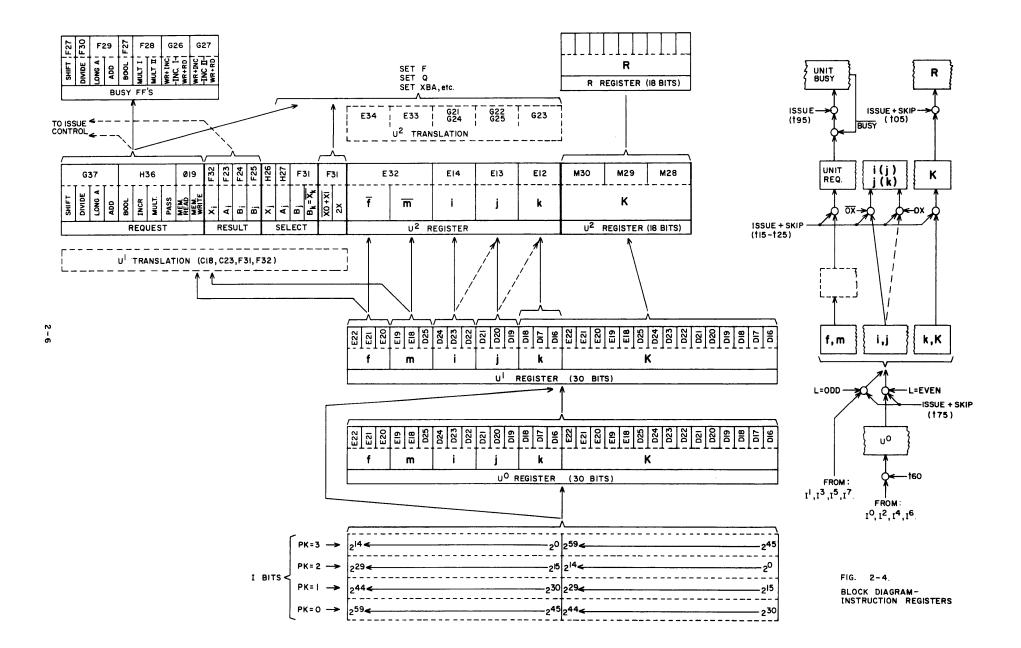

#### INSTRUCTION REGISTERS

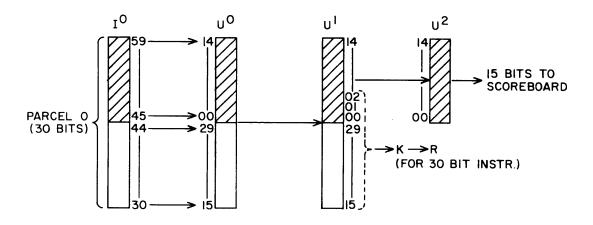

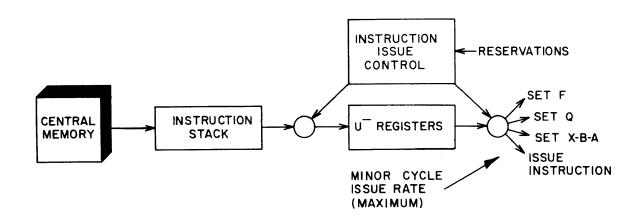

From the instruction stack, instructions flow in sequence to two registers to be translated. (Refer to fig. 2-4.)

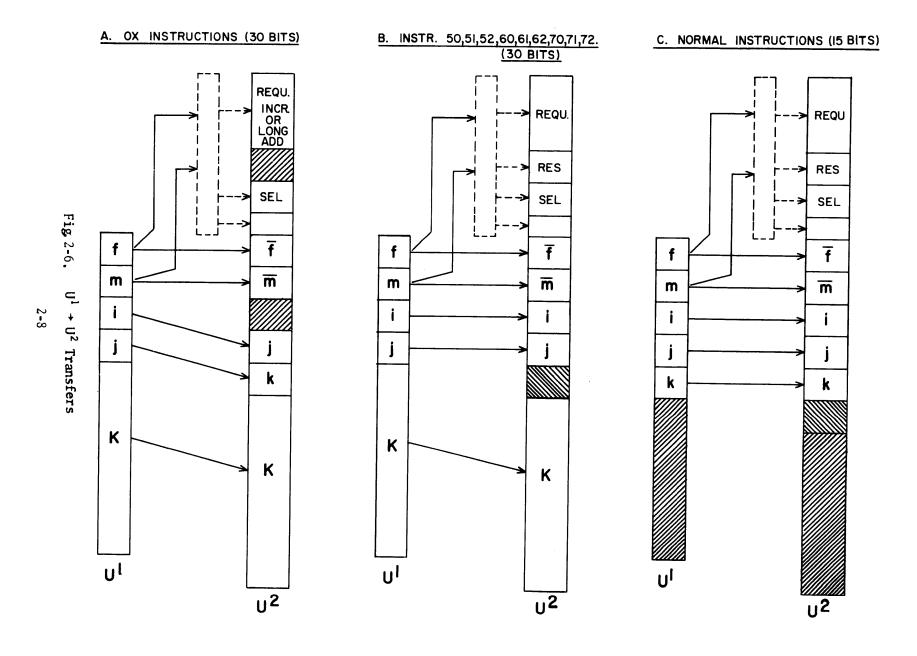

The first register, U1, consists of 30 FFs. Entry into U1 is controlled by the L counter and by the parcel counter. Instructions which come from even stack registers are transferred via an auxiliary register, U0. (Note that this does not affect the transfer time from the stack to U1; instructions from even and odd ranks of the stack arrive in U1 at the same time (t80).

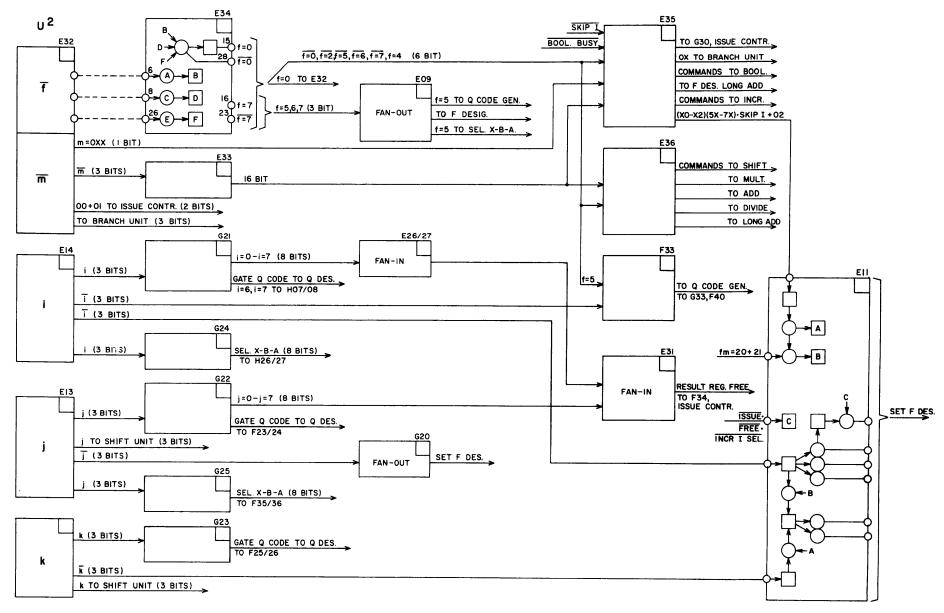

The fm portion is now translated to set the proper Select, Request and Result FFs. (Refer to fig. 2-5.)

At approximately the same time these FFs are set, the transfer to U2 is performed (t15-25). There are 3 different cases:

- a) 0X Instructions which contain the branch address in the K portion.

- b) 30-bit instructions which contain one of the two operands in the K portion.

- c) 15-bit instructions which do not use K.

(Refer to fig. 2-6.)

The second register, U2, consists of 53 FFs, which holds:

- a) Information about the Functional Unit request, and result and operand register selections gained from the translation in U1.

- b) The instruction designators (f, m, i, j, k).

- c) K portion.

This information is now translated and transmitted into the scoreboard (refer to figs. 2-4 and 2-7).

#### Parcel Counter

The parcel counter is used to extract 4 parcels of 30 bits each from  $I_N$ . The 4 parcels are needed in order to pick out any 30 bit or 15 bit instruction combination which could be contained in  $I_0$  and send these instructions to the Scoreboard. (Refer to fig. 2-8.)

|         | U <sub>l</sub> fm      | 0               | 1        | 2               | 3           | 4        | 5                              | 6               | 7               |     |

|---------|------------------------|-----------------|----------|-----------------|-------------|----------|--------------------------------|-----------------|-----------------|-----|

| W U 2   | FFS                    | 0   2 3 4 5 6 7 | 01234567 | 01234567        | 01234567    | 01234567 | 01234567                       | 01234567        | 0 1 2 3 4 5 6 7 |     |

| REQUEST | SHIFT                  |                 |          | *****           |             | ×        |                                |                 |                 |     |

|         | DIVIDE                 |                 |          |                 |             | x x x    |                                |                 |                 | 007 |

|         | LONG ADD               | ×               |          |                 | x x         |          |                                |                 |                 | G27 |

|         | ADD                    |                 | !        |                 | ×××××       |          |                                |                 |                 |     |

|         | BOOLEAN                |                 | ×××××××  |                 |             |          |                                |                 |                 |     |

|         | INCREMENT              | x x x x x       |          |                 |             |          | X <b>≪</b> IF i =0>X           | ** * * * * * *  | x               | :   |

| TINO    | MULTIPLY               |                 | •        |                 |             | x x x    |                                |                 |                 | Н36 |

|         | PASS                   |                 |          |                 |             | X        |                                |                 |                 |     |

| ).      | MEM. READ              |                 |          |                 |             |          | X <b>≪</b> -IF i=I5->X         |                 |                 |     |

| REQU.   | MEM. WRITE             |                 |          |                 |             |          | X <del>&lt;-</del> IF i=6+7->X |                 |                 | Ø19 |

|         | Xi                     |                 | ×××××××  | ×××××××         | *****       |          | X 11 120172X                   |                 | x               | F32 |

| -       | A <sub>i</sub>         |                 |          |                 |             |          | x x x x x x x x                |                 |                 | F23 |

| RESULT  |                        |                 |          |                 |             |          |                                |                 |                 |     |

| RE      | B <sub>i</sub>         |                 |          |                 |             |          |                                | *** * * * * * * |                 | F24 |

|         | Вј                     |                 |          | XXX             |             |          |                                |                 |                 | F25 |

|         | × <sub>j</sub>         | ××              | ×××××××  |                 | ×××××××     | ××× ×××× | ХХ                             | XX              | ××              | H26 |

| SELECT  | Aj                     |                 |          |                 |             |          | x xx                           | x xx            | x xx            | H27 |

|         | Вj                     | x xxxx          |          | * * * * * * * * | 3           | ×        | x xx                           | x xx            | x xx            |     |

|         | $B_k = \overline{X_k}$ | x xxxx          |          |                 |             |          | ****                           | ×××××××         | xxxxxxx         | F31 |

|         | XO + XI                | ****            | xxxxxx   | xxxxxx          | x x x x x x | xxxxx    | x x x x x x                    | ××××××          | xxxxxx          |     |

|         | 2 X                    |                 |          | ×××××××         |             |          |                                |                 |                 | F31 |

Fig. 2-5. Ul Translation

FIG. 2-7. U2 TRANSLATION

#### 15-Bit Instructions

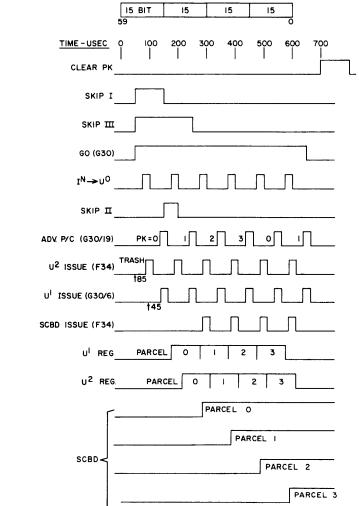

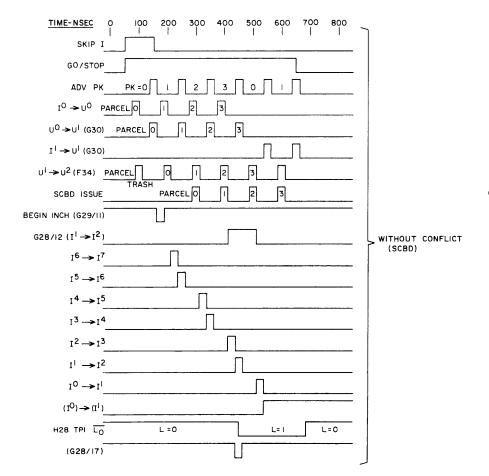

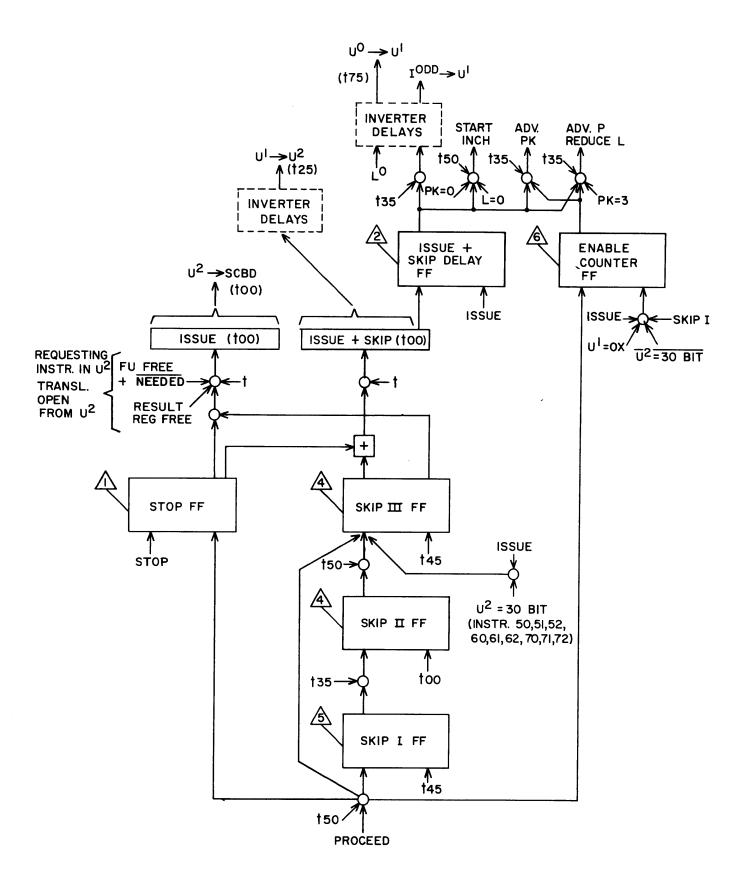

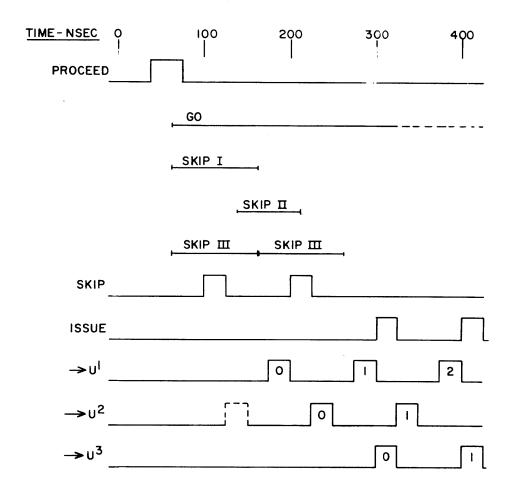

With the first issue pulse, Parcel 0 is sent to  $U_1$  and the parcel counter is advanced to 1. The second Issue Pulse transfers  $U_1$  to  $U_2$ ; parcel 1 is now in  $U_0$ . The ensuing Scoreboard Issue sends the contents of  $U_2$  to the Scoreboard. (Refer to fig. 2-10.)

Fig. 2-9. Parcel Path to Scoreboard

After all parcels have been issued to the Scoreboard, the parcel counter will be at count 1. This enables a "0" into F37/P3. Because FFs TP/5 and TP/6 have been set after the inching of I4 to I5, a "0" from F37/P25 goes through H25 and G36 and sets the Stop FF on G30, preventing any more Scoreboard issue pulses. Also, FF A on F37 will be set giving a "1" out of F37/P23, setting the FF TP6 on R32 at t50. One output of this FF is used to send a clear pulse to the Parcel Counter on G31, setting the counter back to 0.

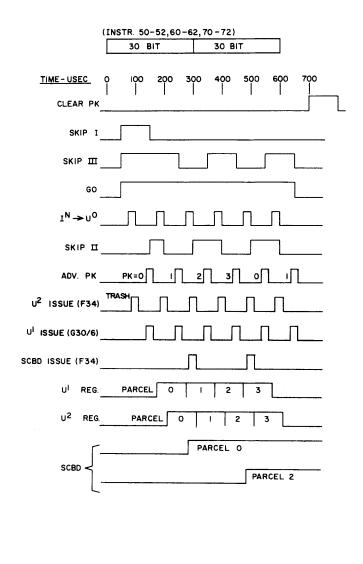

30-bit Instructions (50-52, 60-62, 70-72)

| $I^{N}$ | 30 BIT INSTRUCTION |   |

|---------|--------------------|---|

|         | 59                 | 0 |

FIG. 2-10. INSTRUCTION ISSUE TIMING.

The proceed signal coming into G30/P11 sets Skip I, III and the GO FF, resulting in a  $\rm U_2$  Issue signal from F34. This enables an Advance PK pulse from G20/P19, and sets the PK to 1. The same Issue pulse also enables parcel 0 into U1. The next Issue pulse (100 ns. later) transfers  $\rm U_1 \rightarrow \rm U_2$ , parcel 1 into  $\rm U_1$  and advances PK to 2. By this time, the Skip III FF will have been cleared, allowing a Scoreboard Issue pulse.

This pulse transfers the 30-bit parcel 0 from  $\rm U_2$  to the Scoreboard. It also allows the Skip II FF to reset. The 3rd Issue pulse sets PK to 3, transferring parcel 1 to  $\rm U_2$ , parcel 2 to  $\rm U_1$ . By now, the Skip II FF is reset, disabling any Scoreboard Issue pulses. The 4th Issue pulse transfers parcel 2 to  $\rm U_2$  thereby destroying parcel 1, which was still in  $\rm U_2$ . The only difference between a 30-bit and 15-bit instruction is that the Skip II FF is reset to prevent the second Scoreboard Issue pulse and therefore does not send parcel 1 to the Scoreboard.

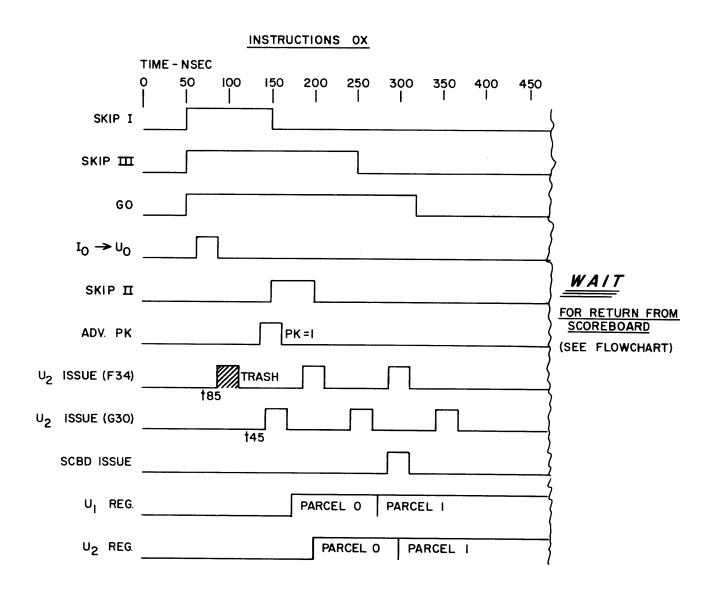

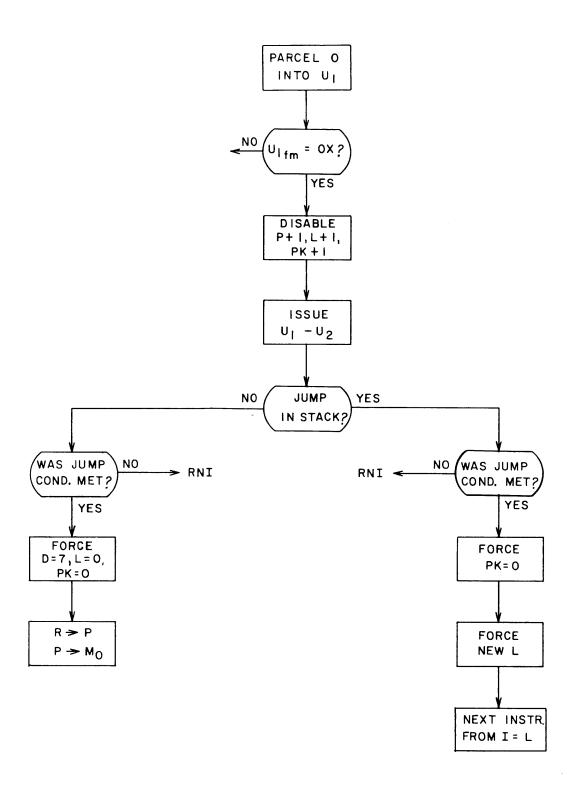

#### 30-bit Instructions (0X)

The first Issue pulse will again transfer  $\rm U_0$  to  $\rm U_1$  and advance PK to 1. The second Issue will be fed into G30/P23 together with the 0X translation from  $\rm U_1$ . This clears FF/E, disabling a second Advance PK pulse and also disabling the P and L incrementers. This Issue also transfers  $\rm U_1$  to  $\rm U_2$  and parcel 1 into  $\rm U_1$ . Together with the third Issue, a Scoreboard Issue transfers  $\rm U_2$  to the Scoreboard. This Scoreboard pulse, together with the 0X translation from  $\rm U_2$ , is fed into H05/P9 setting the Stop FF. This disables any more Scoreboard Issue pulses. Instruction issue control now waits for an indication from the Scoreboard as to whether the jump condition was met or not. (Refer to figs. 2-11 and 2-12.)

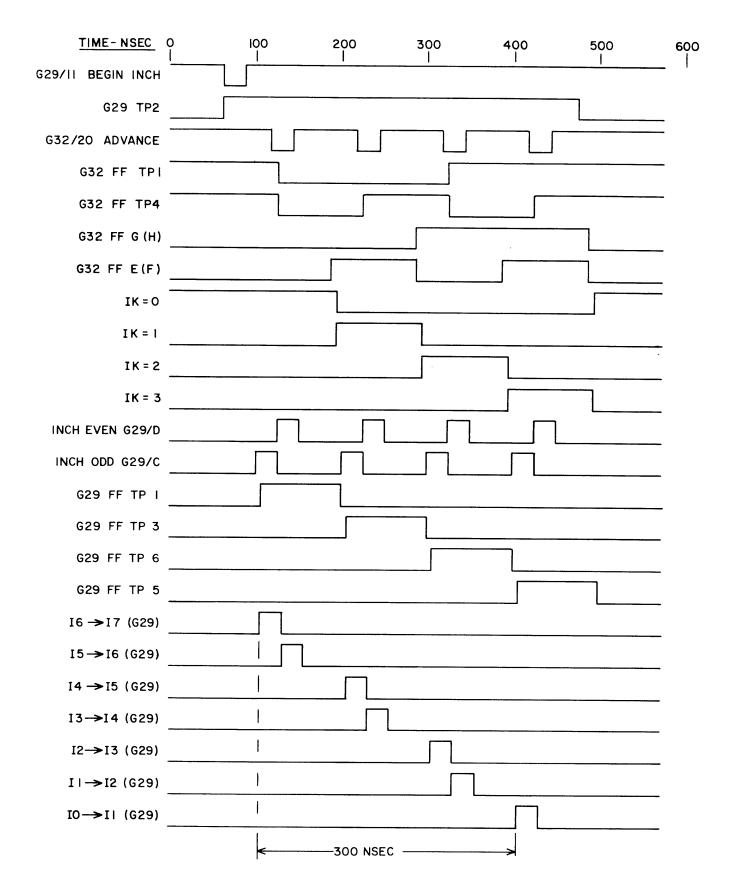

#### INCH COUNTER

The inch counter is used to shift 60-bit instruction words upward in the instruction stack ( $I_0$ - $I_7$ ). When the parcel counter = 0, L counter = 0 and t = 60, and an Issue or Skip signal occurs, a "0" into G29/11 sets the Inch FF. This FF sends an advance pulse to the inch counter. Before the counter is advanced to 1, gates C and D on G29 are enabled setting FF/TP1. One output of this FF will set the Program Address FF on P37, starting a new RNI. Another output first clears

Fig. 2-11. OX Instruction Issue Timing

Fig. 2-12. 03-07 Instructions

the  $I_7$  register and then enables the transfer of  $I_6 \rightarrow I_7$ . Another pulse from this FF, at a slightly later time, clears the  $I_6$  register and transfers  $I_5 \rightarrow I_6$ . (Refer to fig. 2-13.)

By now, the inch counter is set to 1 enabling the transfer of  $I_4 - I_5$  and  $I_3 - I_4$  etc. After the last transfer has been enabled ( $I_0 - I_1$ ), the counter is set at 3. The 4th advance pulse now sets the counter back to 0 and the Inch FF is cleared.

The counter is again ready to begin a new transfer sequence. The instruction word now in  $\mathbf{I}_7$  is discarded when the next  $\mathbf{I}_6$ — $\mathbf{I}_7$  transfer occurs.

#### L COUNTER

To avoid confusion in the L counter discussion which follows, the following statements should be noted:

- 1) The L counter FFs on H28/TP1, 2, 5 contain the complement of the L count. (e.g., all set: L count = 0; all clear: L count = 7) Note the distinction between L counter and L count.

- 2) Reduce L means the L count goes from  $6 \Rightarrow 5$  or  $3 \Rightarrow 2$ .

The major function of the L counter is to guide the parcel extraction from the proper register (e.g., I0, I1 etc.) in the instruction stack; an L count of 0 corresponds to  $I_0$ , L = 1 to  $I_1$  etc. Assume L = 0 and PK = 0; this means that the upper 30 bits of  $I_0$  would be gated to  $U_0$ . When PK advances to 1, the next parcel will be transferred etc. By now, the Inch counter also started the inching of  $I_6 \xrightarrow{\bullet} I_7$ ,  $I_5 \xrightarrow{\bullet} I_6$  etc. During this time the L count was equal to 0.

When the PK reaches 3, and no 0X (Branch) instruction is in the  $U^1$  translator, a "0" into G28/P17 will enable the H gates and disable the G gates.

The function of these H and G gates are to switch the L counter FFs from one loop to another. One loop called the L-T loop goes from H28 through H29, G36, G28 and back to H28. The second loop, called the Reduce L loop, goes from H28 through H30, G28 and back to H28. In a no branch instruction the T FFs on H28 are all set which means that in the L-T loop we are actually subtracting 0 from L. This permits holding L to its same value through the L-T loop as long as the G gates are made. As soon as we switch to the Reduce L loop we will also

Fig. 2-13. Inch Counter

get a "1" into G28/P12 (from G29/P18) disabling the H and G gates. This prevents FF  $L_0$  from holding its value and it is cleared at the next t50.

This means that we have advanced the L count to 1. However, as soon as the GO FF on G30 is cleared, a "0" out of A on G36 will set all L FFs on H28 forming an L count of 0. Parcelling of the next instruction word from  $\mathbf{I}_0$  is now ready to begin.

In case of a conflict (instruction not accepted by the Scoreboard), all Issue pulses are stopped preventing Advance P and Advance PK. However, the Inching process will continue until completion. After the inching of  $I_1$ — $I_2$  is completed, the L counter is again advanced setting the count to 1; the count remains set at 1 since the GO FF remains set. This will allow a new instruction to be entered into  $I_0$  while we are waiting for our instruction to be accepted. Once the instruction is accepted by the Scoreboard, the following Issue will advance the Parcel counter again but the remaining parcels are taken from I1. We now have to wait until all instructions out of  $I_1$  are accepted before we can start a new Inching process and therefore a new RNI.

For a branch instruction (if conditions are met and jump is in stack), the L-T loop supplies the new L count and sets the L FFs to the new value. After all the instructions in this new instruction stack register (defined by the L count) have been issued, a count enable K on H30, together with the H gate on G28 allows the L count to be reduced by one, and so on until L is again equal to 0.

At the beginning of the branch, the inching also transferred  $I_0 \rightarrow I_1$  but now we cannot start a new inching process because we need L = 0. There is also only one RNI immediately after the inching has started but as we cannot start a new inching we will not get a new RNI.

#### Remember:

To start Inching: (PK = 0)(L = 0) (Issue pulse)

To start RNI: Inch I<sub>6</sub> - I<sub>7</sub>

### ISSUE CONTROL

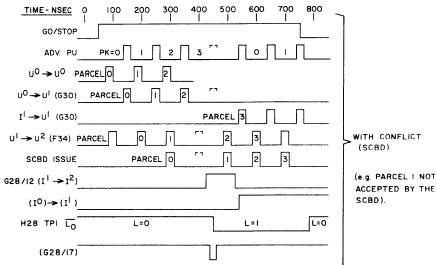

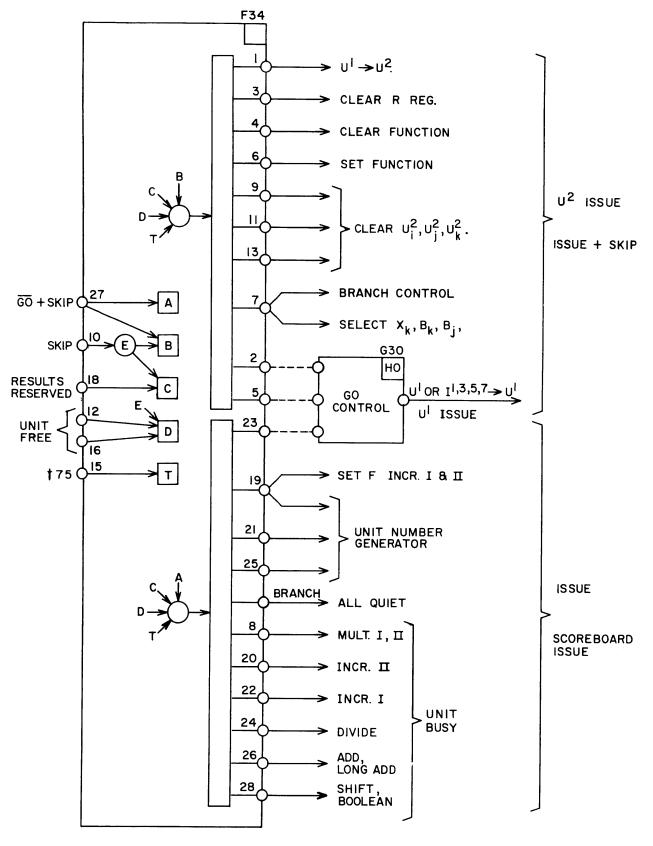

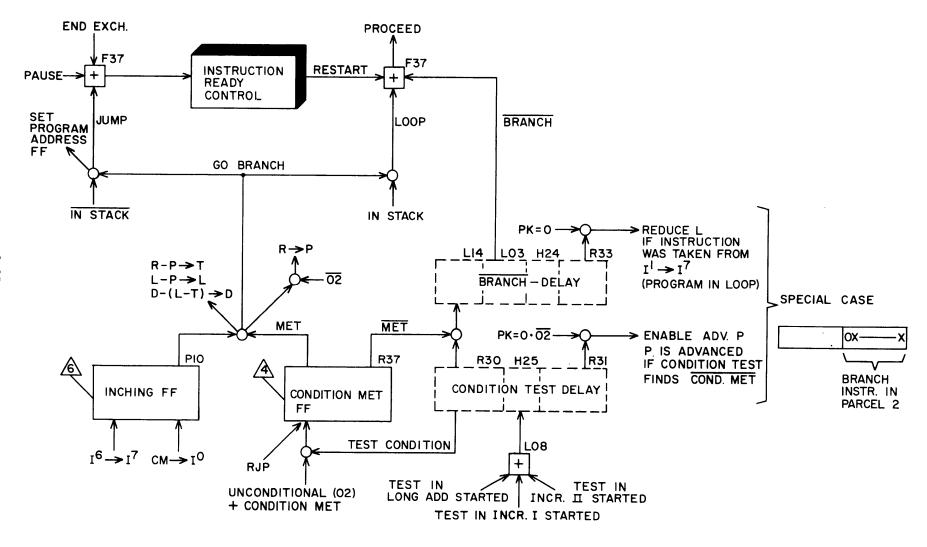

The Issue Control block diagram in fig. 2-15 depicts the functions performed by the Issue pulses from F34 and G30. As not all of these pulses are produced by the same conditions, we shall give them the following names:

- 1) Pulses from F34/P9, 11, 13 are called:  $\frac{U^2 \text{ Issues}}{U^1 \text{ Issues}}$  also called:  $\frac{\text{Issue+Skip}}{U^1 \text{ Issues}}$

- 3) Pulses from F34/P8, 14, 19/26, 28 are called: <u>Scoreboard Issues</u> also called: <u>Issues</u>

These pulses are produced if the following conditions exist:

U<sup>1</sup> and U<sup>2</sup> Issues = (Unit Request . Unit Busy . Dest. Reg. free . GO) + Skip Scoreboard Issues = (Unit Request . Unit Busy . Dest. Reg. free . GO . Skip)

# STOP INSTRUCTION ISSUE

The Issue signal, which moves instructions and their translations through U1 and U2 into the scoreboard, and the Skip signal, which moves these instructions up to U2, are controlled by the G0/Stop FF. Conditions necessary for these signals are as follows:

ISSUE: (Go) (Skip) (Unit Request) (Unit Free) (Destination Register Free) (t90)

SKIP: During the 200 ns. after Proceed and during 100 ns. after a 30-bit instruction where K is an operand.

The following section describes the conditions that place the Go/Stop FF in the Stop state. (Refer to fig. 2-16.)

#### 1) PAUSE

When the first parcel is extracted from the 60-bit instruction word in  $\mathbf{I}_0$ , the inch process begins. The beginning of the inch process, in turn, requests the next instruction word from central memory. When all parcels of the word in  $\mathbf{I}_0$  (meanwhile, inching may have moved the word into  $\mathbf{I}_1$ ) have been transferred to the scoreboard, the central processor waits for the next instruction word. This wait period is called <u>Pause</u>.

To get the Pause signal, the inch process sets the Request Pause I FF. When parcel 2 is taken from the stack, the Request Pause II FF is set. The next time PK = 1, parcel 3 is placed in the scoreboard and issue is stopped. (Refer to figure 16.) The Issue and Skip signals are restarted by instruction ready control.

Fig. 2-15. Issue Control

Fig. 2-16. Stop Instruction Issue

### 2) EXCHANGE JUMP STOP

During the Exchange Jump process, the Go/Stop FF is set to the stop state. The Exchange Jump signal, issued by a peripheral processor, forces the stop when PK = 1. (A PK = 1 count indicates parcel 3 was the last parcel issued to the scoreboard. Thus, an entire 60-bit instruction word is issued before permitting the stop on an Exchange Jump.)

### 3) ERROR STOP

The contents of bits 2 0 - 2 2 in the Exit mode register specify which errors can stop instruction issue. The Program FF, set at the beginning of a new program by the Exchange Jump, insures that only the first error sets the Error Stop FF. The error signal is also gated by a Skip signal. The Skip signal gate permits finishing a loop in the stack (for branch cases) before stopping. (Only the next Branch instruction performs a Skip.)

The Error Stop FF is cleared by a master clear or by the execution of the Exit mode process.

### 4) OX - INSTRUCTION STOP

When a Branch instruction is issued into the scoreboard, further instruction issue halts to allow time for branch condition tests; i.e., branch/no branch, jump/loop, etc.

### 5) MASTER CLEAR

A master clear stops all instruction issues.

# PROCEED INSTRUCTION ISSUES

The requirements for proceeding with instruction issues are outlined below:

# 1) INITIAL START OR RESTART AFTER PAUSE:

When the central processor starts (after an Exchange Jump), or proceeds (after referencing memory for the next instruction word; i.e., pause), two transfer pulses are required to bring the first parcel (parcel 0) from IO into U2. No information is placed in the scoreboard during this period; these transfer pulses that move the parcel to U2, but not to the scoreboard are called SKIPS.

# 2) PROCEED AFTER A BRANCH INSTRUCTION:

Three possible "proceed" cases exist after a Branch instruction:

- a) BRANCH: When the branch condition is not met, the next instruction may be in the same 60-bit instruction word as the Branch instruction.

- b) LOOP: The branch condition is met, and the next instruction is parcel 0 of an instruction word in the stack.

- c) JUMP: The branch condition is met; the next instruction must be obtained by a memory reference.

Case (a), if the Branch instruction was in parcel 0 or 1, requires one parcel be skipped. In cases (b) and (c), where a new instruction word is requested, it is necessary to perform two skips to transfer the new instruction into U2.

For simplicity, the logic treats all "proceeds" after a stop condition the same (i.e., as requiring two skips). Case (a) above, the only case requiring only one skip, is reverted to the normal case by disabling one advance pulse of the parcel counter. Thus after every stop condition, two skips are performed before information can be issued to the scoreboard.

3) In cases (1) and (2c), which require a new instruction word from memory, a "proceed" signal occurs only if the new instruction word is available in IO.

### **OPERATION**

A Proceed signal may originate from one of three different sources (cases): (Refer to fig. 2-17.)

- 1) Restart (Instruction Ready Control)

- 2) Loop

- 3) Branch

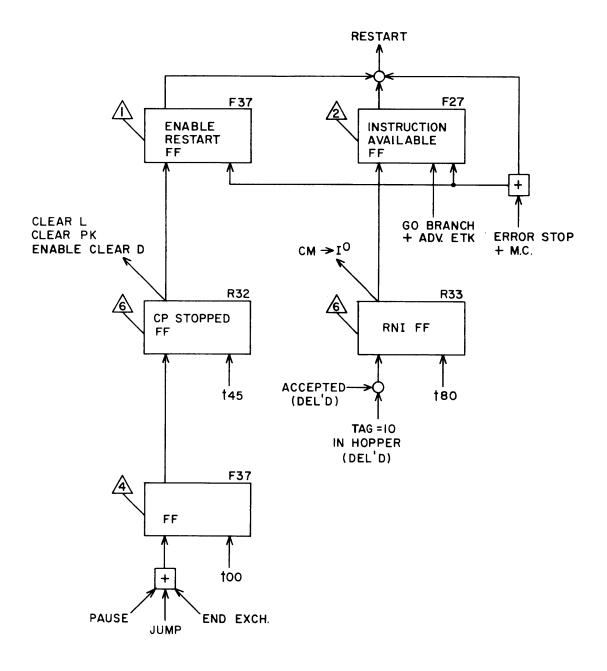

### RESTART:

The Restart signal occurs when a new instruction word is available in I0. This occurs in the following cases:

Fig., 2-17. Proceed Instruction Issue

- a) End Exchange (start after an Exchange Jump)

- b) Pause (stop between instruction words)

- c) Jump (Branch is not in the stack)

The corresponding signal sets the CP Stopped FF, clears L, PK, and (in the jump case) the D count, and sets the Enable Restart FF. (Refer to fig. 2-18.)

When the 10-tag (RNI tag) is detected in the hopper and the address is accepted by central memory, the new instruction word is read from memory. The new instruction word is guided to IO, and the Instruction Available FF is set, permitting the Restart. Note that it is possible for an instruction to be available before the Enable Restart FF is set. For example, a Functional Unit conflict before Pause, or (in the jump case) when a requested instruction word must be in the stack before the Go Branch signal occurs.

### LOOP:

If the Branch test indicates that the next instruction is located in the stack, the Proceed signal is issued. (In case the inch process is occurring, the Inching FF delays the Go Branch signal until movement in the stack is completed.)

## NOT BRANCH;

In a conditional Branch instruction, and the branch condition is not met, the Proceed signal can be issued. (As previously stated, the parcel counter skips one advancement in Branch instructions; this permits two skips following a Proceed signal.)

A special case exists for a branch condition. During a Branch instruction, the P and L counters are disabled. This disabling occurs from the moment a Branch instruction is detected in U1 until the Proceed signal is issued. (Meanwhile, the parcel counter is advanced by one.) If a Branch instruction comes from parcel 2 of an instruction word and enters U2, the parcel count is now 3. Normally on PK = 3, P is advanced and L is reduced. However, in Branch instructions this does not occur. Action proceeds with a PK = 0; PK is counted to 2 during the two Skips, then a stop occurs to wait for the new instruction word. Since this action would not provide opportunity to correct the counts in P and L, special circuits exist to accomplish this before the Proceed signal is given.

Fig. 2-18. Instruction Ready Control

Fig. 2-19. Go Control/Issue/Skip

Fig. 2-19a

SECTION III

Central Processor Scoreboard

#### CENTRAL PROCESSOR

#### SCOREBO ARD

#### Introduction

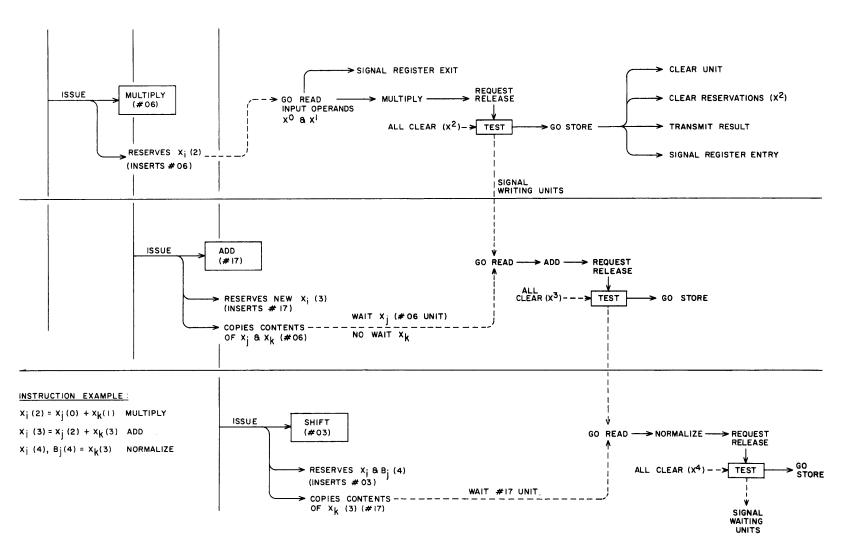

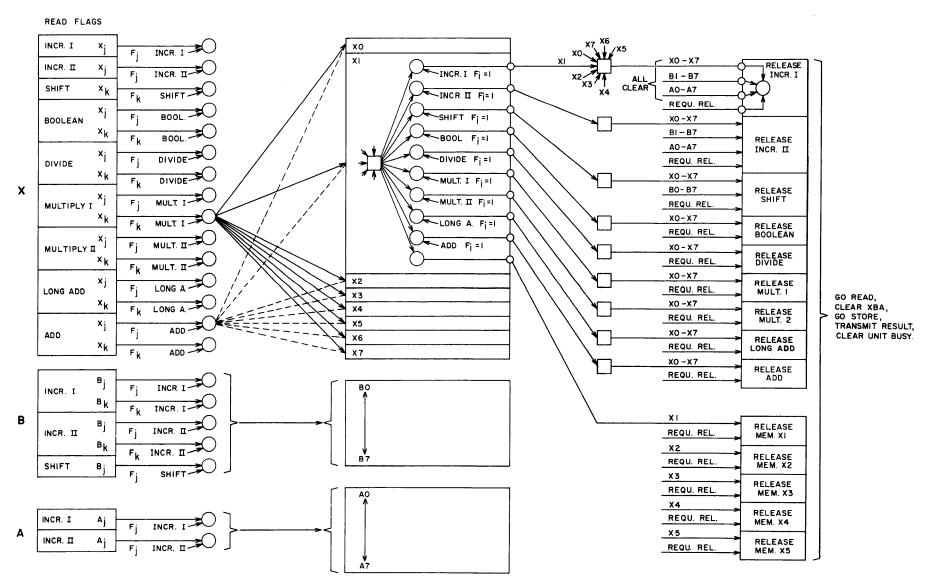

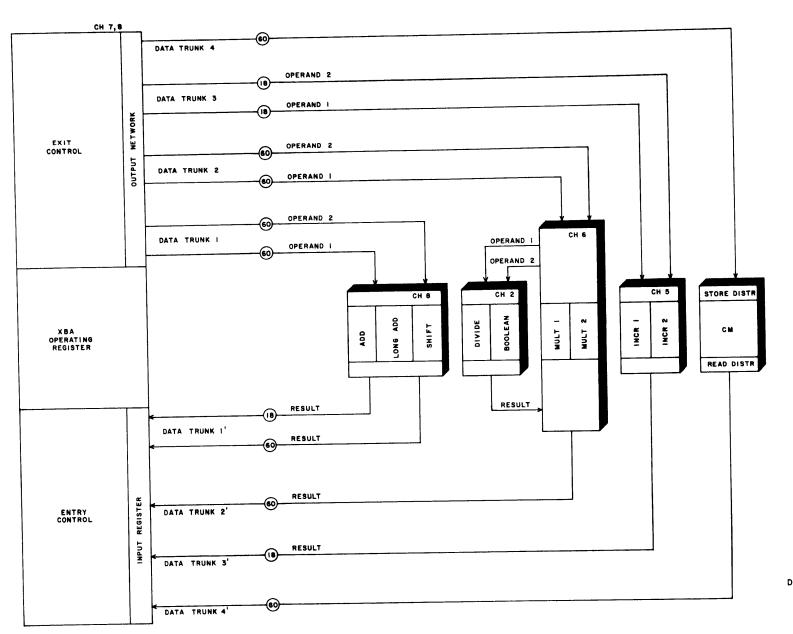

The scoreboard directs the exchange of operands and results among the 24 operating registers, central memory, and the 10 functional units. Instructions are issued to the units for execution in the order prescribed by the original program sequence. The scoreboard permits instructions to be executed out of order while retaining the original program sequence.

Scoreboard reservations are made in serial order for one unit at a time and at a maximum rate of one every minor cycle; this corresponds to the maximum instruction issue rate. However, processing of requests to read operands or store results from all units goes on in parallel and coincidently with placing of reservations. Hence, program instructions are executed in a series-parallel arrangement resulting in very high-speed running of a program.

The scoreboard uses a reservation system on the registers and units to direct the instruction issue and execution sequence. The scheme allows all units to be in operation at the same time but prevents one unit from executing more than one instruction at one time or more than one unit from storing in a common register at the same time. Lockouts for the functional units and operating registers and a series of designators which identify registers and units aid the control system.

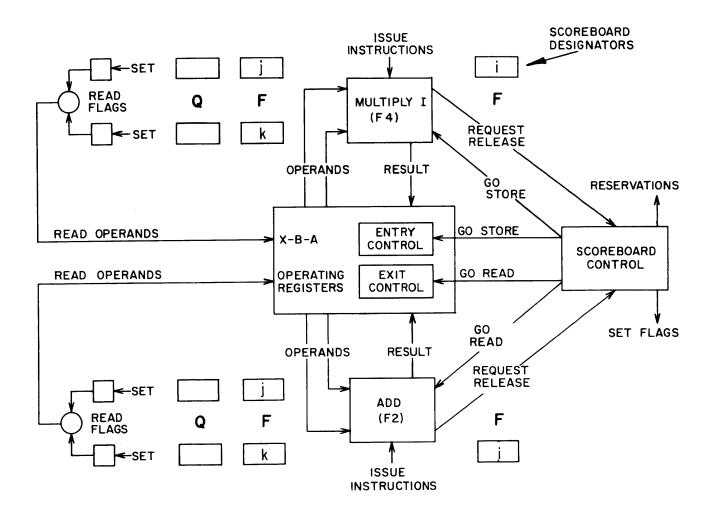

An instruction is issued to a functional unit only if the unit and the required result register are free; i.e., they are not reserved for another instruction or another result. With both elements free, the instruction is issued and reservations placed in the scoreboard for the necessary operating registers and unit (fig. 3-1).

FIG. 3-1. SCOREBOARD CONTROL

Scoreboard control directs the unit in obtaining its operands and storing its result; computation in the unit proceeds independently. The unit requests permission from the scoreboard to release its result to its result register. The scoreboard determines that the path to the register is clear and signals the requesting unit to release its result. The releasing unit's reservations are then cleared and units waiting for the result are signalled to read the result for their computation.

Special scoreboard action handles the reservation and control scheme for address modification in the increment units. A change to an  $A^1-A^7$  address register changes the corresponding  $X^1-X^7$  operand register so that an operand is read into  $X^1-X^5$  or  $X^6-X^7$  is stored. Hence, for 50-57 instructions, the A result register and associated X register are reserved together to prevent the X register from being pre-empted by a subsequent instruction.

The increment unit computes the address and sends it to the stunt box for issue to CM. Coincidently, the result is released to the A register through normal scoreboard processing. Also, the releasing increment unit's reservations are cleared to free the unit for further computation. However, the X register reservation is held until after the address is accepted by CM (thus spanning any delay time in the stunt box because of bank conflict) and the data word is delivered to the X register (for  $X^1-X^5$  cases) or delivered to the CM store distributor (for  $X^6-X^7$  cases). Additional information is given later for the increment and branch unit action in the scoreboard.

The functional units exchange data with the 24 operating registers over a number of data trunks. A priority system regulates trunk usage, and the scoreboard selects the proper data trunk and honors the priority system in directing the data exchange.

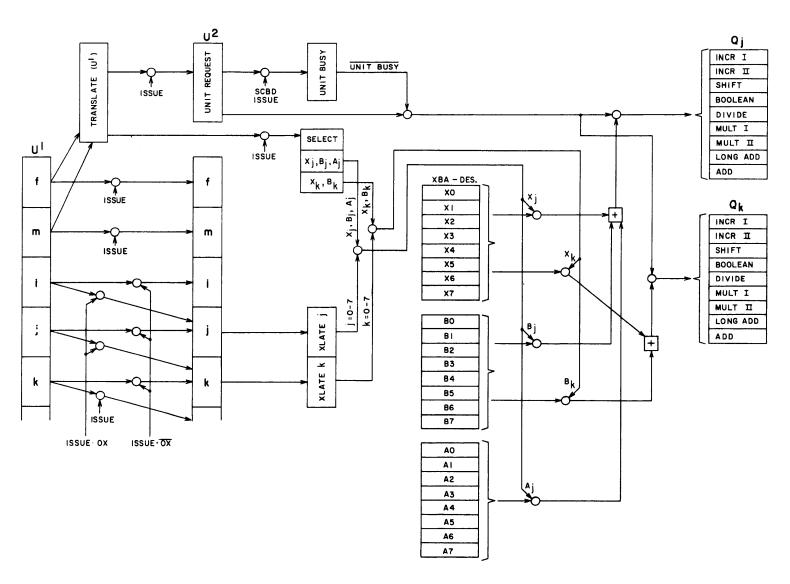

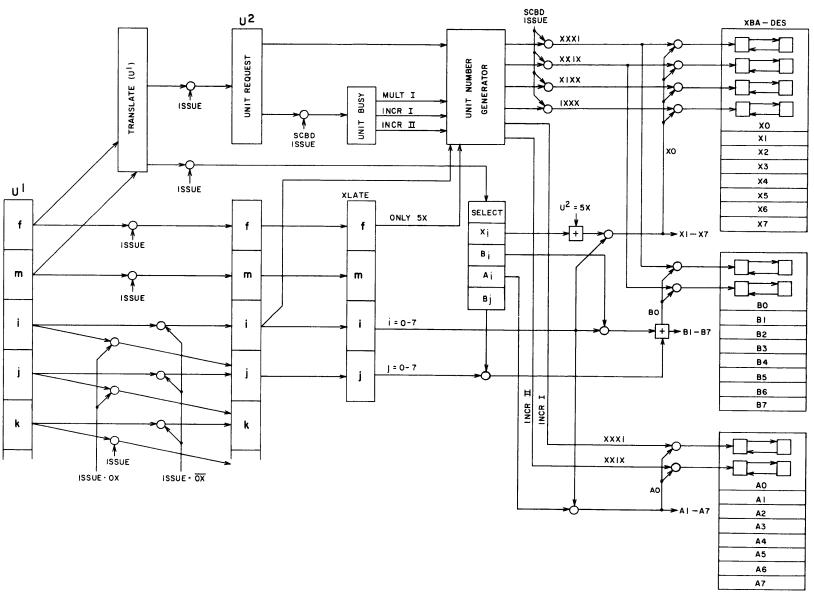

The designators in the reservation system are listed below and shown in fig. 3-2.

| X | Operand register   | j | First entry operand register designator  |

|---|--------------------|---|------------------------------------------|

| В | Increment register | k | Second entry operand register designator |

| A | Address register   | i | Result register designator               |

| F | Functional         | Q | Entry operand reservation designator     |

Note that reservation designators are part of the scoreboard circuits but are shown in fig. 3-2 as related to the entry operand and result registers of a given unit.

Scoreboard operation is described first from the view of placing reservations, and second, the control system which interprets reservations and directs a unit to read its entry operands and store its result.

Placing Reservations

Reservations are placed in three sequential steps following issue to the scoreboard.

- 1. Assign operating registers to functional unit (set F).

- 2. Determine previous reservations on entry operand regs. (set Q).

- 3. Update reservation list to reflect the result register of the latest reserving unit (set XBA).

#### Set Unit Busy FF

The fm portion of the instruction is translated at the output of  $\mathbb{U}^1$  selecting one of the following Unit Request FFs:

a) Shift, Divide, Add, Long Add, Boolean (G37, H36)

The outputs of these FFs are sent to their respective Unit Busy FFs, (F27, 29, 30). The input gates of these cards, however, can only be made if the Unit Busy FF is in the clear state. If this gate is made we will enable the D gate on F34 of the Issue Control.

FIG. 3-2. RESERVATION DESIGNATORS

# b) Multiply, Increment (H36)

As there are two Multiply and Increment units, these unit request FFs can set one of two Busy FFs under the same conditions described in paragraph a). To set Mult. II or Incr. II Busy FF, their respective unit I Busy FFs must be set.

For 5X instructions when i=0, only FF CD (Write or Increment) will be set on G26 and G27. FF AB (Read or Write) remains cleared, because no memory reference can be made by changing AO.

# c) Memory Read, Memory Write (#19)

A 5X translation and i=6+7 will set the Memory Write FF on Ø19. A 5X translation and i=1-5 will set the Memory Read FF. These FFs in turn can set the Busy FFs for increment I or II on G26 if all conditions are satisfied.

# d) Pass (H36)

This FF on H36/TP6 will send its output directly to the Issue Control to enable gate D on F34.

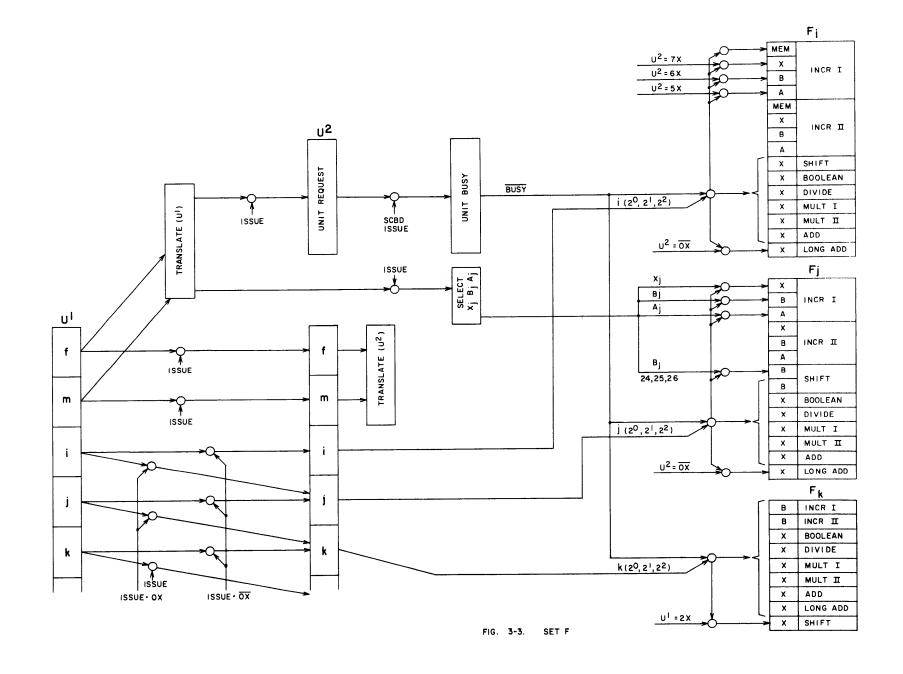

### SET F

The set F step sets the result and entry operand register designators i, j, k for the selected unit. This assigns operating registers to the selected unit. The i designator identifies a result register for most instructions and j and k the entry operands. Each 3 bit designator specifies one of the eight registers in an X, B or A register group. For example, the j designator of the add unit may be set to  $X^1$ , which reserves operand register X1 as one of the entry operand registers.

Looking at Table 3-1 we can see that for the Shift and Increment Units, the F designators can specify X, B or A registers. For these units therefore, we must decide which register F designator must be set for a particular instruction.

| UNIT         | Fj |          |   |   | Fk           |   | Fi                                               |                                                  |  |

|--------------|----|----------|---|---|--------------|---|--------------------------------------------------|--------------------------------------------------|--|

|              | X  | В        | Α | X | В            | × | В                                                | Α                                                |  |

| ADD          | Х  |          |   | × |              | × | 1                                                | 1                                                |  |

| MULTIPLY I   | х  |          |   | X |              | × |                                                  | <u> </u>                                         |  |

| MULTIPLY II  | ×  | <b>†</b> |   | × | 1            | × | <del>                                     </del> | <u> </u>                                         |  |

| DIVIDE       | x  |          |   | × | 1            | × | <b>†</b>                                         |                                                  |  |

| LONG ADD     | ×  |          |   | × |              | × | <u> </u>                                         | $\vdash$                                         |  |

| BOOLEAN      | ×  |          |   | × | <del> </del> | × |                                                  | <del>                                     </del> |  |

| SHIFT        |    | х        |   | x |              | × | ×                                                | <del> </del>                                     |  |

| INCREMENT I  | ×  | ×        | x | † | ×            | × | ×                                                | ×                                                |  |

| INCREMENT II | ×  | х        | х | 1 | х            | × | ×                                                | ×                                                |  |

TABLE 3-1.

This selection is done by the  $U^2$  translation and the select Xj, Bj, Aj FFs which will enable the required F designator or designators.

## SET Q

The set Q step determines if the entry operand registers are reserved for results of other units already in operation, and which units have them reserved. The fact that the current instruction has been issued to a unit indicates that its own result register is not reserved. The register reservation information is held in 24 separate X-B-A designators. Each unit is assigned a number for reservation purposes, table 3-2, and the number of the last reserving unit is transferred from the proper X-B-A designator to the Q designator of each entry operand of the waiting unit.

As an example, if register X1 was already reserved for the result of multiply 1 unit and the Add unit wants to use X1 as its j entry operand, then the  $Q_j$  designator of the add unit will be set to the unit code (06) identifying the multiply 1 unit. (See table 3-2.) If the required register

is not reserved, the respective Q designator will be set to zero and its Read flag will be set to indicate that the register is free and ready to be read. However, a unit will read its operands only when both are flagged.

# Q designators are set in the following manner:

After setting the Unit Select FF, the entry operand register numbers for the requesting unit are identified from translation of the i, j, k portions of  $U^2$ . Select FFs, corresponding to that instructions entry operands  $(X_j, X_k, B_j, \text{etc.})$ , are set to identify the XBA register groups. In the case of an add unit selection,  $X_j$  and  $X_k$  FFs (H26 and F31) are set and their outputs are combined with the k and j translation from  $U^2$  (G22, G23) to identify and read the respective X designators (H01-08). This information is sent to the Q designators (I17, I18) of the add unit under control of the add unit select FF.

Q Designators for Functional Units

| Q (octal) | Functional Unit                         |

|-----------|-----------------------------------------|

| 00        | Branch                                  |

| 01        | Increment 1                             |

| 02        | Increment 2                             |

| 03        | Shift                                   |

| 04        | Boolean                                 |

| 05        | Divide                                  |

| 06        | Multiply 1                              |

| 07        | Multiply 2                              |

| 10        | marciply 2                              |

| 111       | Read Memory Channel 1 (X <sub>1</sub> ) |

| 12        | Pood Memory Channel 2 (Va)              |

| 13        | Read Memory Channel 2 (X2)              |

|           | Read Memory Channel 3 (X <sub>3</sub> ) |

| 14        | Read Memory Channel 4 (X <sub>4</sub> ) |

| 15        | Read Memory Channel 5 (X <sub>5</sub> ) |

| 16        | Long Add                                |

| 17        | Add                                     |

| L,        |                                         |

Table 3-2

FIG. 3-4. SET Q

## SET X-B-A

The set XBA step updates the XBA reservation list to include the result register of the latest or current reserving unit. In the previous example, if the add unit result register is XO, the identifying code for the add unit (octal 17) is entered in the XO designator as the latest reservation. Should a subsequent instruction require XO as a result register, it is not issued until the add unit releases XO. Instructions which require  $X_O$  as an entry operand however, are issued and receive the add unit code in their respective Q designator.

Three steps are necessary to place this reservation:

- 1. The unit is identified

- 2. The register number is identified

- 3. The register group (XBA) is identified

The unit is identified by translating the fm portion of  $U^1$ ; this will set the unit select FF. A second translation of the fm portion of  $U^1$  identifies one of four possible result register groups: Ai, Bi, Xi, or Bj. This information is stored in separate Result FFs.

The register number is derived from translations of the j and k portions of U<sup>2</sup>. The register number and group (XBA) are combined to gate the unit code (Table 3-2) into the XBA designator. Each unit selection is converted to a 4 bit binary code by driving four inverters in a combination equalling the binary code. Thus, the add selection drives four inverters which yield binary 1111 or octal 17; a shift selection, for example, drives only bits 0 and 1 to yield binary 0011 or octal 03. (See G33 and F40.) The shift and increment units are the only ones that use the A and B registers for results. The codes for these units use only bit positions 0 and 1. Thus, the B and A designators need be only two bits, whereas the X designators are four.

FIG. 3-5. SET X-B-A

5X instructions place their result in an A register and thereby cause a read or write operation in the corresponding X register (except for AO and XO). In this case, both registers are reserved.

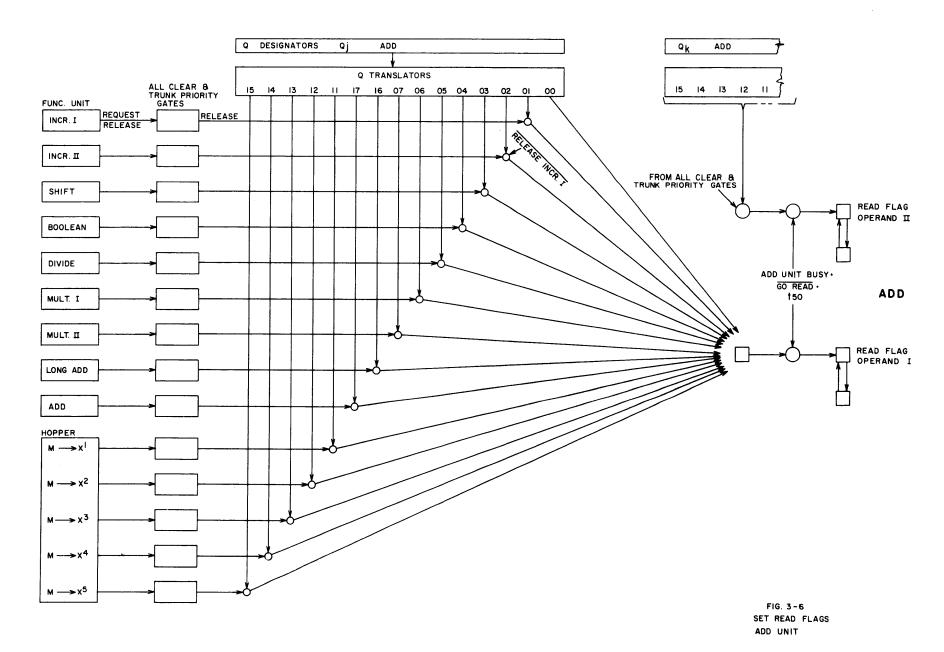

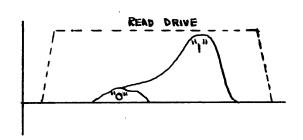

### SET READ FLAGS

When the Q designators have been set, the Q translators will provide outputs for Q=0 through 17 (Q=10 not used). These octal codes define the unit that has reserved the particular register. (See Table 3-2.) For example, let Q=01. The increment 1 unit has reserved the particular register referred to by the Q designator. The Q=01 output from the Q translator will be anded with the output of the Increment 1 Release FF setting the operand read flag. In the case of Q=0 the read flag is set directly, since that particular register had not been reserved by another unit. Operands are read only when both read flags are set.

## Reservation Control

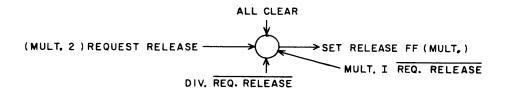

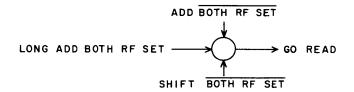

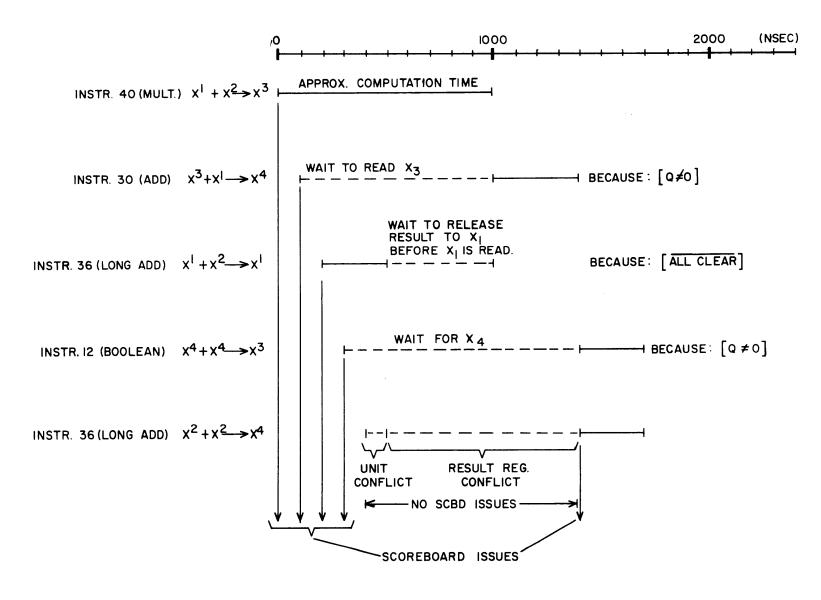

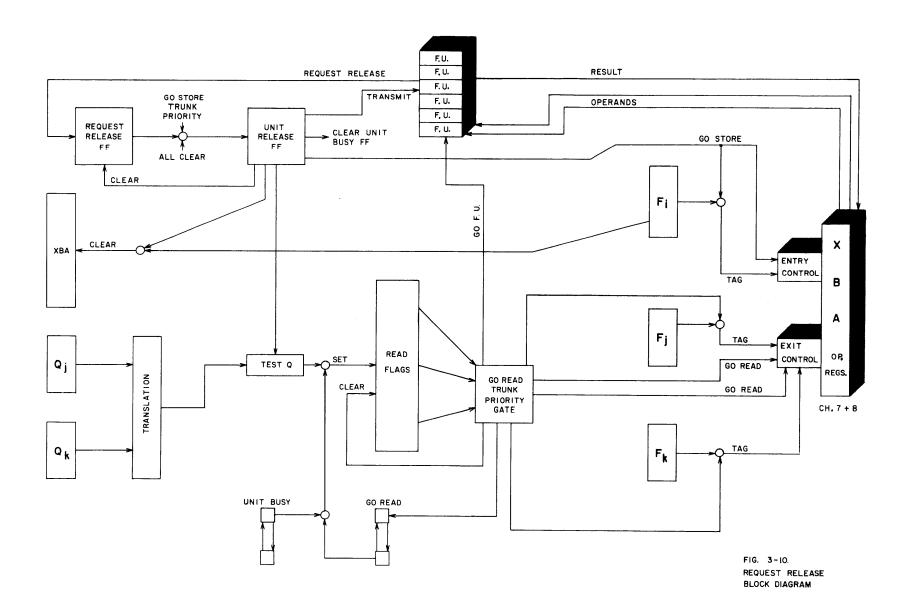

A unit reads its operands, computes, and stores its result after its reservations have been placed. Scoreboard control directs the read operand and store result action. The example used to describe placing reservations is described further to illustrate control operation.