# CONTROL DATA® 6600 COMPUTER SYSTEM

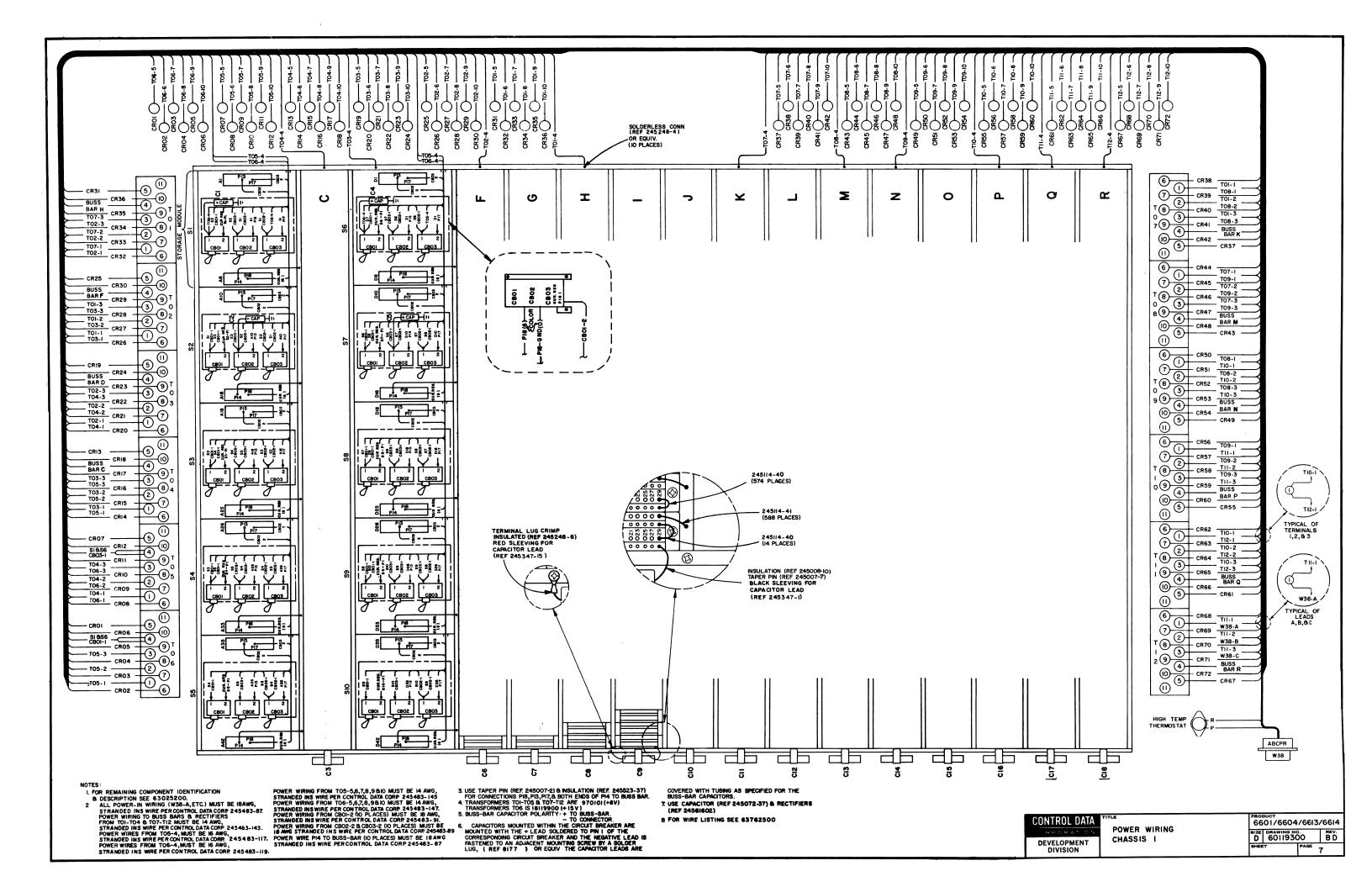

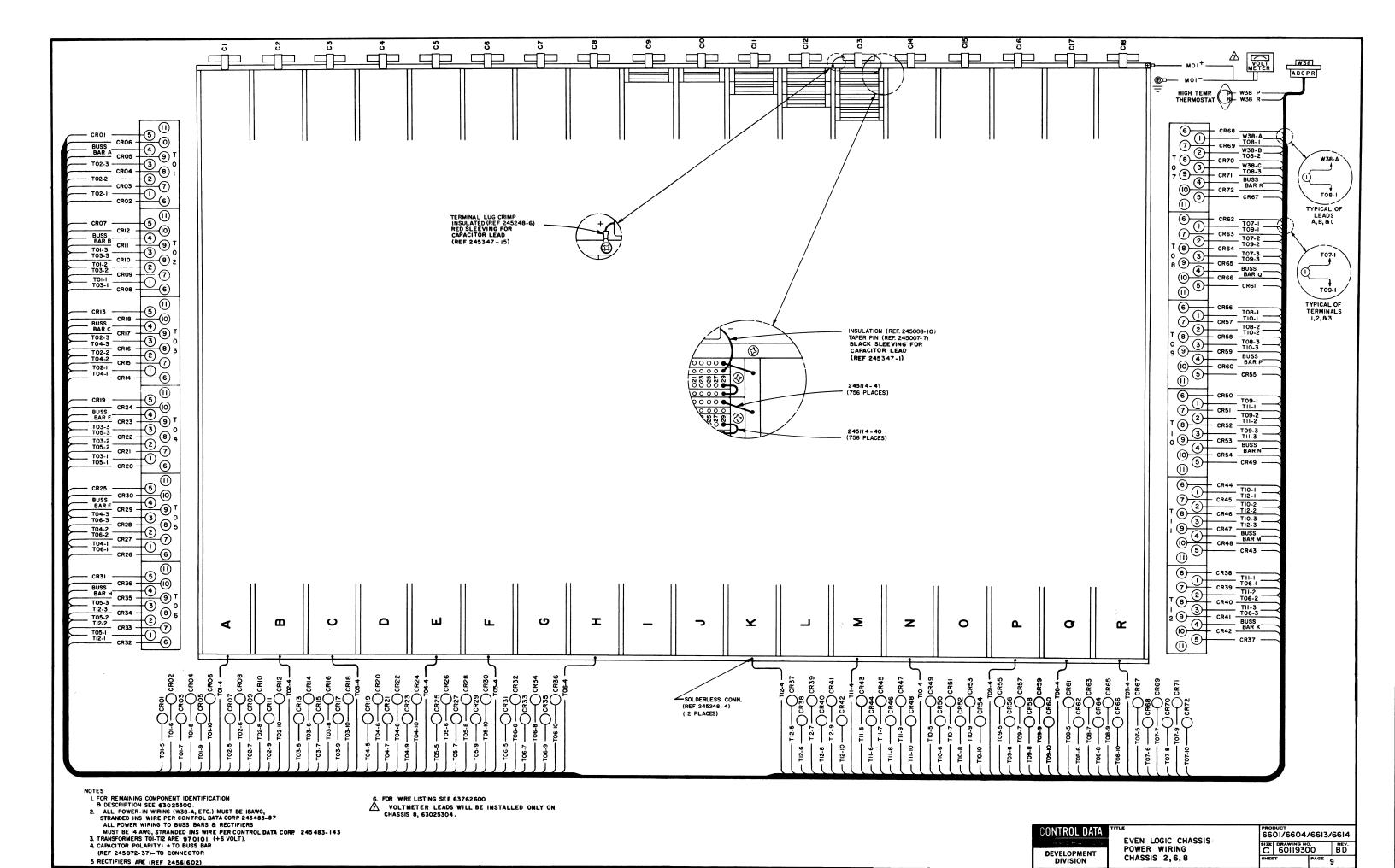

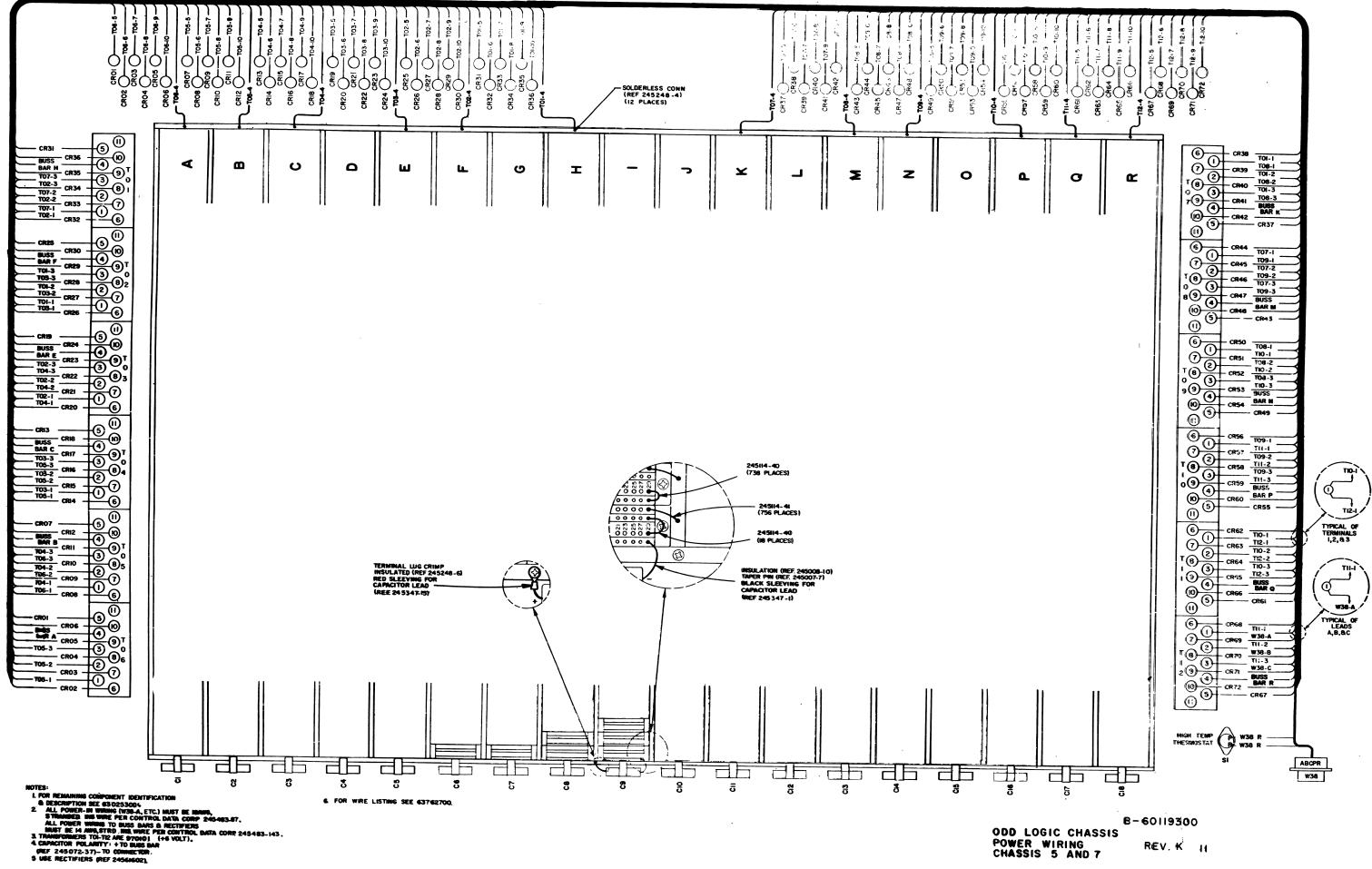

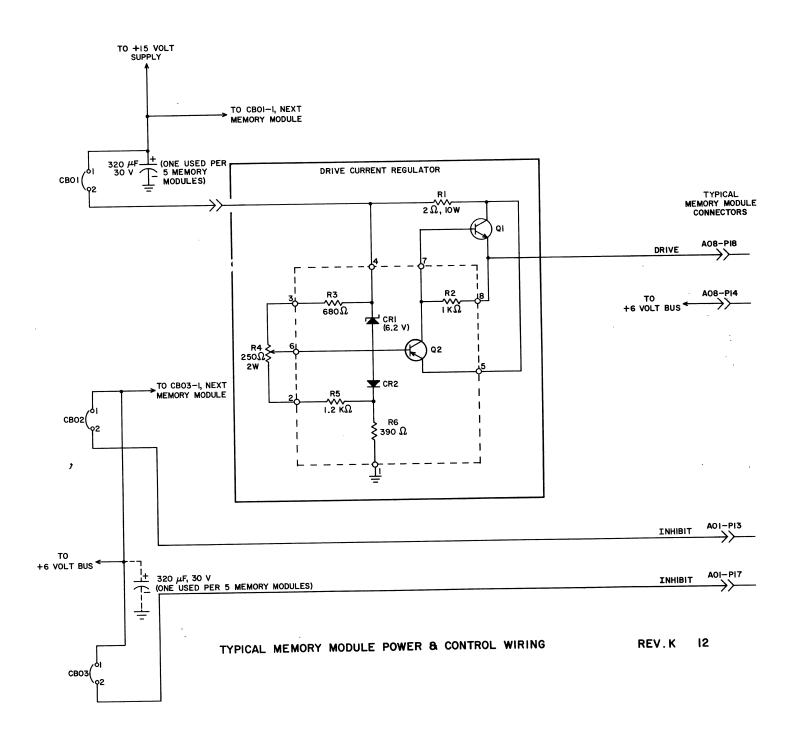

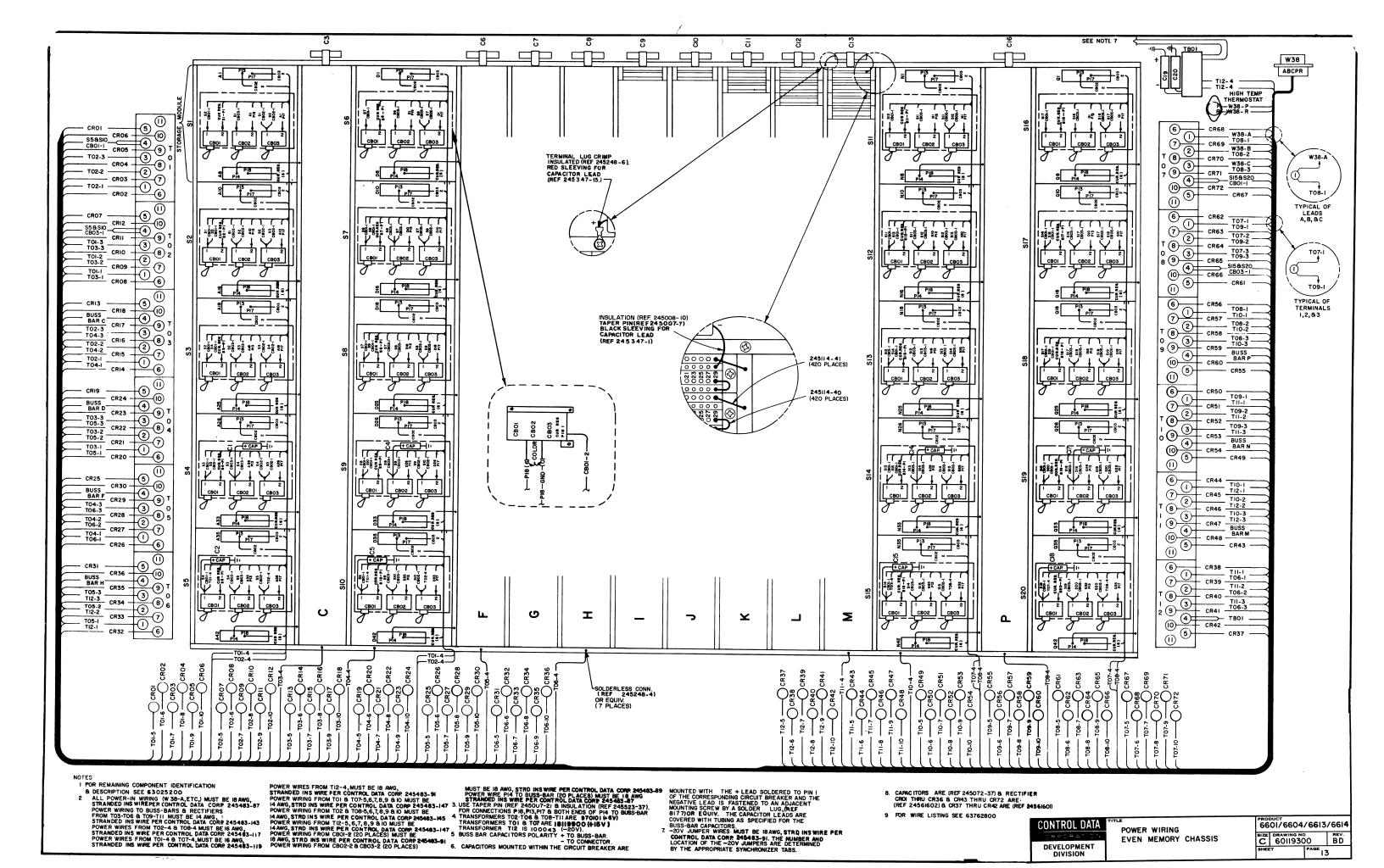

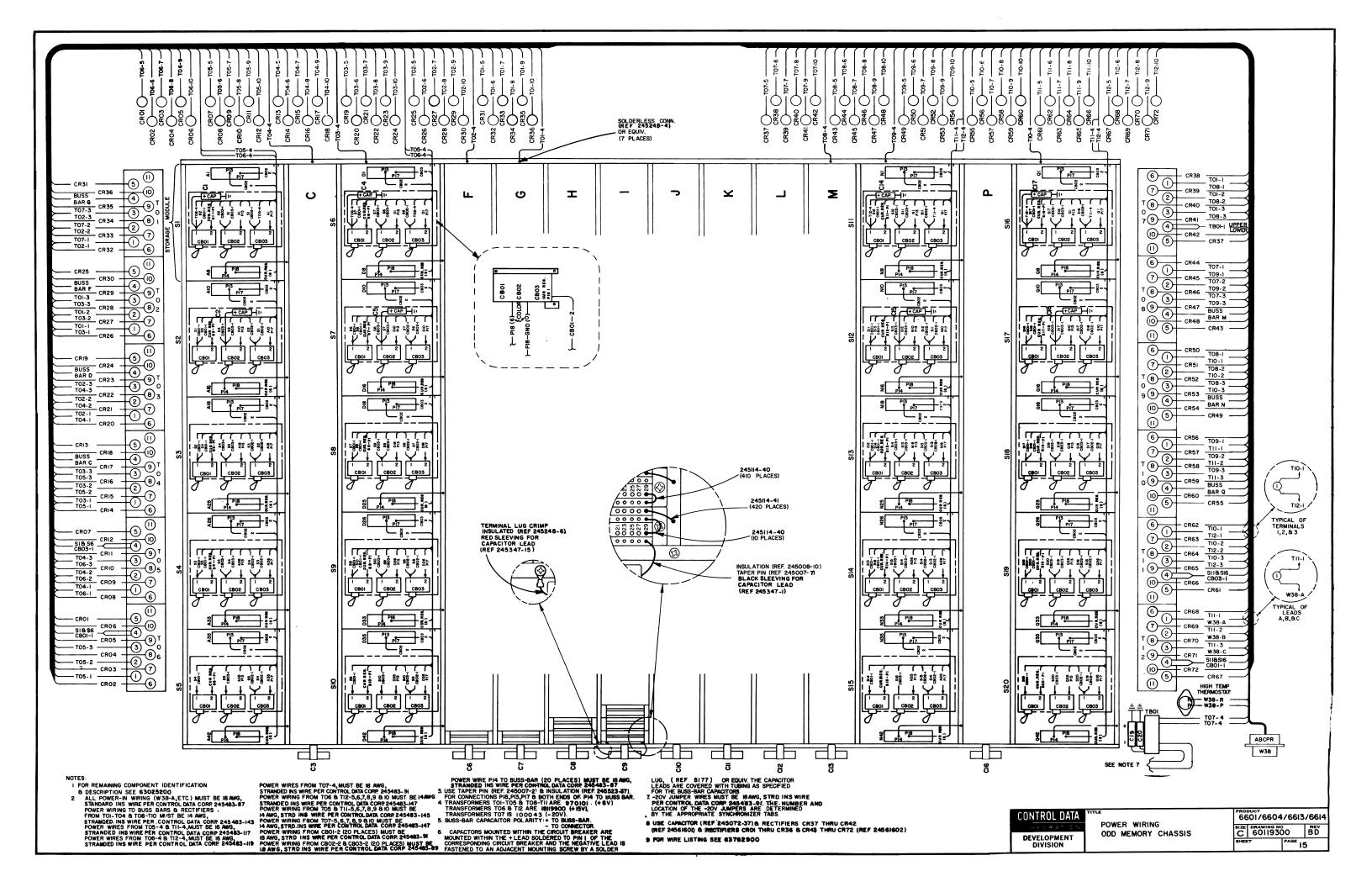

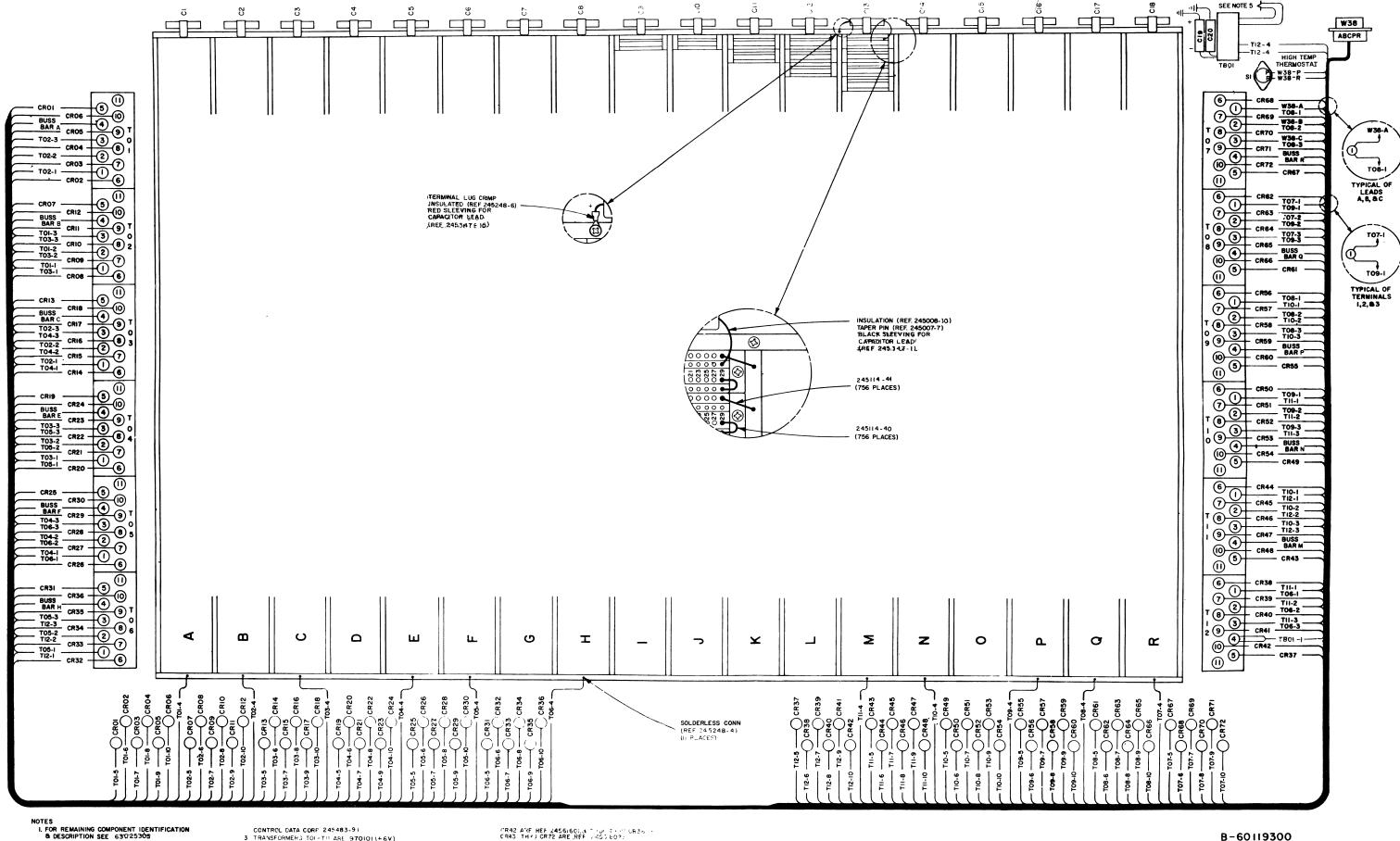

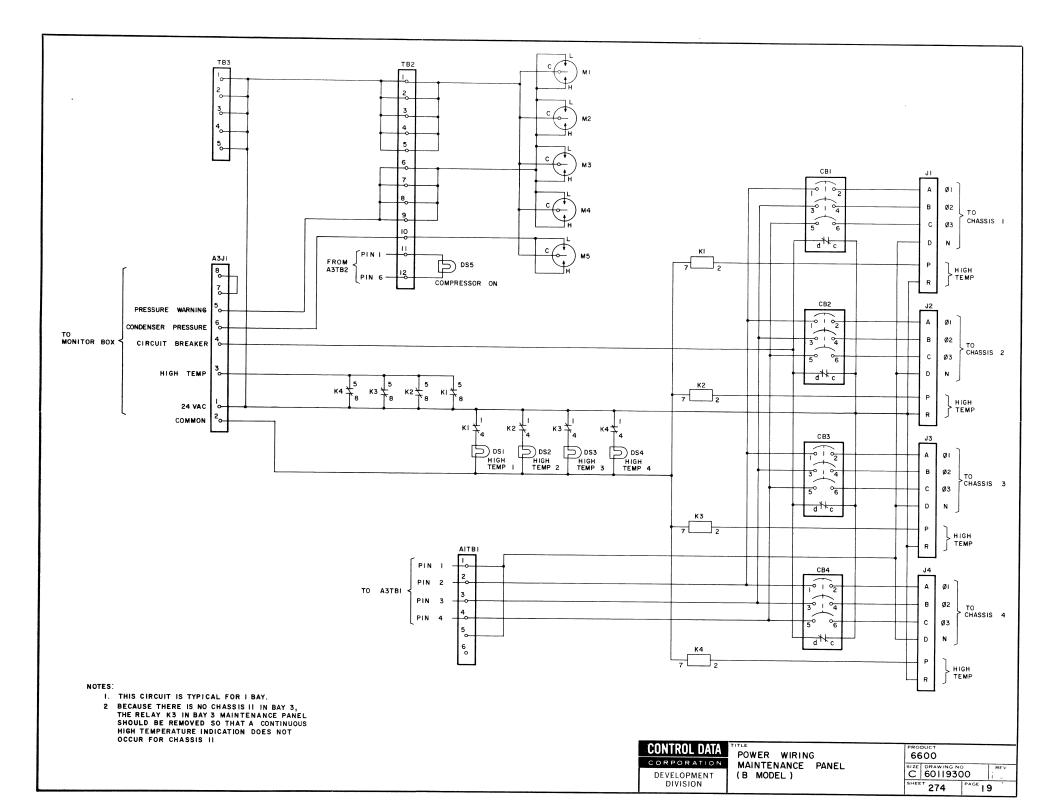

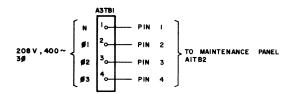

6601 A-J, 6613-A/B/C 6604-A/B/C, 6614-A/B/C Peripheral and Control Processor Central Memory Clock Extended Core Storage Coupler (Std Opt 10102 and/or Spec Opt 60080) Power Wiring

Volume 2

DIAGRAMS & CIRCUIT DESCRIPTIONS

|           | RECORD of REVISIONS                                                                                                                                                                                                                                                              |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REVISION  | NOTES                                                                                                                                                                                                                                                                            |

| A         | Equation Lists and Appendix A added. Miscellaneous changes made for purposes of clarification.                                                                                                                                                                                   |

| В         | Central Memory diagrams added, sheets 38-44. Central Processor diagrams added, sheets                                                                                                                                                                                            |

|           | 45-114. Clock diagrams added, sheets 115-121. Corrections made to Appendix A.                                                                                                                                                                                                    |

| С         | This reprint obsoletes all previous editions. Central Processor completely revised.                                                                                                                                                                                              |

| (3-29-65) | Miscellaneous changes made for purposes of clarification. This printing includes Change Order                                                                                                                                                                                    |

|           | 10946.                                                                                                                                                                                                                                                                           |

| D         | Volumes 1 and 2 obsolete all previous editions. "Add Unit" diagrams added in Volume 1.                                                                                                                                                                                           |

| (7-12-65) | Miscellaneous changes made for purposes of clarification. This printing includes Change Order                                                                                                                                                                                    |

|           | 11826.                                                                                                                                                                                                                                                                           |

| E         | Change Order 12006.                                                                                                                                                                                                                                                              |

| F         | Change Order 12051.                                                                                                                                                                                                                                                              |

| G         | Change Order 12082.                                                                                                                                                                                                                                                              |

| H         | Change Order 12182.                                                                                                                                                                                                                                                              |

| J         | Change Order 12187.                                                                                                                                                                                                                                                              |

| K         | Publication Change Order 12481. The following pages have been revised: 6601/04 Central                                                                                                                                                                                           |

| (1-27-66) | Processor - 1, 3, 4.1, 4.2, 5, 7, 9, 13, 15, 16, 19, 21, 23, 24.1, 25, 29, 31, 33, 35, 43, 53,                                                                                                                                                                                   |

|           | 57, 61, 63, 64, 65, 66, 67, 68.0, 68.1, 68.3, 68.5, 68.7, 68.9, 69, 70, 71, 73, 74, 74.1, 75,                                                                                                                                                                                    |

|           | 77, 79, 80.1, 80.3, 81, 82, 83, 85, 86.1, 86.3, 87, 88.1, 89, 91, 99, 101 and 103. 6601/04                                                                                                                                                                                       |

|           | Functional Units - Contents, 2.3, 3, 5, 7, 9, 11, 13, 14.1, 14.3, 14.4, 14.5, 14.7, 14.8, 15,                                                                                                                                                                                    |

|           | 16, 17, 19, 23, 25, 26, 29, 31, 33, 35, 37, 43, 44, 47, 48, 49, 51, 53, 55, 57, 59, 61, 63, 64,                                                                                                                                                                                  |

|           | 67, 95, 97, 103, 126.1, 126.2, 127, 181, 182.0, 183, 185, 187, 189, 190, 191, 193, 194, 197,                                                                                                                                                                                     |

|           | 201, 205, 207, 211, 213 and Comment Sheet. 6601/04 Peripheral and Control Processor - 1, 2,                                                                                                                                                                                      |

|           | 3, 5, 9, 11, 19, 21, 39, 47, 55, 57, 58, 59, 61, 63, 65 and 67. 6601 Central Memory (131K) -                                                                                                                                                                                     |

|           | Contents, 1, 3, 5, 11, 12.0, 12.1, 12.2, 13, 14.0, 14.1, 14.3, 15. 6604 Central Memory (65K)                                                                                                                                                                                     |

|           | Contents, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14.1, 15. 6601/04 Clock - 3, 5, 7, 9, 11,                                                                                                                                                                                   |

|           | 13, 15, 17. 6601/04 Power Wiring - Contents, 1, 3, 5, 6, 7, 9, 11, 12, 13, 15, 17. 6601/04                                                                                                                                                                                       |

|           | Appendix A - Title page, 2 and Comment Sheet.                                                                                                                                                                                                                                    |

| L         | Field Change Order 13358 which advanced the Product Designation to 6601-H31, 6604-A33 and                                                                                                                                                                                        |

| (6-28-66) | 6605-A12. Central Processor pages 11, 13, 17, 19, 22.1, 24.01, 24.1, 25, 37, 41, 45, 86.01                                                                                                                                                                                       |

|           | and 90.1 revised. Functional Units pages 5, 11, 14.21, 14.3, 14.5, 182 and 185 revised.                                                                                                                                                                                          |

| M         | Publications Change Order 13629 which incorporated Change Orders 11310, 11389, 11467, 11487,                                                                                                                                                                                     |

| (6-28-66) | 11826, 11937, 12006, 12450, 12543, 12655, 12656 and 12761 into this Manual. Vol. 1 Pages                                                                                                                                                                                         |

|           | changed: Cover, Title page, Record of Revisions, Key to Logic Symbols, Central Processor                                                                                                                                                                                         |

|           | Contents, 7, 19, 21, 22.1, 23, 24.01, 24.1, 35, 36.1, 39, 40.1, 43, 44.1, 63, 79, 80.01, 80.3,                                                                                                                                                                                   |

|           | 81, 82.1, 85, 86.01, 86.1, 86.3, 87, 88.1, 89, 90.1, 91, 101, 103 and 105. Functional Unit                                                                                                                                                                                       |

|           | Contents, 3, 5, 7, 9, 11, 13, 14.1, 14.21, 14.3, 14.5, 14.7, 15, 39, 63, 99, 101, 103, 137,                                                                                                                                                                                      |

| ,         | 149 173 181 182 01 182 1 185 187 197 and 213 Wal 2 Degree sharped Green William                                                                                                                                                                                                  |

|           | 149, 173, 181, 182.01, 182.1, 185, 187, 197 and 213. Vol. 2 Pages changed: Cover, Title page, Record of Revisions, Key to Logic Symbols, Peripheral Processor Contents, 5, 6.1 and 6.2. Central Memory (131K) Contents, 10.1 and 11. Central Memory (65K) Contents, 11 and 12.1. |

|           | Memory (131K) Contents 10 1 and 11 Central Memory (65K) Contents 11 and 12 1                                                                                                                                                                                                     |

|           | - Contral Memory (Ook) Contents, 11 and 12.1.                                                                                                                                                                                                                                    |

Address comments concerning this manual to:

Control Data Corporation Technical Publications Department 4201 North Lexington Avenue St. Paul, Minnesota 55112

or use Comment Sheet in the back of this manual.

| RECORD of REVISIONS (CONT'D)            |                                                                                                                     |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| REVISION                                | NOTES                                                                                                               |  |

| M (Con't)                               | Clock Contents 1, 3, 4.1, 11, 12.1.                                                                                 |  |

| N thru AP                               | Publication Change Order 14798 which incoporated the following Change Orders: 13415, 13512,                         |  |

| (10-10-66)                              | 13513, 12930, 13536, 13545, 13569, 12932, 12933, 12931, 13731, 13814, 14136, 13999, 14045,                          |  |

|                                         | 14111, 14112, 14153, 13757, 14202, 14203, 13746 and 13756. Vol. 1 Pages changed: Central                            |  |

|                                         | Processor 23, 24.01, 24.1, 31, 55, 71, 86.01, 86.3, 87, 89 and 90.1. Functional Units 19, 31,                       |  |

|                                         | 61, 63, 73, 93, 125, 157, 161, 175, 197, 209, 211 and 213. Vol. 2 Peripheral and Control                            |  |

| *************************************** | Processor page 67. 6601/6613 Central Memory (131K) page 7. 6604/6614 Central Memory                                 |  |

|                                         | (65K) pages 7 and 12.1. 6601/6604/6613/6614 Clock page 15 and 17.                                                   |  |

| AR thru BD                              | Publication Change Order 16000 which incorporated the following Change Orders: 14247, 14767,                        |  |

| (3-22-67)                               | 15218, 15252, 15338, 15339, 15191, 15562, 15563, 15068 and 15750. Vol. 1 pages changed:                             |  |

|                                         | Central Processor 31, 39, 81, 82.1, 89, 99 and 105. Functional Units 101. Vol. 2 pages                              |  |

|                                         | changed: Peripheral and Control Processor 5, 15 and 23. Clock - Contents and page 3. Power                          |  |

|                                         | Wiring - Pages 7, 9, 13 and 15 revised. Pages 19, 21, 23 and 25 added. Cover and title page                         |  |

|                                         | revised for Vol. 1 and Vol. 2.                                                                                      |  |

| BE thru BL                              |                                                                                                                     |  |

| (11-9-67)                               | Publication Change Order 17138, which incorporated the following change orders: 14642, 15841,                       |  |

| (11-9-07)                               | 15829, 15968, 15985 and 16269. Vol. 1 pages changed: General Contents (new). Central                                |  |

| <del></del>                             | Processor 17 and 91. Functional Units 3, 14.5, 31, 93, 101, 103, 107, 117, 123, 163, 173,                           |  |

|                                         | 181, 182.0, 187, 189, 203 and 213. Vol. 2 pages changed: Cover and Title Page, General                              |  |

|                                         | Contents (new), Peripheral and Control Processors 3, 5, 25, 29, 49, 53, 55 and 57. Central                          |  |

|                                         | Memory (131K) 8.1. Central Memory (65K) 8.1. Clock, page 3. E.C.S. Coupler Section                                  |  |

|                                         | Pages 1 thru 37 (new). Power Wiring 1, 19, 21, 23 and 25.                                                           |  |

| BM thru BT                              | Publication Change Order 18437, which incorporated the following Change Orders: 17014, 17269,                       |  |

| (1-12-68)                               | 17251, 17346 and 17660. Vol. 1 pages changed: Central Processor, pages 7, 9, 11, 13, 19, 22. 1,                     |  |

|                                         | 24.01,41,67,68.7,69,71,87,90.1,91 and 105; Functional Units pages 3,5,7,9,11,14.1,14.3,14.5,                        |  |

|                                         | 14.7, 19, 31, 61, 63, 75, 77, 79, 81, 83, 85, 93, 95, 97, 101, 103, 105, 109, 111, 117, 119, 121, 123, 125, 133,    |  |

|                                         | 135, 137, 139, 141, 145, 147, 149, 151, 153, 155, 159, 161, 163, 165, 167, 169, 173, 175, 180, 3, 180, 7, 185, 197, |  |

| ······································  | 199, 207, 209, 211 and 213. Vol. 2 pages changed: Peripheral and Control Processors pages 6.1,7,9                   |  |

|                                         | 19, 21, 25, 29, 31, 37, 39, 41, 47, 51, 55, 57, 59, 61, 65, and 67; Central Memory (131K) pages 4, 5, 8, 8. 1,      |  |

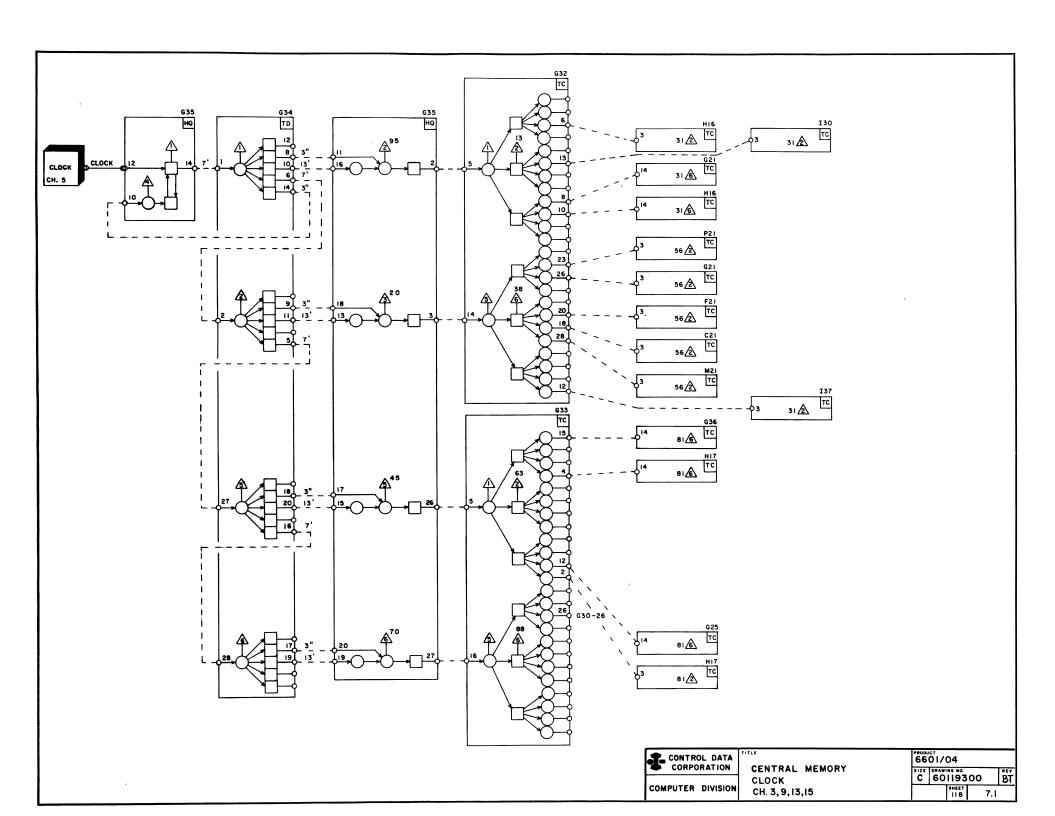

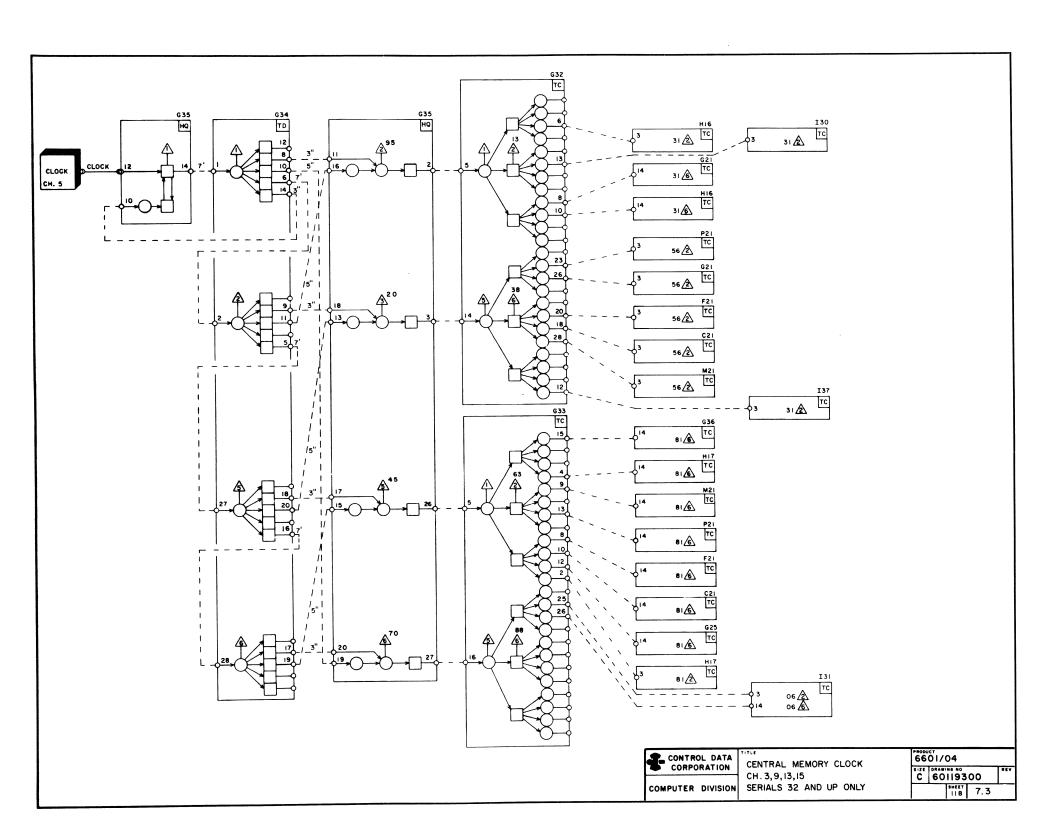

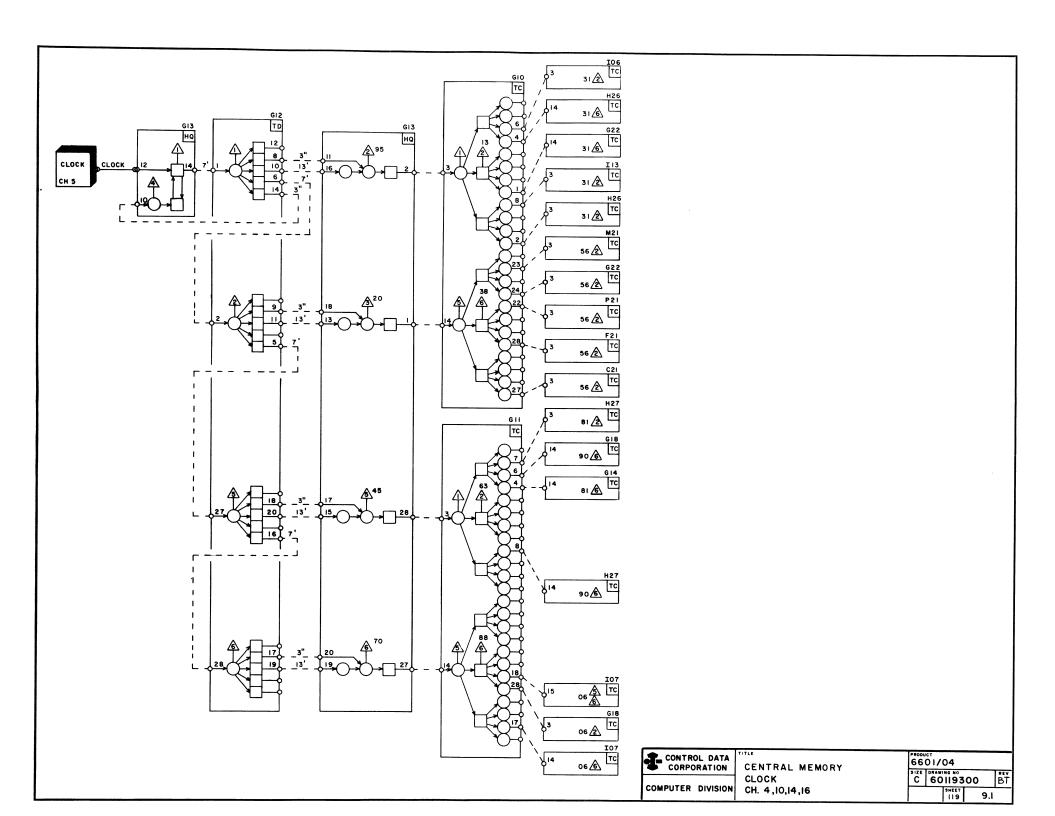

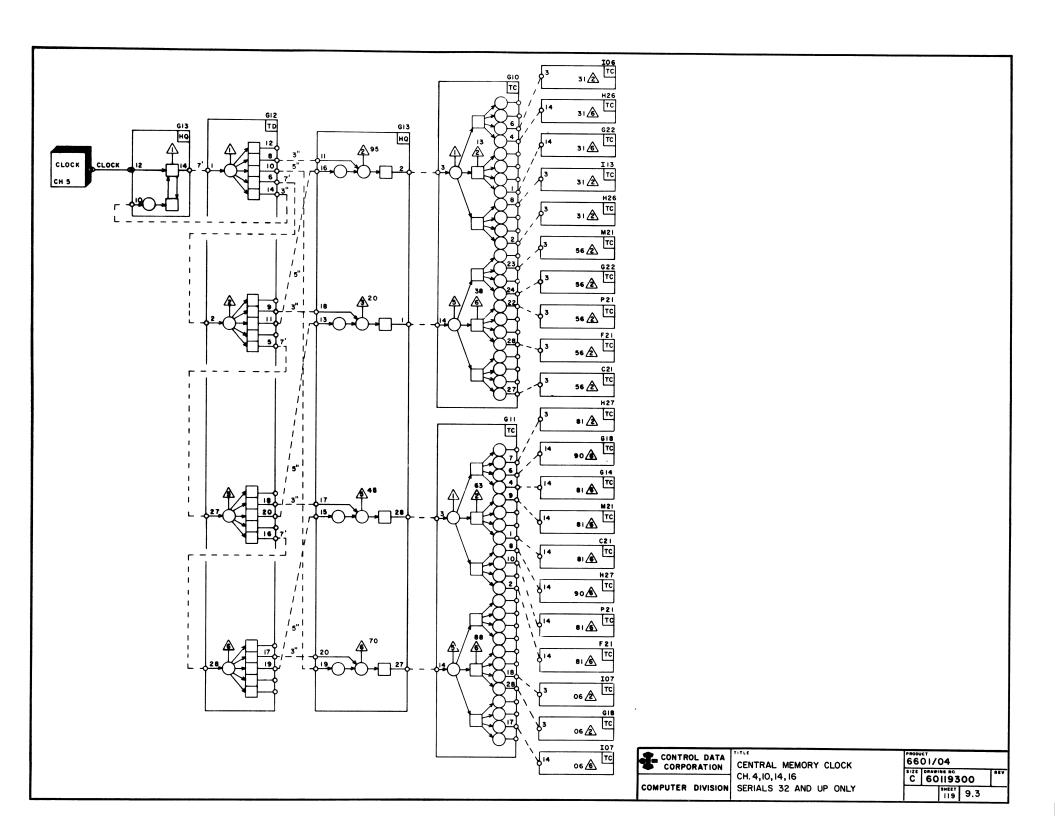

|                                         | 11 and 15. Central Memory (65K) pages 4,5,8 and 15. Clock Section pages Clock Contents, 4.1,                        |  |

|                                         | 5, 7. 1, 7. 3 (new), 9. 1, 9. 3 (new), 12. 1, 12. 3 (new), 13, 15 and 17. Appendix pages 12 and 14.                 |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

|                                         | -                                                                                                                   |  |

|                                         |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

| <u> </u>                                |                                                                                                                     |  |

|                                         |                                                                                                                     |  |

# GENERAL CONTENTS

| VOLUME 1 | Part 1. | Central Processor                                                                                                               |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------|

|          | Part 2. | Functional Units                                                                                                                |

| VOLUME 2 | Part 3. | Peripheral and Control Processors                                                                                               |

|          | Part 4. | Central Memory 131K                                                                                                             |

|          | Part 5. | Central Memory 65K                                                                                                              |

|          | Part 6. | Clock                                                                                                                           |

|          | Part 7. | Extended Core Storage Coupler (Standard Option 10102 and Special Option 60080 for 6601/04, Special Option 60080 for 6613/14/15) |

|          | Part 8. | Power Wiring                                                                                                                    |

|          | Part 9. | Appendix A                                                                                                                      |

## FOREWORD

Logic diagrams contained in this manual do not attempt to show the entire device, nor even depict complete modules within that device. The purpose of the diagrams is to show the logical significance of circuits that may involve parts of many modules on several chassis. Logic hardware that is not pertinent to the particular logic

sequence being illustrated is not included. Certain areas may not be shown at all, while others may appear on several drawings. These limitations are important to remember; the logic diagrams do not replace the 6000 Series chassis and cable tabs, but they are a valuable tool in understanding the tabs and the overall operation of the machine.

#### KEY TO LOGIC SYMBOLS

(Standard 6000 Series Card Types)

Logic diagrams represent a symbolic approach to electronic schematics. By using symbols to represent building block circuits, the schematic becomes easy to read if the reader understands the function of the symbols. In CONTROL DATA\* logic, two signals, a logical "0" and a logical "1" are the possible input or output conditions of a circuit. For example, "1" is considered "up" and "0" is considered "down" on a timing chart. Detailed descriptions of logic symbols and their associated electronic representations are contained in the Printed Circuit Manual, Cordwood Modules (Pub. No. 60042700).

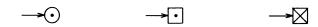

#### STANDARD LOGIC SYMBOLS

Standard logic diagram symbols for Control Data equipment using 6000 Series card types are inverters, test points, flip-flops, twisted pair line drivers, and coaxial cable line drivers.

#### Inverters

An inverter is a logic element which provides an output that is a negation of its imput. When more than one input is provided to an inverter, "0's" take precedence over "1's" and therefore drive the output of the inverter to "1". Because all of the several inputs have to be "1" to drive the output of the inverter to a "0", the inverter may be considered an inverting AND (or NAND) gate when more than one input is present. The basic inverter is shown in the logic diagrams as an arrow into either a circle or a square (Figure 1). Both symbols represent the same electronic circuit and have the same logic interpretation. In a logic sequence of inverters, circle and square symbols are usually alternated as an aid in tracing signals, e.g., a "1" output from a square symbol implies a "1" output from subsequent squares in the logic chain.

Figure 1. Inverter Symbols

Certain card types employ variations of the standard inverter building block. These differences are indicated in the logic diagrams by a dot or a cross in the circle or square (Figure 2). Both the chassis tabs containing the card in question and the Printed Circuit Manual, Cordwood Modules (Pub. No. 60042700) contain electronic schematics of these special variations.

Figure 2. Special Inverters

Acceptable conventions for showing multiple inputs and outputs are given in Figure 3. Note that the output of inverter A is "0" only if inputs X, Y, and Z are all "1". The multiple outputs are identical.

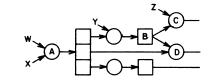

Figure 3. Multiple Inputs/Outputs

Acceptable conventions for showing inverter networks are illustrated in Figure 4. As a general rule, circle inverters alternate with square inverters wherever possible. Because multiple outputs are identical, only one arrow is shown in cases where an inverter (A) serves as the single input to several succeeding inverters. In more complex inverter networks, multiple arrows are used (B to C and D; in this case because B is not the only input to C or D).

Figure 4. Inverter Networks

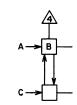

## Test Points

A test point has no logic function, but is shown in the logic diagrams as a triangle (Figure 5). They are numbered from 1 to 6.

Figure 5. Test Point Symbols

<sup>\*</sup>Registered trademark of Control Data Corporation

## Flip-Flops (FF)

The flip-flop (FF) is a storage device with two stable states--designated as Set and Clear--and is composed of two inverters (Figure 6). The flip-flop is said to be set when the set output (B) is a "1", and clear when it is a "0". Note that the input (A) must be "0" to set the flip-flop and (C) must be "0" to clear it.

Figure 6. Flip-Flop Symbol

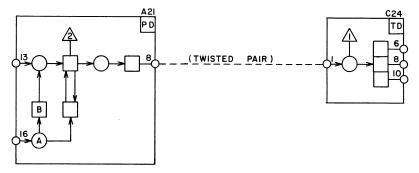

Logic signals are transmitted from one module to another by means of a line driver. Modules on the same chassis are connected with twisted pair lines, and those on separate chassis are connected by coaxial cable.

## Twisted Pair Drivers

The twisted pair driver is represented by the standard square or circle. The output of the square or circle, however, is connected to a pin of the module in question and wired from there to a pin on another module (Figure 7). The ground wire of the pair is wired to the connector ground bus of each module. The pins are represented by small circles and are numbered from 1 to 28 (Pins 29 and 30 are ground and +6 volts, respectively, and generally are not shown in logic diagrams). The module location is shown above the card, and the module type is denoted in the upper right corner.

Figure 7. Twisted Pair Line Driver

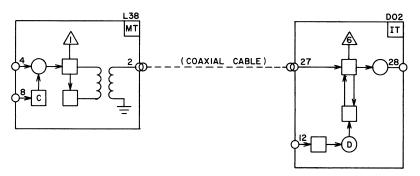

## Coaxial Cable Drivers

The coaxial cable driver is a 25 nsec pulse circuit, and is represented as shown in Figure 8. The pins used are represented by a small double circle.

Figure 8. Coaxial Cable Driver

# PERIPHERAL AND CONTROL PROCESSORS

# CONTENTS

| Page       | Title                                                        | Page       | Title                                             |

|------------|--------------------------------------------------------------|------------|---------------------------------------------------|

|            | Peripheral and Control Processors, Introduction              | 37         | A Adder                                           |

| 1          | Overall Block Diagram                                        | 39         | A Register Gates                                  |

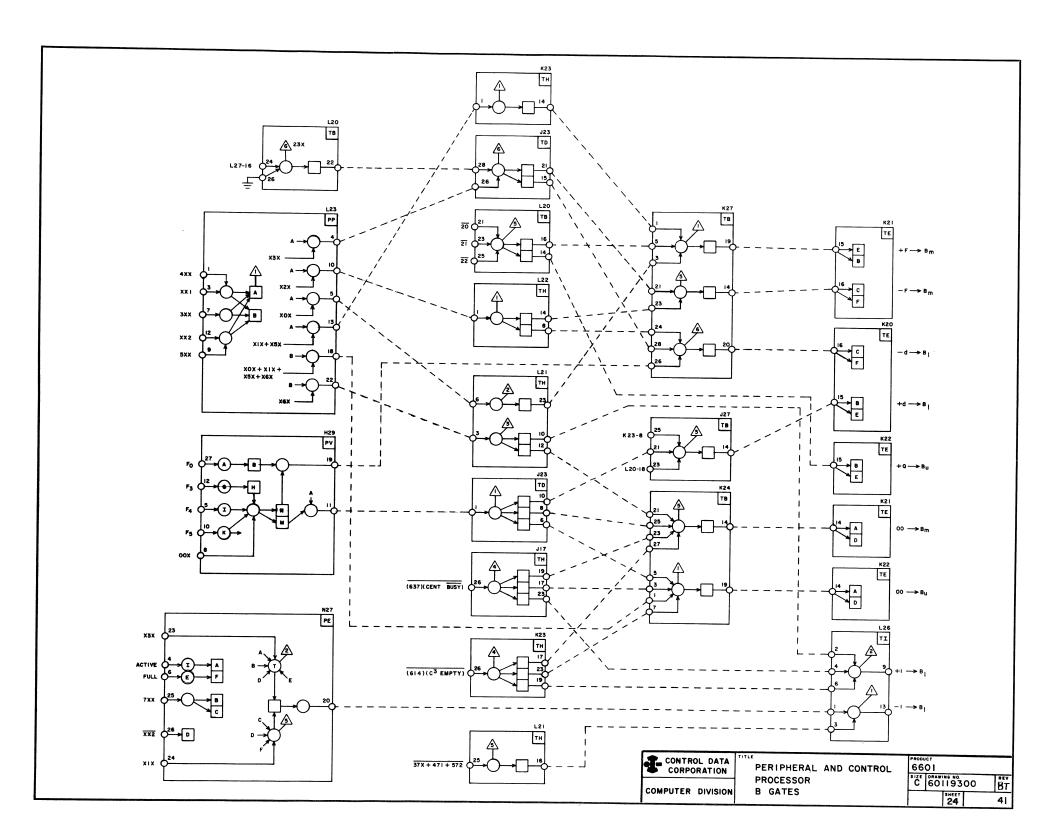

| 2          | Equation Lists                                               | 41         | B Gates                                           |

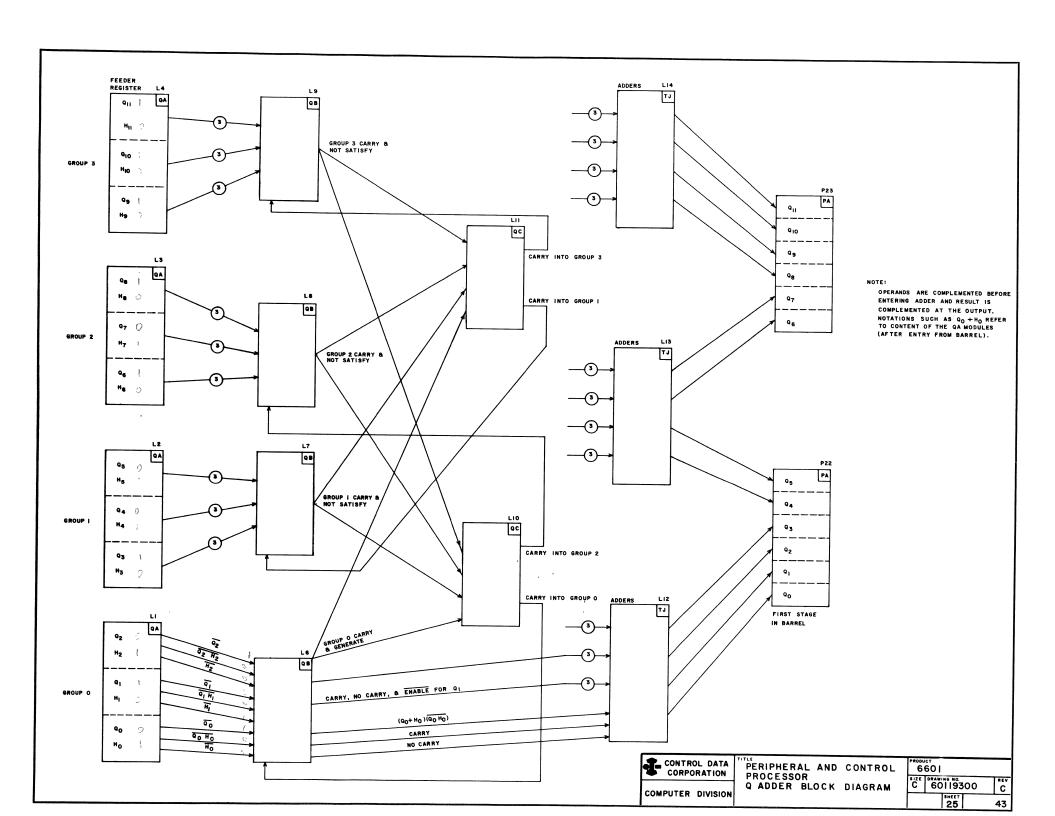

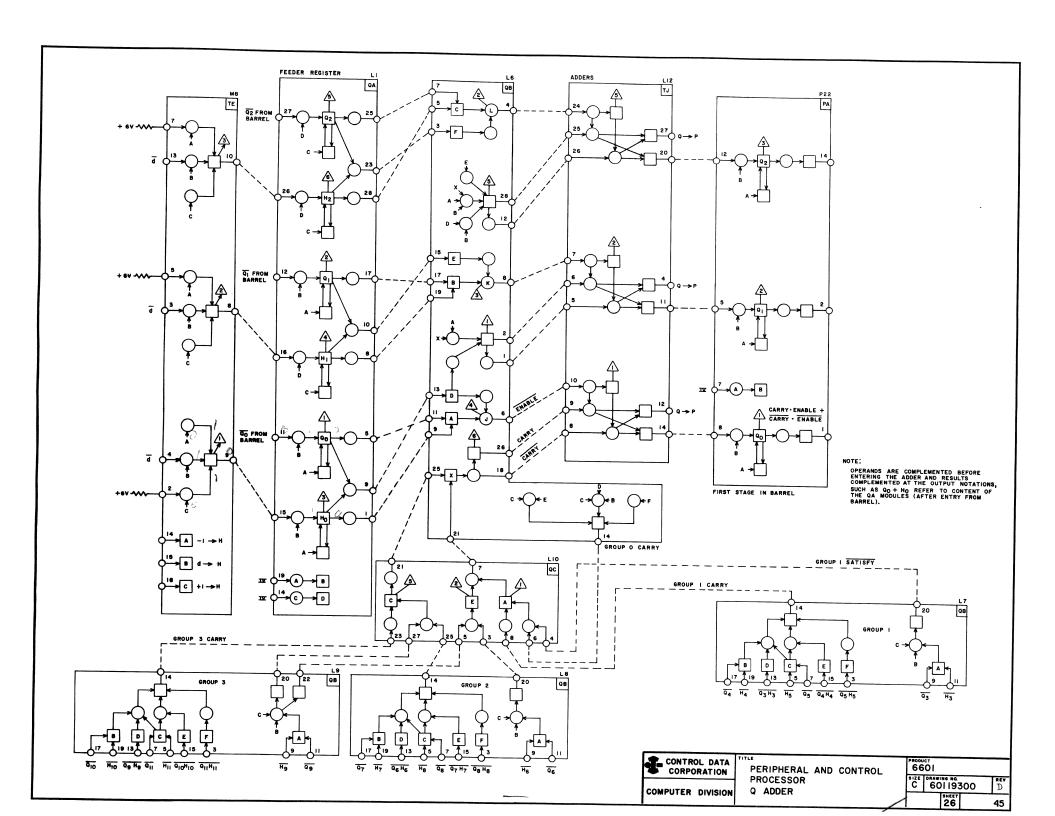

| 3          | Detail Block Diagram                                         | 43         | Q Adder Block Diagram                             |

| 4          | Timing, Master Clock                                         | 45         | Q Adder                                           |

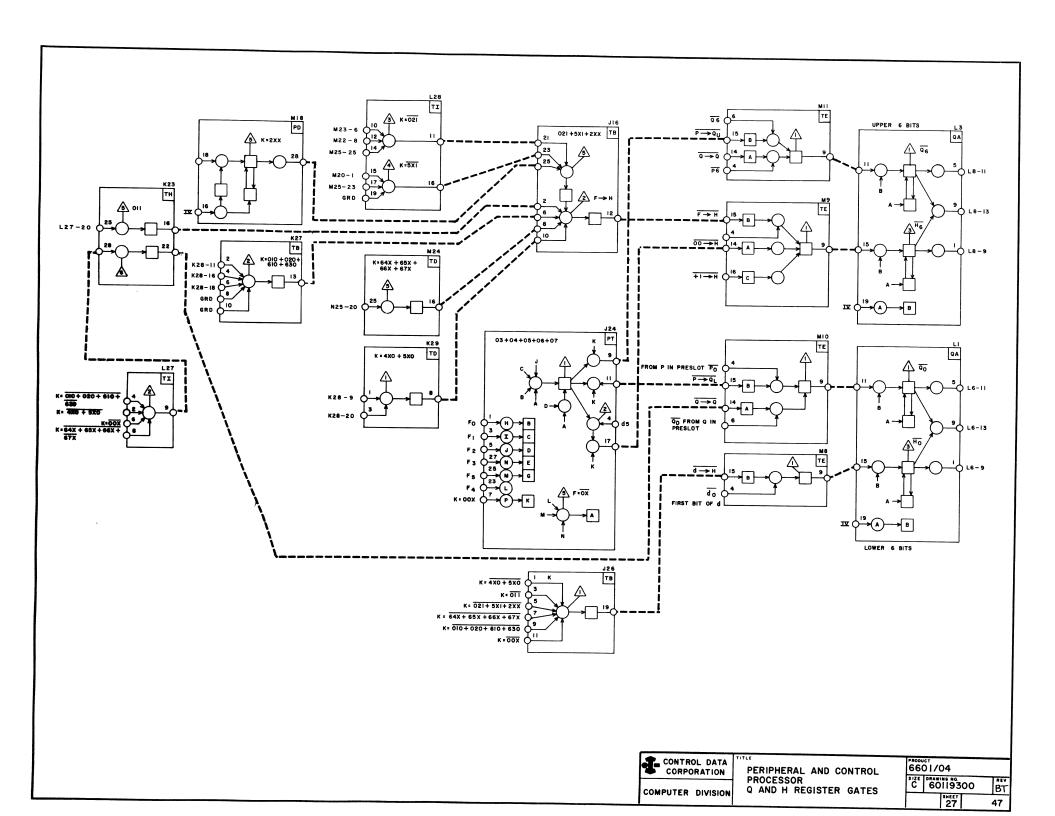

| 5          | Central Processor Master Clock (Chassis 1), Serials 1-7      | 47         | Q and H Register Gates                            |

| 6.1        | Central Processor Master Clock (Chassis 1), Serials 8 and up | 49         | H Gates                                           |

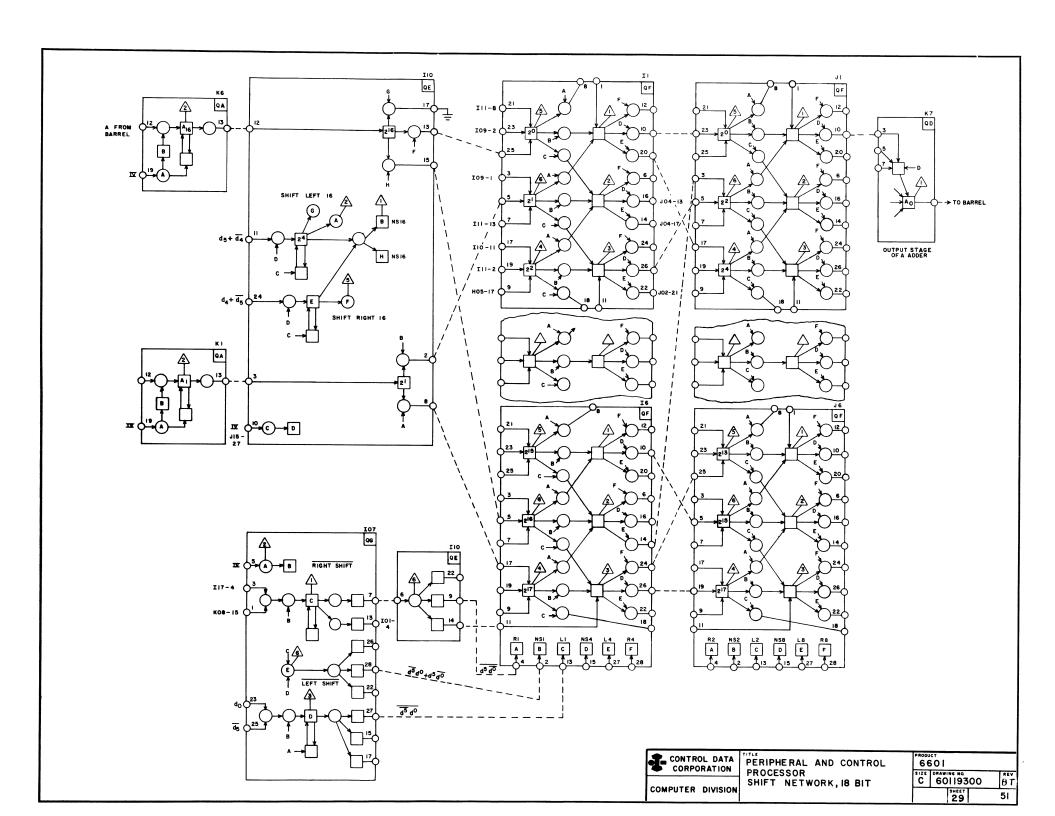

| 6.2        | Barrel, A Register, P Register, Q Register                   | 50         | Shift Network                                     |

| 7          | A, P, Q Typical Barrel Paths                                 | 51         | Shift Network, 18-Bit                             |

| 8          | K Register                                                   | 52         | Communication with Central Memory and Central     |

| 9          | KO Barrel and Slot Paths, and Typical Translations           |            | Processor, Central Program Monitor, Exchange Jump |

| 10         | Slot                                                         | 53         | Central Read Control                              |

| 11         | Barrel Timing                                                | 54         | Central Read                                      |

| 13         | Barrel Map                                                   | 55         | Central Read Pyramid                              |

| 14         | Storage Sequence Control, Memory                             | 56         | Central Write                                     |

| 15         | Storage Sequence Control                                     | 57         | Central Write Pyramid                             |

| 17         | Storage Sequence Control Timing                              | 58         | Input/Output, Master Clear, Disconnect (75),      |

| 18         | Memory Cycle Path                                            |            | Function (76 or 77), Activate (74)                |

| 19         | Typical Memory Cycle Path                                    | <b>5</b> 9 | Input/Output Paths                                |

| 21         | <b>P → G, Q →</b> G                                          | 60         | Data Input Sequence, Status Request               |

| 22         | K Register                                                   |            | Data Output Sequence.                             |

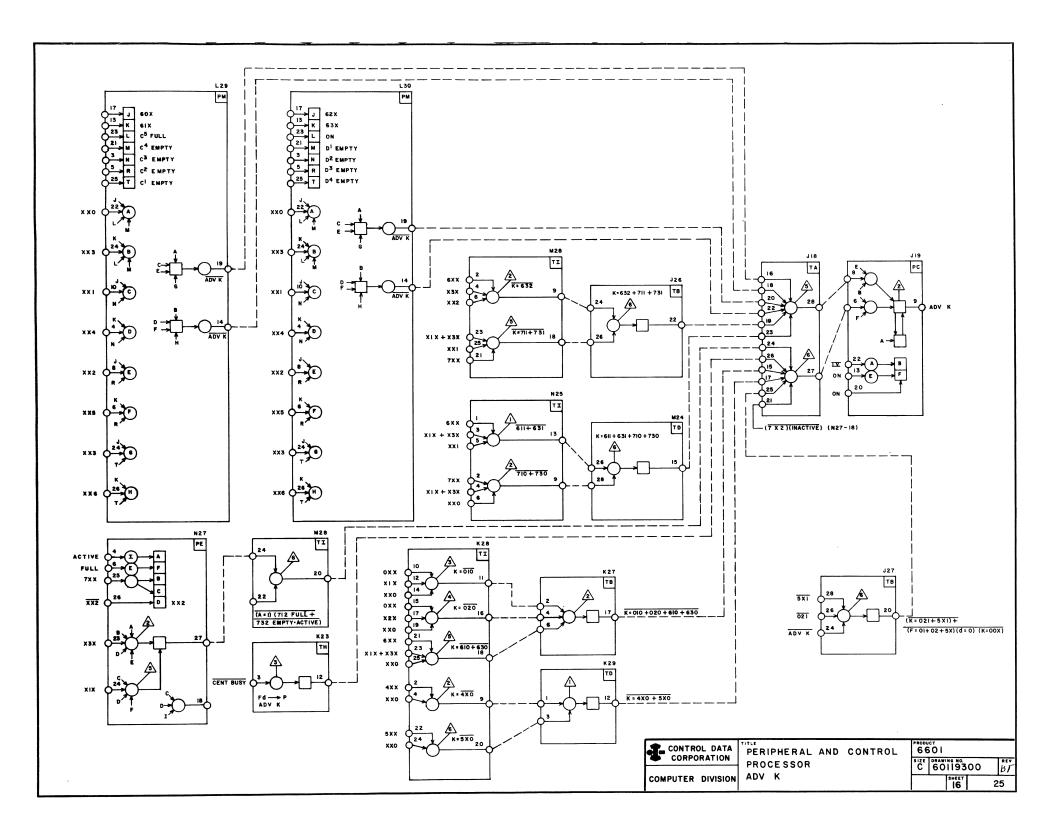

| 23         | K Translations, General                                      | 61         | Dead Start                                        |

| 25         | Adv. K                                                       | 62         | Dead Start, Load, Sweep, Dump                     |

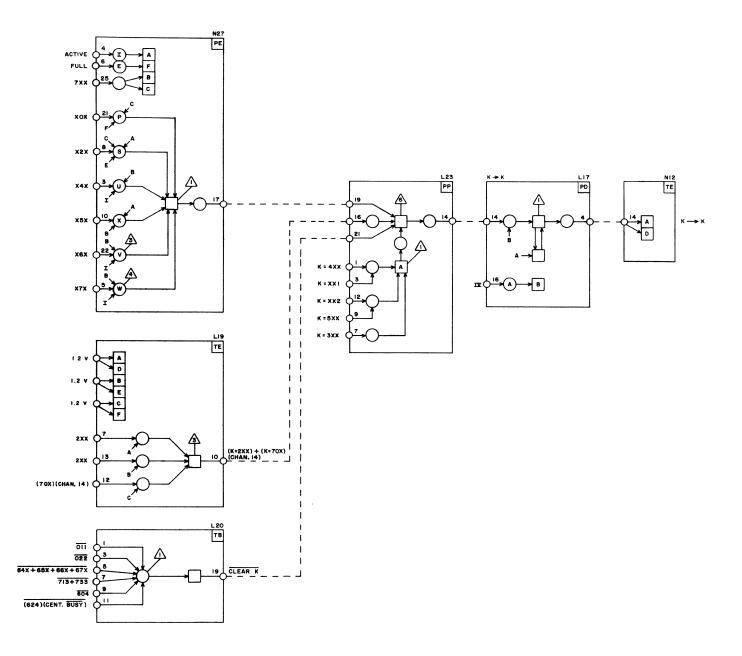

| 27         | K → K Gate                                                   | 63         | 712, 732, 505 → K (Dead Start)                    |

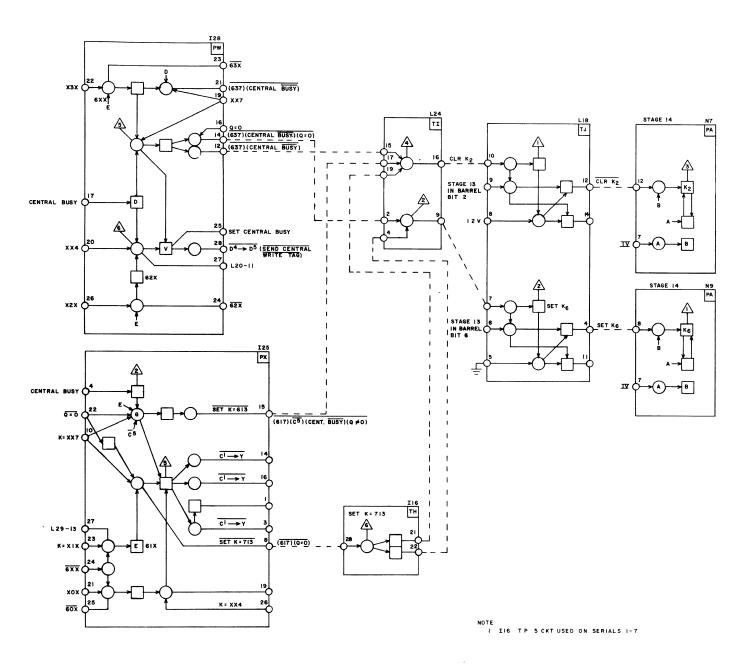

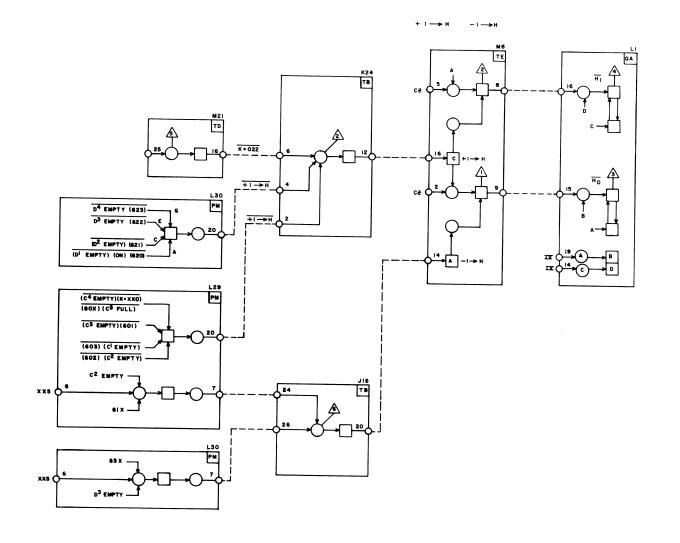

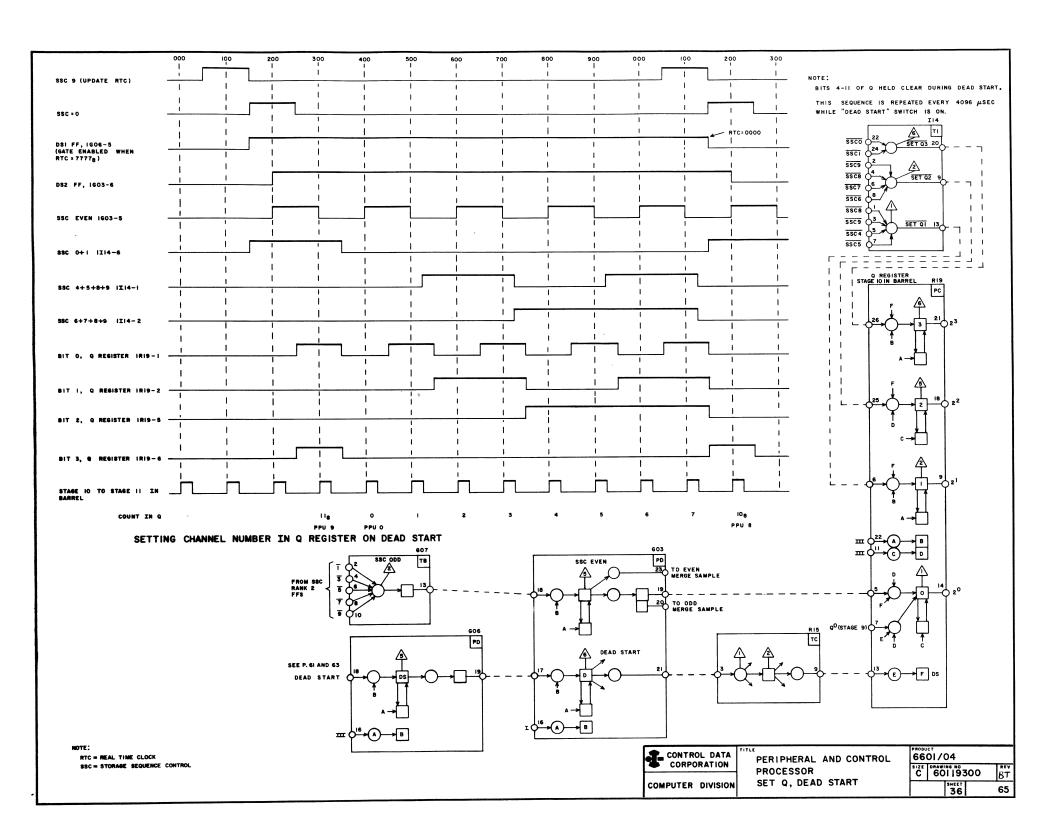

| <b>2</b> 9 | Clr. K <sub>2</sub> , Set K <sub>6</sub>                     | 65         | Set Q, Dead Start                                 |

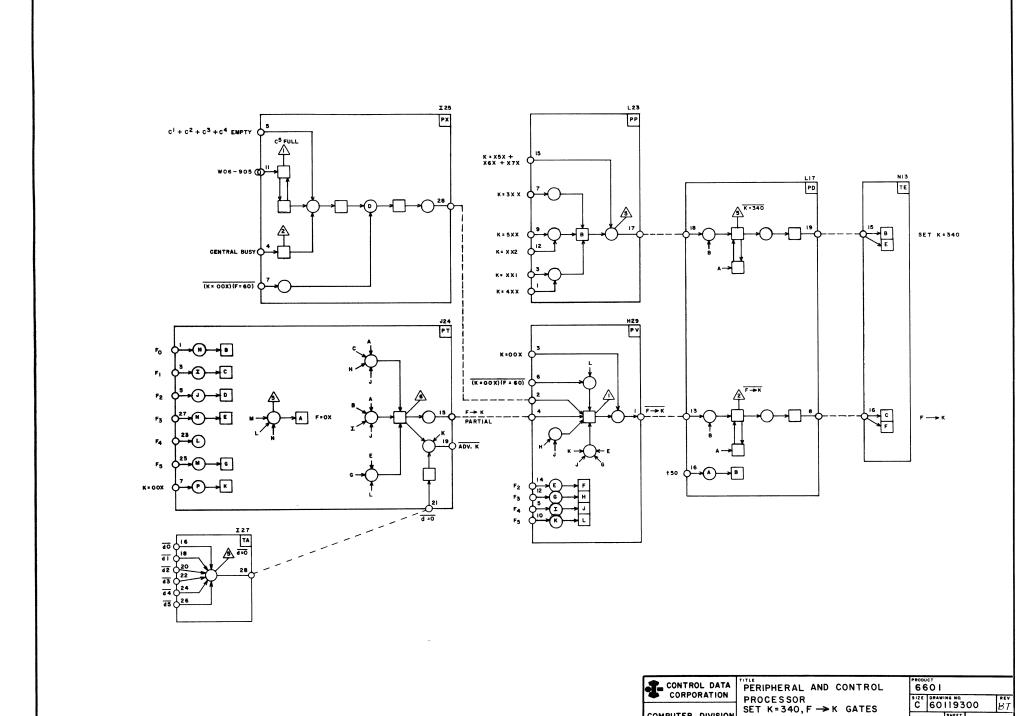

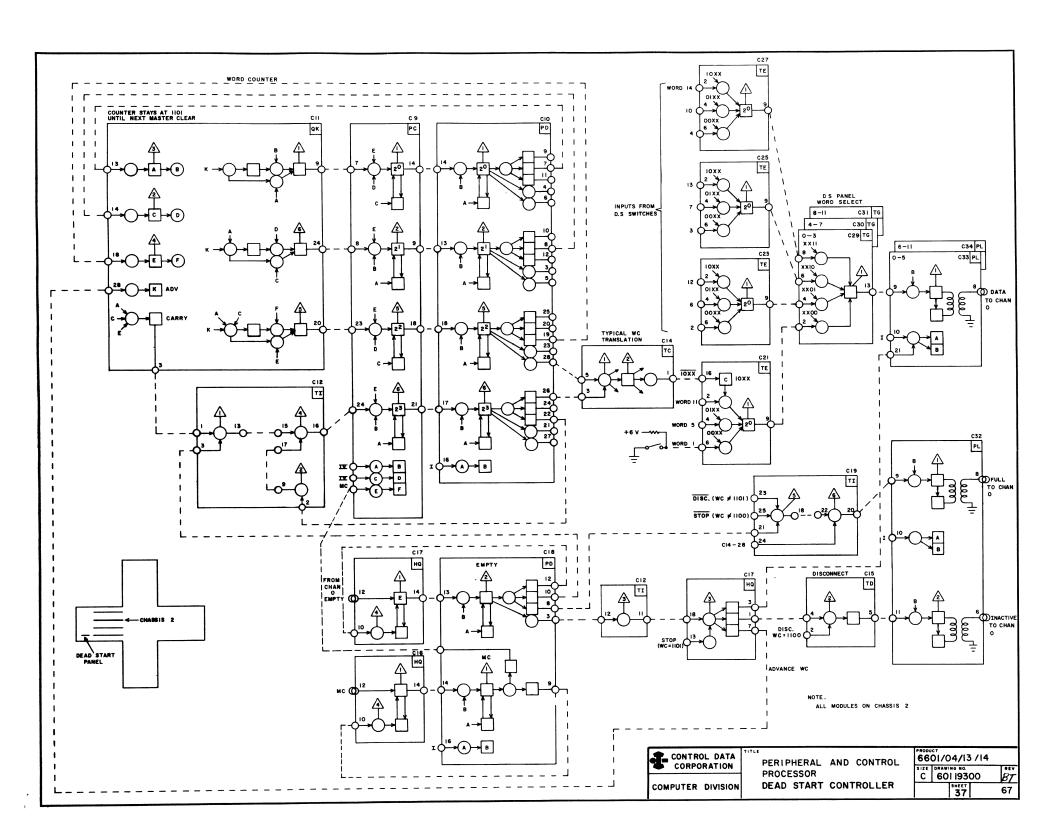

| 31         | Set K = 340, F → K Gates                                     | 67         | Dead Start Controller                             |

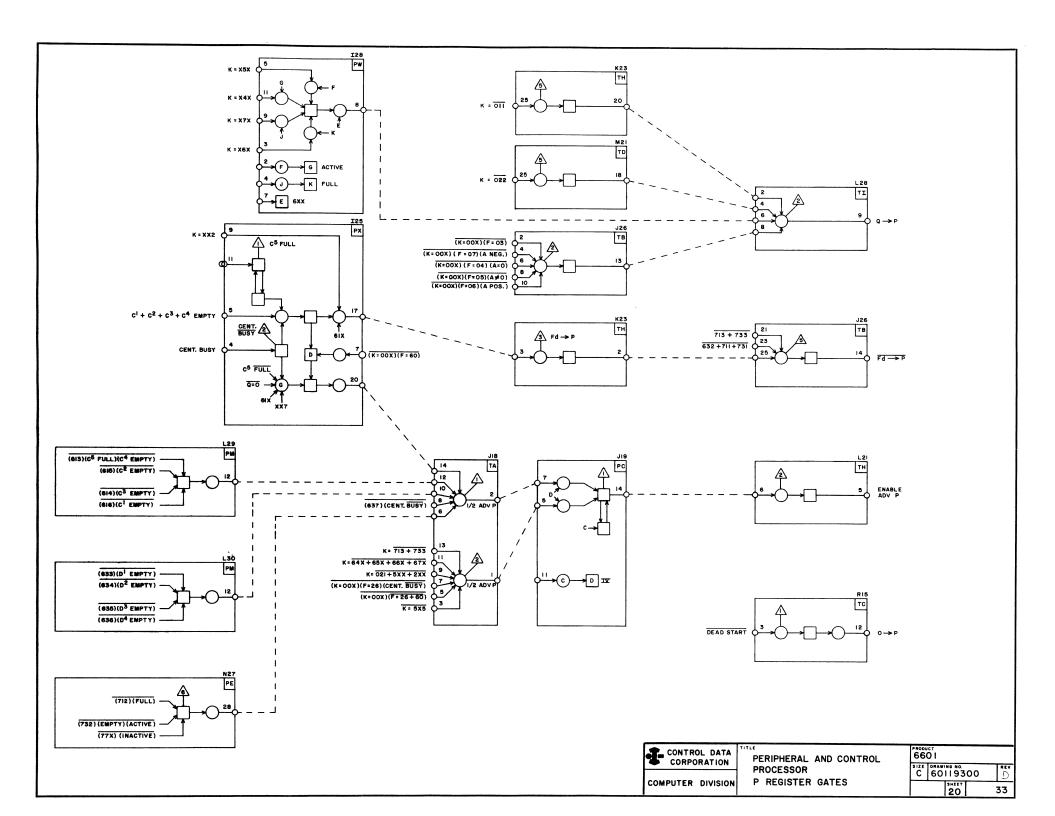

| 33         | P Register Gates                                             |            | * 1                                               |

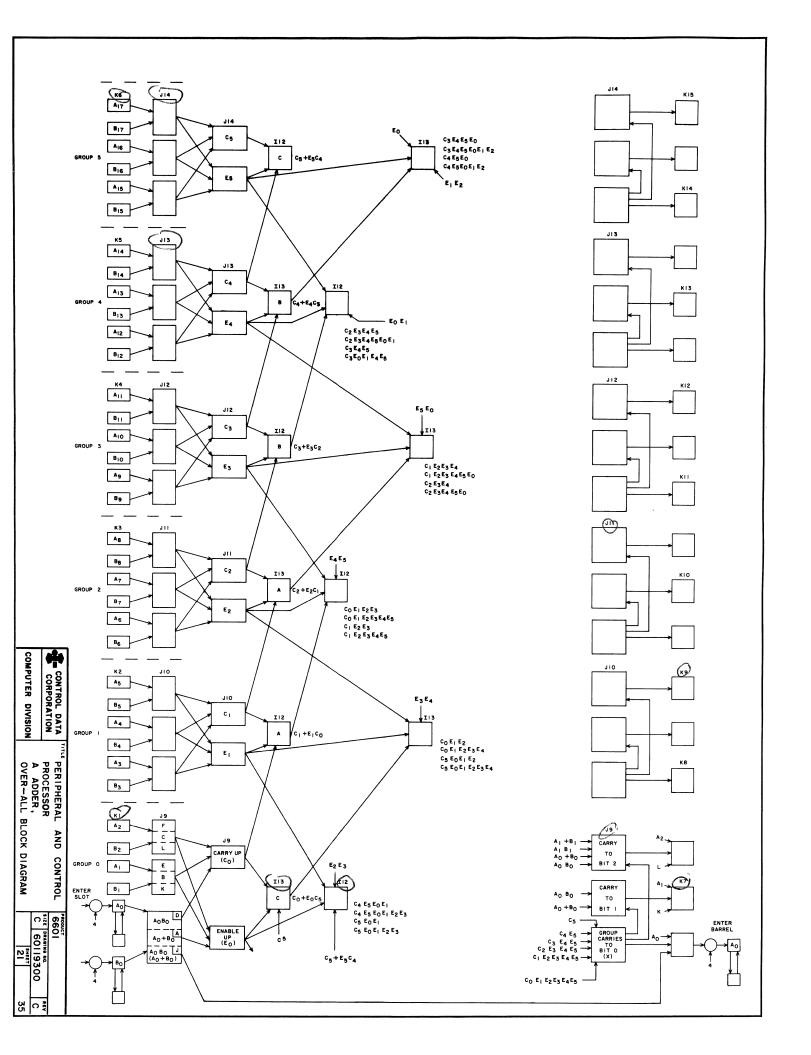

| 35         | A Adder, Overall Block Diagram                               |            |                                                   |

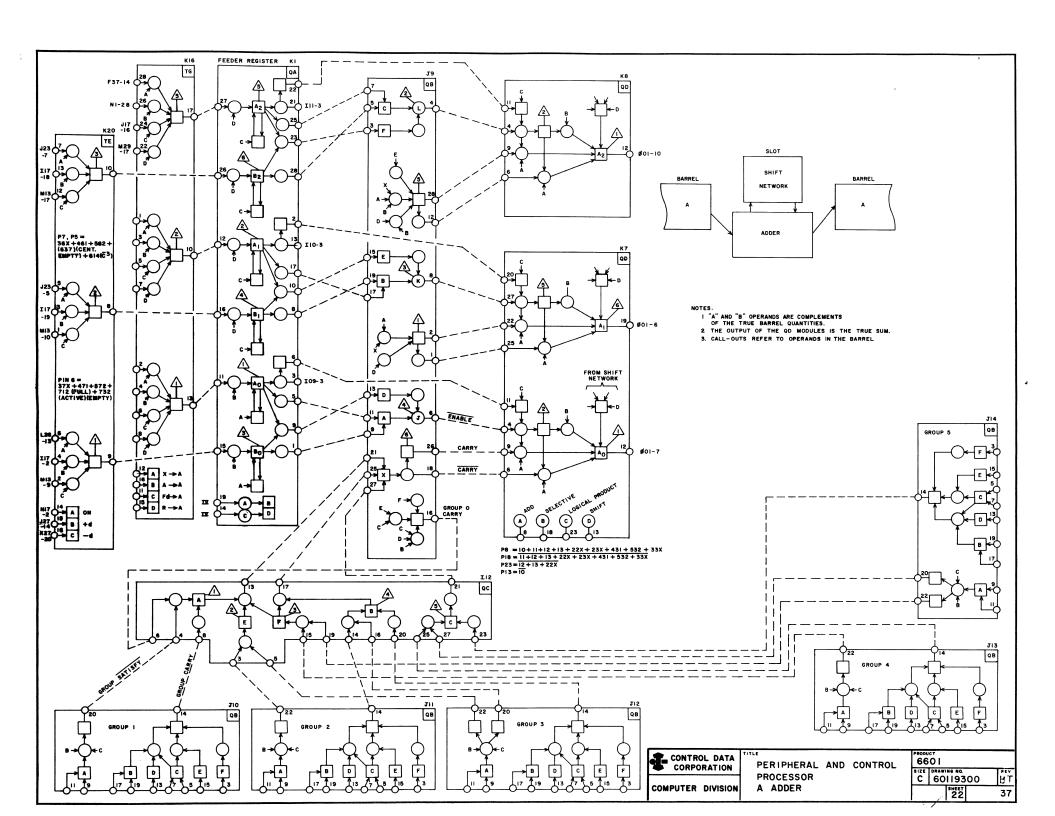

| 36         | A Adder                                                      |            |                                                   |

## PERIPHERAL AND CONTROL PROCESSORS

## INTRODUCTION

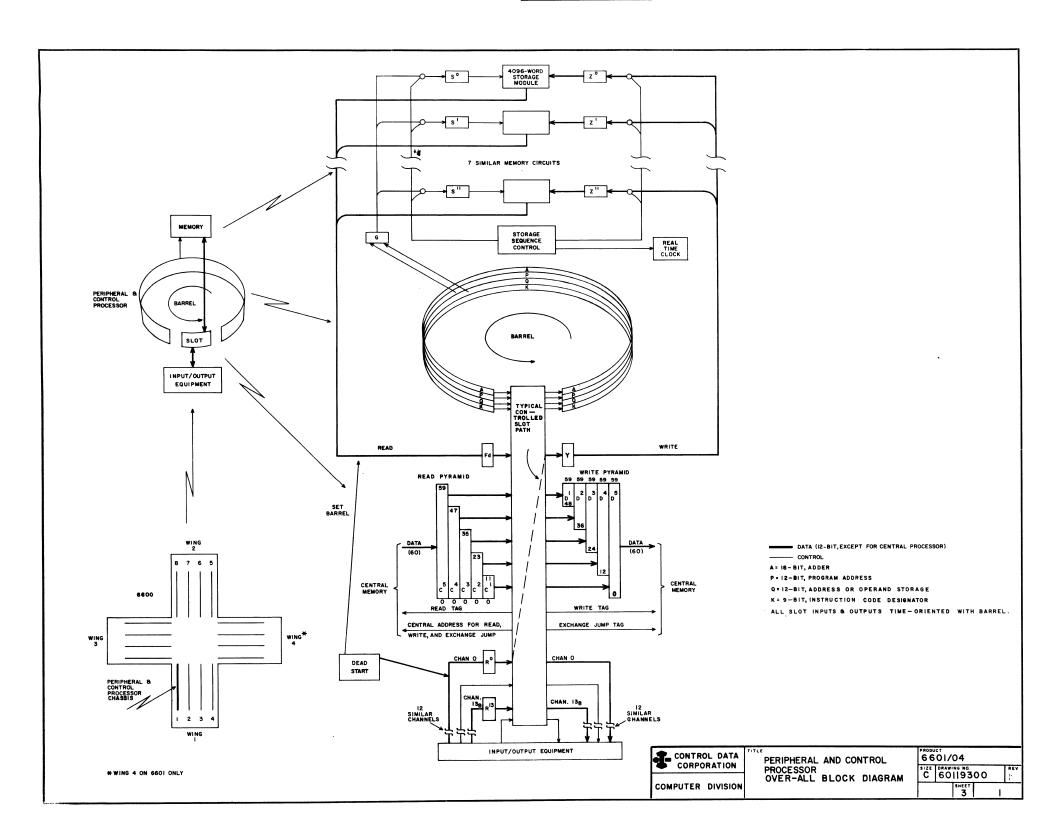

The CONTROL DATA 6601 Central Computer consists of ten peripheral and control processors, a central processor, central memory, and peripheral equipment controllers. Each peripheral and control processor is an independent computer with 4096 words of core storage and a repertoire of 64 instructions. The peripheral and control processors share access to central memory and to 12 bi-directional input-output channels.

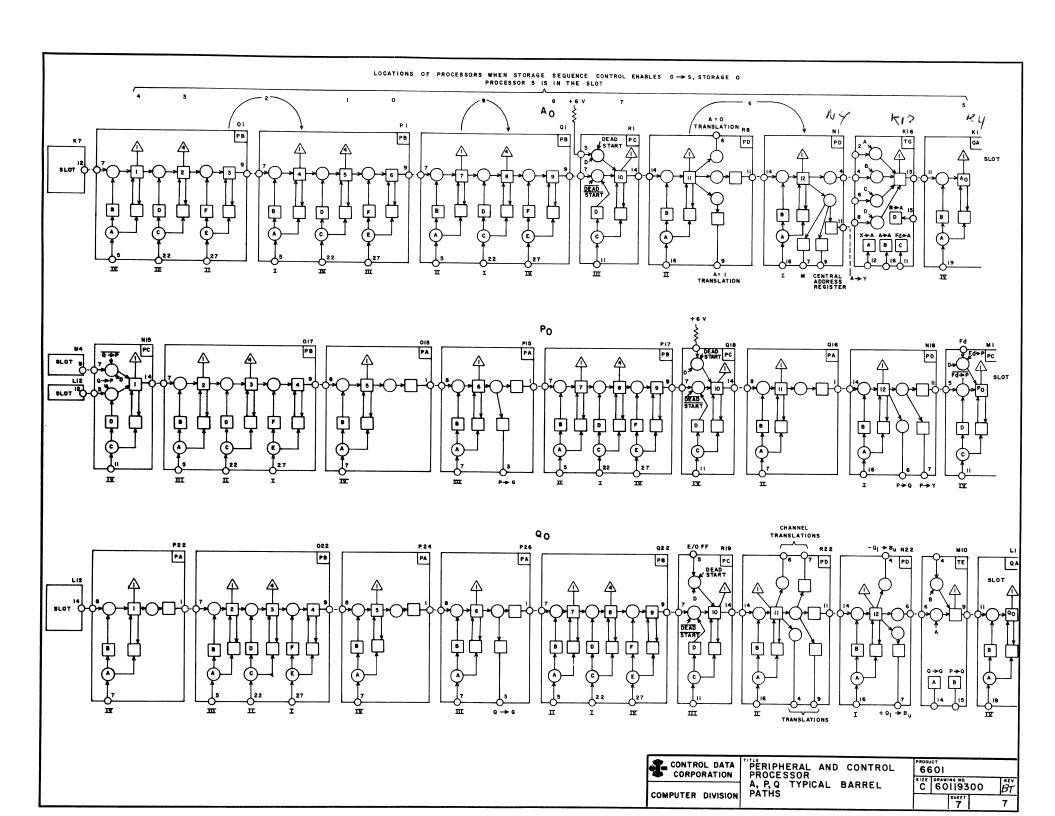

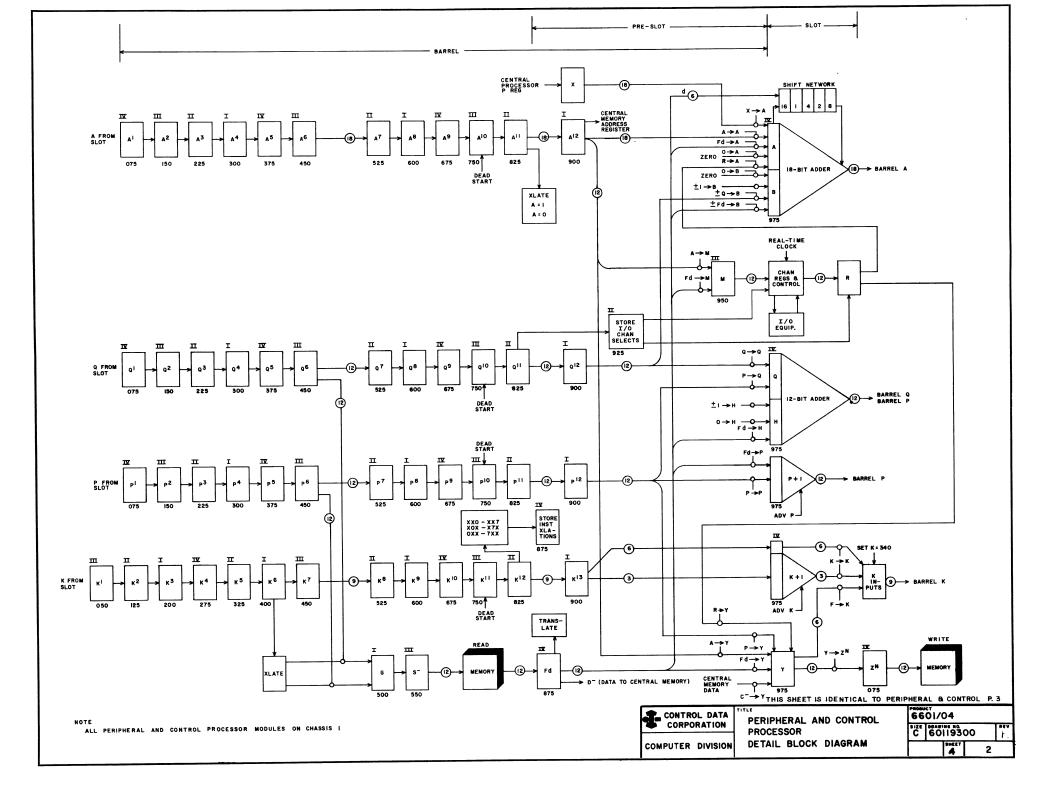

The ten peripheral and control processors are combined in a multiplexing arrangement which allows them to share common hardware for arithmetic, logical, I/O, and other operations without sacrificing speed or independence. This multiplexing arrangement consists of the barrel, the slot, and common paths to storage and I/O channels.

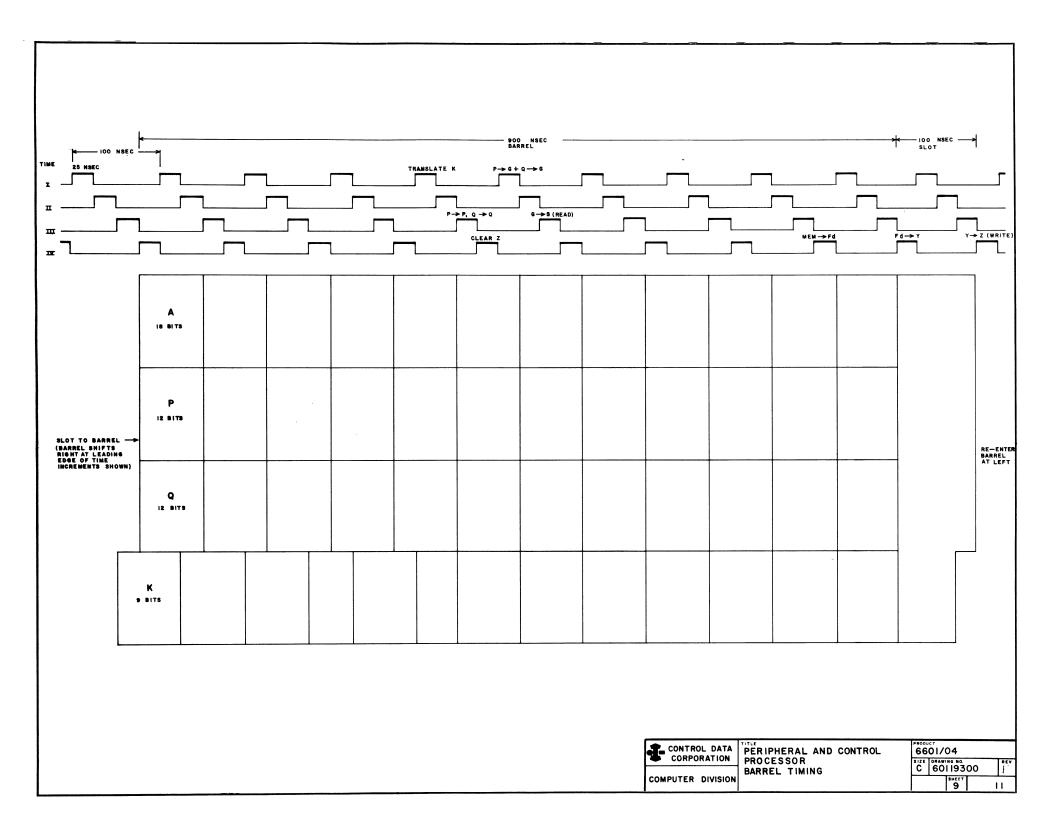

The barrel is a matrix of FFs used to hold the quantities in the operating registers of the ten processors and to give each a turn to use the execution hardware in the slot (adders, shift network, etc.). The quantities in the barrel are shifted from slot output to slot input. Each time a processor's data enters the slot, a portion of the instruction is executed. A trip around the barrel requires 1000 nsec (one major cycle), of which each processor's data spends 900 nsec in the barrel and 100 nsec in the slot, Each processor has its own independent 4096 word memory which may be referenced once each major cycle (once each trip around the barrel).

The peripheral and control processors read data from input devices, perform preliminary arithmetic and logical operations, send data and programs to central memory, assign tasks to the central processor, read central processor results from central memory, and send results to external storage (magnetic tape, disc file, etc.) or to output devices (line printer, display console, etc.).

## Characteristics of the peripheral and control processors are:

- -- 4096 word magnetic core storage (12-bits) Random access, coincident current Major cycle - 1000 ns Minor cycle - 100 ns

- -- 12 bi-directional input-output channels

All channels available to all processors

Maximum transfer rate per channel one word/major cycle.

- -- Real-time clock (period 4096 major cycles)

- -- Instructions

Arithmetic

Logical

Input-output

Central memory read/write

Exchange jump

- -- Average instruction execution time two major cycles

- -- Indirect addressing

- -- Indexed addressing

Pub. No. 60119300

Rev. C

Peripheral and Control Processors

## **EQUATION LISTS**

#### P Register and P Incrementer K Register P Incr. $\rightarrow$ P= $\overline{Q} \rightarrow \overline{P}$ 2XX+(70X.clock select)+(70X.full)+(72X.active.empty)+(74X K + K = Q Adder $\rightarrow$ P=011+022+(64X.active)+(65X.inactive)+(66X.full)+(67X.empty)+ inactive)+(75X.active)+(76X.inactive)+3XX+4X1+5X2+011+022 $(03+(04. A=0)+(05. A=\overline{0})+(06. A pos)+(07. A neg)).(K=00X)$ +64X+65X+66X+67X+713+733+604+(624) (central busy)+(77X (K=00X). $(\overline{26+60})+5X5+(26. central \ \overline{busy}. K=00X)+021+5XX+2XX+$ $64X+65X+66X+67X+713+733+(637.central\ \overline{busy})+(617.Q\neq0.central\ \overline{busy})$ 340 → K = 35X+36X+37X+451+461+471+552+562+572 $\overline{\mathrm{busy}}.\,\overline{\mathrm{C}}^{5}) + 613.\,\overline{\mathrm{C}}^{4}.\,\mathrm{C}^{5} + 614.\,\overline{\mathrm{C}}^{3} + 615.\,\overline{\mathrm{C}}^{2} + 616.\,\overline{\mathrm{C}}^{1} + 633.\,\overline{\mathrm{D}}^{1} + 634.\,\overline{\mathrm{D}}^{2} + 635.\,\overline{\mathrm{D}}^{3} + 634.\,\overline{\mathrm{D}}^{2} + 634.\,\overline{\mathrm{D}^{2} + 634.\,\overline{\mathrm{D}}^{2} + 634.\,\overline{\mathrm{D}^{2} + 634.\,\overline{\mathrm{D}}^{2} + 634.\,\overline{\mathrm{D}}^{2} + 634.\,\overline{\mathrm{D}}^{2} + 634.\,\overline{\mathrm{D}^{2} + 634.\,\overline{\mathrm{D}}^{2} + 634.\,\overline{\mathrm{D}^{2} + 634.\,\overline{\mathrm{D}^{2}$ F → K = 01+02+20+21+22+23+3X+4X+5X+(F $^5$ , $\overline{60}$ )+(60, central $\overline{busv}$ $\overline{C}^5$ ( $\overline{C}^1$ : 636. $\overline{D}^4$ +712. full +(732, empty, active)+(77X mactive)+central busy. $\overline{C}^5$ . $\overline{C}^{2}+\overline{C}^{3}+\overline{C}^{4})$ $(\bar{C}^1 + \bar{C}^2 + \bar{C}^3 + \bar{C}^4)$ . (K=00X). (F=60) 712 → K = load. dead start (clock=7777) Fd → P = 612. central $\overline{\text{busy}}$ . $\overline{C}^5$ . $(\overline{C}^1 + \overline{C}^2 + \overline{C}^3 + \overline{C}^4) + 632 + 711 + 731 + 733 + 713$ 732 → K = dump.dead start. (clock=7777) Zero → P = dead start. (clock=7777) 505 → K = sweep. dead start. (clock= 7777) Adv K = $010 + 020 + 610 + 630 + \ \mathbf{021} + 5\mathbf{X1} + 4\mathbf{X0} + 5\mathbf{X0} + 632 + 711 + 731 +$ A Register and A Adder ( (712+732). 112+732). 112+631+710+730+((01+02+5X). 112+631+710+730+((01+02+5X)). $(600, \mathbb{C}^5 \ \overline{\mathbb{C}}^4) + (601 \ \overline{\mathbb{C}}^3) + (602, \overline{\mathbb{C}}^2) + (603, \overline{\mathbb{C}}^1) + (613, \overline{\mathbb{C}}^4 \ \mathbb{C}^5) + (614 \ \overline{\mathbb{C}}^3) + (613, \overline{\mathbb{C}}^4 \ \mathbb{C}^5) + (614 \ \overline{\mathbb{C}}^3) + (613, \overline{\mathbb{C}}^4 \ \mathbb{C}^5) + (613, \overline{\mathbb{C}}^4 \ \mathbb{C}^4) + (613, \overline{\mathbb{C}}^4 \ \mathbb{C}^4) + (613, \overline{\mathbb{C}}^4 \ \mathbb{C}^4) + (613, \overline{\mathbb{C}}^$ $10000_{8} \rightarrow A = dead start$ . (clock=7777) $X \rightarrow A = 27$ (K=00X) $\scriptstyle{(615.\,\overline{C}^2)+(616.\,\overline{C}^1)+(620.\,\overline{D}^1)+(621\,\,\overline{D}^2)+(622.\,\overline{D}^3)+(623.\,\overline{D}^4)+}$ $(633, \overline{D}^1)+(634, \overline{D}^2)+(635, \overline{D}^3)+(636, \overline{D}^4)+(712 \text{ full. } A=1)+(732)$ Fd = A = 37X+471+572+36X+461+562empty. A=1)+(612. central $\overline{busy}$ $\overline{C}^5$ ( $\overline{C}^1+\overline{C}^2+\overline{C}^3+\overline{C}^4$ ) ) $A \to A = \overline{14X + 15X + 20X + 27X + 30X + 36X + 37X + 401 + 461 + 471 + 502 + 562 + 572 + 70X}$ $Clr \ K^2$ 617. Q=0+617. central $\overline{\text{busy}}$ $\overline{\text{C}}^5$ . R + A = 70XQ=0+637. central busy Set $\kappa^6$ $+1 \rightarrow B_L = 36X+461+562+(637, central \overline{busy})+614.\overline{C}^3$ 617. Q=0+637. central busy Q=0 $-1 \Rightarrow B_{L}^{E} = 712$ , full + 37X+471+572+(732, active, empty) $+d \rightarrow B_L = 10+12+14+16+20X+21X+22X+31X+35X+411+451+552+30X+401+502$ $-d \rightarrow B_L = 11+13+15+17+23X+33X+431+532+32X+421+522$ $+F \rightarrow B_{M} = 20X + 21X + 22X + 30X + 31X + 35X + 401 + 411 + 451 + 502 + 512 + 552$ $-\mathbf{F} + \mathbf{B}_{\mathbf{M}} = 23X+33X+431+532+32X+421+522$ $00 \rightarrow B_{\overline{M}}^{=} 10+12+14+16+36X+461+562+(614, \overline{C}^3)+(637, central \overline{busy})$ A Adder Control $16 + (614.\overline{C}^3) + (637.central \overline{busv})$ Add = $10 \cdot 11 \cdot 12 + 13 + 22 \times +23 \times +33 \times +431 +532$ Selective = 11+12+13+22X+23X+33X+431+532 $+Q_L = B_U = 20X + 21X + 22X$ Logical Prod. = 12+13+22X -QL + BU = 23X Shift = 10 Q Adder Controls $Q_{L}^{\to Q} \text{ Adder} = \overline{010+020+4X0+5X0+630+64X+65X+66X+67X+610+K=00X}$ Q Register and Q Adder P $\rightarrow$ Q Adder = (03 +04 +05. +06 +07 ) (K=00X) +1 $\rightarrow$ H<sub>L</sub> . H<sub>1</sub> = 022 +(60X, C<sup>5</sup>, $\overline{C}^4$ K=XX0)+(601, $\overline{C}^3$ )+602, $\overline{C}^2$ +603, $\overline{C}^1$ +620, $\overline{D}^1$ + 000 000 00X XXX $\rightarrow$ Q = dead start (clock=7777) = dead start (clock=7777) $621 \ \overline{D}^2 + 622. \overline{D}^3 + 623. \overline{D}^4$ Minor cycle 8+9+4+5 $\mathsf{d} \to \mathsf{H}_{L} = 0.0 \times (010 + 020 + 021 + 011 + 4 \times 0 + 5 \times 0 + 5 \times 1 + 2 \times 3 + 64 \times + 65 \times + 66 \times + 67 \times + 68 \times 1 + 10 \times 1 +$ $1 \rightarrow Q^2$ = dead start (clock=7777) 610 - 630 Minor cycle 6+7+8+9 $\mathbf{F} \stackrel{\rightarrow}{\rightarrow} \mathbf{H}_{\xi} = 011 \cdot 021 \cdot 5 \times 1 + 2 \times \times + 010 + 020 + 610 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 4 \times 0 + 630 + 64 \times + 65 \times + 66 \times + 67 \times + 60 \times + 630 + 64 \times + 65 \times + 66 \times + 60 \times + 60$ = dead start (clock= 7777) 5 \ 0 $\begin{array}{c} -1 \stackrel{+}{\to} H_{L} = \underbrace{615, \overline{C}^2}_{+005}, \underbrace{\overline{D}^3}_{-000} \\ (0.03 + 0.04 + 0.5 + 0.6 + 0.7), \underbrace{d^5}_{-000}) (K = 0.0X) \end{array}$ Minor cycle 0+1 $1 \rightarrow Q^{(i)}$ = dead start (clock=7777) Minor cycle 1:3+5+7+9 Q Adder → Q = Unconditional G Register $P \rightarrow G = (Q \rightarrow G) \cdot (713 + 733 + 710 + 730 + 611 + 631)$ $Q \triangleq G = 010 + 020 + 022 + 4 \times X + 610 + 630 + 60 \times + 62 \times + 3 \times 0 + 5 \times 0 + 5 \times 2$

Peripheral and Control Processors Pub. No. 60119300 Rev. K Page 2

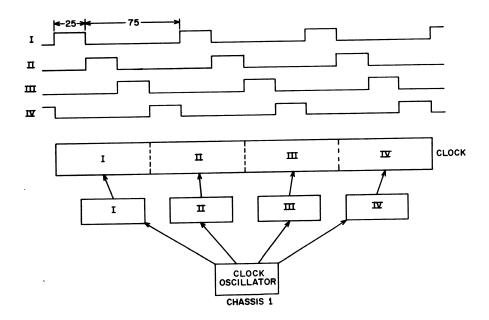

## TIMING

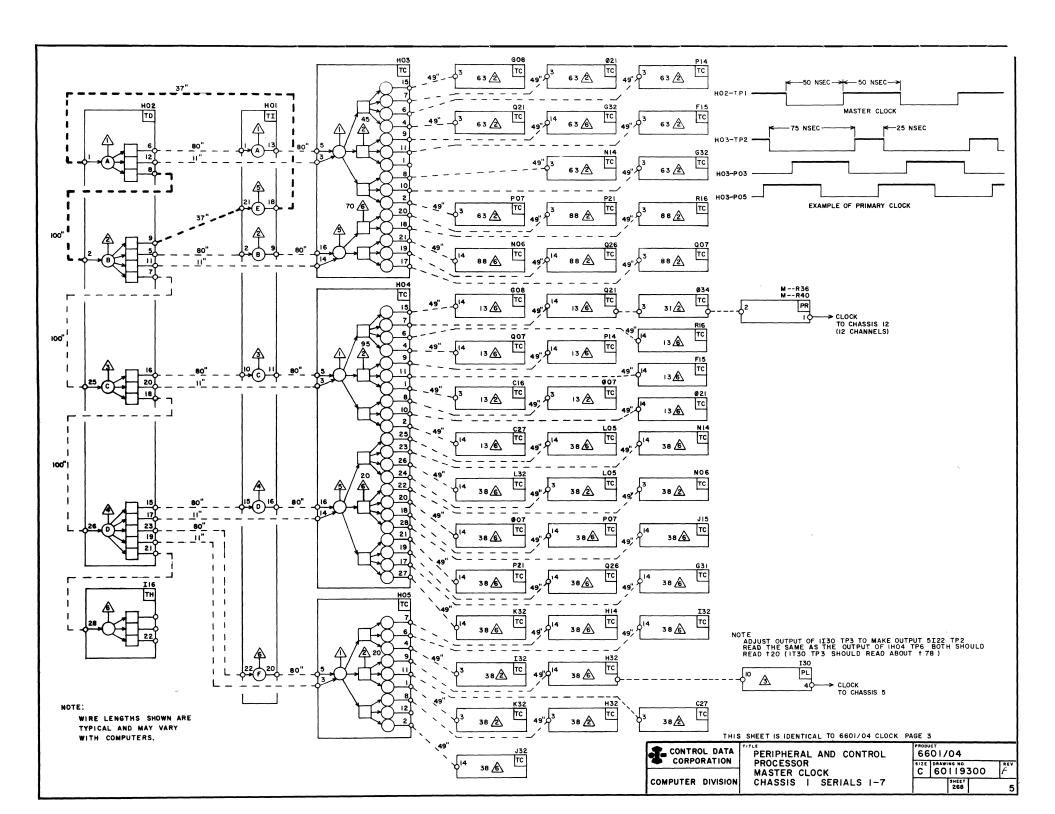

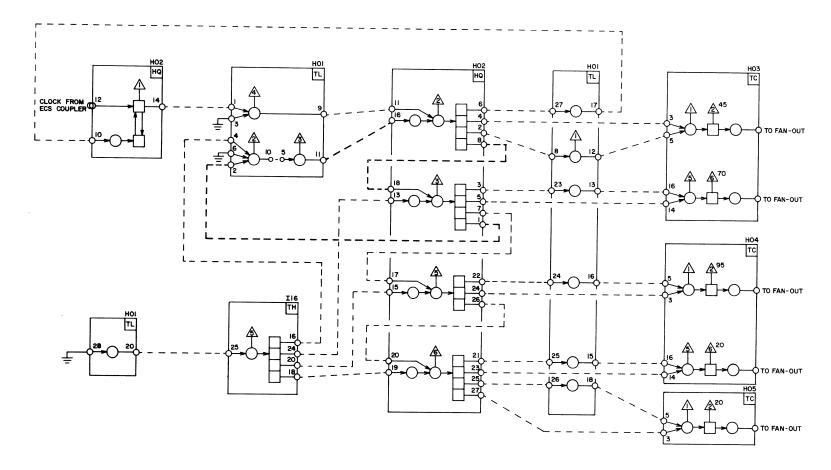

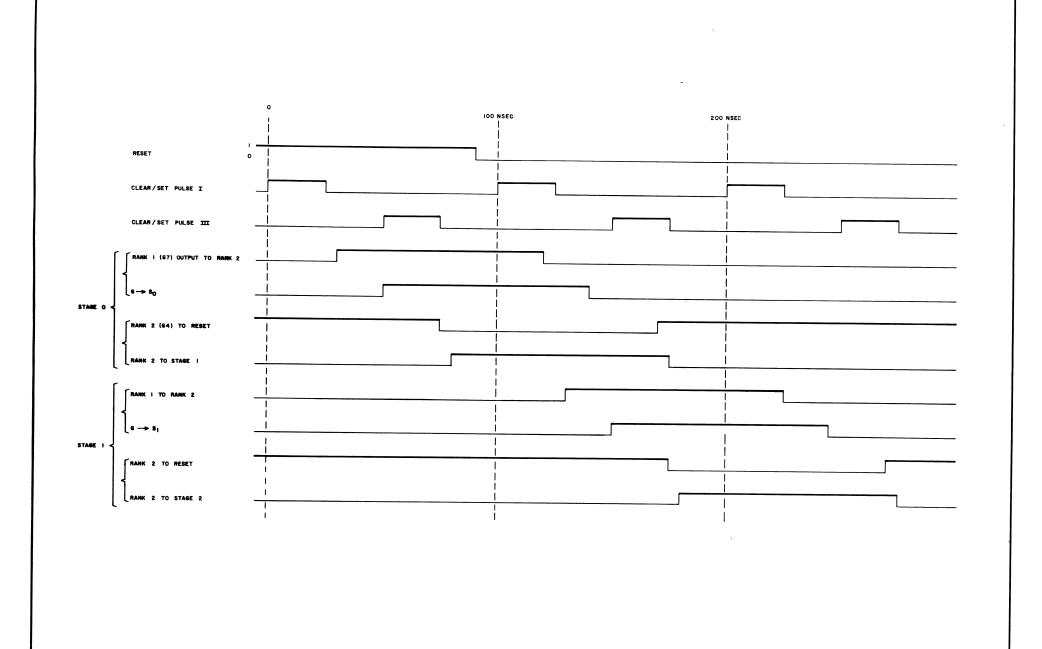

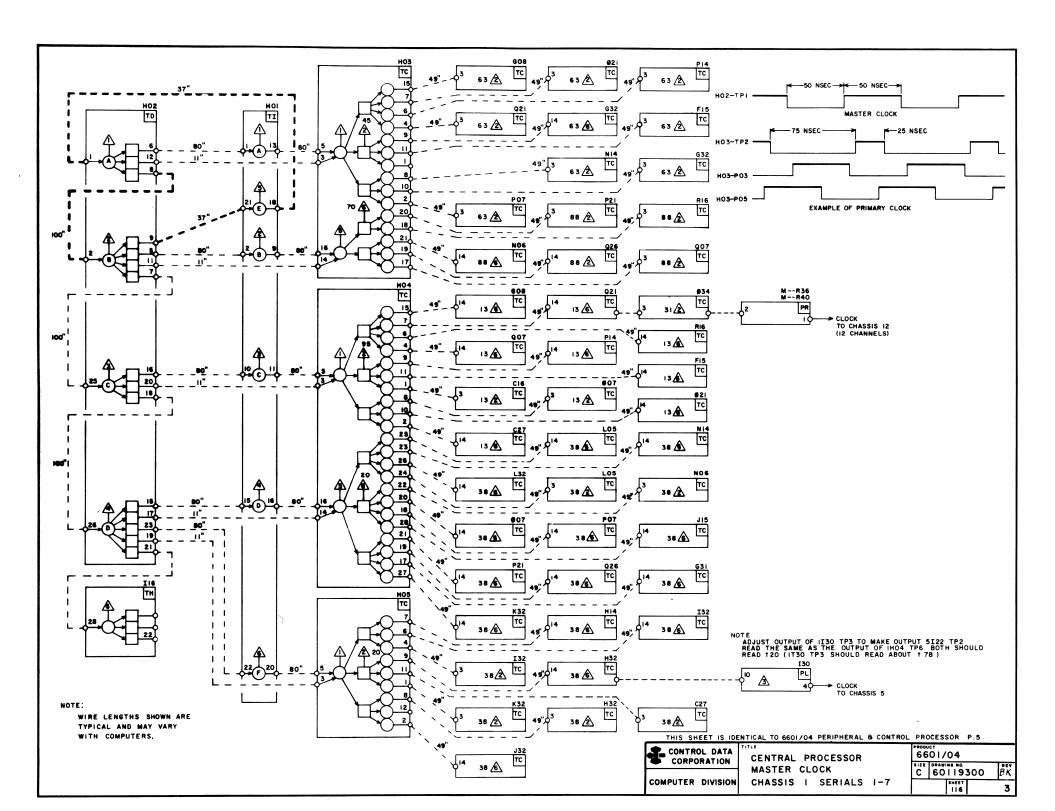

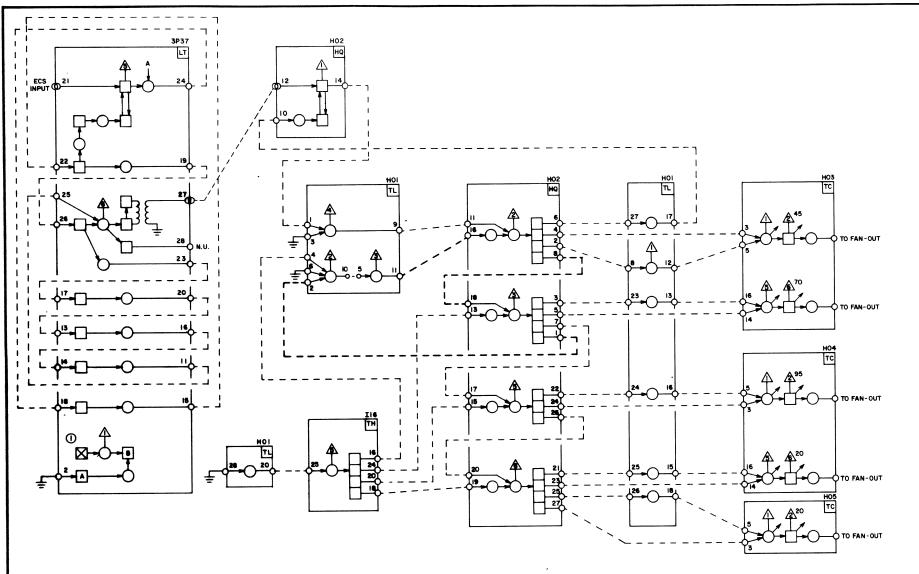

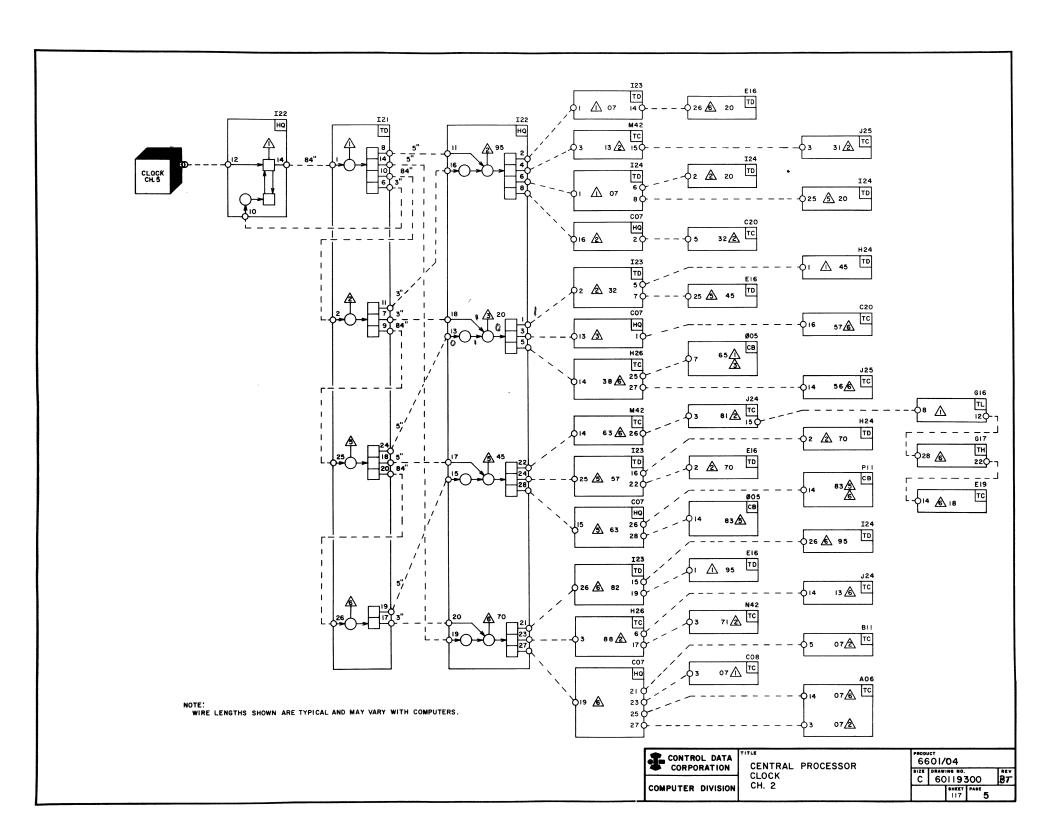

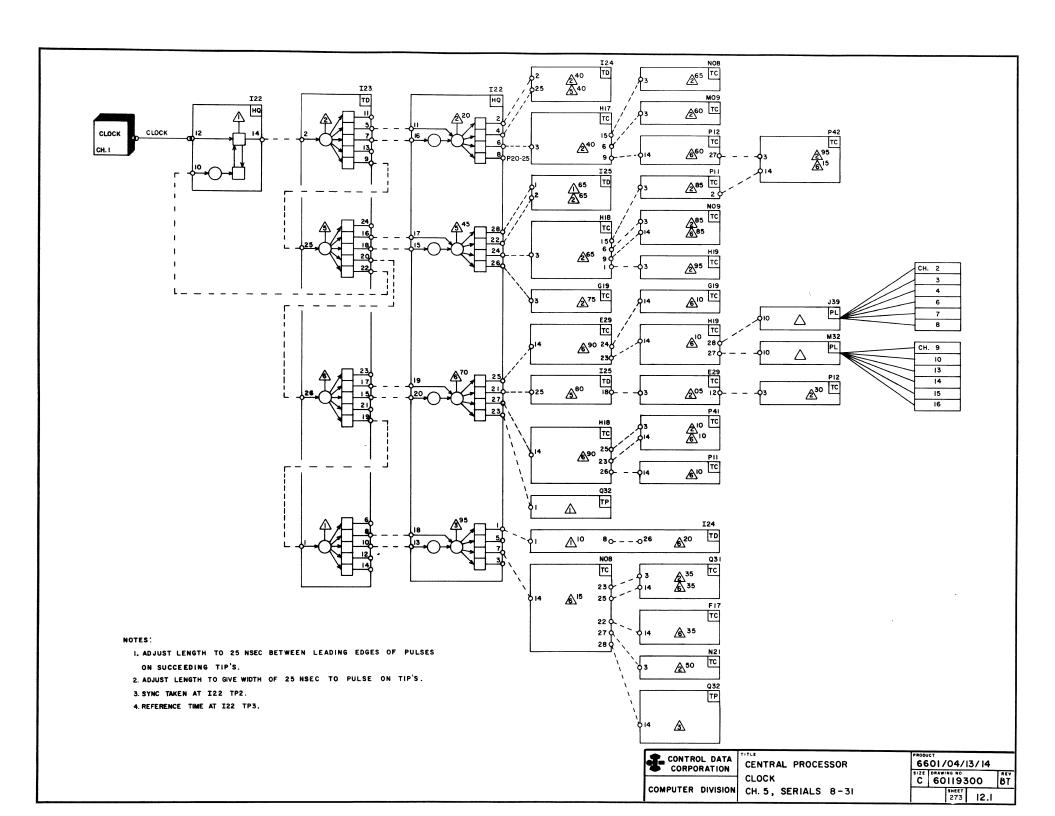

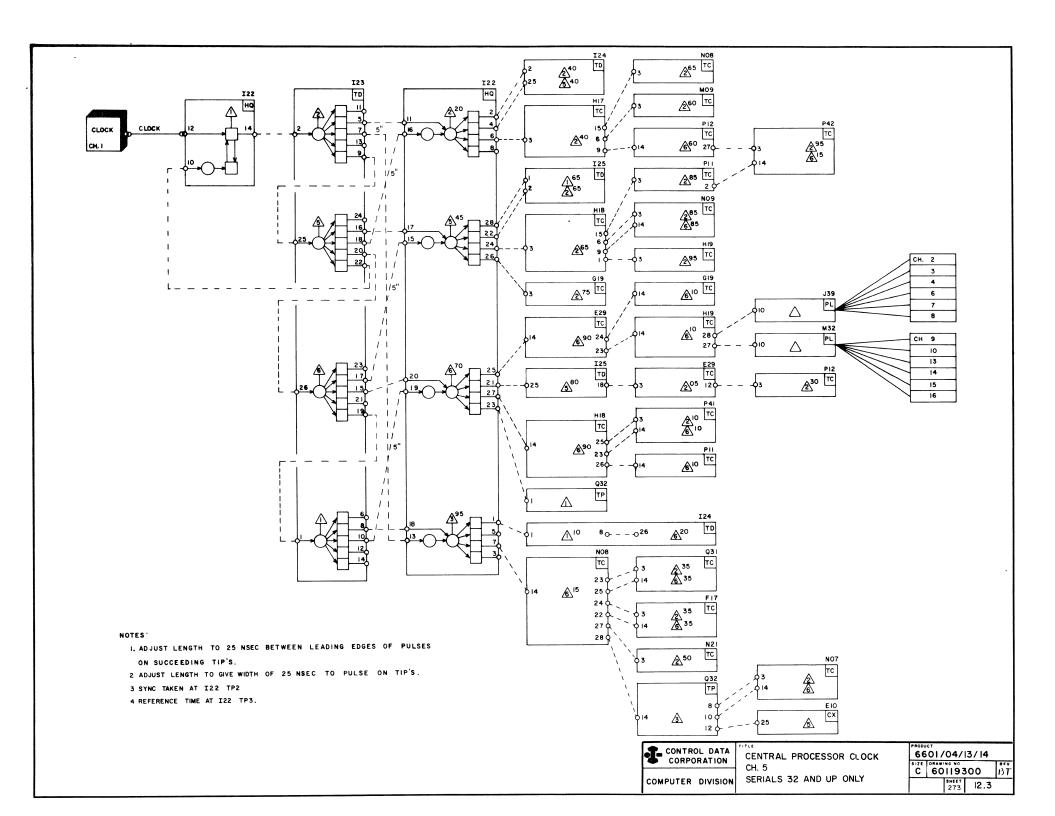

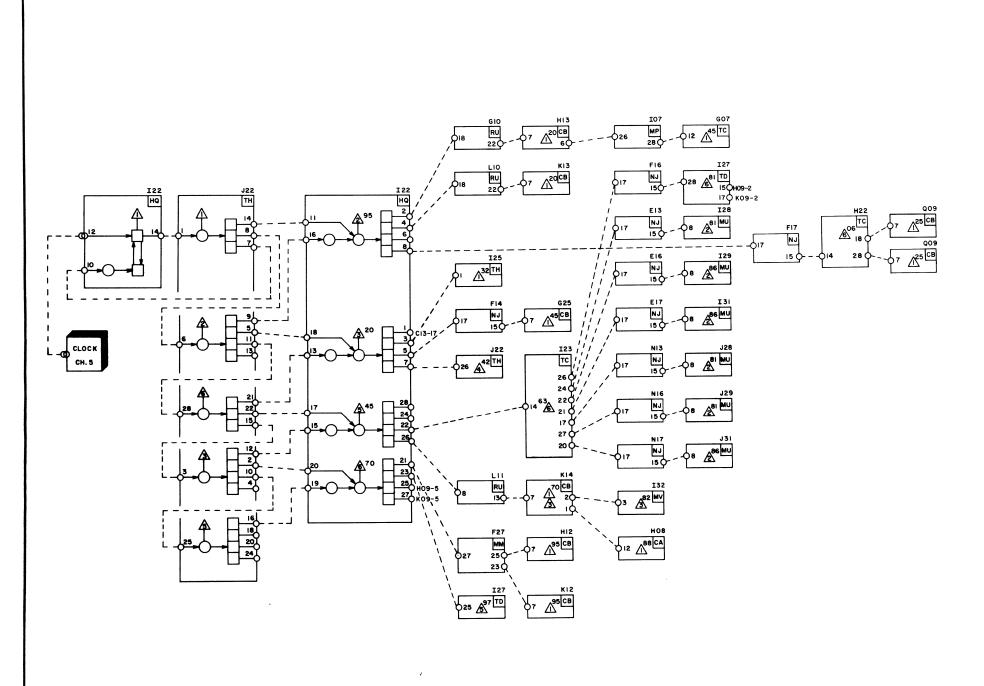

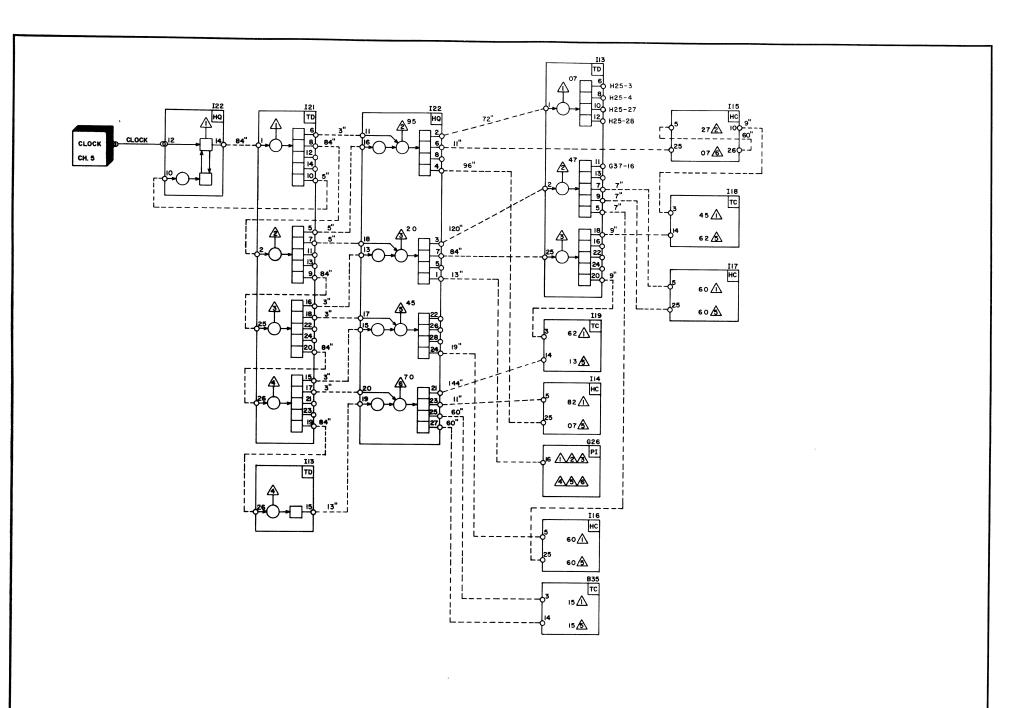

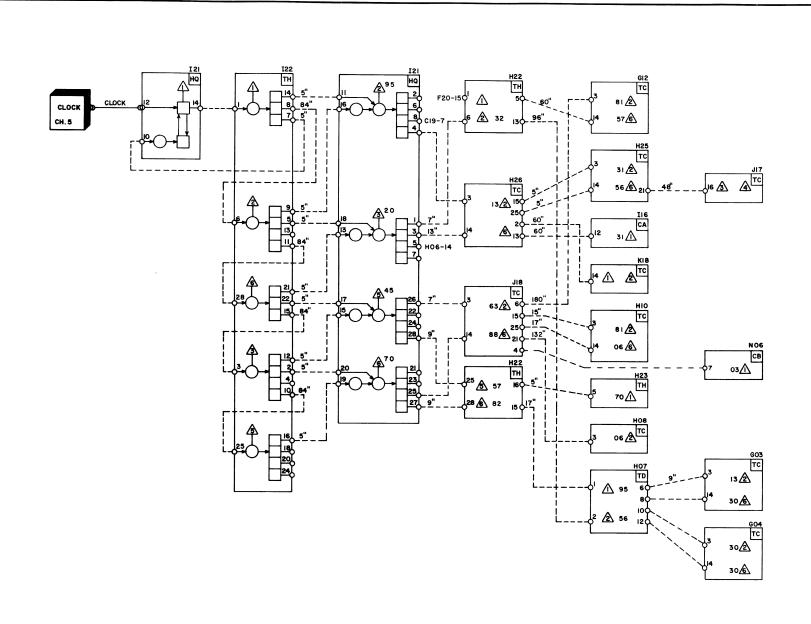

Timing in the 6600 is controlled by a four-phase master clock located on the peripheral and control processor chassis (chassis 1). Four 25 nsec pulses are issued each minor cycle to control movement of data and instructions. A storage sequence control system, timed by the four-phase clock, controls storage references and defines the ten peripheral and control processors.

## MASTER CLOCK

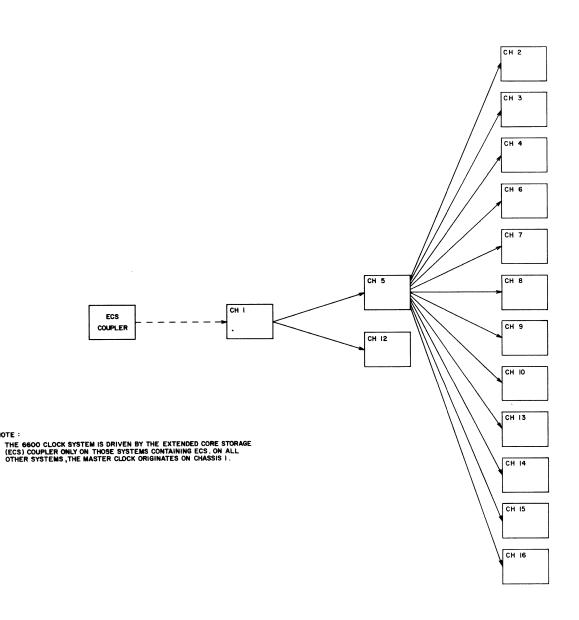

The master clock oscillator consists of a TD module and a TI module. To form the 25 usec clock pulses, a pulse from the TD is ANDed with a similar pulse which has been delayed and inverted by the TI. The result is a series of pulses (primary clock) which are fanned out through TC modules to be used as timing control. In addition to forming the clock pulses on chassis 1, the master clock sends pulses to chassis 5 and from there to all the other chassis. On each chassis, the incoming clock pulses are used to form a clock system similar to chassis 1. The clocks on all chassis are synchronized so that time 00 on any chassis is the same as time 00 on any other chassis.

NOTES:

I.TURN TO PAGE 5 FOR COMPLETE CLOCK FAN-OUT ON CHASSIS I.

THIS SHEET IS IDENTICAL TO 6601/04/13/14 CENTRAL PROCESSOR CLOCK P 4 1

| THIS SHEET IS IDENTICAL | TO 6601/04/13/14 CENTRAL PROCESSOR CLOCK | K,P. 4 I                 |

|-------------------------|------------------------------------------|--------------------------|

| CONTROL DATA            | PERIPHERAL AND CONTROL                   | PRODUCT<br>6601/04/13/14 |

| COMPUTER DIVISION       | MASTED CLOCK                             | C 60119300 B7            |

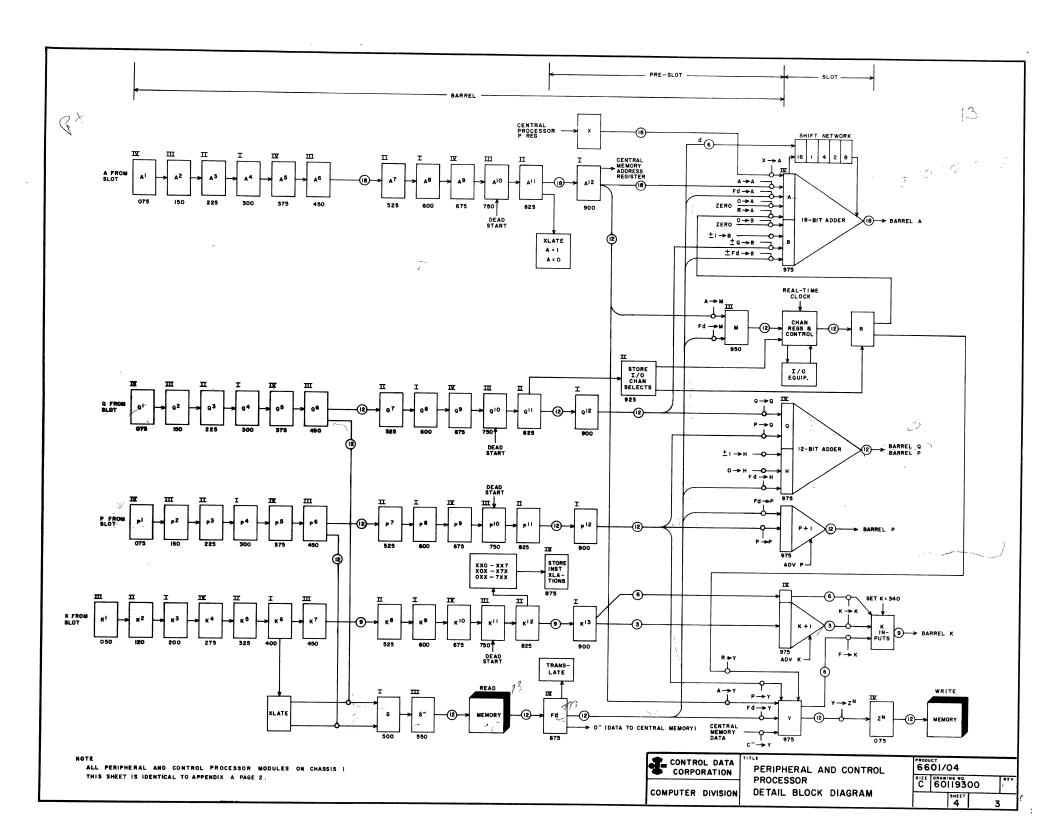

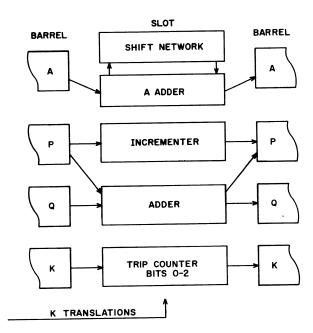

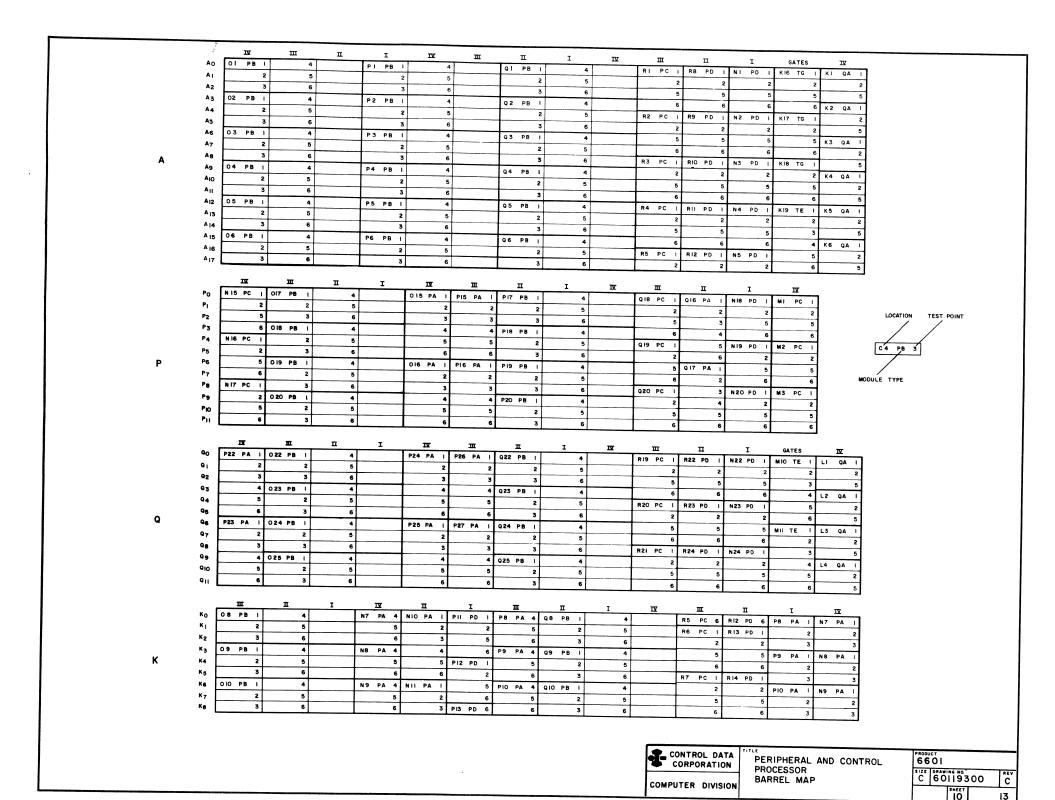

#### BARREL

The barrel contains the A, P, Q, and K registers for each of the ten processors. The functions of these four registers in the barrel are:

| A (18 bits)                                 | A holds one operand for add, shift, logical and selective |  |

|---------------------------------------------|-----------------------------------------------------------|--|

|                                             | operations. The 18-bit quantity in A may be an arith-     |  |

| metic operand, central memory address, or a |                                                           |  |

|                                             | function or data word.                                    |  |

- P (12 bits) P is the program address register. (P) is also used as a data address in certain I/O and central instructions.

- Q (12 bits) Q holds the d portion of instructions or may hold a data word when d is an address.

- K (9 bits) K holds the F portion of an instruction word and the trip count (the number of times an instruction has been around the barrel).

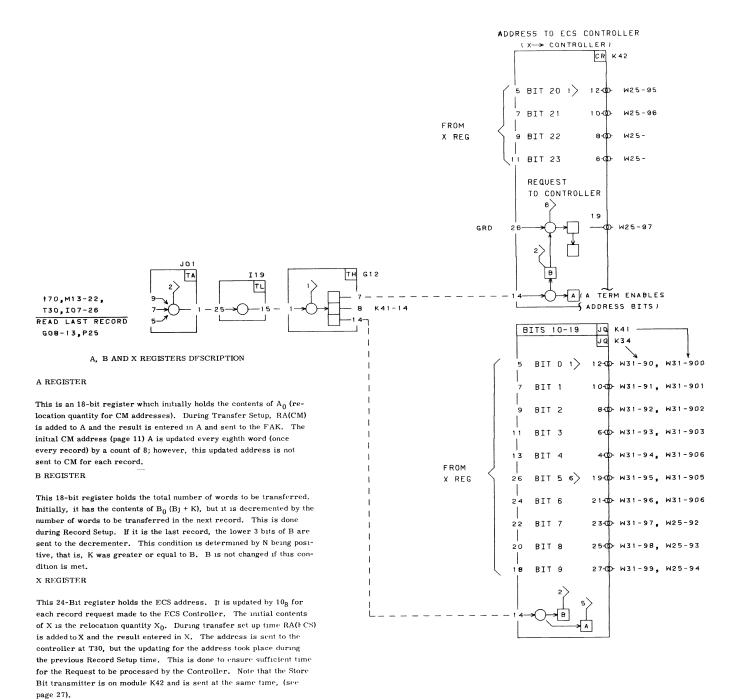

#### A REGISTER

The A register in the barrel receives the result of add, shift, logical or selective operations in the slot. This quantity may be stored, returned to the slot unaltered or used to condition other operations. A is always tested to determine its sign and whether it is zero, non-zero, or one. The result of these tests may be used to condition jump or other instructions. The quantity in A may be a full 18-bit central address or a 12-bit peripheral word (in which case the upper 6 bits will be zero).

The connections to A in the barrel are:

## Outputs

- A M (A) may be sent as a data or function word on one of the I/O channels.

- A → Central Address Register (A) is the central memory address in central read and write and exchange jump instructions.

Peripheral and Control Processors

- $A \rightarrow Y$  For a store instruction, (A) is sent to Y and then to storage.

- A → Translation Networks

## <u>Inputs</u>

- X + A The content of the central program address register is sent to the peripheral X register every minor cycle. A 27 instruction sends (X) to A and enables a peripheral and control processor to monitor the progress of the central program.

- $R \, \mbox{$\stackrel{\rightharpoonup}{\rightarrow}$} \, A \, \,$   $\,$  An input to A instruction gates a word from an I/O channel into A.

- Fd A A data word from storage is entered into A by the Fd A path.

- $A \rightarrow A$  When the quantity in A is to be returned to the slot unaltered, the  $A \rightarrow A$  gate is enabled.

## P REGISTER

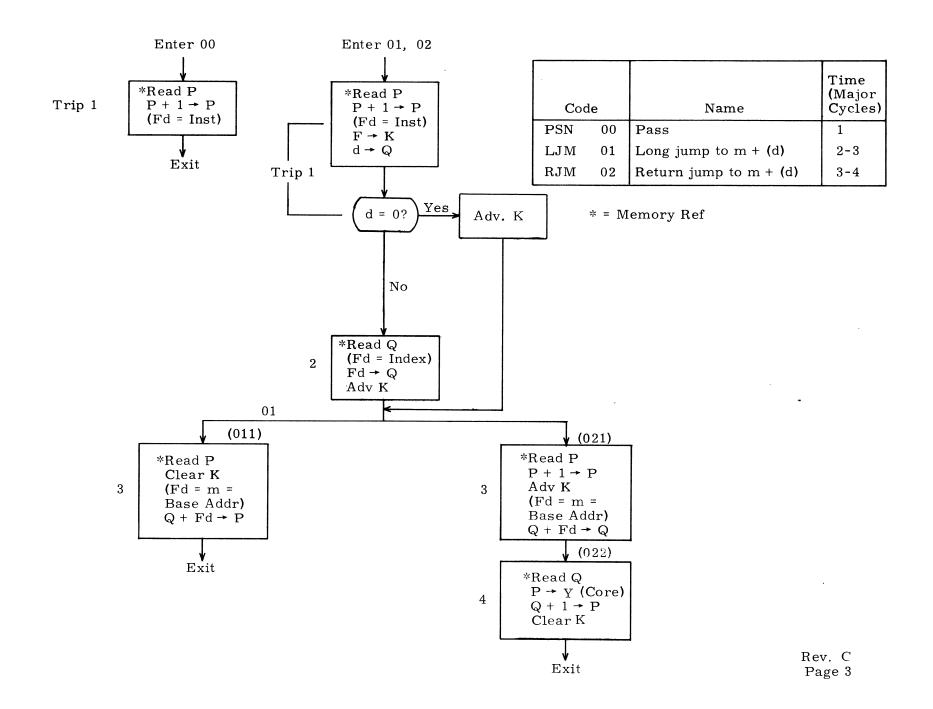

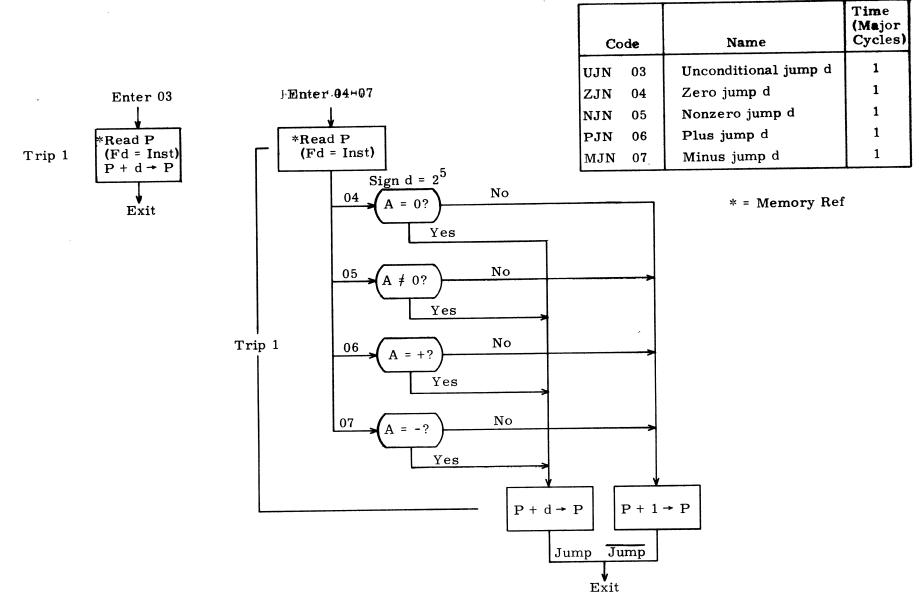

P holds the program address and is not changed in the barrel (except by Dead Start). (P) is sent to a storage unit from stage 6 in the barrel. This allows time to read a word from storage and make it available at slot time. (P) is sent to the G register which feeds all ten storage address or S registers. When a jump is called for, P is sent to Q from barrel stage 12. Q is then altered by the Q adder in the slot and the new address returned to P at the first stage of the barrel.

## Q REGISTER

Q holds the d portion of an instruction and has several outputs to translation networks which make channel selections for I/O instructions. When d is an address, (Q) is sent from the slot to P in the barrel and the word obtained from that address is entered into Q in the slot. When a jump is called for, the quantity in Q is added to or subtracted from (P) in the Q adder and the result sent to P. When an instruction calls for an 18-bit operand, the lower six bits of Q are sent to the upper six bits of A to form the 18-bit quantity dm.

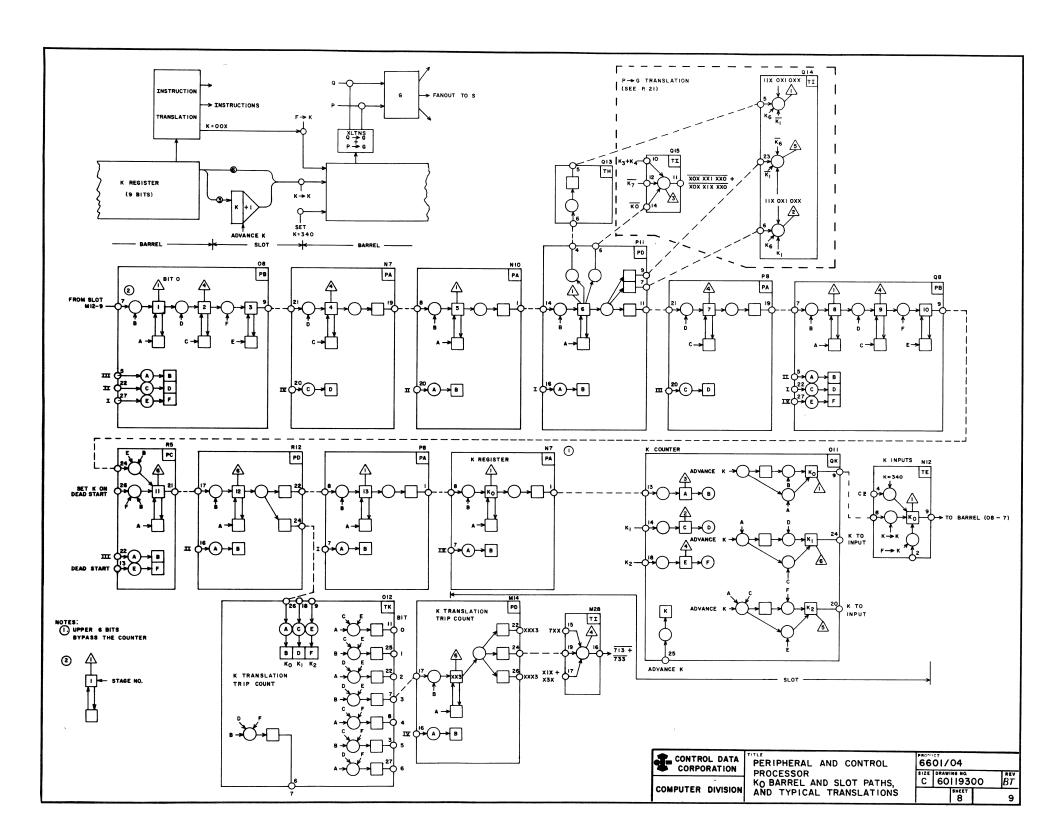

## K REGISTER

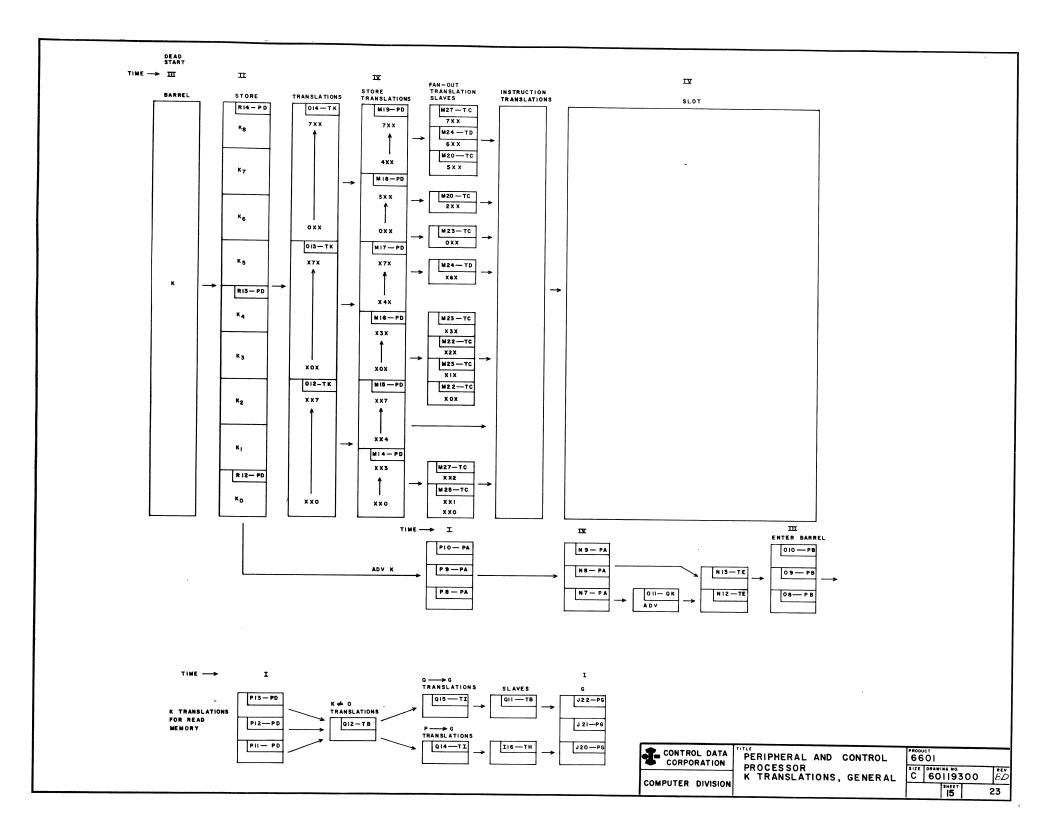

K holds the F portion of an instruction word and a 3-bit trip count which sequences the execution of an instruction. K is translated at two different times during a trip around the barrel; first, to determine if a storage reference is needed, and second, to provide the proper commands at the slot. During the barrel trip in which a new instruction is being read from storage, a translation of K = 00X enables

translations from Fd in the storage cycle path to be used in place of K translations. This eliminates the need for a separate "Read Next Instruction" trip through the barrel and allows certain instructions to be read from storage and executed all in one trip. The K = 00X translation arises from the fact that K is cleared at the end of each instruction.

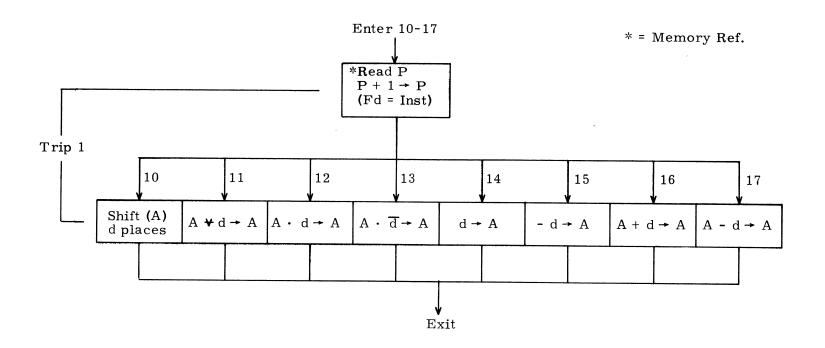

SLOT

The slot contains the execution hardware for A, P, Q, and K. Each processor is allowed one minor cycle in the slot every major cycle. Included in the slot are:

- A Adder

Shift Network

Logical Circuits

Selective Circuits

- P Incrementor Inputs from P or Q in the barrel

- Q Adder Input Path from Fd

- K 3-bit Trip Counter

Input from F

K = 340 Gate

As A, P, Q, and K enter the slot, K translations (started earlier in the barrel) become available and a portion (or all) of an instruction is executed. The results are gated back into the barrel to be stored, used again, or sent to I/O equipment.

Peripheral and Control Processors

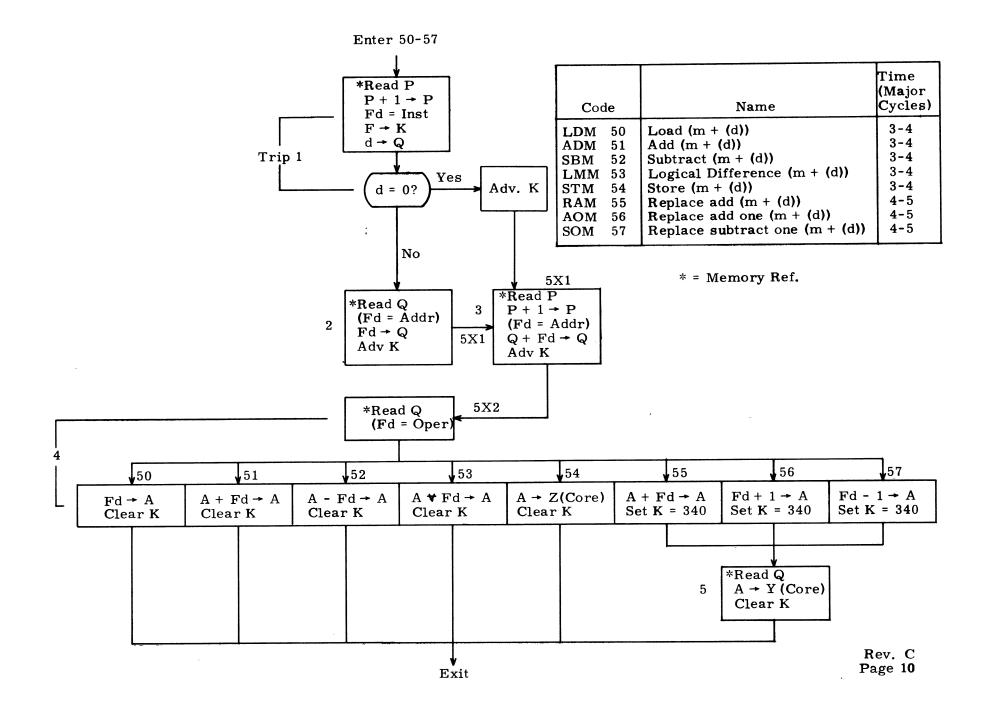

Pub. No. 60119300 Rev. C Page 10

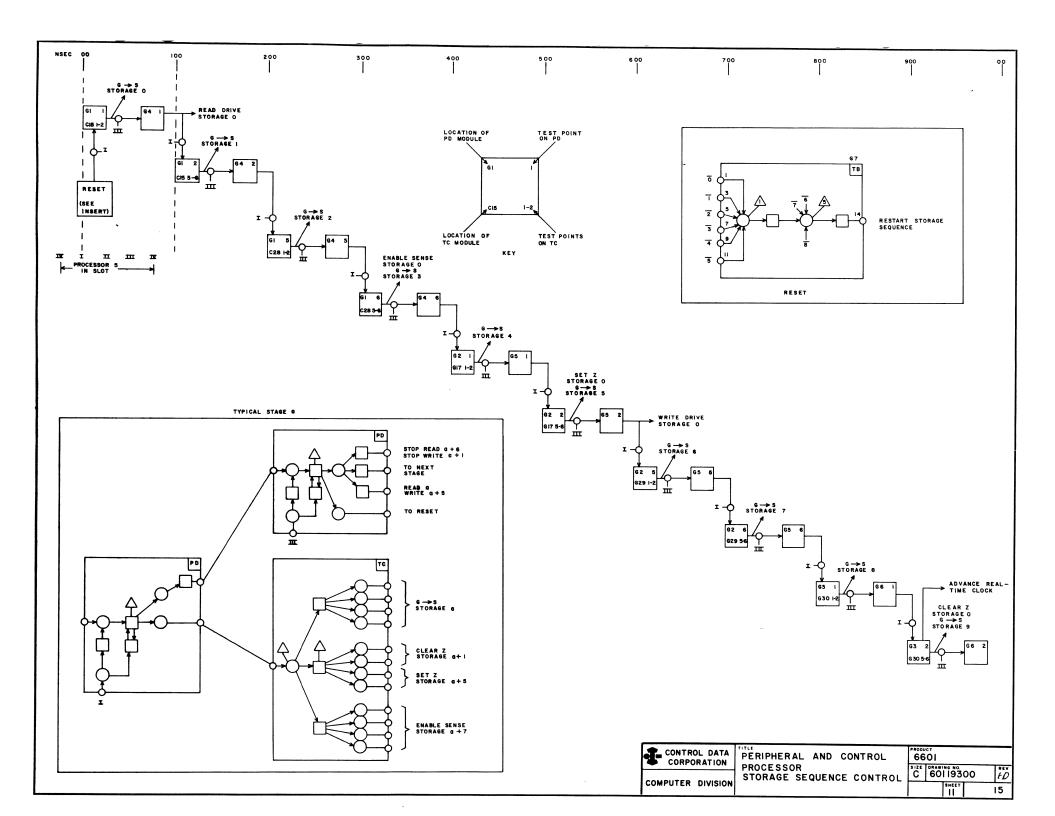

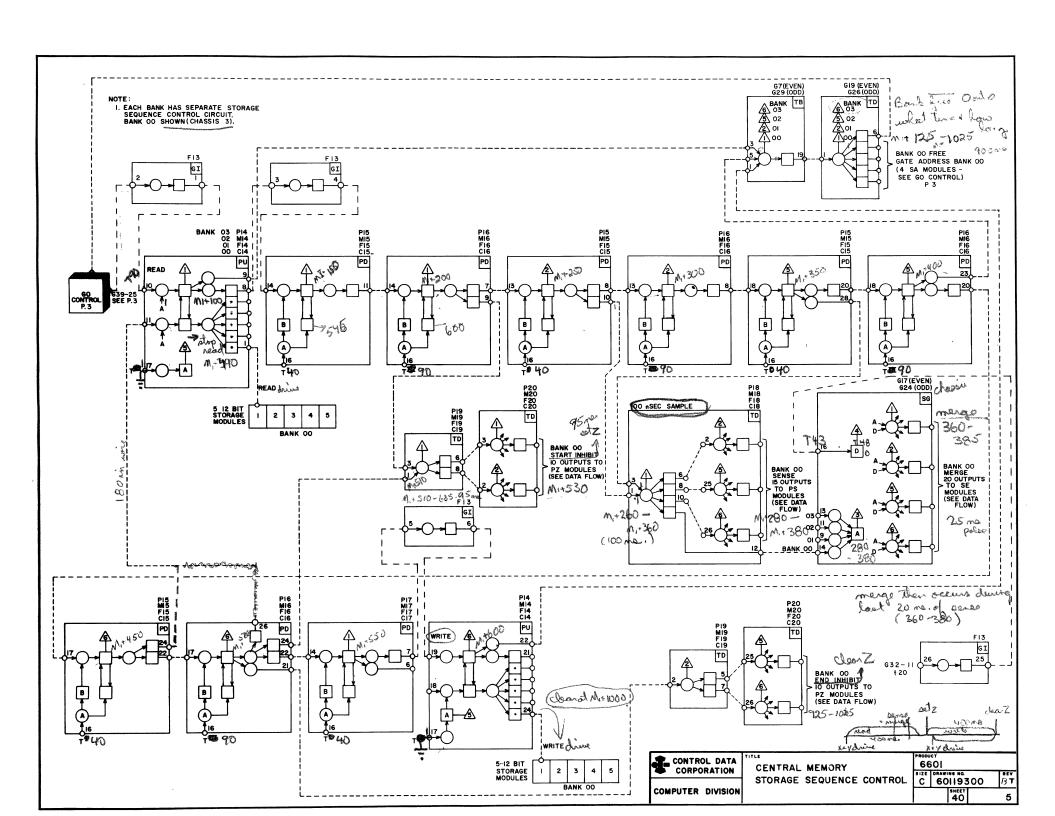

## STORAGE SEQUENCE CONTROL

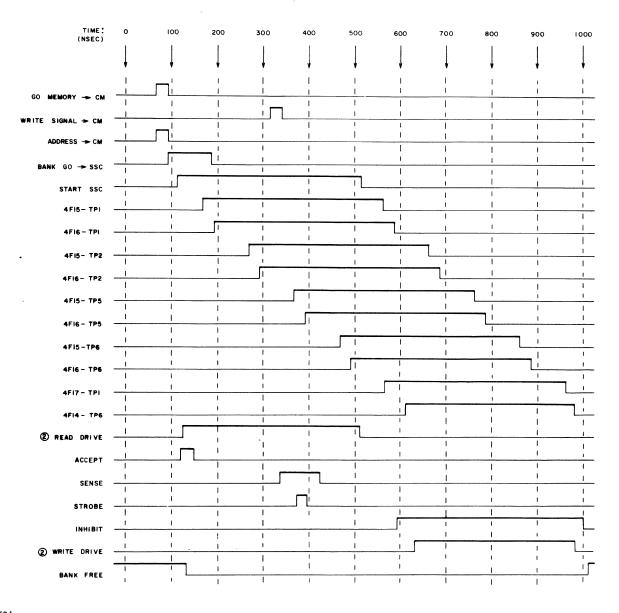

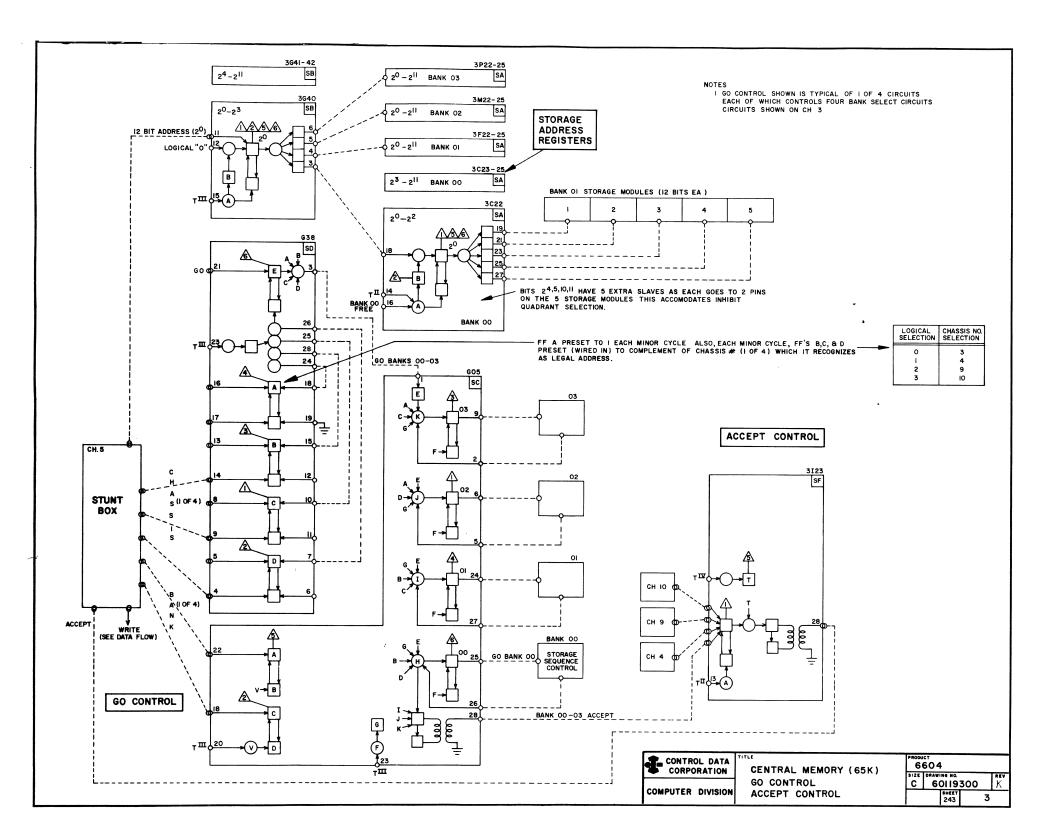

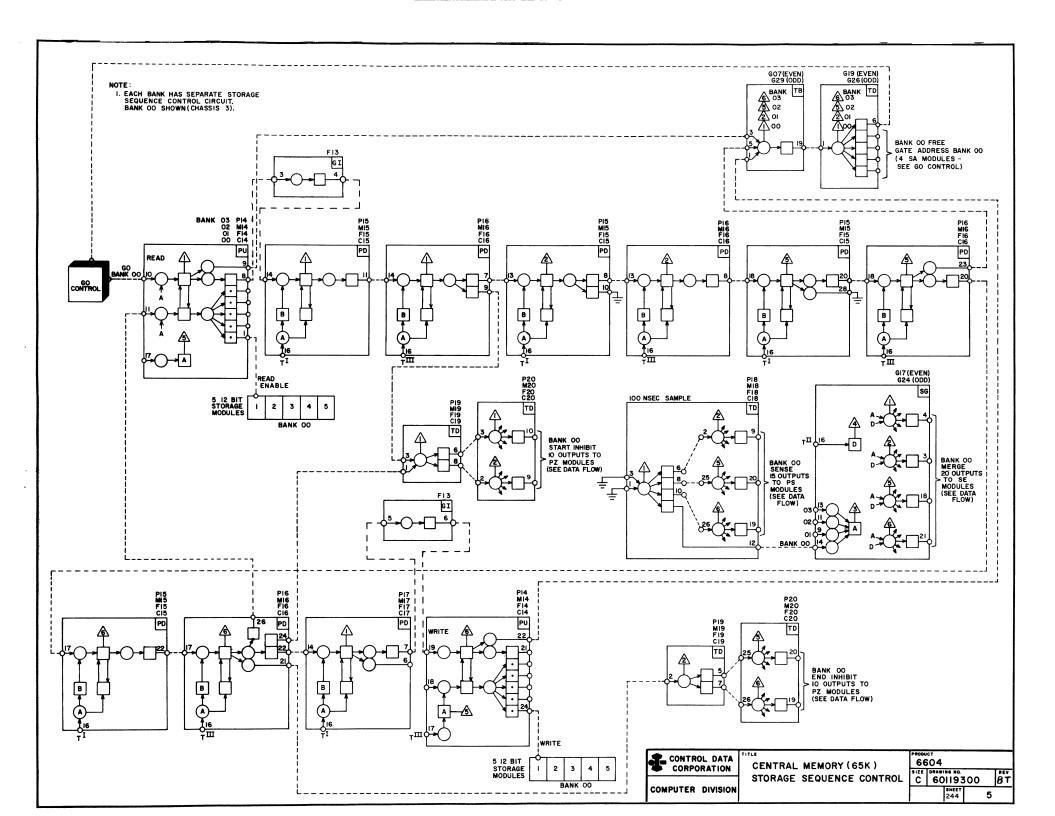

Timing for memory references is controlled by the Storage Sequence Control, which is a timing chain of FFs gated by clock pulses. As a "1" passes down the chain, each FF is set for one minor cycle during which it issues commands to the storage logic. This chain reinitiates itself after each cycle and runs continuously. One memory reference is initiated each minor cycle. The Storage Sequence Control overlaps the references as shown in the typical stage "a".

The stages of storage sequence control are numbered according to the processor for which they initiate a memory reference. The commands issued by the first half of a typical stage are:

G +S, Storage a Clear Z, Storage a + 1 Set Z, Storage a + 5 Enable Sense, Storage a + 7

The second half of state "a" issues the commands:

Read, a Write, a + 5 Stop Read, a + 6 Stop Write, a + 1

These commands and other signals from storage sequence control

define and separate the peripheral and control processors.

The reset circuit which reinitiates storage sequence control senses whether stages 0-8 are set; if not, stage 0 is reinitiated just after stage 9 has issued its commands.

A memory reference is initiated from stage 6 in the barrel, so that information from memory is available at slot time. Thus, a memory reference for processor 0 (storage 0) is initiated while processor 5 is in the slot.

## MEMORY

Each of the ten peripheral and control processors has its own independent core-storage unit with a capacity of 4096 12-bit words. Each has its own address register (S), sense amplifiers, and restoration register (Z). However, the ten storage units share a common memory cycle path and common paths to and from the barrel.

Each peripheral and control processor makes one memory reference each major cycle. When no memory reference is called for by the current instruction, address 0000 is read and restored.

Peripheral and Control Processors

Pub. No. 60119300 Rev. C Page 14

CONTROL DATA CORPORATION

PERIPHERAL AND CONTROL

PROCESSOR

STORAGE SEQUENCE

CONTROL TIMING

PRODUCT 6601

3126 dinawing NO. C C | SHEET | 17

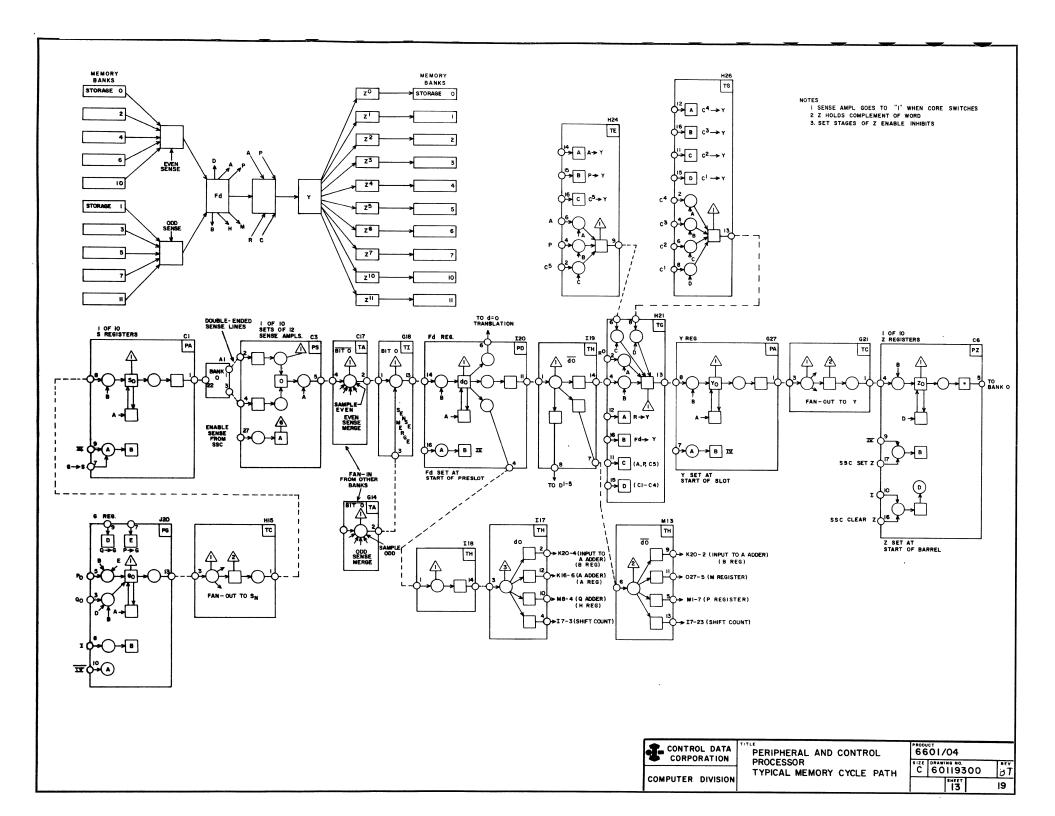

## MEMORY CYCLE PATH

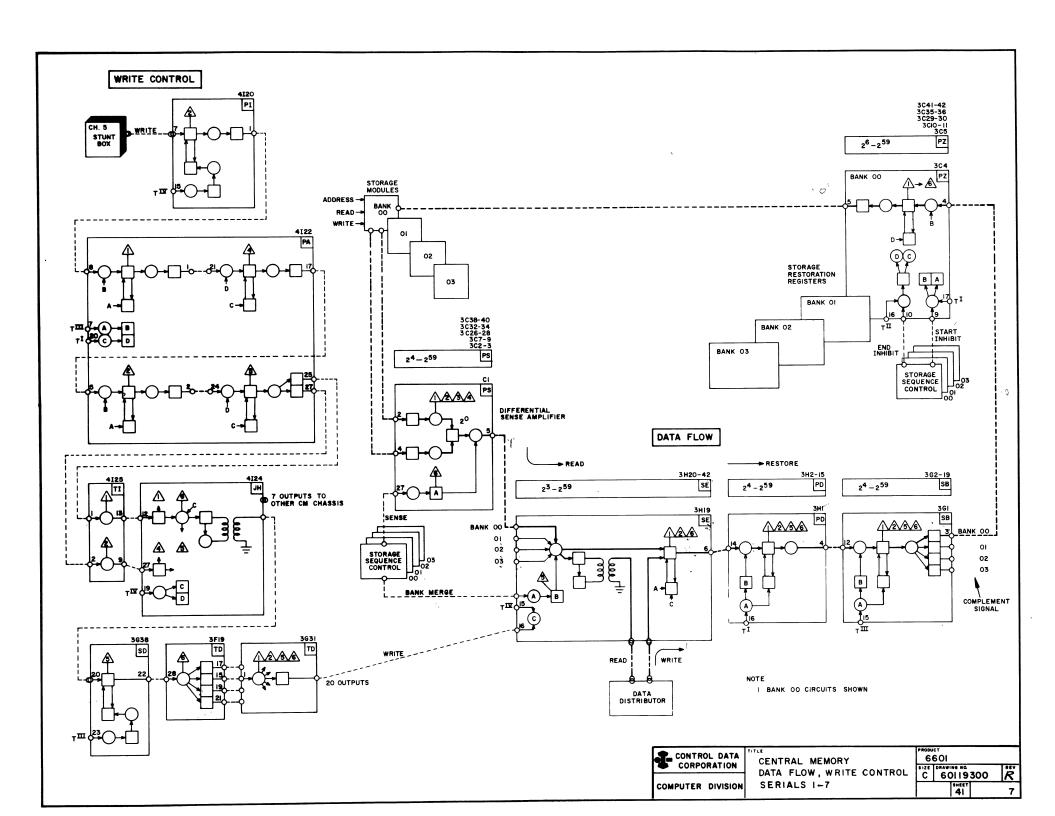

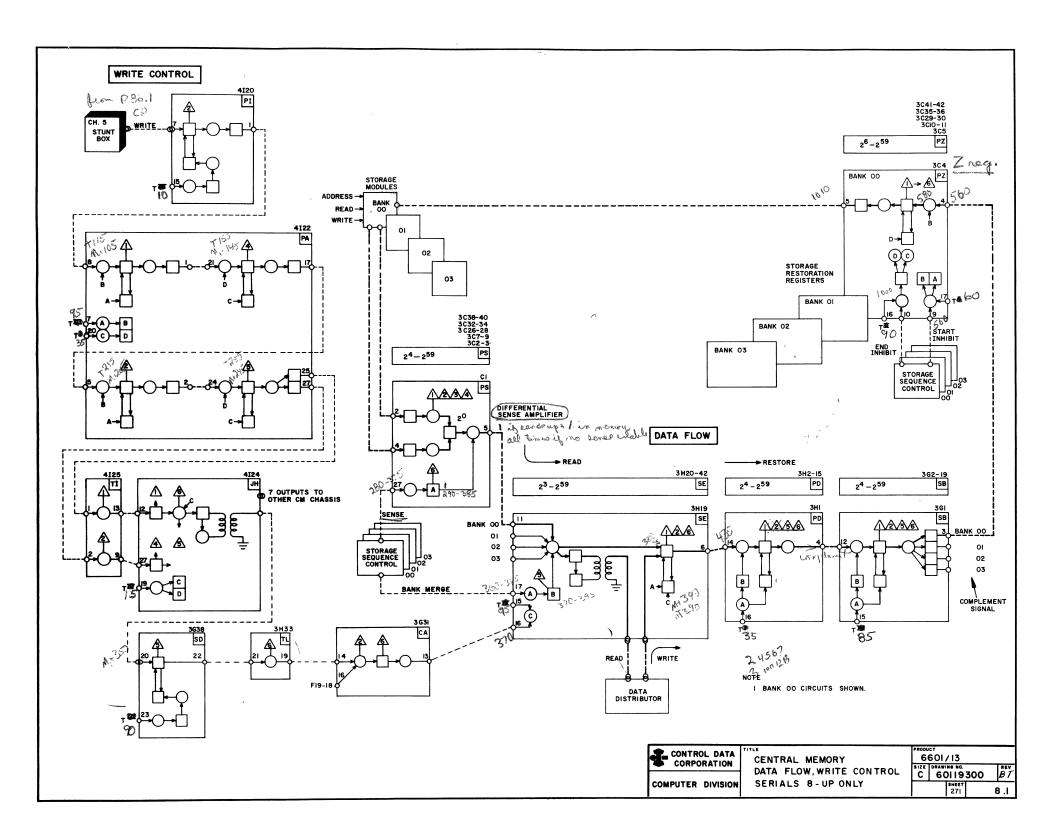

The common memory cycle path used by all processors receives data from the memories via the sense merge. Inputs to the sense merge from the sense amplifiers are a logical "1" (0.2v) when sense is not enabled. When a processor's sense amplifiers are enabled, the outputs of the PS modules are allowed to go to +1.2v for a sensed "0". If the core switches, the sense amplifier output goes to +0.2v "1". The AND combination of logical "1's" from unselected processors, even or odd sense enable, and "1" bits from the selected processor's sense amplifiers sets the word from memory into the Fd register in the memory cycle path.

The memory cycle path sends information to the barrel, I/O channels, translators and central write pyramid and receives information from the barrel, central read pyramid, and I/O channels. Outputs from Fd in the memory cycle path are translated and used to form commands when K = 00X (read next instruction trip).

Information in the memory-cycle path (either the read word or a new word) is fanned out from the Y register to the ten Z registers. The set Z signal from storage sequence control gates the complement of the word to be stored into the proper Z register.

| CONTROL DATA      | PERIPHERAL AND CONTROL | 6 6 0 1 / 0 4 |

|-------------------|------------------------|---------------|

|                   | PROCESSOR              | C 60119300 BT |

| COMPUTER DIVISION | F - 20, Q - 20         | 14 21         |

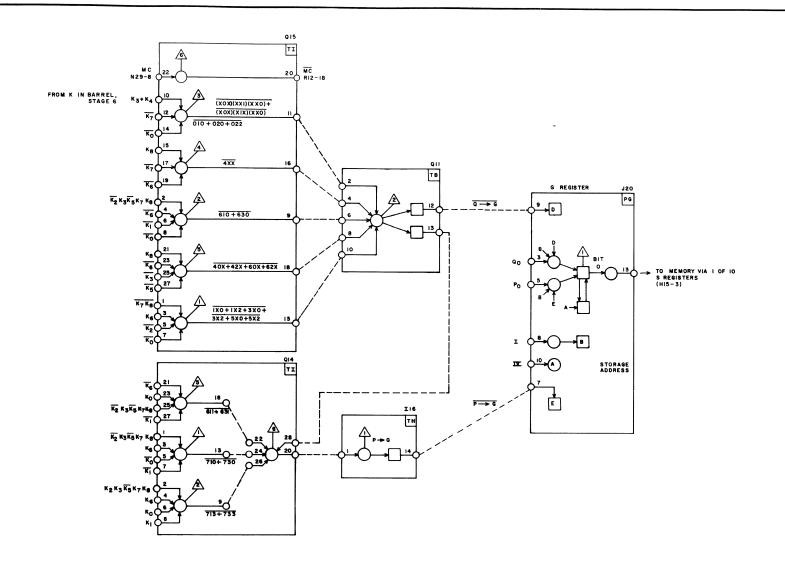

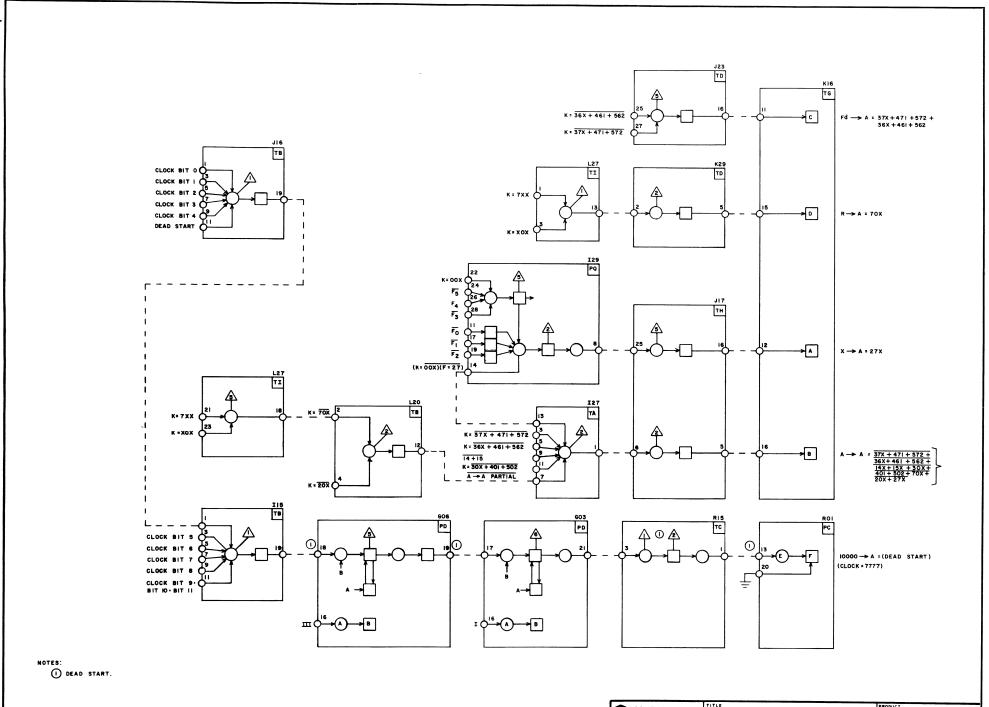

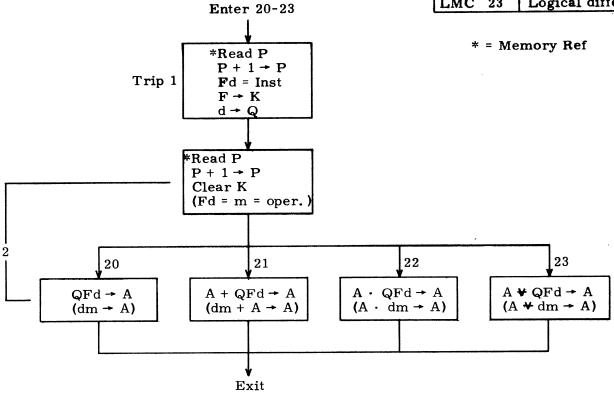

## K REGISTER

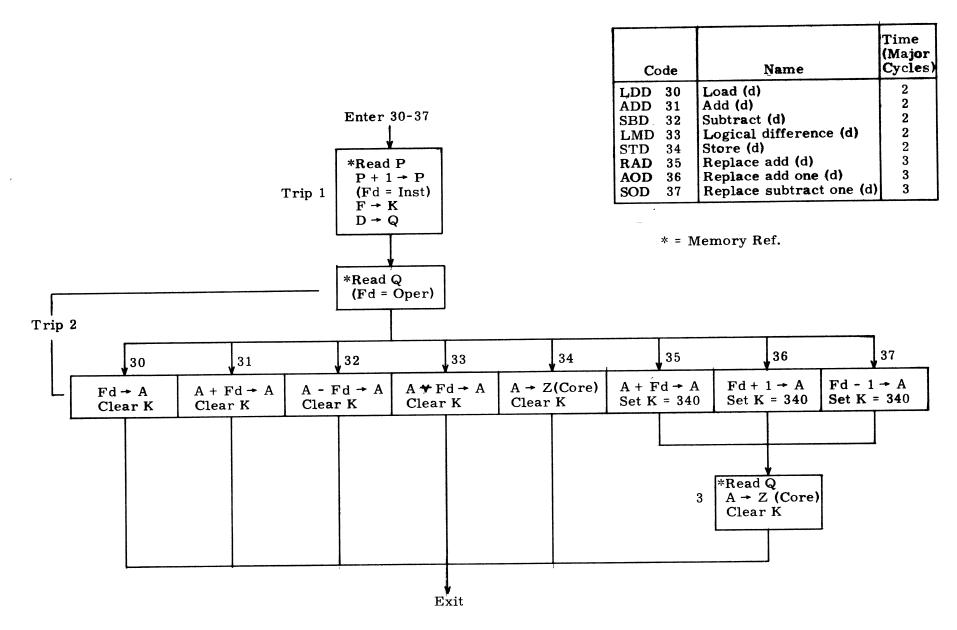

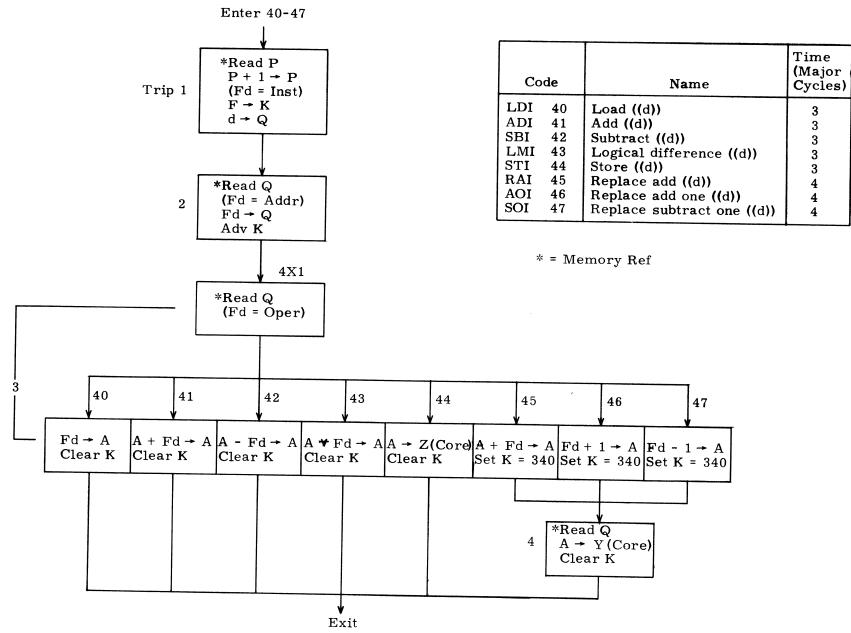

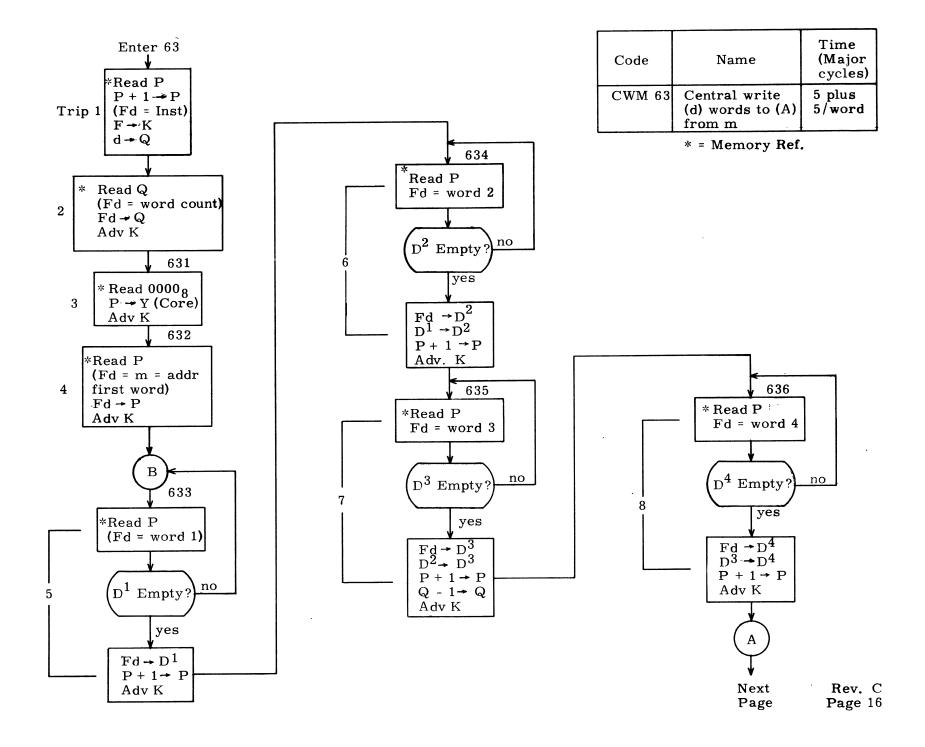

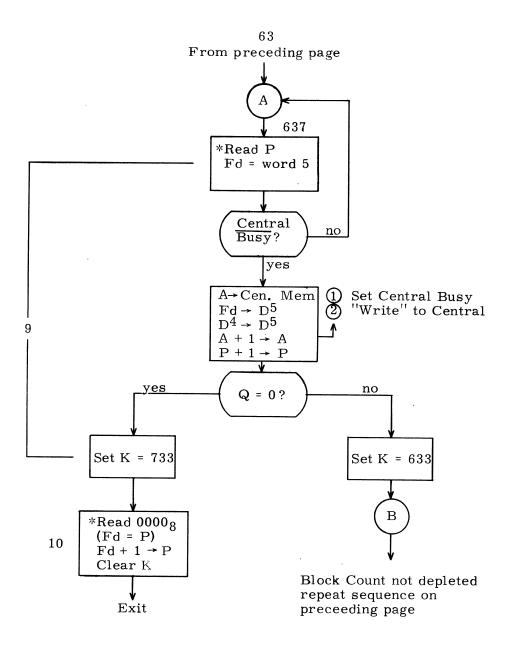

K in the slot consists of a 3-bit trip counter for the lower three bits and a fan-in for the upper six bits. The advance K signal to the trip counter is enabled by instruction translations. For some instructions, the advance K signal is controlled by signals which indicate status, i.e., the  $5\times0$  trip is skipped by all  $5\times1$  instructions if d = 0, and when K = 732, K is advanced only if the I/O channel is empty and active and A = 1.

The three-bit trip count controls the sequence of operations for each instruction and is sometimes changed by gates other than the trip counter. For instance, for a central write instruction (63), K is changed from 637

to 633 to repeat the sequence of commands and send another word. When a 63 instruction is completed, K is changed from 637 to 733 to finalize the instruction and obtain the next instruction from storage.

The fan-in to the upper six bits of K allows the instruction code F to be entered into K from storage. The K  $\rightarrow$  K path allows another trip around the barrel for the present instruction. The path K = 340 is used by replace instructions which automatically use the store instruction 34 to accomplish the store portion of the replace instructions.

| CONTROL DATA      | PERIP           |

|-------------------|-----------------|

| COMPUTER DIVISION | PROCE<br>K -> K |

| PERIPHERAL AND CONTROL | 6601       |

|------------------------|------------|

| PROCESSOR  K -> K GATE | C 60119300 |

| K-K GAIE               | SHEET      |

CONTROL DATA CORPORATION

COMPUTER DIVISION

COMPUT

COMPUTER DIVISION

C 60119300

SHEET 19

31

# A ADDER

The A adder is used to execute add, subtract, selective clear, logical product, and logical difference instructions. Parts of the A adder are also used to enter a word into the shift network and gate the result back to the barrel. The quantity in A in the barrel is always complemented when it enters the slot. When no operation on A is called for, (A) is complemented, enters the A adder, is added to zero, and the result is recomplemented at the output. The Add gate on the QD modules is always enabled except when Selective Clear, Logical Product, or Shift commands are enabled.

#### Add

For an add instruction (A) is complemented and entered into the A input register. The second operand is also complemented and entered into the B input register. The two quantities in the input registers, taken as positive, are added and the sum is re-complemented as it is gated out of the QD modules to the barrel.

## Subtract

For subtract instructions, the minuend, (A) is complemented as it enters the adder. The subtrahend is entered into B without being complemented and the two quantities are added as in an add instruction.

# Selective Clear

For selective clear, the complement of A and the true value of d are entered into the adder and both the selective and the logical product gates are enabled.

## Logical Product

For logical product instructions, both A and d (or dm) are complemented before entering the adder and both the logical product and the selective gates are enabled.

# Logical Difference

For logical difference instructions, the complement of A and the true value of the second operand enter the adder and only the selective gate is enabled.

> Peripheral and Control Processors

CONTROL DATA CORPORATION

PERIPHERAL AND CONTROL PROCESSOR A REGISTER GATES | PRODUCT | FROM | PRODUCT | SIZE | DRAWING NG | C | 60119300 | BT | SIZE | 23 | 39

CONTROL DATA PERIPHERAL AND CONTROL PROCESSOR

COMPUTER DIVISION H GATES

PRODUCT 660 | SIZE DRAWING NO. C 60119300 | NEV C 28 49

# SHIFT NETWORK

The shift instruction (10) provides for shifting the number in A up to 31 places left or right. Left shift is circular with the high order bits re-entering A at the low-order end. Right shift is end-off with low-order bits discarded as they shift out of the A register and with no sign extention. Thus, a left shift of 18 is equivalent to no shift, and a right shift of 18 clears the A register.

The shift network is a static network. The content of A enters the register at time IV, each bit follows a path established by static translations of the 6-bit shift count in d, and the result re-enters A in the barrel at the next time IV. The input to the shift network comes from the A input register in the A adder (the content of that register, which is the complement of A, is re-complemented before entering the shift register). The output of

the shift network is gated back to the barrel by way of the output modules (QD) of the A adder. Note that the quantity in A is always shifted but the result is gated to the barrel only when the current instruction is a shift.

If d is positive  $(00-37_8)$  the shift is left and the shift count is the content of d. If d is negative  $(40-77_8)$  the shift is right and the shift count is the complement of the number in d.

At the first stage of the shift network,  $\rm d_4$  and  $\rm d_5$  are tested to determine whether the shift is greater or less than 16 and whether it is right or left. If the shift is 16 or greater, a shift of 16 is made at this point and the result then enters the rest of the shift network.

Bits  $\mathbf{d_0^{-d}_3}$  are tested with  $\mathbf{d_5}$  to set up paths through the rest of the network.

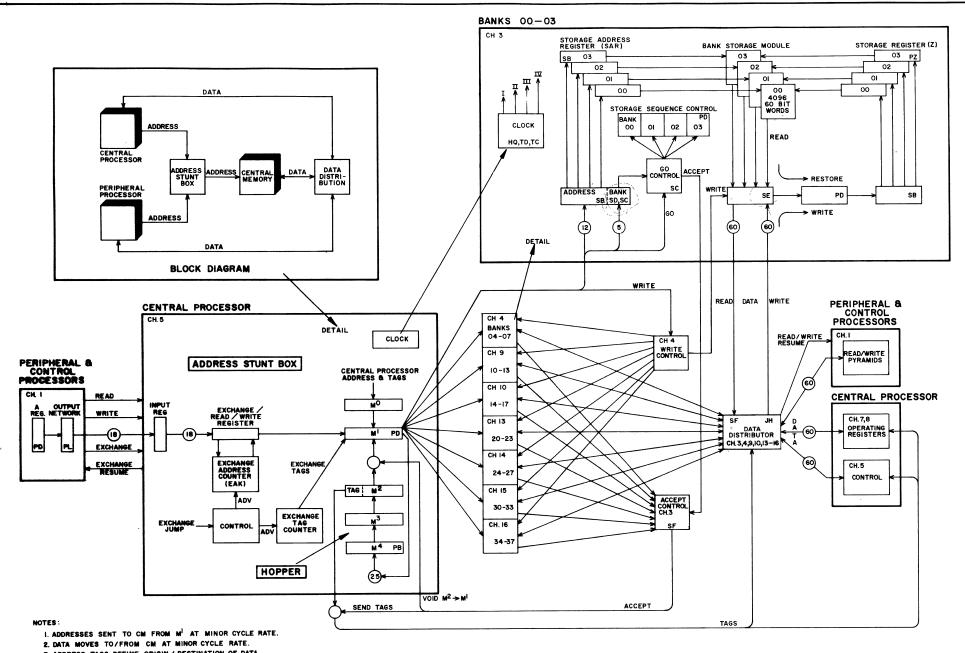

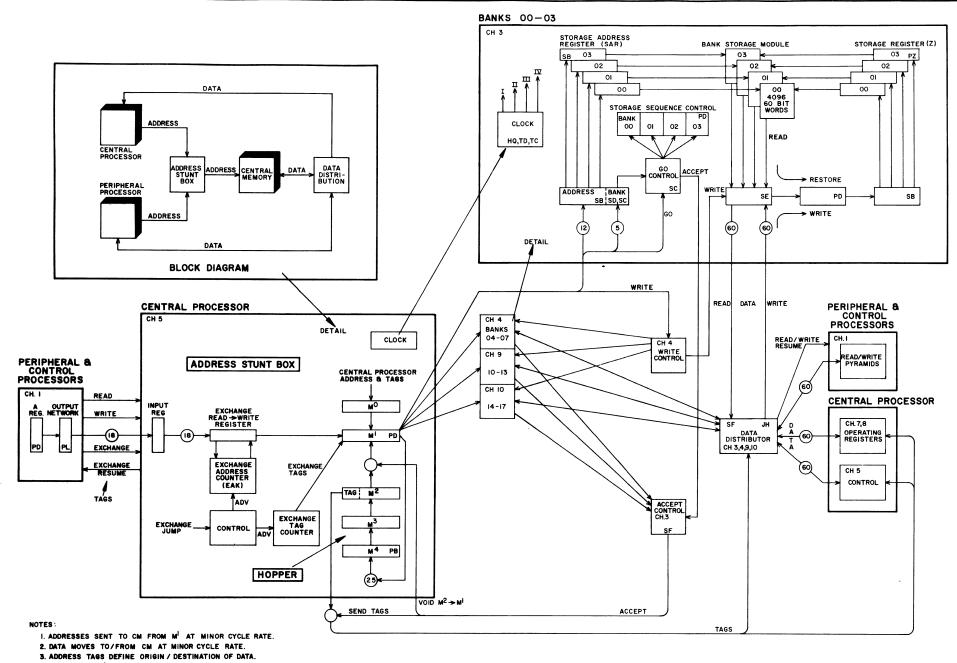

# COMMUNICATION WITH CENTRAL MEMORY AND CENTRAL PROCESSOR

The peripheral and control processors may communicate with the central processor and central memory in several ways. They may read the central processor's program address, tell the central processor to jump to given central memory address for its next instruction, or read from or write into central memory.

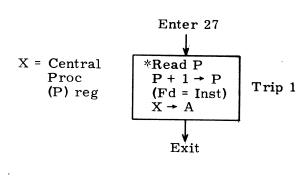

#### CENTRAL PROGRAM MONITOR

The 18-bit central processor program address is sent to the central program monitor register on chassis 1 every minor cycle. A Read Program Address instruction (27) sends the central address to the A register. Thus the progress of a central program may be monitored by any peripheral and control processor.

Exchange Jump, Central Read, and Central Write instructions all use the content of A as a central memory address, (A) is unconditionally sent to address control in the central processor every minor cycle. This quantity is recognized and used as a central memory address only if accompanied by a Central Read, Central Write, or Exchange Jump signal.

The Central Busy FF indicates when a reference to central is in progress. A central Busy condition prevents initiating a central reference until one in progress is completed.

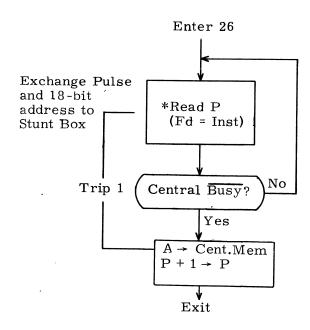

#### EXCHANGE JUMP

An exchange jump instruction is used to command the central processor to stop the program it is executing and go to a central memory location specified by the instruction. An exchange jump may be issued by any peripheral and control processor so long as the Central Busy FF is clear. The instruction sends an Exchange Jump signal to the central processor and sets the Central Busy FF. The Exchange Jump signal tells the central processor to recognize the 18-bit address sent from the peripheral processor and to perform an exchange jump. After the central processor has performed the exchange jump and started a new program it sends a Resume signal which clears the Central Busy FF to allow another central reference. If a peripheral and control processor tries to issue an Exchange Jump instruction while the Central Busy FF is set, the processor must wait until the previous central reference is completed and the Central Busy FF is cleared.

Peripheral and Control Processors

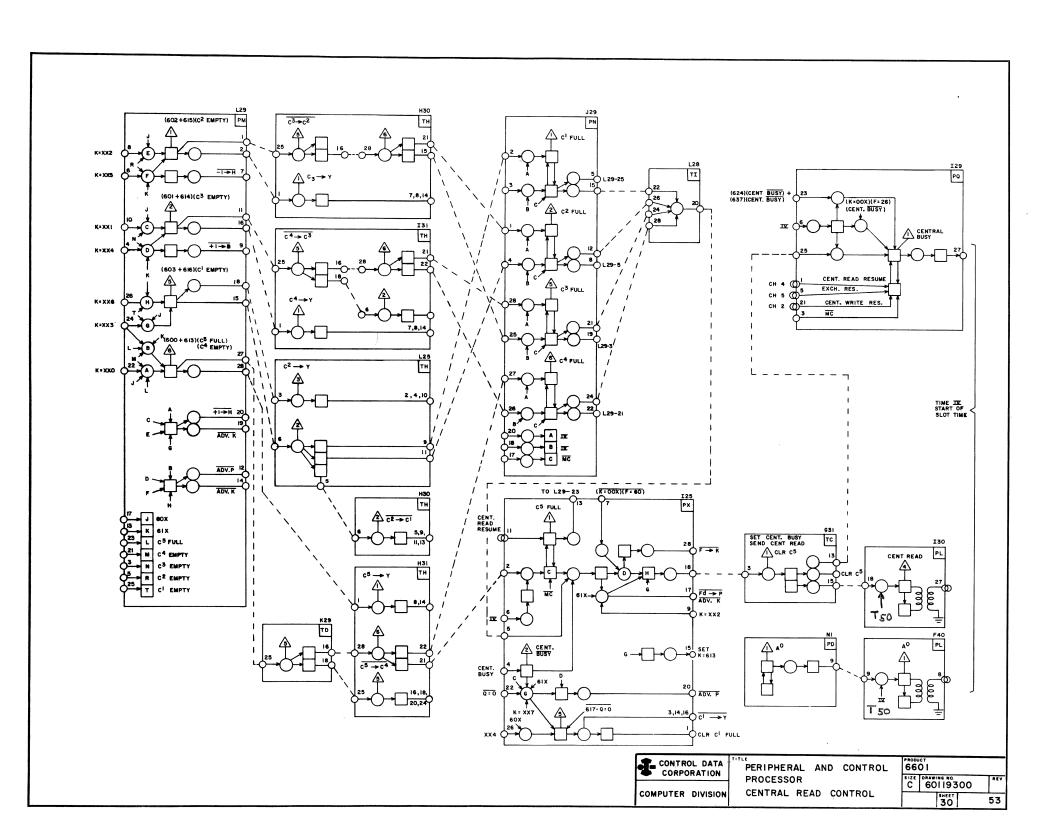

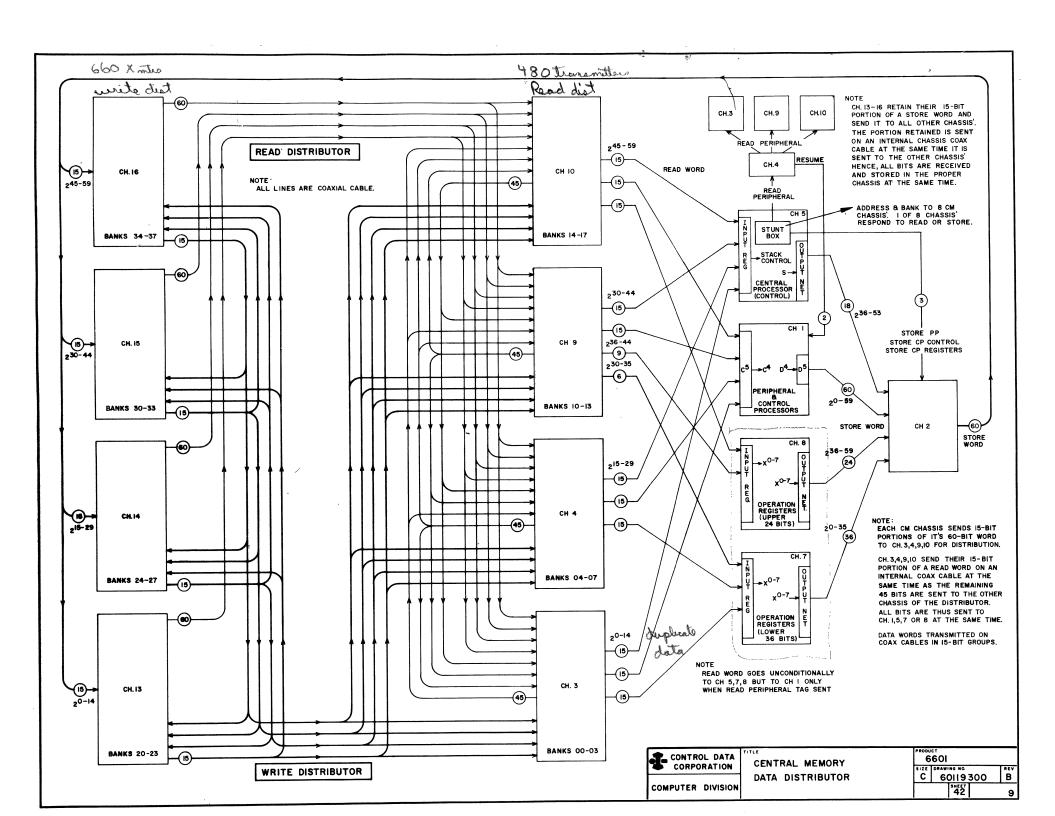

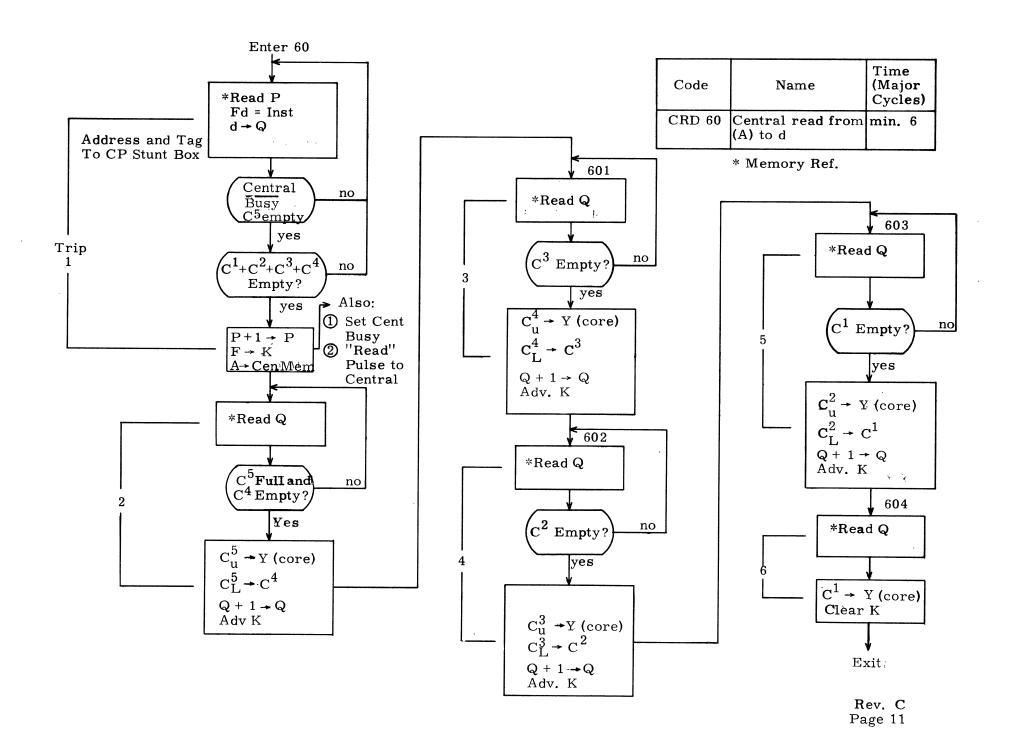

#### CENTRAL READ

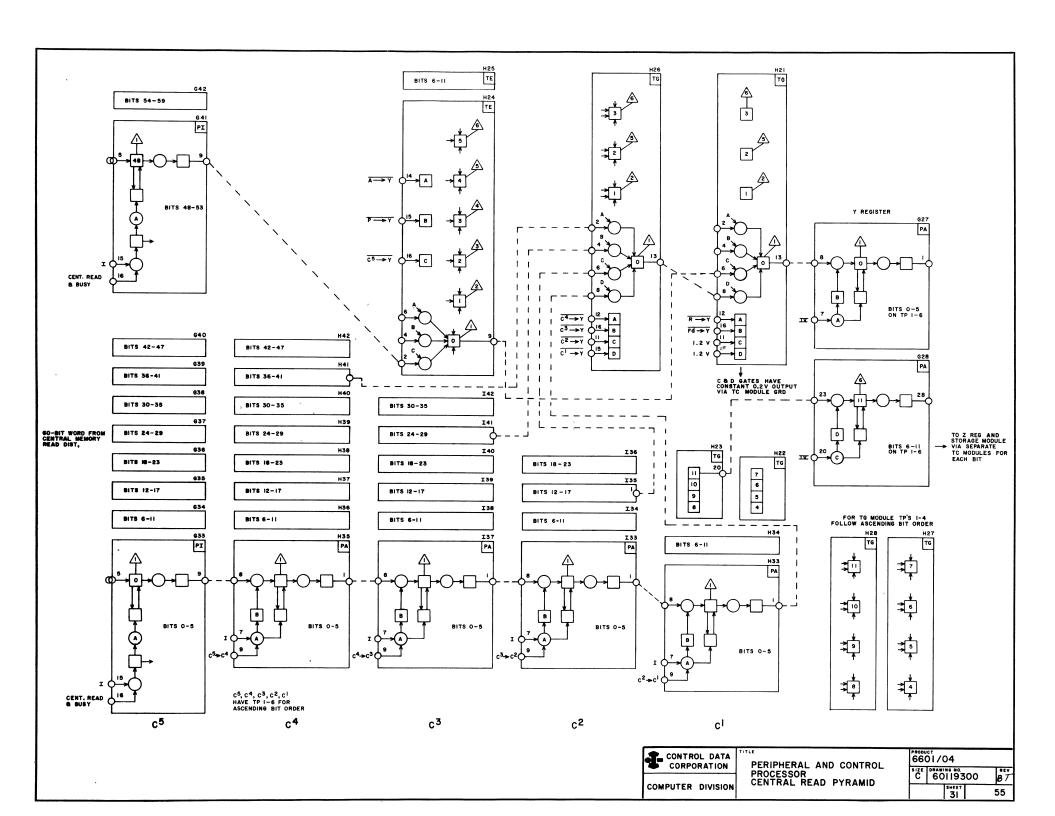

The Central Read instruction allows a peripheral and control processor to obtain one word (60-bits) or a block of words from Central Memory. The instruction sends a Central Read signal to central address control enabling it to use the 18 bit quantity from A as a central memory address. At the same time, the Central Busy FF is set to inhibit other references to central until the read word is received. When a 60-bit word is sent by central to the Central Read Pyramid, it is accompanied by two control signals; Read Resume which clears the Central Busy FF and a signal which sets the  $C^5$  Full FF. Each rank of the Central Read Pyramid  $C^1$ - $C^5$  has an associated Full/Empty FF used to control the flow of data through the pyramid. C<sup>5</sup> Full and C<sup>4</sup> Empty enables the processor doing the read instruction to send the upper 12 bits of C<sup>5</sup> to memory and the lower 48 bits to C4. Subsequent steps in the Central Read instruction step the central word down through the pyramid and store the rest of the central word as 12-bit peripheral words. Each step in this storage procedure J 1: - ^

requires that the next lower rank in the pyramid be empty before a transfer is made. No Central Read instruction may be issued until the C<sup>5</sup> Full FF and Central Busy FF are clear. However, as many as four central memory words, in different stages of disassembly, may be in the Central Read Pyramid at one time. A read instruction for which the proper full and empty conditions are not met must wait until previous instructions progress further and conditions are met.

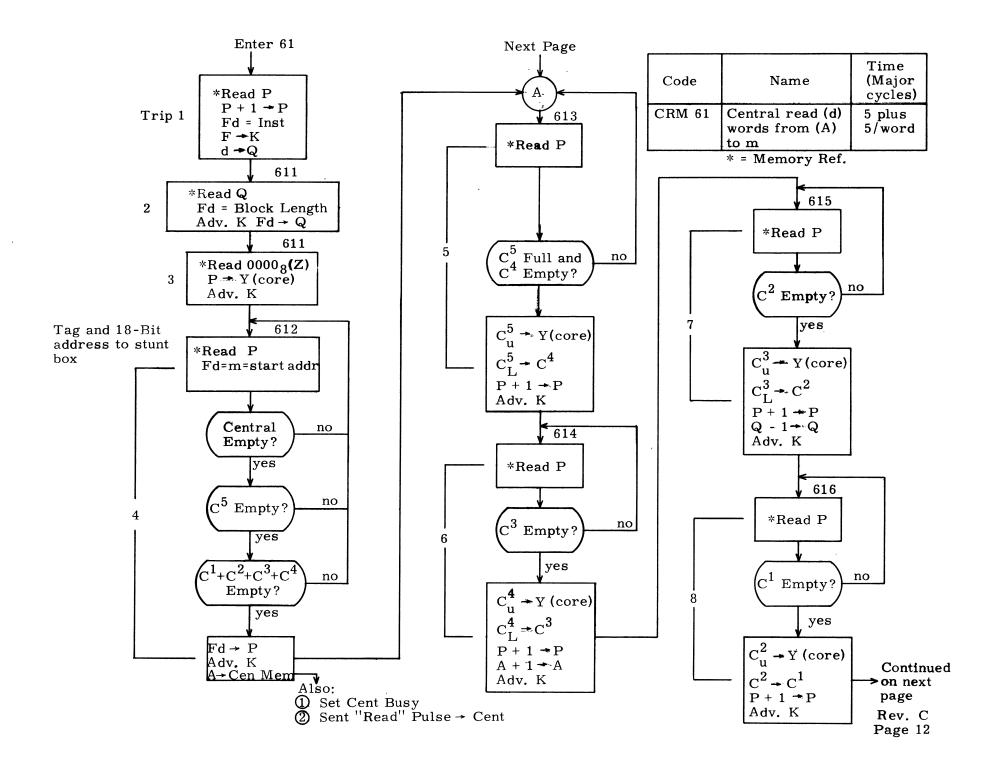

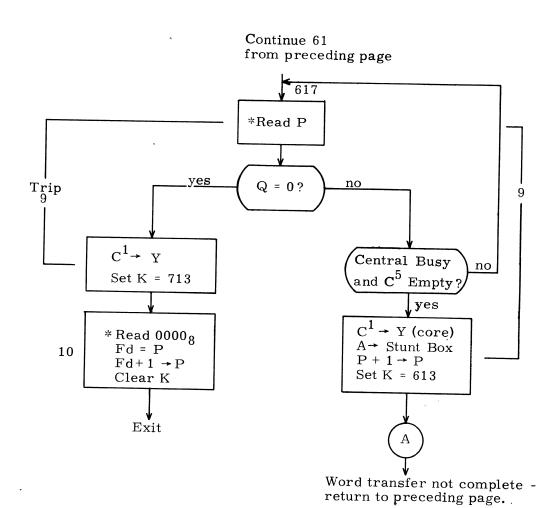

A 60 instruction reads only one central memory word and stores it as five peripheral words. A 61 instruction reads a block of words specified by (d). In either instruction the first central memory address is specified by (A). For a 60 instruction, d specifies the peripheral address at which the upper 12 bits of the peripheral word are stored; the next lower 12 bits go to d + 1, etc. For a 61 instruction, (d) gives the number of central words to be read and m is the address for the upper 12 bits of the first central word.

Peripheral and Control Processors

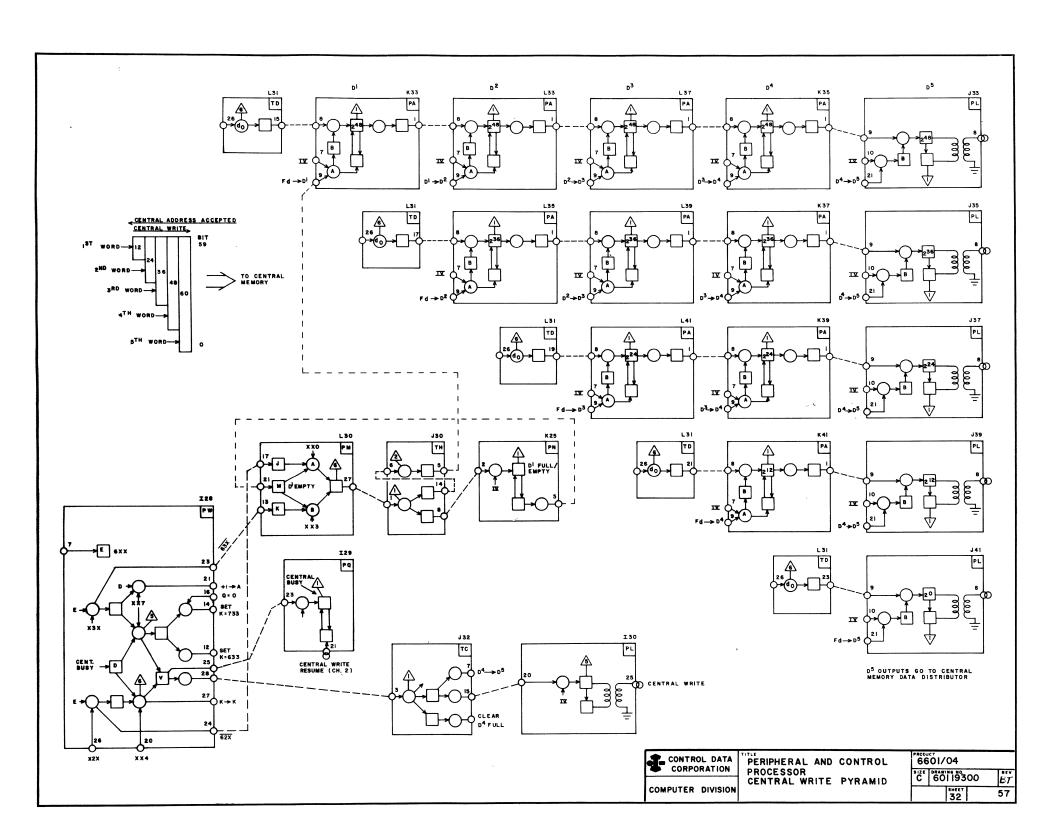

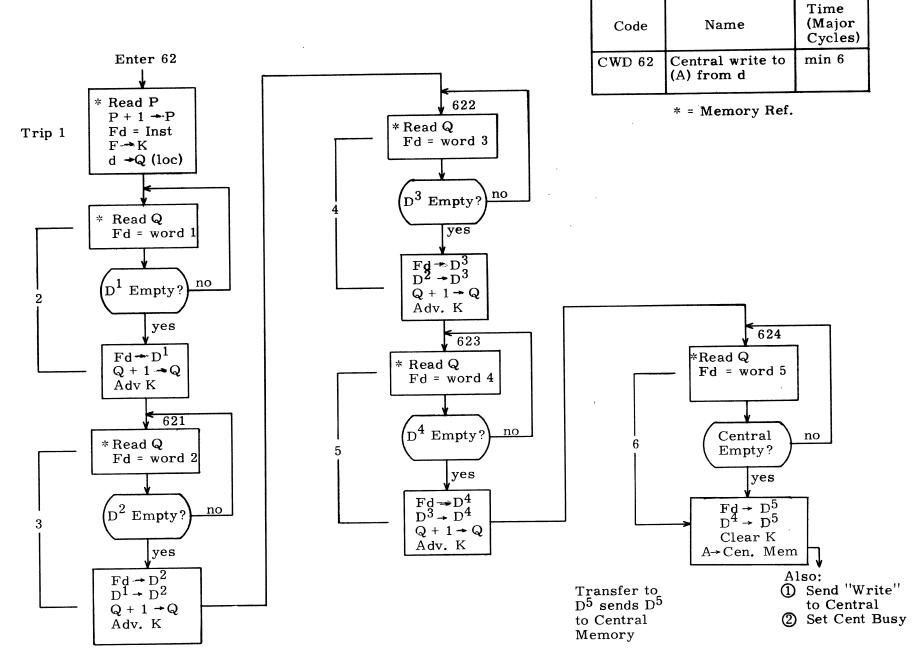

#### CENTRAL WRITE

Central Write instructions send one 60-bit word or a block of 60-bit words to Central Memory. Each 60-bit word sent to Central Memory is assembled in the Central Write Pyramid from five 12-bit peripheral words. A Central Write instruction assembles a 60-bit word and sends the word and a Central Write signal to central address control and sets the Central Busy FF. The Central Write signal enables central address control to accept the 60-bit word and store it at the

address specified by (A). When the word has been stored, an accept signal is sent back to clear the Central Busy FF. Up to four Central Write instructions may be in progress at one time with portions of four different words in  $D^1-D^4$ .  $D^5$  is an output network only and cannot store a word. The first 12-bit word goes to  $D^1$  and will be the upper 12 bits of the 60-bit word. When a second 12-bit word goes to  $D^2$ ,  $D^1$  is also sent to  $D^2$ . When the fifth word goes to  $D^5$ , the 48 bits in  $D^4$  are also sent to  $D^5$  and the 60-bit word is sent to central.

Peripheral and Control Processors

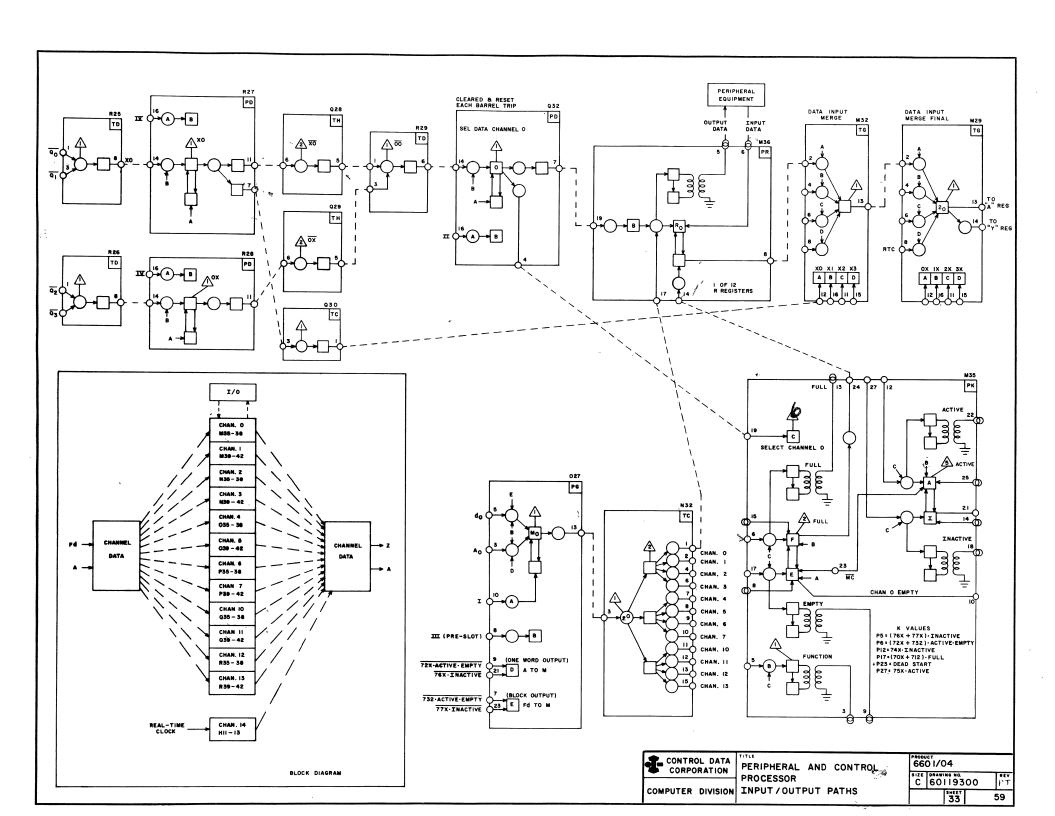

#### INPUT/OUTPUT

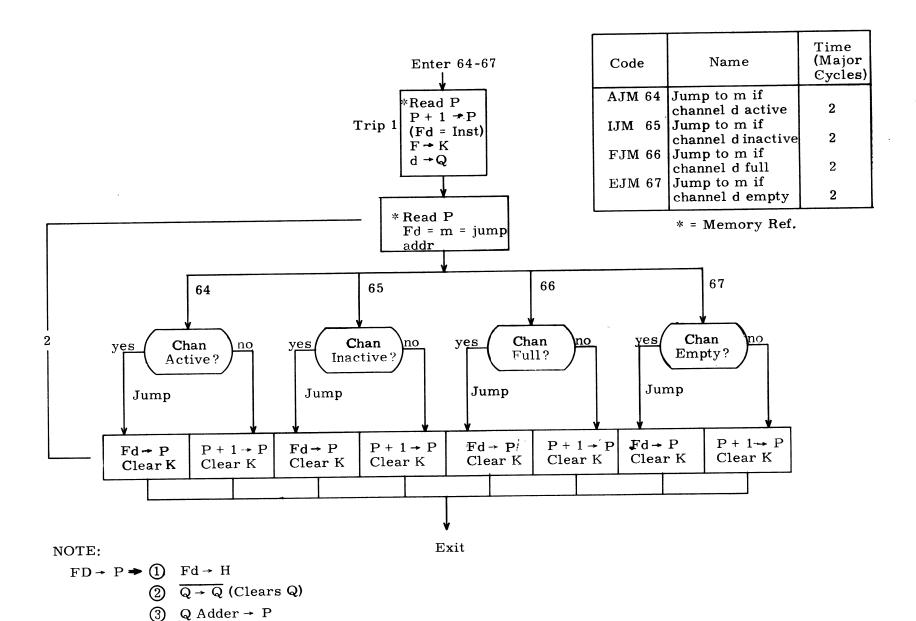

Each of the 12 independent data channels can handle 12-bit words at a maximum rate of one word every major cycle (equivalent to a 1 megacycle rate). Each channel has an Active/Inactive FF and a Full/Empty FF which indicate channel status to the processors. Any channel may be used by any processor, but the external equipment assigned to a channel is wired in and may be assigned to another channel only by changing cable connections.

The lines of a data channel are:

| Input                                                                              | Output                                                                 |

|------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Data or Status Reply (12 bits)<br>Active<br>Inactive (Disconnect)<br>Full<br>Empty | Data or Function word (12 bits)<br>Active<br>Inactive<br>Full<br>Empty |

|                                                                                    | MC                                                                     |

In addition, two clock signals are available to external equipment: a 1 mc clock and a 10 mc clock. The clock pulses are 25 nsec wide, as are all data and control signals (except master clear). Controllers for each external equipment (or group) perform the conversion between the 6600 pulse signals and the signals required by I/O devices.

A data channel may be used for communication between processors if it is selected for input by one processor and for output by another. The status of data channels may be sensed by instructions 64-67: jump to m if channel d active. etc.

#### MASTER CLEAR

A Master Clear (MC) signal is generated only by the Dead Start circuit. MC removes all equipment selections (except Dead Start) and sets all channels to the Active and Empty condition (ready for input). MC is a

1 usec pulse which is repeated every 4096 usec while the Dead Start switch is on.

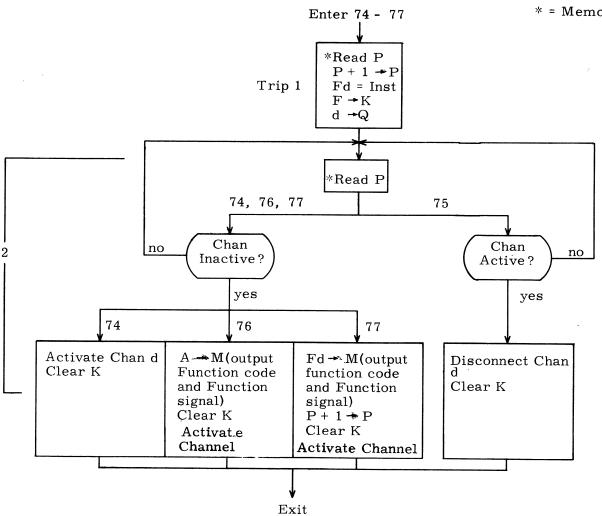

#### **DISCONNECT (75)**

A disconnect instruction clears the channel Active FF if it is set and sends an inactive pulse to the equipment on that channel. If a disconnect instruction is given for a channel which is already inactive, the processor which issued the disconnect will "hang up" and will not be able to continue until the channel is activated by another processor (or by MC).

#### FUNCTION (76 or 77)

A function instruction sends a 12-bit function code (from A or Fd) on the data lines and sends a Function signal. It also sets the Active and Full FFs for the channel but does not send Active and Full pulses. Upon receipt of the function code, the external equipment sends an Inactive (disconnect) signal, clearing the Active FF in the data channel which in turn clears the Full FF. If a Function instruction is given for an active channel, the processor will hang up until the channel is deactivated.

#### ACTIVATE (74)

An Activate instruction sends an Active signal on the channel and sets the Active FF if the channel is inactive. If an Activate instruction is given for a channel which is already active, the processor which issued the instruction will "hang up" until the channel is inactivated by another processor or by an Inactive (disconnect) signal from an external equipment on the channel.

Peripheral and Control Processors

#### DATA INPUT SEQUENCE

An external device sends data to the processor by way of the controller in the following manner:

- The processor places a function word in the channel register and sets the full flag and the channel active flag. Coincidently, it sends the word and a function signal to all controllers. The function signal tells all controllers to sample the word and identifies the word as a function code rather than a data word. The code selects a controller and a mode of operation. Non-selected controllers clear, leaving only the selected one turned on.

- The controller sends an inactive signal to the processor indicating acceptance of the function code. The signal drops the channel active flag which in turn drops the full flag and clears the channel register.

- 3 The processor sets the channel active flag and sends an active signal to the controller which signals the device to start sending data.

- The device reads a word and then sends the word to the channel register with a full signal which sets the channel full flag.

- 5 The processor stores the word, drops the full flag, and returns an empty signal indicating acceptance of the word. The device clears its data register and prepares to send the next word.

- 6 Steps 4 and 5 repeat for each word transferred.

- 7 At the end of the transfer, the controller clears its active condition and sends an inactive signal to the processor to indicate end of data. The signal clears the channel active flag to disconnect the controller and the processor from the channel.

- As an alternative, the processor may choose to disconnect from the channel before the device has sent all of its data. The processor does this by dropping the active flag and sending an inactive signal to the controller which immediately clears its active condition and sends no more data, although the device may continue to the end of its data record or cycle (e.g., a magnetic tape unit would continue to end of record and stop in the record gap).

# STATUS REQUEST

A status request is a special one word data input transfer in which an external device indicates a ready or error condition to a processor.

The processor places a function word in the channel register and sets the full flag and the channel active flag. Coincidently, it sends the word and a function signal to all controllers. The function signal tells all controllers to sample the word and defines

the word as a function code rather than a data word. The code selects a controller and places it in status mode. Non-selected controllers clear, leaving only the selected one turned on.

- The controller sends an inactive signal to the processor indicating acceptance of the status function code. The signal drops the channel active flag which in turn drops the full flag and clears the channel register.

- 3 The processor sets the channel active flag and sends an active signal to the controller which signals the device to send the status word.

- The controller sends the status word to the channel register with a full signal which sets the channel full flag.

- 5 The processor stores the word, drops the full flag, and returns an empty signal indicating acceptance of the word.

- The processor drops the channel active flag to disconnect the channel and sends an inactive signal to the controller to disconnect it.

#### DATA OUTPUT SEQUENCE

The processor sends data to an external device in the following manner:

- The processor places a function word in the channel register and sets the full flag and the channel active flag. Coincidently, it sends the word and a function signal to all devices. The function signal tells all controllers to sample the word and identifies the word as a function code rather than a data word. The code selects a controller and a mode of operation. Non-selected controllers clear, leaving only the selected one turned on.

- The controller sends an inactive signal to the processor, indicating acceptance of the function code. The signal drops the channel active flag which in turn drops the full flag and clears the channel register.

- The processor sets the channel active flag and sends an active signal to the controller which signals the device that data flow is starting.

- The processor places a data word in the channel register and sets the full flag. Coincidently, it sends the word and a full signal to the controller.

- The controller accepts the word and sends an empty signal to the processor where it clears the channel register and drops the full flag.

- 6 Steps 4 and 5 repeat for each processor word.

- After the last word is transferred and acknowledged by the controller empty signal, the processor drops the channel active signal to the controller to turn it off.

Peripheral and Control Processors

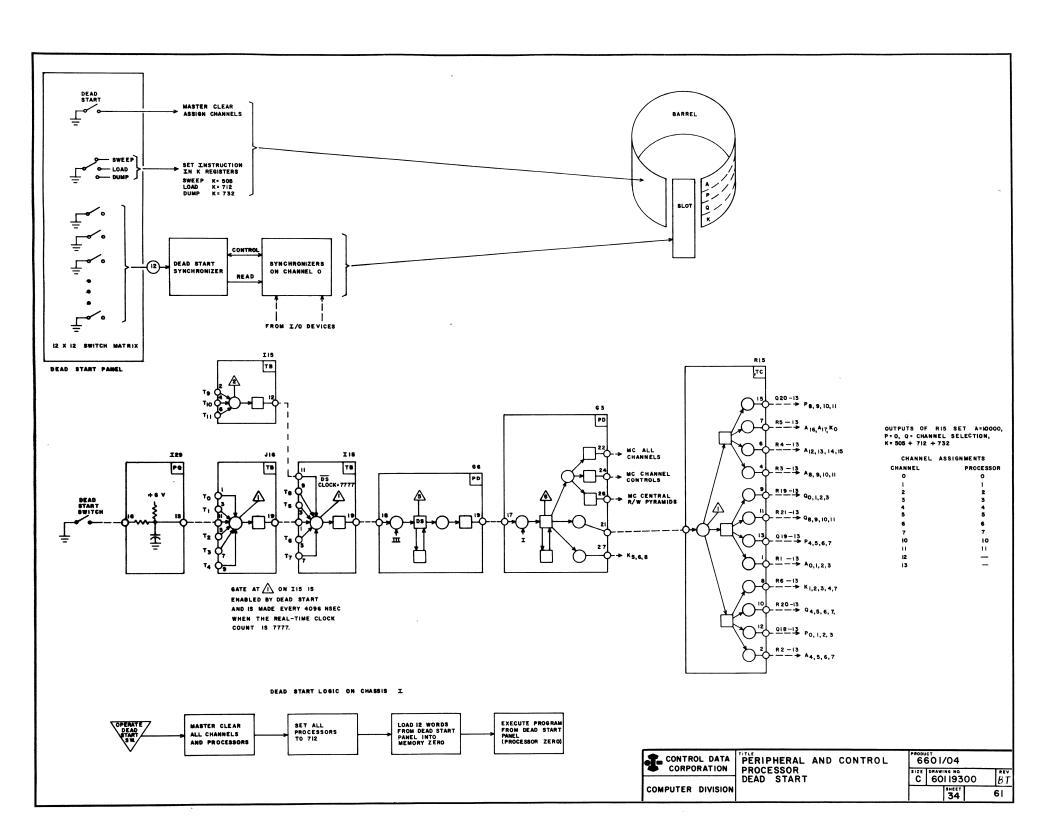

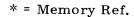

#### DEAD START

Dead Start is a system used to initially start the computer, dump the contents of the peripheral and control processor memories to a printer or other output device, or sweep memory without executing instructions.

The Dead Start panel contains a 12x12 matrix of toggle switches, a Sweep-Load-Dump switch and a Dead Start switch. It also contains memory margin switches which are used for maintenance checks.

#### LOAD

To initially load programs and date, the Sweep-Load-Dump switch is put in the Load position. The matrix of toggle switches is set to a 12-word program (up = "1", down = "0"). When the Dead Start switch is turned on, a 1 usec Dead Start pulse:

- 1 Assigns to each peripheral and control processor the corresponding I/O channel.

- 2 Sets all channels to Active and Empty

- 3 Sets K for all processors to 712 (Input)

- 4 Sends a MC on all channels

- 5 Sets P for all processors to zero. (A is then set to  $10000_8$  in the barrel)

The Dead Start pulse is repeated every 4096usec while the Dead Start switch is on. To start the machine, the DS switch is normally turned on momentarily, then off. Recycling of the DS pulse is controlled by the Real Time Clock; the pulse is formed by ANDing DS switch in the ON position with 10 bits of Real Time Clock.

When the Dead Start controller on channel 0 receives the MC sent by Dead Start, it sends a Full pulse but no data. When processor 0 receives the Full, it stores the content of the channel 0 input register (All zeros) in location 0000 and sends an Empty pulse to the Dead Start controller. The Dead Start controller then acts like an input device, sending twelve 12-bit words from the switch matrix which processor 0 stores in locations 0001-0014<sub>8</sub>. After the last word, the Dead Start

controller sends a disconnect which causes processor 0 to exit from the 712 instruction. Processor 0 reads location 0000, adds one to its contents and goes to 0001 for its next instruction. It then executes the 12-word (or less) program which normally is a control program to load information and begin operation. The other processors are still set to 712 (waiting to input when their channels become full) and may receive data from processor 0 via their assigned I/O channels.

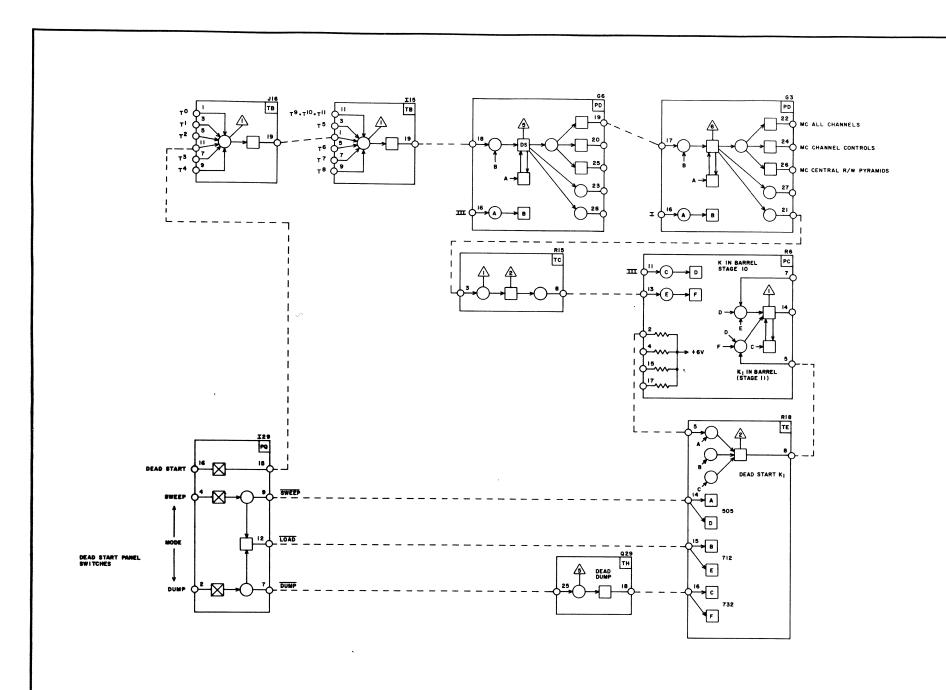

#### SWEEP

If the DS switch is operated with the Sweep-Load-Dump switch in the Sweep position, all processors are set to a 505 instruction and P registers set to 0000. Since the 50 instruction doesn't require 5 trips around the barrel there is no logic to clear or advance K from 505. The 50X translation of K, causes all processors to sweep through their memories; reading and restoring without executing instructions. This is a maintenance routine and may be used to check the operation of memory logic.

#### DUMP

Dead Start with the Sweep-Load-Dump switch in the Dump position:

- 1 Sets all processors to 732.

- 2 Sends MC on all channels.

- 3 Holds channel 0 Active and Empty.

- 4 Assigns each processor to its corresponding I/O channel.

- 5 Sets all A and P registers to 0.

All processors sense the Empty and Active condition of their assigned channels, output the content of their address 0000, set their I/O channels to Full, and wait for an Empty. All processors advance P by one and reduce A by one (A = 7776<sub>8</sub>). Channel 0, which is assigned to processor 0, is held by Empty by the Dump switch. Processor 0 therefore cycles through the 732 instruction until A = 1 and then goes to memory location 0001 for its next instruction. Processor 0 has sent its entire memory content on channel 0 although no I/O device was selected to receive it. Processor 0 is now free to execute a dump program which must have been previously stored in memory 0 (beginning at location 0001).

Peripheral and Control Processors

| 4- | CONTROL DATA |   |

|----|--------------|---|

|    | COM CHAITON  | ı |

PERIPHERAL AND CONTROL PROCESSOR COMPUTER DIVISION 712, 732, 505-K (DEAD START)

| 6601/04   |          |    |

|-----------|----------|----|

| SIZE<br>C | 60119300 | K  |

|           | SHEET    | 63 |

# CENTRAL MEMORY (131K) CONTENTS

| Page | Title                                                   |  |

|------|---------------------------------------------------------|--|

|      | Central Memory                                          |  |

| 1    | Address-Data Flow                                       |  |

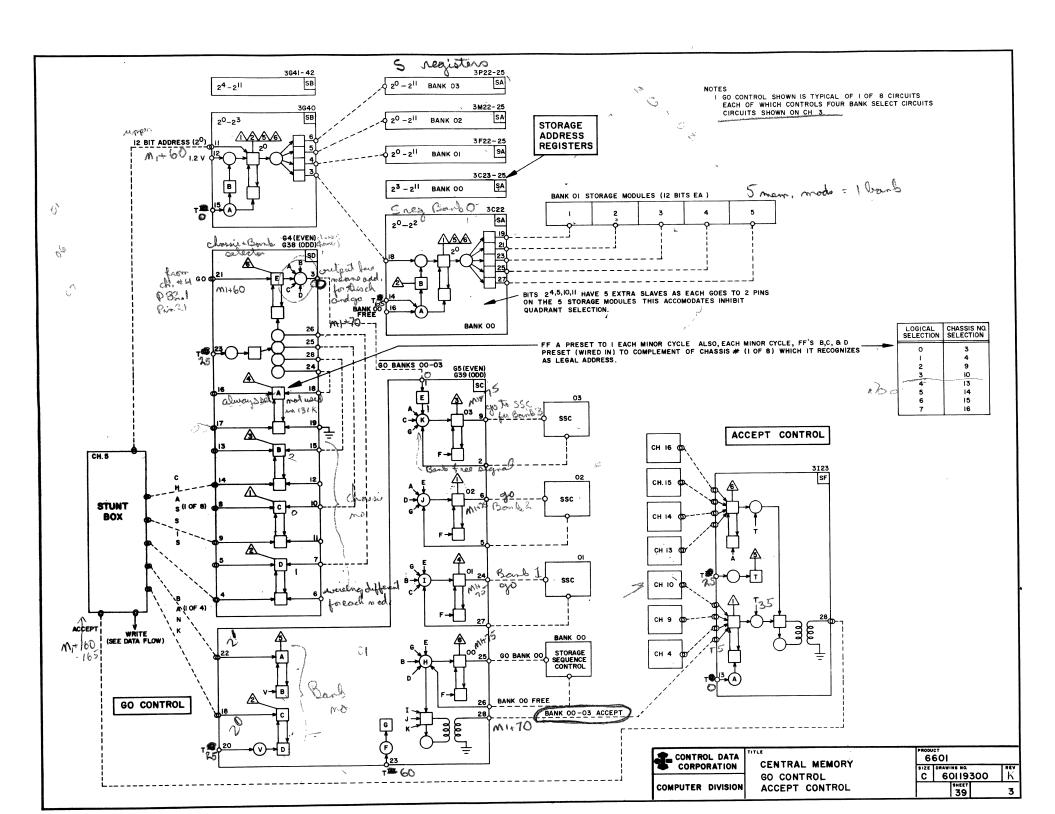

| 2    | Go Control                                              |  |

| 3    | Go Control, Accept Control                              |  |

| 4    | Storage Sequence Control                                |  |

| 5    | Storage Sequence Control                                |  |

| 6    | -Data Flow                                              |  |

| 7    | Data Flow, Write Control                                |  |

| 8    | Data Distributor                                        |  |

| 9    | Data Distributor                                        |  |

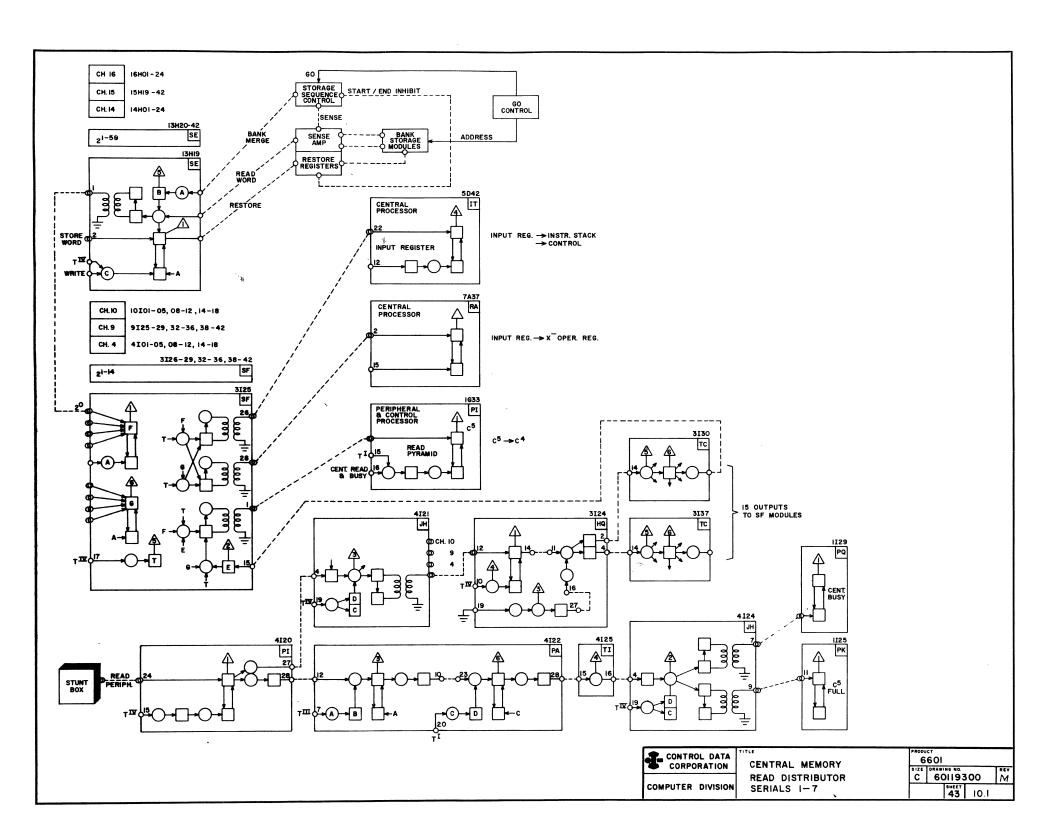

| 10   | Read Distributor                                        |  |

| 10.1 | Read Distributor, Serials 1-7                           |  |

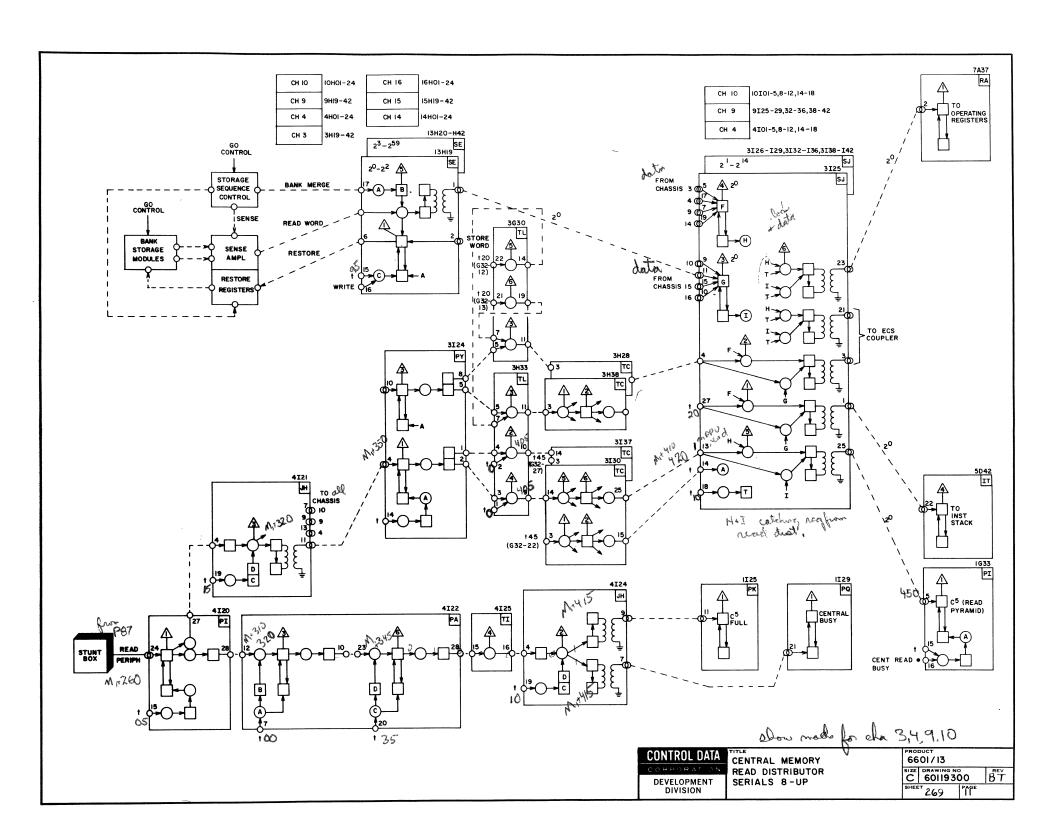

| 11   | Read Distributor, Serials 8 and up                      |  |

| 12,0 | Read Distributor, Chassis 3, 4, 9, 10 (Test Points)     |  |

| 12.1 | Read Distributor, Chassis 13, 14, 15, 16 (Test Points)  |  |

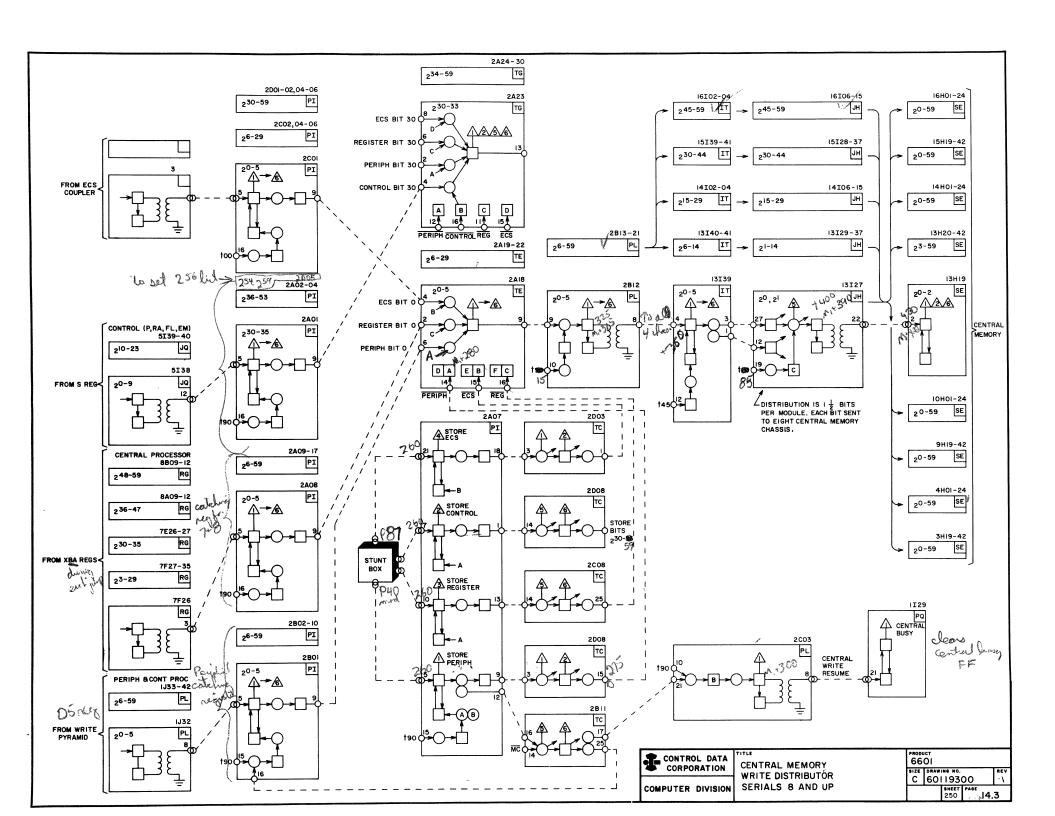

| 12.2 | Write Distributor                                       |  |

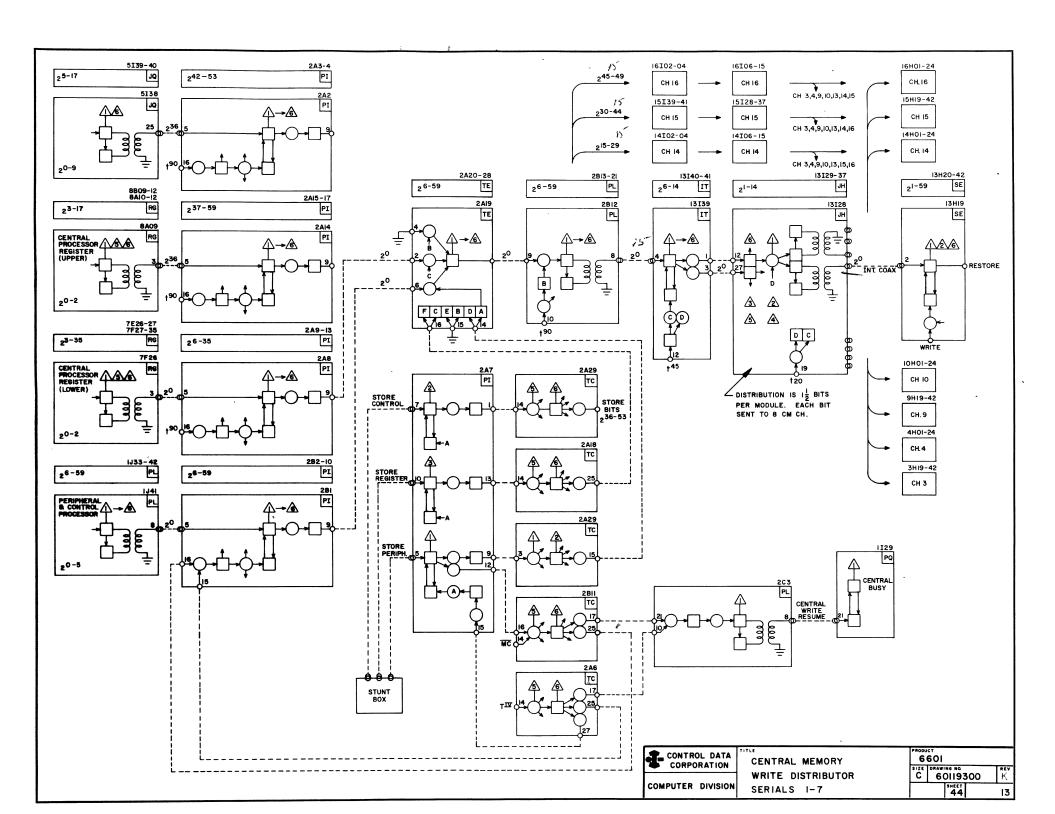

| 13   | Write Distributor, Serials 1-7                          |  |

| 14.0 | Write Distributor, Chassis 3, 4, 9, 10 (Test Points)    |  |