LSI-11 Compatible

# **BUBBL-MACHINE**<sup>™</sup>

Technical Manual for

# **QBC-11/02**

LSI-11 Compatible

## **BUBBL-MACHINE**

Solid-State Mass Storage System

6800 Sierra Court Dublin, CA 94568 Telephone: 415-829-8700 TWX/Telex: 910-389-6890

Copyright 1983

TABLE OF CONTENTS

|                                 |                                                                                                                                                                                                                                                                                                                                                                                         | Page Number                                                               |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| 1.0                             | DINTRODUCTION                                                                                                                                                                                                                                                                                                                                                                           | 1-1                                                                       |

|                                 | 1.1 IN CASE OF DIFFICULTY                                                                                                                                                                                                                                                                                                                                                               | 1-3                                                                       |

| 2.0                             | D INSTALLATION                                                                                                                                                                                                                                                                                                                                                                          | 2-1                                                                       |

|                                 | <ul><li>2.3 DEVICE ADDRESS SELECTION</li><li>2.4 INTERRUPT VECTOR ADDRESS SELECTION</li><li>2.5 BOOTSTRAP ADDRESS SELECTION</li></ul>                                                                                                                                                                                                                                                   | 2-1<br>2-2<br>2-5<br>2-6<br>2-6<br>2-6<br>2-7<br>2-7<br>2-7<br>2-8<br>2-9 |

| 3.0                             | O PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                           | 3-1                                                                       |

|                                 | <ul> <li>3.1 COMMAND AND STATUS REGISTER (RXCS)</li> <li>3.2 DATA REGISTER (RXDB)</li> <li>3.3 FUNCTION CODES</li> <li>3.4 SECTOR INTERLEAVING</li> <li>3.5 PROGRAMMING EXAMPLES</li> </ul>                                                                                                                                                                                             | 3-1<br>3-3<br>3-6<br>3-10<br>3-11                                         |

| 4.                              | 0 DIAGNOSTICS                                                                                                                                                                                                                                                                                                                                                                           | 4-1                                                                       |

|                                 | <ul><li>4.1 MANUALLY-INITIATED SELF-TEST</li><li>4.2 ODT-INITIATED SELF-TEST</li><li>4.3 LSI-11 HOST DIAGNOSTIC SOFTWARE</li></ul>                                                                                                                                                                                                                                                      | 4-1<br>4-2<br>4-4                                                         |

| 5.0                             | O OPERATION WITH RT-11                                                                                                                                                                                                                                                                                                                                                                  | 5-1                                                                       |

|                                 | <ul> <li>5.1 DEVICE HANDLERS</li> <li>5.2 DEVICE INITIALIZATION</li> <li>5.3 COPYING FROM FLOPPY DISK to BUBBLE MEMORY</li> <li>5.4 BOOTSTRAPPING RT-11</li> </ul>                                                                                                                                                                                                                      | 5-1<br>5-2<br>5-3<br>5-3                                                  |

| 6.0                             | O OPERATION WITH RSX-11                                                                                                                                                                                                                                                                                                                                                                 | 6-1                                                                       |

|                                 | <ul> <li>6.1 SUBSTITUTING A QBC-11/02 FOR AN EXISTING RX02</li> <li>6.2 ADDING THE QBC-11/02 TO A SYSTEM WITHOUT RX02'S</li> <li>6.3 ADDING THE QBC-11/02 TO A SYSTEM WITH RX02'S</li> <li>6.4 USING THE QBC-11/02 AS AN RXS-11S BOOT DEVICE</li> <li>6.5 CORRECTING FOR DEVICE SIZE DIFFERENCES</li> </ul>                                                                             | 6-1<br>6-1<br>6-2<br>6-2<br>6-2                                           |

| 7.0                             | O THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                   | 7-1                                                                       |

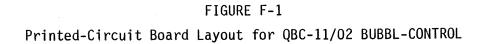

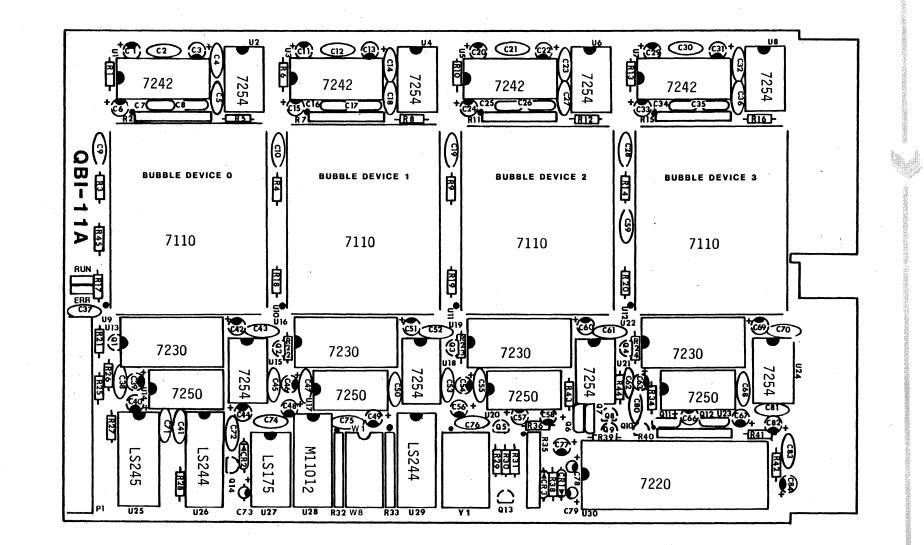

| API<br>API<br>API<br>API<br>API | PENDIX A: ADDING AN RT-11 HANDLER FOR THE QBC-11/02<br>PENDIX B: Non-RT-11 DEVICE HANDLER<br>PENDIX C: READING and WRITING BOOT LOOPS<br>PENDIX D: TECHNICAL SPECIFICATIONS FOR QBC-11/02 CONTROLL<br>PENDIX E: TECHNICAL SPECIFICATIONS FOR QBI-11 BUBBL-BOARD<br>PENDIX F: PRINTED-CIRCUIT LAYOUT FOR QBC-11/02 CONTROLLED<br>PENDIX G: PRINTED-CIRCUIT LAYOUT FOR QBI-11 BUBBL-BOARD | D E-1                                                                     |

## SECTION 1.0

#### INTRODUCTION

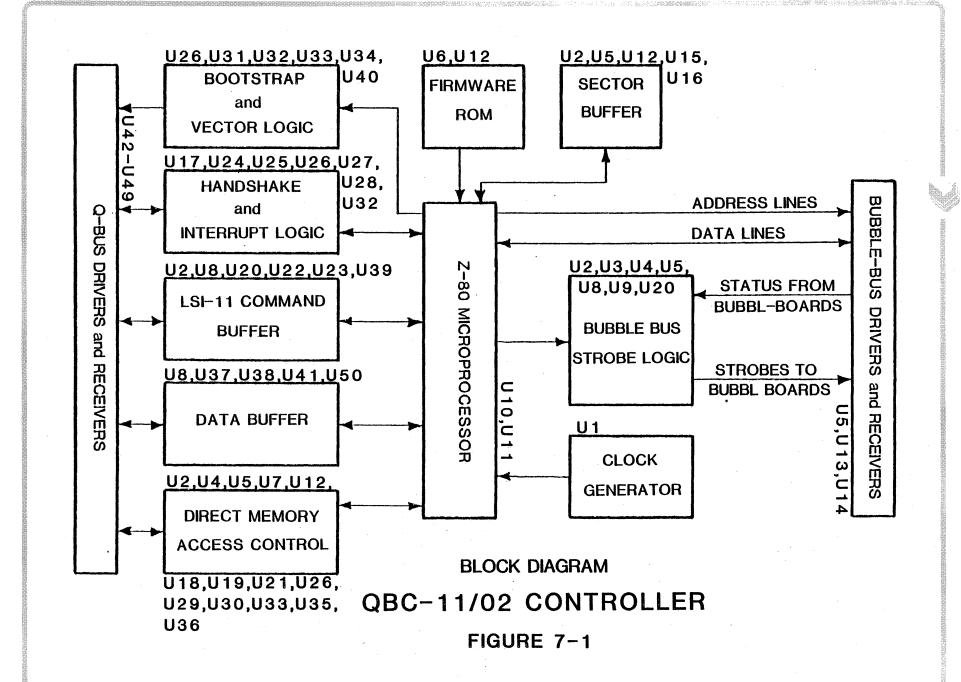

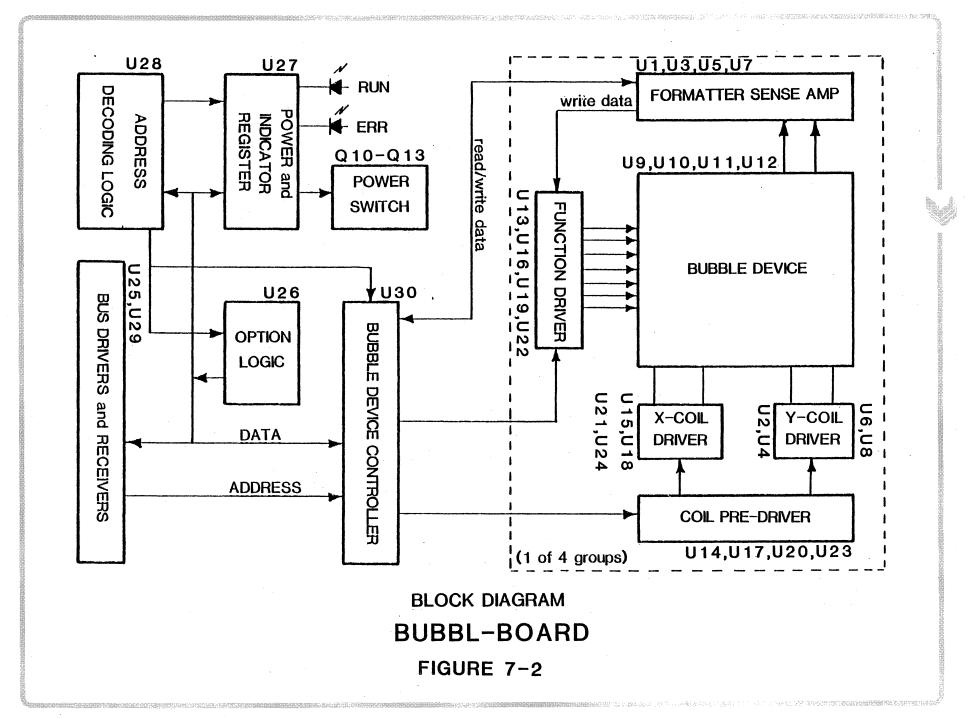

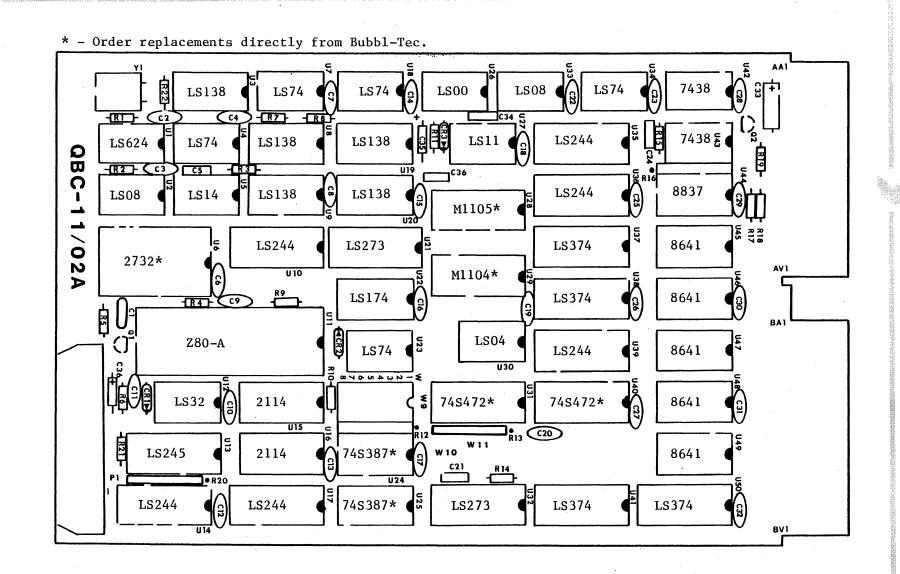

The QBC-11/02 BUBBL-CONTROL<sup>TM</sup> and its companion QB-series BUBBL-BOARDs form a complete non-volatile mass-storage system implemented on dual-height modules that plug directly into an LSI-11 computer system. Each QB-series BUBBL-BOARD can provide as much as 512 kilobytes of mass storage in an all-solid-state package, completely eliminating all external chassis, power supplies, moving parts and mechanical storage media. The QBC-11/02 BUBBL-CONTROL module can control as many as 16 BUBBL-BOARDs, providing up to 8 megabytes of on-line mass storage.

The QBC-11/02 plugs directly into the LSI-11 backplane bus. All required power (+5 and +12 volts only) is derived from the bus. The BUBBL-BOARDs include on-board power-switching circuitry which the QBC-11/02 controller uses to power-down any BUBBL-BOARD module which is not currently in use. This technique greatly diminishes the overall system power requirement, especially when system storage capacity is extended beyond 1 megabyte. Very little additional power is required when more than two QB-series BUBBL-BOARDs are used in the system.

The QBC-11/02 controller connects to the companion BUBBL-BOARDs via a 26-conductor ribbon cable. The BUBBL-BOARDs receive all their control signals from this cable, and therefore require no connection to the LSI-11 backplane except to receive power. As a result, the BUBBL-BOARDs can be externally mounted, if desired.

The QBC-11/02 is capable of operation in direct-memory-access mode, and is compatible with DEC's RT-11 and RSX-11 operating systems. The bubblememory system can be operated as either a system or non-system mass-storage device using DEC's standard "DY" floppy-disk handlers. The required bootstrap is stored in a PROM on the QBC-11/02 module, so no additional bootstrap module is required.

QB-series BUBBL-BOARD modules are removable and transportable without loss of data contained within the magnetic-bubble devices. Therefore, data can be moved from one machine to another simply by pulling a BUBBL-BOARD out of one machine and installing it in another.

The QBC-11/02 controller provides built-in self-diagnostics which can be invoked with simple ODT commands. The self-test mode is intended for use in acceptance testing, and as a field maintenance aid.

A green activity-indicator light (labeled RUN) on each QB-series BUBBL-BOARD indicates when the bubble devices on the module are being accessed. A red indicator labeled ERR illuminates if the controller ever detects an error in the bubble-stored data.

NOTE: DEC, LSI-11, RSX-11 and RT-11 are registered trademarks of Digital Equipment Corporation, Maynard, Massachusetts, USA.

### 1.1 IN CASE OF DIFFICULTY

If you have difficulty with your BUBBL-MACHINE system and/or decide to return one or more units to the factory for repair, you may do so after you have obtained a return authorization. <u>Please note that no merchandise returns</u> will be accepted without a prior return authorization having been issued. To obtain return authorization, simply call or write Bubbl-Tec and explain why it is necessary to make a return. You will then be promptly provided with the necesary Return Authorization Number.

When returning a module for repair, be sure to pack it properly in anticipation of rough handling in transit. Also, be sure you have prominently displayed the Return Authorization Number and your return address in at least <u>two</u> places on the <u>outside</u> of the shipping carton. Shipments not properly marked will not be accepted by the receiving department at Bubbl-Tec. Be sure to adequately insure your shipment, and prepay all necessary shipping and insurance charges. COD shipments will not be accepted at Bubbl-Tec.

When returning merchandise for repair, be sure to write a detailed letter to the attention of the Repair Department, describing the nature of the difficulties you have encountered. Also, include a purchase order or other memorandum authorizing us to perform the required work (warranty repairs are, of course, done without charge). Send this letter by AIR MAIL, so that it will arrive at the factory before, or coincident with, the arrival of the returned merchandise. Always mention the Return Authorization Number in your letter, and fully describe the merchandise you are returning for repair.

#### SECTION 2.0

#### INSTALLATION

The QBC-11/02 controller is intended to be installed in the card cage of the host LSI-11 microcomputer. It furnishes all required control signals for the companion QB-series BUBBL-BOARDs via a 26-conductor ribbon cable. To set up the bubble-memory system, the LSI-11 Device Address and Vector Address must be selected, the QB-series BUBBL-BOARDs must be properly strapped, and the power-down sequence must be checked. Each of these items is discussed below.

#### 2.1 POWER SUPPLY REQUIREMENTS

Power consumption for the QBC-11/02 controller and typical companion BUBBL-BOARDs is shown in Table 2-1. Regulation, sensing and filtering must be provided on the +5 and +12 volt power supplies to assure that they remain within +5% of their nominal values at all times while the system is operating.

The OBC-11/02 uses power-control circuitry on the BUBBL-BOARD modules to put them into power-down mode when they are not being accessed. The two most recently accessed BUBBL-BOARDs are always kept in standby mode (powered up, but not necessarily shifting bubbles). Bubbles are only shifted on one board at a time. When bubbles are shifted the module is said to be 'active'.

| Model      | Power | -down | Stan | d-by | Active |     |  |

|------------|-------|-------|------|------|--------|-----|--|

| Moder      | +5    | +12   | +5   | +12  | +5     | +12 |  |

| 0BC-11/02  |       |       |      |      | 1.4    |     |  |

| OBI-11/256 | 0.25  | 0.01  | 0.5  | 0.15 | 0.5    | 0.6 |  |

| OBI-11/512 | 0.25  | 0.01  | 0.6  | 0.25 | 0.6    | 1.2 |  |

TABLE 2-1

Current Consumption by Board Type (in amperes)

#### 2.2 POWER-UP and POWER-DOWN SEQUENCING

The QBC-11/02 controller executes a sequence of operations at power-up and power-down time which assures proper synchronization of the bubble storage medium. These special sequences are triggered by the BPOK H and BDCOK H signals on the LSI-11 bus, or (if these signals are not available) by powerfail detection circuitry on the BUBBL-BOARDs. The user must review his system's power supply circuitry to assure that either the BPOK and BDCOK bus signals are provided as described in Section 2.2.1, <u>or</u> his power supply provides sufficient "hold-up" at power-down time as described in Section 2.2.2.

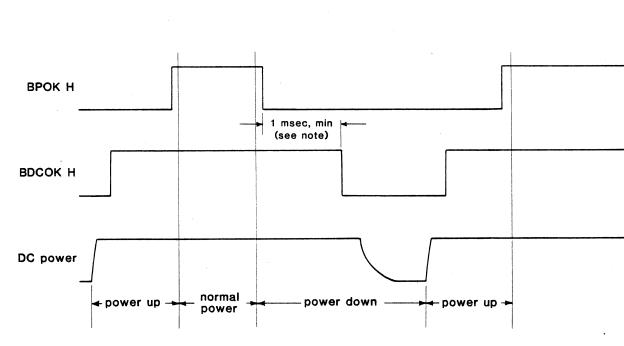

## 2.2.1 BPOK and BDCOK BUS SIGNALS

The normal power-up and power-down timing using a DEC power supply is shown in Figure 2-1. During power-up, the BDCOK signal is not asserted high until both the +5 and +12 volt supplies have stabilized at their nominal values. Then, after several milliseconds, the BPOK signal is also asserted high, indicating that AC power is stable. The circuitry on the QBC-11/02 controller is held in a reset state until both BPOK and BDCOK are asserted high, at which point (after an additional brief delay) it begins its initialization sequence.

At power-down time, the BPOK signal is de-asserted at least 1 millisecond before BDCOK is de-asserted, and DC power begins to go out of tolerance. (One millisecond is required by the QBC-11/02; DEC power supplies normally provide 4 milliseconds.) The QBC-11/02 detects the de-assertion of BPOK and completes all necessary power-down operations before DC power begins to drop out of tolerance.

On some LSI-11 systems a front-panel DC-power switch, or a switch labeled "INIT" or "RESTART", is provided that shuts off the DC-power regulators and forces the BDCOK bus signal low. This switch will not disturb proper QBC-11/02 operation if it either de-asserts the bus BPOK signal at least 1 millisecond before the DC supplies are shut off, <u>or</u> allows the DC supplies to gradually decay, as explained in Section 2.2.2, below. A DC power switch that crow-bars the DC supplies without first de-asserting BPOK, however, could potentially cause loss of all stored data in the bubble devices, as well as loss of the boot loops in the bubble devices themselves. (If the boot loops are ever lost, they must be restored by the procedures described in Appendix C.)

## 2.2.2 BUBBL-BOARD POWER-DOWN REQUIREMENTS

If the BPOK and BDCOK signals are not provided on the backplane bus, or if the QB-series BUBBL-BOARDs are to be operated with a power supply separate from that which powers the Q-bus backplane, the power-up sequence will begin as soon as power is applied to the QBC-11/02 controller, but will not complete until both the controller and BUBBL-BOARDs have proper power applied.

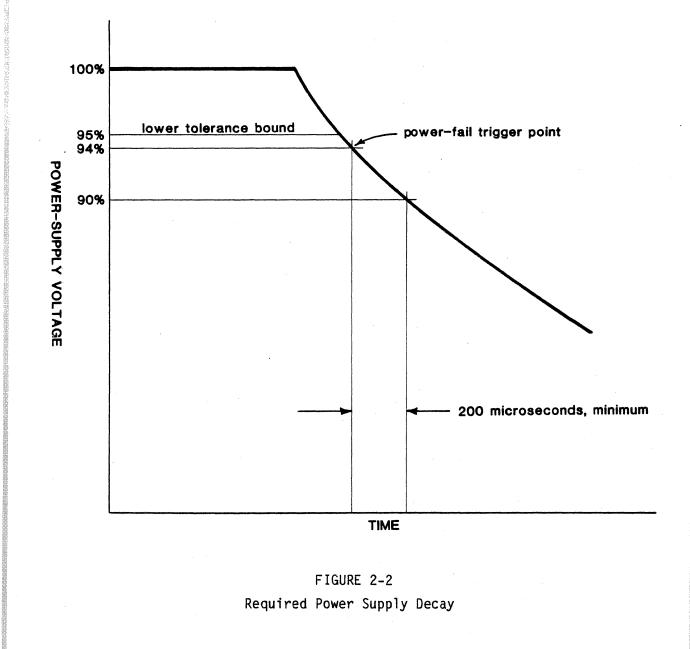

If either the +5 or +12 volt supply to the BUBBL-BOARDs falls below the 94% point during normal operation, it will be detected by special circuitry on each BUBBL-BOARD and the on-board device-control circuitry will begin it's power-down sequence. See Figure 2-2. This sequence takes a maximum of 200 microseconds to complete, and <u>it is mandatory that both the +5 and +12 volt supplies stay above the 90% point for this entire 200 microseconds after the power-down sequence begins.</u>

For LSI-11 systems that do not provide properly sequenced BPOK and BDCOK signals on the backplane bus, and for systems in which the BUBBL-BOARDs will be powered from a separate power supply, it is essential that the user check

the BUBBL-BOARD power supplies to be sure they provide the required 200-microsecond hold-up at power-down time, or stored date can be scrambled, and the bubble-device boot loops lost.

The 200-microsecond requirement should be easily met by any linear 5-volt supply if at least 2000 microfarads of output filter capacitance is provided per load amp. Similarly, the 12-volt supply should provide at least 1000 microfarads per load amp. Almost any linear supply should have more than enough output capacitance to satisfy these requirements.

The decay characteristic of switching-type power supplies varies greatly between designs, however, so the user of a switching supply should investigate the supply's power-down characteristics to assure that they meet the requirements shown in Figure 2-2. If necessary, additional output capacitance could be added to slow down the decay characteristic.

Pursuant to the above requirements, it is not advisable to remove or install either the QBC-11/02 controller, or any BUBBL-BOARD module, from/to the host equipment while any power supply voltage is on.

#### 2.3 DEVICE ADDRESS SELECTION

Before operating the QBC-11/02 controller for the first time, the proper device address must be set-up on the printed-circuit module. Four addresses are available: 177150, 177160, 177170 and 177174. The selection of one of these four addresses is accomplished by installing or removing shunts at positions W1 and W2, as indicated in Table 2-2. The QBC-11/02 is delivered with all shunts installed (closed). Appropriate shunts may be opened by cutting the narrow center of the shunt with a sharp instrument, such as a screwdriver.

|   |                                                                                                  |           |           | <u> </u>             |                      |                    |                |                      |                      |

|---|--------------------------------------------------------------------------------------------------|-----------|-----------|----------------------|----------------------|--------------------|----------------|----------------------|----------------------|

| - | SELECTED<br>FUNCTION                                                                             | <u>W8</u> | <u>W7</u> | W6                   | T POSIT<br><u>W5</u> | 10N<br><u>W4</u>   | W3             | <u>W2</u>            | <u>W1</u>            |

| - | Device Address 177170<br>Device Address 177150<br>Device Address 177160<br>Device Address 177174 |           |           |                      |                      |                    |                | CL<br>CL<br>OP<br>OP | CL<br>OP<br>CL<br>OP |

|   | Vector Address 000264<br>Vector Address 000270<br>Vector Address 000274                          |           |           |                      |                      | CL<br>CL<br>OP     | CL<br>OP<br>CL |                      |                      |

|   | Boot Address 173000<br>Boot Address 171000<br>Boot Address 175000<br>Bootstrap Disabled          |           |           | CL<br>CL<br>OP<br>OP | CL<br>OP<br>CL<br>OP |                    |                |                      |                      |

|   | RX01 Mode Operation:                                                                             |           |           |                      |                      |                    |                |                      |                      |

|   | With only 1 or 2 drives<br>With 3 or more drives                                                 | OP<br>CL  | CL<br>CL  |                      |                      |                    |                |                      |                      |

|   | RXO2 Mode Operation:                                                                             |           |           |                      |                      |                    |                |                      |                      |

|   | Single-sided Emulation<br>Double-sided emulation                                                 | OP<br>CL  | 0P<br>0P  |                      |                      |                    |                |                      |                      |

|   | CL = strap installed<br>(Also see Sections 2.6 and                                               | •         |           |                      |                      | p omitt<br>f jumpe | • •            |                      | )                    |

TABLE 2-2

Strap Options for QBC-11/02 Controller

The Device Address selects the address for the RXCS Command and Status Register. The RXDB Register is the next even address above the RXCS address.

The standard device address for the RXCS register when the bubble-memory system is used as the RT-11 system device is 177170. For a second controller or non-system device, 177150 or 177174 are the preferred device addresses.

The QBC-11/02 uses the LSI-11 Q-bus signal BBS7 L to enable the address decoder. This signal insures that the decoder only responds to addresses in the highest bank of memory. The bubble-memory system may be used with LSI-11 systems that generate extended address bits without making changes on the module.

## 2.4 INTERRUPT VECTOR ADDRESS SELECTION

Three interrupt-vector addresses can be selected on the QBC-11/02: 264, 270 or 274. The selection of the Vector Address is made by installing or removing shunts at positions W3 and W4 on the printed-circuit board, as indicated in Table 2-2.

The standard Vector Address for the controller when it is used as a system device is 264. When a second (non-system) controller is installed, the preferred Vector Address is 270.

#### 2.5 BOOTSTRAP ADDRESS SELECTION

The on-board RT-11 bootstrap is started at one of three memory addresses: 171000, 173000 or 175000. Selection is made by means of programmable shunts at positions W5 and W6 on the printed-circuit board, as shown in Table 2-2. Starting address 173000 should be used if the LSI-11 processor is strapped to boot automatically on power-up.

The bootstrap routine normally assumes that the address for the system device to be booted is 177170. The device address used by the bootstrap can be changed to 177150 by installing a jumper between wirewrap posts W11.

#### 2.6 RX01 MODE and DOUBLE-SIDED DISK EMULATION IN RX02 MODE

When shunt W7 is installed, the QBC-11/02 controller emulates an RXV11/RX01 floppy-disk controller. With shunt W7 open (as it normally will be), the controller emulates the RXV21/RX02 double-density floppy controller.

When operating in RXO1 mode, two logical drives are assigned to each 512K-byte QBI-11 Bubbl-Board module. If 256K-byte Bubbl-Boards are to be used, wire-wrap jumper W9 should be installed on the OBC-11/02 to make the

controller firmware assign logical drive numbers 0, 1, 2 (etc.) to Bubbl-Boards 0, 1, 2 (etc.), respectively.

If more than two Bubbl-Boards are to be used in the system, W8 should be installed to allow the use of the high-order byte of the track address to select the Bubbl-Boards, as shown in Figure 3-2. In this case, the software driver should be written to put the correct drive number in the upper half of the track word. Word-move instructions should be used to write the track address into the RXDB register. Byte-move instructions should <u>not</u> be used, because both bytes of the word-length RXDB register are strobed when either byte is written. If DEC's 'DX' (RXO1) drivers are to be used with jumper W8 installed, they will require revision to accomodate more than two drives, and to insure that the upper byte of the track address is written properly.

When shunt W8 is installed, the QBC-11 emulates double-sided disk operation when running in RXO2 mode, and two 512-Kbyte BUBRL-BOARD modules are considered to be one logical unit. Double-sided operation should not be attempted when using 256-Kbyte BUBBL-BOARDs. Bit 9 (Side Select) of the RXCS Register is used as the least-significant board-address select bit. Shunt W8 is normally left open, i.e., single-sided operation is the default mode.

## 2.7 DIAGNOSTIC JUMPER

The wire-wrap jumper-post pair W10 is made available for diagnostic purposes. When jumper W10 is installed, the OBC-11/02 module will ignore commands sent to it by the LSI-11 host, and the internal write/read self-test function is invoked. The OBC-11/02 begins a continuous write/read test of the controller itself as well as all BUBBL-BOARDs to which it has access. If a data error is detected during these tests, the ERRor light on the offending BUBBL-BOARD will be illuminated. If a controller error is detected, the test will halt. See Section 4 for further discussion of the diagnostic self-tests.

## 2.8 INSTALLATION IN CARD CAGE

The QBC-11/02 can be installed anywhere in the LSI-11 Q-bus. However, care must be taken to insure that the Priority Interrupt Grant and Direct Memory Access (DMA) bus chains are not broken anywhere along the bus. Normally there must be a card in every slot lying between the CPU and cards that use interrupts or direct-memory-access.

The user should analyze the timing requirements of his system to determine the optimum placement of the QBC-11/02 within the interrupt-priority

and DMA-priority chains.

Due to the power-up and power-down sequencing required by the bubble devices, the QBC-11/02 module (and its companion BUBBL-BOARDs) should never be inserted into, or removed from, the LSI-11 system when power is present on the bus.

#### 2.9 BUBBL-BOARD JUMPERS

Each QB-series BUBBL-BOARD module must be set-up to respond to a unique board address, from 0 to F (hex). Up to 16 BUBBL-BOARD modules can be connected to one QBC-11/02 controller. The board address is selected by installing shunts at locations W1 through W4 on the BUBBL-BOARD printed-circuit board. W1 selects the least-significant address bit. A closed shunt sets a logical zero for that address bit. Thus, a four-position shunt with all positions installed (closed) selects board-address 0; opening W1 (only) selects board-address 1; etc..

When the system is operated in RXO1 mode, a 512-Kbyte BUBBL-BOARD module corresponds to two logical units (and a 256-Kbyte module corresponds to a single logical unit). All 512K-byte BUBBL-BOARDs should be assigned even addresses, and a maximum of eight BUBBL-BOARD modules is allowed in an RXO1-mode system.

When only two bubble devices are installed on the BUBBL-BOARD module, strap W6 is installed on the BUBBL-BOARD to indicate to the QBC-11/02 that the module has only 256 Kbytes of storage capacity. If only 256K-byte modules are to be used, they may be assigned both odd and even addresses if W9 is installed on the QBC-11/02 controller.

#### 2.9.1 STRAPPING FOR SINGLE BUBBLE-DEVICE OPERATION

In normal operation, no jumper should be installed at position W7 on the BUBBL-BOARD module, since this jumper is used for maintenance purposes only.

For diagnostic purposes it is sometimes desireable to operate each bubble device individually on a particular BUBBL-BOARD, in order to help isolate the cause of an operational problem. This is done by installing a shunt in position W7 to select single-device operation, and then selecting the desired bubble-device number with appropriate shunts at W5 and W6. W5 is the leastsignificant bubble-device selection bit. Again, an installed shunt selects a logical zero, so shunts installed at both W5 and W6 would select bubble-device number 0 on the BUBBL-BOARD; opening W5 (only) selects device number 1; etc.

## 2.9.2 STRAPPING FOR WRITE PROTECTION

For normal RT-11 (or other) operation, shunt W8 should not be installed on any BUBBL-BOARD. If the user wishes to write-protect a particular BUBBL-BOARD module, however, jumper W8 should be installed on that board. This will permanently inhibit writes to the bubble devices on that module, protecting any previously-stored data from being altered.

#### 2.10 ACCEPTANCE TESTING

Before operating the bubble-memory system for the first time, the user may wish to run a few preliminary checks to insure that it will operate properly in his system. To do this the QBC-11/02 module should be plugged into the Q-bus with the SELF-TEST shunt W10 installed (and all other QBC-11/02 jumpers omitted). One BUBBL-BOARD module should be installed in the Q-bus and connected to the controller using the ribbon cable provided. This BUBBL-BOARD should be configured as board-address 0 by installing shunts W1-W4. For a 512-Kbyte BUBBL-BOARD, all other shunts should be omitted. For a 256-Kbvte module, jumper W6 must also be installed. The LSI-11 system can then be The green RUN lamp on the BUBBL-BOARD should come on briefly and powered up. The internal self-test firmware will exercise all logic on the then go out. BUBBL-BOARD (turning the RUN lamp back on), and will turn on the ERRor lamp if the controller detects an uncorrectable error. The system should be run in this mode for several minutes to be sure that the system is running properly. If the system refuses to run as described, it usually indicates a controller error, or that the operator has not set the system up correctly.

After running the preliminary self-test, the user should power down the system, remove the SELF-TEST shunt, and then set up the OBC-11/02 for the desired device address, vector address, bootstrap address, etc. as discussed above. When the system is then again powered up, there will be a brief illumination of the RUN lamp on the BUBBL-BOARD. When the RUN lamp goes out, the controller has completed its initialization process. LSI-11 console ODT can then be used to access the RXCS register at the device-address location. The RXCS should contain  $04440_8$ . The RXDB register, which is located at the next higher (even) address, should contain  $244_8$ .

After successfully completing the above checks, the hardware should be ready for operation in the user's system.

## SECTION 3.0

#### PROGRAMMING

The QBC-11/02 bubble-memory controller is designed to respond to the same command protocol as DEC's RXV21/RX02 floppy-disk controller. The QBC-11/02 contains a Command and Status Register (RXCS), and a Data Register (RXDB). These registers serve as communication paths between the LSI-11 and a Z-80 microprocessor located on the controller module. The Z-80 interprets the commands produced by the LSI-11 and controls the data transfers to and from the bubble storage medium.

This section, although not intended to be a general tutorial on massstorage controller operation, will define the function of each bit in the Command and Status Register, and the sequence of commands that is expected by the Z-80 for correct system operation.

The QBC-11/02 can be strapped so that it emulates either an RX01 (single density) or RX02 (double density) floppy-disk system. Because of the inherent advantages, we will assume in this section that the controller is configured to emulate an RX02. Contact Bubbl-tec if you must run in RX01 mode and you do not have access to RX01 programming information.

#### 3.1 THE COMMAND AND STATUS REGISTER (RXCS)

Whenever a command is written into the RXCS register the DONE flag is cleared. The clearing of the DONE flag is sensed by the Z-80, which reads the RXCS register and performs the desired function. Note that if the RXCS is written into by the LSI-11 while the Z-80 is executing a function, the new command will be ignored. Bits 0 through 3 and bits 12-14 are write-only bits, i.e., they can be written but not read by the LSI-11. Bits 5, 7, 11 and 15 are read-only bits for the LSI-11. Bit 6 is a read/write bit. Both bytes of the RXCS are written whenever either byte is written by the LSI-11. Bits 5, 7, 11 and 15 of the RXCS are writeable only by the Z-80 on the QBC-11/02 module. Bits 4, 8 and 9 are writeable by the LSI-11 and are readable at the completion of a function (when DONE is set).

The format for the RXCS register is shown in Figure 3-1. Except for the

Interrupt Enable and Transfer Request bits, none of the bits read by the LSI-11 should be considered asserted unless the DONE bit is also asserted.

| <u>, 1</u> | 5  | 14         | 13         | 12 | 11   | 09          | 08  | 07 | 06         | 05   | 04          | 03 | 02     | 01 | 00 |

|------------|----|------------|------------|----|------|-------------|-----|----|------------|------|-------------|----|--------|----|----|

| E          | RR | RX<br>INIT | E X<br>ADD |    | RX02 | SIDE<br>SEL | DEN | TR | INT<br>ENB | DONE | UNIT<br>SEL | FI | UNCTIO | DN | GO |

## FIGURE 3-1

RXCS Register Format

Definitions of the RXCS bits are:

| BIT<br>NUMBER | NAME                | DEFINITION                                                                                                                                                                                                                                                                                          |  |  |  |

|---------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0             | GO                  | Must be set to enable Function Codes in bits 1-3.                                                                                                                                                                                                                                                   |  |  |  |

| 1-3           | FUNCTION            | Defines operation to be performed by QBC-11/02 controller,<br>as follows (left-hand bit in CODE column below is bit 3;<br>right-hand bit is bit 1):                                                                                                                                                 |  |  |  |

|               |                     | CODEFUNCTION000Fill Sector Buffer001Empty Sector Buffer010Write a sector of data into bubble memory011Read a sector of data from bubble memory100Diagnostic and power-control functions101Read status from RXES register110Write a deleted data sector mark (not implemented)111Read Error Register |  |  |  |

| 4             | UNIT                | This bit is used to select Drive #0 or Drive #1 in the RXO2<br>floppy-disk system. See the description of the Read Sector<br>and Write Sector functions in Section 3.3 for information<br>on selecting 'drives' 2 through 15.                                                                       |  |  |  |

| 5             | DONE                | If=0, the controller is busy.<br>If=1, the controller has completed a function.<br>This bit is cleared whenever anything is written into the<br>RXCS register by the LSI-11, and may be set or cleared by<br>the QBC-11/02 controller.                                                              |  |  |  |

| 6             | INTERRUPT<br>ENABLE | If=1, an interrupt will be generated when DONE is asserted.                                                                                                                                                                                                                                         |  |  |  |

| <br>  |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | TRANSFER<br>REQUEST | If=1, the controller is ready to receive data from, or send data to, the LSI-11 via the RXDB register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8     | DENSITY             | For an RXO2, this bit determines the density of the disk-<br>ette being accessed. For the QBC-11/02, this bit must be<br>set for all READ, WRITE, FILL BUFFER, and EMPTY BUFFER func-<br>tions. It is a read/write (R/W) bit, only valid when DONE<br>is set, and will always read 1.                                                                                                                                                                                                                                                                                                                                 |

| 9     | SIDE SEL            | When double-sided-disk emulation is enabled via jumper W8,<br>two BUBBL-BOARD modules constitute one logical unit. Bit 9<br>then becomes the least-significant board-address select bit.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10    | Unused              | To be RXO2 compatible, always write as O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11    | RX02                | Read-only bit which identifies the device as an 'RXO2'.<br>Always set for the QBC-11/02 in RXO2 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12-13 | EXT ADDR            | Two most significant bits (write-only) of the starting DMA address for data transfers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14    | INITIALIZE          | Asserting this bit will initialize the bubble-memory system<br>without initializing other LSI-11 devices. This software<br>INIT performs the same function as a hardware INIT received<br>from the Q-bus. DONE will first be negated, and the con-<br>troller will initialize the bubble devices to determine the<br>current position of the bubble pages. Sector 1, Track 1<br>will then be read into the sector buffer. The QBC-11/02<br>controller will then assert DONE and set the BUBBLE READY<br>and INITIALIZE DONE bits in the RXES register. The RXES<br>contents will then be placed in the RXDB register. |

| 15    | ERROR               | When this bit is asserted by the QBC-11/02 controller, an error has occurred during a command execution. This bit will be cleared when another command or an INIT pulse is                                                                                                                                                                                                                                                                                                                                                                                                                                            |

## 3.2 THE DATA REGISTER (RXDB)

1 Berger

The RXDB Data Register serves as the data path between the LSI-11 and the Z-80 on the QBC-11/02 controller module. Two 16-bit registers are actually used, one that can be written by the LSI-11 and read by the Z-80, and one that can be written by the Z-80 and read by the LSI-11. The LSI-11 address of the RXDB is always the next even-numbered address above that of the RXCS register.

sent to the QBC-11/02 controller.

Different information will be placed in the RXDB register at different times depending upon the function that is being executed. During the Fill Buffer and Empty Buffer functions, starting address and word count are transferred between the LSI-11 and the Z-80 via the RXDB. During the Write and

Read Sector functions, the sector and track addresses are sent to the Z-80 from the LSI-11 through the RXDB. For the Read Status function, the RXES Status Register is placed in the RXDB by the Z-80. For the Diagnostic Function, parameters defining the diagnostic operation to be performed are placed in the RXDB register as described in Section 4.2. At the end of execution of each function, the RXES Status Register contents are loaded into the RXDB to be read by the LSI-11.

The formats for the data transfers and track and sector addresses are shown in Figure 3-2:

| 15        | 14 | 13          | 12           | 11  | 10 ·              | 09           | 08    | 07             | 06           | 05           | 04         | 03           | 02                | 01  | 00 |

|-----------|----|-------------|--------------|-----|-------------------|--------------|-------|----------------|--------------|--------------|------------|--------------|-------------------|-----|----|

| 4         |    |             |              |     |                   | - MEI        | MORY  | ADDR           | ess —        |              |            |              |                   |     |    |

|           |    |             |              |     | Format            | for          | RXBA  | DMA            | Memor        | y Addi       | ress       |              |                   |     |    |

| <u>15</u> | 14 | 13<br>BOARD | 12<br>NIIME  |     |                   | 09           | 08    | 07             | 06           | 05<br>TRACK  |            | 03<br>ESS (( | $\frac{02}{0-76}$ | 01  | 00 |

|           |    | DOMUD       | NORL         |     | ***************** | at f         |       | a 40.000 April | rack A       |              |            |              | 5-70)             |     |    |

| •         |    |             |              |     | FORM              | al 10        | JP RA |                | ack A        | uures        | <b>.</b>   |              |                   |     |    |

|           |    |             |              |     |                   | ÷            |       |                |              |              |            |              |                   |     |    |

| 15        | 14 | 13          | 12           | 11  | 10                | 09           | 08    | 07             | 06           | 05           | 04         | 03           | 02                | 01  | 00 |

| 4         |    | <u> </u>    | <u>OT US</u> | SED |                   |              | ->    | 4              |              | - WOI        | RD CO      | UNT ((       | 0-128             | ) — | -> |

|           |    |             |              |     | Four              | . <b>.</b> £ |       |                |              |              | - <b>-</b> |              |                   |     |    |

|           |    |             |              |     | FOrme             | di ri        | or KX | WC DN          | 1A Wor       | d Cour       | ΤĊ         |              |                   |     |    |

| 15        | 14 | 13          | 12           | 11  | 10                | 09           | 08    | WC DN<br>07    | 1A Wor<br>06 | d Cour<br>05 | 04         | 03           | 02                | 01  | 00 |

| 15        | 14 |             | 12<br>OT US  |     | •                 |              |       |                |              | 05           | 04         | 03<br>ADDRES |                   |     | 00 |

The Error and Status Register (RXES) is displayed in the RXDB at the completion of each function and after a Read Status function command. The format for the RXES Register is shown in Figure 3-3:

| 15 | 14    | 13         | 12 | 11  | 10         | 09        | 08   | 07         | 06 | 05         | 04         | 03       | 02 | 01            | 00         |

|----|-------|------------|----|-----|------------|-----------|------|------------|----|------------|------------|----------|----|---------------|------------|

| -  | _ LAS | ST<br>TION |    | NXM | WC<br>OVFL | HD<br>SEL | UNIT | BUB<br>RDY | DD | DRV<br>DEN | DEN<br>ERR | AC<br>LO | ID | SIDE 1<br>RDY | DAT<br>ERR |

## FIGURE 3-3

RXES Register Format

The definitions for each of the applicable RXES bits are:

| BIT    |                 |                                                                                                                                                                                                                                           |

|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUMBER | NAME            | DEFINITION                                                                                                                                                                                                                                |

| 00     | DATERR          | When set, an uncorrectable data error has been detected<br>during the reading of a sector of data from bubble memory.<br>The ERROR and DONE bits are set in the RXCS register. (For<br>DEC RXO1 systems, this bit is called "CRC Error".) |

| 01     | SIDE 1<br>READY | When double-sided disk emulation is enabled by jumper W8, this bit will be set.                                                                                                                                                           |

| 02     | ID              | The INITIALIZE DONE bit is set after the completion of the<br>INIT function which occurs after power-up or when either a<br>software or a hardware (bus) INIT is received by the con-<br>troller.                                         |

| 03     | AC LO           | Set when a power failure is detected by the QBC-11/02.                                                                                                                                                                                    |

| 04     | DEN ERR         | Set when a READ, WRITE, FILL, or EMPTY is attempted without the RXCS DENSITY bit set.                                                                                                                                                     |

| 05     | DRV DEN         | Always 1.                                                                                                                                                                                                                                 |

| 06     | DD              | The DELETED DATA bit used in RXO2 floppy-disk systems will always be set to 0 by the QBC-11/02.                                                                                                                                           |

| 07     | BUBRDY          | The BUBBLE READY bit will be set whenever the bubble-memory<br>system is ready for operation. This bit is valid only<br>after a Read Status or INIT function. (For DEC RXO2 sys-<br>tems, this bit is called "DRVRDY".)                   |

| 08    | UNIT    | The least-significant bit of the selected BUBBL-BOARD number.                                                                                   |

|-------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 09    | HD SEL  | When double-sided disk emulation is enabled by jumper W8,<br>the side selected for the last function executed will be<br>indicated by this bit. |

| 10    | WC OVFL | Set when a FILL or EMPTY buffer command is attempted with a word count larger than the sector size.                                             |

| 11    | NXM     | Set when any DMA operation detects non-existent memory.                                                                                         |

| 12-15 | CMD     | These bits echo the last function executed by sending back the four least-significant bits of the RXCS Register.                                |

#### 3.3 FUNCTION CODES

A 3-bit function code is sent to the controller in bit positions 03, 02, and 01 when the RXCS is written by the LSI-11. Bit 00 must also be set to enable the Z-80 to perform the function. The function codes are described below. (Refer also to Section 3.1.)

## 3.3.1 FILL BUFFER (000)

Before a sector of data can be written into bubble storage, the Sector Data Buffer on the QBC-11/02 controller must be loaded with the 128 sixteenbit words of data. This is accomplished with the Fill Buffer function.

When the controller receives a Fill Buffer command, it negates DONE and asserts the Transfer Request (TR) flag in the RXCS register. The LSI-11 senses the TR flag and loads the word count into the RXDB, clearing the TR flag in the process. The word count is normally 128 for a full sector transfer. The Z-80 senses the clearing of the TR flag and stores the count internally. It then re-asserts the TR flag. The LSI-11 then sends the 16 leastsignificant bits of the starting DMA address for the data transfer, which clears TR. The Z-80 then fills the Sector Buffer from memory. If the word count is less than 128, zeroes fill the remainder of the buffer. The DONE flag is then asserted by the Z-80, signifying completion of the function.

## 3.3.2 EMPTY BUFFER (001)

This function transfers data from the Sector Buffer to the host. Word count and starting address are sent via the RXDB as for FILL BUFFER function.

## 3.3.3 WRITE SECTOR (010)

The Write Sector function transfers data from the Sector Buffer to the bubble device. When the QBC-11/02 controller receives a Write Sector command from the LSI-11, it negates the DONE flag and asserts the TR flag to request the sector address. When the LSI-11 loads the sector address into the RXDB register, TR is negated by the Z-80. The QBC-11/02 will then assert the TR flag again to request the track address.

The track address has a special format, since the QBC-11/02 can support sixteen 'units' instead of only two. The most-significant byte of the track address is interpreted as a 'board number' used to select the unit for data transfer. The QBC-11/02 logically OR's this byte with the Unit Select bit in the RXCS, so units 0 and 1 can be selected in the standard way. Do not use byte instructions (e.g., MOVB) to write the track address since the LSI-11 will write the same byte to both halves of the RXDB, usually resulting in erroneous BUBBL-BOARD selection.

After the LSI-11 loads the track address into the RXDB, the QBC-11/02 will check to see that the track address is greater than or equal to zero, and the sector address is in the range 1-26. It also checks to see that the combined track and sector address actually exists within the bubble-memory system. If any of these conditions is not met, the O4O error code is placed in the Error Register. The QBC-11/02 also checks to see if the selected BUBBL-BOARD actually exists in the system, and if it is write-protected (jumper W8 installed). If the BUBBL-BOARD does not exist, an O6O error code is placed in the Error Register. If the BUBBL-BOARD is write-protected, an O65 error code is placed in the Error Register. If any of the above three errors are detected, the ERROR flag is set in the RXCS register, and DONE is asserted. An interrupt is also generated if the Interrupt Enable bit is set.

If no errors are detected, the green RUN light will be turned on, and the QBC-11/02 controller will write the data into bubble storage. Four bubble devices are operated in parallel to store the 128-word sector in one 64-byte page of each bubble. An error-correction code is also written into each page of the sector.

After the data has been written to bubble storage, the QBC-11/02 controller turns off the RUN light, asserts the DONE flag, and generates an interrupt if the Interrupt Enable bit (bit 6) is set in the RXCS register. The contents of the Sector Buffer are not destroyed during the Write Sector operation.

## 3.3.4 READ SECTOR (011)

The Read Sector function is used to transfer information from bubble storage to the QBC-11/02 Sector Data Buffer. When the LSI-11 writes the Read Sector command into the RXCS register, the DONE flag is negated by the Z-80. The QBC-11/02 controller then asserts the TR flag twice, as in the Write Sector function, to obtain the sector address and then the track address for the read operation. The addresses are checked for out-of-range conditions as in the Write Sector function, and the DONE and ERROR flags are set if an error is detected. Also, if an addressing error is detected, an O40 or O60 error code will be placed in the Error Register.

If the address is within range, the QBC-11/02 controller reads the page corresponding to the specified sector-address from bubble storage, checking the data for errors as it is read. Correctable errors are automatically corrected. If an un-correctable error is detected, the QBC-11/02 will re-read the sector. This automatic retry will be repeated until either the sector is read without error, or the re-try count equals four. If after four retries an uncorrectable error is still detected, the RXES register contents (with the DATA ERROR bit set) are loaded into the RXDB register, and the DONE and ERROR flags are set in the RXCS register. If no errors are detected, the DONE flag is set, and an interrupt is generated if the Interrupt Enable bit is set in the RXCS register.

#### 3.3.5 POWER CONTROL and DIAGNOSTIC FUNCTIONS (100)

When the QBC-11/02 receives a function code four (100), it will assert the Transfer Request (TR) flag to get further information from the LSI-11. The LSI-11 processor should respond by placing in the RXDB either a diagnosticfunction select code as described in Section 4.2, or one of the two powercontrol select codes.

Normally, as explained in Section 2.1, only two (at most) BUBBL-BOARDs are powered up at any given time. However, each time a BUBBL-BOARD is brought from the powered-down state to the standby state, it must be re-intialized by the controller. Since the initialization process takes as much as several hundred milliseconds, overall system speed can be enhanced by keeping more than two BUBBL-BOARDs in stand-by. The power-control commands make it possible to take advantage of this possibility - trading off additional power consumption to gain an increase in throughput.

To put a given BUBBL-BOARD in standby mode, the user should place the octal power-on code 400\*b+10 in the RXDB in response to the TR flag, where 'b' is the board address for the particular BUBBL-BOARD. The QBC-11/02 will then leave that BUBBL-BOARD powered up until a power-off code is received.

To turn power off on a given BUBBL-BOARD, the LSI-11 should place the power-off code 400\*b+11 in the RXDB in response to the Transfer Request flag.

Function code four (100) is also used to implement several diagnostic functions; see Section 4.2. Both the power-control codes and the diagnostic codes are non-DEC commands; they are intended for use only with bubble memory.

### 3.3.6 READ STATUS (101)

The Read Status command will cause the QBC-11/02 controller to place the contents of the RXES Error and Status Register into the RXDB. The RXES contents will contain information produced as a result of the last command executed by the QBC-11/02. The DONE flag is negated by the Z-80 when the LSI-11 loads the Read Status command into the RXCS register, and is reasserted by the controller after the RXES has been loaded into the RXDB. As usual, an interrupt will be generated if the Interrupt Enable bit is asserted when the DONE flag is set.

#### 3.3.7 WRITE DELETED DATA SECTOR (110)

The Write Deleted Data Sector function is the same as the Write Sector function. No deleted data marks are written by the QBC-11/02 controller.

## 3.3.8 READ ERROR CODE (111)

When the Read Error Code command is written into the RXCS by the LSI-11, the DONE flag is negated, and TR is asserted. The LSI-11 sends a starting address to the RXDB, and the QBC-11/02 dumps four words into memory. The first byte sent contains definitive error codes which are defined below. This error code is placed in the RXDB Register, DONE is asserted, and an interrupt is generated if the Interrupt Enable bit is set.

The error codes are:

| Code | Error                                      |

|------|--------------------------------------------|

| 001  | Correctable Read Error                     |

| 002  | Uncorrectable Read Error                   |

| 004  | BMC Timing Error                           |

| 010  | Initialization Error                       |

| 040  | Track and/or sector address out of range   |

| 060  | No such board (unit)                       |

| 065  | Addressed BUBBL-BOARD is write-protected   |

| 230  | DMA word count too large                   |

| 240  | Density error                              |

| 250  | Non-existent-memory (NXM) error during DMA |

| 260  | BUBBL-BOARD power bad                      |

The other information returned is:

| Word | <u>Bits</u> | Meaning               |

|------|-------------|-----------------------|

| 0    | 15-8        | Word Count            |

| 1    | 7-0         | Unit O Track Address  |

| 1    | 15-8        | Unit 1 Track Address  |

| 2    | 7-0         | Last Track Addressed  |

| 2    | 15-8        | Last Sector Addressed |

| 3    | 15-0        | Not used              |

## 3.4 SECTOR INTERLEAVING

In order to allow the LSI-11 to keep up with a rotating floppy disk during read and write operations, DEC's RT-11 floppy-disk handler provides 2:1 sector interleaving of the 26 sectors on each track, as well as a 6-sector track-to-track skew. The QBC-11/02, however, stops rotating the bubble device at the end of each sector transfer, and is ready to instantly access the next sector no matter how long the LSI-11 takes to fill or empty the Sector Data Buffer. To optimize throughput of the QBC-11/02, the sector addresses within the bubble device have been arranged by the Z-80 to correspond to a sector interleave as produced by the RT-11 handler.

Programmers using a non-RT-11 handler which does not incorporate sector interleaving should set the most-significant bit (bit 7) of the track-address byte passed to the QBC-11/02 during write-sector and read-sector operations. Setting this bit will cause the QBC-11/02 to bypass its interleave algorithms, thereby speeding operations with a non-RT-11 handler. See the example non-RT-11 handler in Appendix B.

## 3.5 PROGRAMMING EXAMPLES

Examples of the programming sequences required to fill the Sector Buffer, write a sector, read a sector, and empty the Sector Buffer may be found in the sample stand-alone driver described in Appendix B. More examples may be found in Chapter 3 of DEC's RXV21 Floppy Disk Operating Manual.

## NOTE

If you are using an LSI-11/23 or are writing your own device drivers, please note that the BIS and BIC instructions will not work on the QBC-11/02 registers as may be expected. This is because these commands use the DATIO bus cycle (read/modify/write) and most of the bits of the status registers are either read-only or write-only bits, as they are in the RXV21/RX01 floppy-disk system. Also, byte commands should not be used to write into the RXCS or RXDB.

## SECTION 4.0

## DIAGNOSTICS

Two levels of diagnostics are available to aid the user in assuring that the bubble-memory system is working properly. The first level is built into the QBC-11/02 firmware and does not require any LSI-11 host software. These "self-test" functions can be triggered by installing a jumper strap on the QBC-11/02, and powering up the module. Alternatively, self-testing can be started with LSI-11 console ODT commands.

If a self-test is started by installing the jumper strap, it is not even necessary that the QBC-11/02 module be installed in an LSI-11 system. Simply apply power to the printed-circuit board, and provide a pull-up on the BINIT L bus line (line AT2). An overall test result can be obtained by viewing the LED indicators on the attached BUBBL-BOARD(s).

A second level of diagnostics uses LSI-11 host software to test the entire system, including the interface to the Q-bus. Each of these diagnostic procedures will be described in this section.

#### 4.1 MANUALLY-INITIATED SELF TEST

To manually start a self-test, the user must install a shunt in location W10, and power up the module. The QBC-11/02 will light the green RUN led on BUBBL-BOARD 0, perform its normal initialization, and then start a write/read test using a random data pattern. The controller will sequentially test all BUBBL-BOARDs in the system starting with BUBBL-BOARD 1. The test first writes a pattern in all sectors of the bubble device, and then reads it back.

If an uncorrectable data error is detected, the red ERR light on the board being tested is turned on and left on. The RUN light is also left on to indicate that the error was a data error, and testing continues.

If a fatal error is detected, such as the Z-80 not being able to communicate with the bubble device controller on a particular BUBBL-BOARD, the ERR light will be turned on, the green RUN light will go out, and testing will cease on that BUBBL-BOARD. If neither the ERR nor RUN light <u>ever</u> comes on, the QBC-11/02 module is completely inoperative, with the Z-80 unable to execute any instructions.

The QBC-11/02 will ignore any commands from the LSI-11 host processor as long as the W10 shunt is installed.

## CAUTION!

The manually-initiated self-test destroys data in all BUBBL-BOARD(s) attached to the QBC-11/02. Use ODT or BUBL initiated self-tests if you want to test the system without losing previously-stored user data.

## 4.2 ODT-INITIATED SELF TEST

The QBC-11/02 firmware has a set of diagnostic routines which can be triggered by commands entered via the LSI-11 console ODT, or by higher-level software such as the BUBL diagnostic program described in Section 4.3, below. To initiate a diagnostic command, the user should send a function code 4  $(100_2)$  to bits 3 through 1 of the RXCS register with the GO bit (bit 0) set; i.e., send an octal O11.

The QBC-11/02 controller will respond by clearing DONE and then setting the Transfer Request flag. The user should then send the code word defining the specific diagnostic function, as listed in Table 4-1. If more parameters are required to further define the function, the QBC-11/02 will raise the TR flag for each parameter, until all are transferred. The DONE flag is set in the RXCS Register at the completion of each diagnostic function, and the RXCS ERROR bit is set if an error is detected during the diagnostic function that was executed.

NOTE

All data errors are classified as soft (automatically corrected by the controller simply by re-reading the data), correctable (automatically corrected by the controller hardware), or un-correctable. Only in the latter case has data actually been lost.

When operating the bubble-memory system at temperatures approaching the upper end of the specification range, it is normal for the correctable and/or soft data-error rate to increase. These errors are all automatically corrected by the controller, however, and are not cause for concern. Uncorrectable data errors will not normally be found within the specified temperature range.

| OCTAL<br>CODE      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0                  | READ ERROR LOG - Makes the 10-byte Error Log available for transfer<br>to the LSI-11 host processor, via the RXDB register. The Transfer<br>Request (TR) flag is asserted in the RXCS register for each byte to<br>be transferred. (NOTE: The Error Log is cleared at power-up.)                                                                                                                                                                                                    |  |  |  |  |

|                    | The Error Log bytes are:                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                    | Byte # Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|                    | 1-4 Number of sectors read since power-up. Byte 1 is least-significant byte.                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                    | 5-6 Number of sectors read having correctable (auto-<br>matically corrected) data errors. Byte 5 is LSB.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                    | 7-8 Number of sectors read having soft data errors (auto matically corrected by re-read). Byte 7 is LSB.                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|                    | 9-10 Number of sectors read having un-correctable data errors. Byte 9 is LSB.                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 400*b + 1          | READ-VERIFY TEST - Reads all sectors on the BUBBL-BOARD selected<br>by 'b'. At completion of an entire read pass, sets DONE flag.<br>Sets ERROR flag in RXCS register if any data error is detected.<br>Also turns on the red ERR light and updates Error Log if an error<br>is detected. This is a "read-only" (non-destructive) test.                                                                                                                                             |  |  |  |  |

| 400*b + 2          | 2 WRITE/READ TEST - Writes a random data pattern into every sector<br>on the selected board and then reads all sectors. At the comple-<br>tion of the test, the DONE flag is set. If any data error is de-<br>tected, the ERROR flag is set in the RXCS register. Turns on the<br>red ERR light and updates the Error Log if an error is detected.                                                                                                                                  |  |  |  |  |

| 400*b + 3          | BOOTLOOP READ FUNCTION - Reads the 40-byte boot map from the bub-<br>ble device and makes the 40 bytes available for transfer to the<br>LSI-11, via the least-significant byte of the RXDB register. The<br>TR flag is set for each byte to be transferred. Turns on the ERR<br>light and sets the ERROR flag in the RXCS register if an error is<br>detected. Sets DONE flag at completion. Hardware straps deter-<br>mine which device on board 'b' is accessed (see Appendix C). |  |  |  |  |

| 400 <b>*</b> b + 4 | BOOTLOOP WRITE FUNCTION - Accepts 40 bytes from the LSI-11, via the least-significant byte of the RXDB register. The TR flag is                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

DO\*b + 4 BOOTLOOP WRITE FUNCTION - Accepts 40 bytes from the LSI-11, via the least-significant byte of the RXDB register. The TR flag is set for each byte transferred. Then writes the 40 bytes into the boot-loop of the bubble device, and sets DONE flag. (Read Appendix C before using this function.)

WRITING THE BOOT LOOP SHOULD NOT BE ATTEMPTED WITHOUT A THOROUGH UNDERSTANDING OF THE PROCEDURES INVOLVED.

## TABLE 4-1

## Available Diagnostic Functions

## 4.3 LSI-11 HOST DIAGNOSTIC SOFTWARE

An LSI-11 diagnostic program called BUBL is provided with each QBC-11/02 shipment to a new customer, on an RT-11 compatible single-density floppy diskette. BUBL contains two routines to exercise the bubble-memory system, and facilitates using the diagnostic functions described in Section 4.2.

To run BUBL, load the diskette into floppy drive 1 after booting RT-11. Then type:

## RUN D?1:BUBL (? is either X or Y)

The program will respond by typing the list of commands that BUBL can execute, and will then print a '>' as a prompt, and await a command to be entered. The commands available are shown in Table 4-2. Legal abbreviations of the commands are shown as underlined letters. Multiple commands and parameters may be placed on a single line, separated by spaces. The commands will not be executed until a carriage-return is typed.

COMMAND

#### DESCRIPTION

| <u>S</u> HOW   | Displays a list of current parameters used by te | st routines. |

|----------------|--------------------------------------------------|--------------|

| <u>H</u> ELP   | Displays list of valid commands.                 |              |

| <u>Se</u> T    | Sets values in parameter list.                   |              |

| <u>C</u> 02BUB | Runs bubble diagnostic routine.                  |              |

| WIZBUB         | Runs bubble-memory reliability test.             |              |

| ĒRRLOG         | Prints 10-byte Error Log                         | (DIAG O)     |

| ROTEST         | Runs read-only data-verification test            | (DIAG 1)     |

| WRTEST         | Runs write-then-read self-test                   | (DIAG 2)     |

| RDMAP          | Reads and prints 40 bytes of hex boot-loop data  | (DIAG 3)     |

| <u>WRM</u> AP  | Accepts 40 bytes of hex data & writes boot-loop  | (DIAG 4)     |

#### TABLE 4-2

### **BUBL Commands**

When the SHOW command is typed, BUBL displays the list of parameters used by the test routines, with their current values:

| genalisine |                                                       |                  |              |                                   |            |           |

|------------|-------------------------------------------------------|------------------|--------------|-----------------------------------|------------|-----------|

|            | >S<br>VARIABLE                                        | VALUE            | USED BY      | VARIABLE                          | VALUE      | USED BY   |

|            | <u>R</u> XCS                                          | 177174           | C W          |                                   |            |           |

|            | UNIT                                                  | 0                | C W          |                                   |            |           |

|            | <u>F</u> IRST <u>T</u> RACK<br>LAST <u>T</u> RACK     | 0<br>0           | C W<br>C W · | <u>FIRST</u> SECTOR<br>LASTSECTOR | 1<br>1     | C<br>C    |

|            | <u>P</u> ASSES                                        | 1                | C W S        |                                   |            |           |

|            | CORRECT ERR<br>READ ONLY<br>RANDOM DATA<br>PRINT FLAG | T<br>F<br>T<br>T | C<br>C<br>C  |                                   |            |           |

|            | <u>PAT</u> TERN                                       | 0                | С            |                                   |            |           |

|            | C=C0                                                  | 2BUB             | W=WIZBUB     | S=Self-Tests (F                   | ROTEST and | I WRTEST) |