ELECTRONIC COMPUTER FOR ADDITION AND SUBTRACTION

Filed June 24, 1948

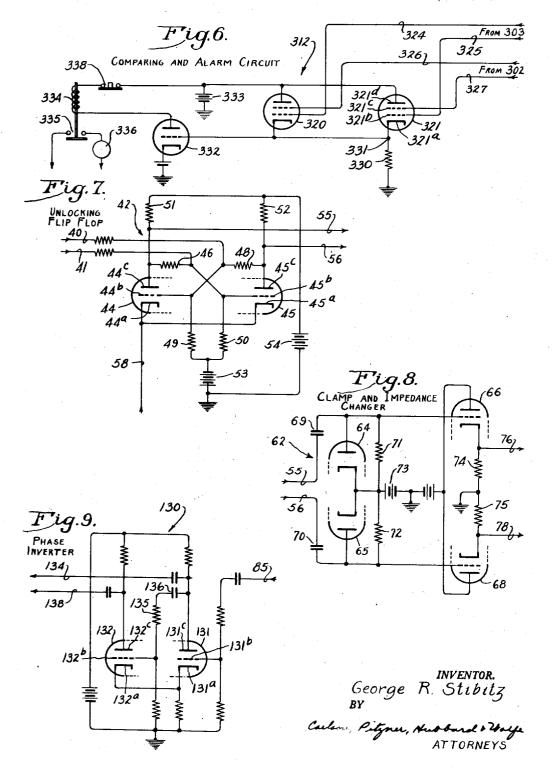

7 Sheets-Sheet 1

2,609,143

ELECTRONIC COMPUTER FOR ADDITION AND SUBTRACTION

<sup>7</sup> Sheets-Sheet 2

# Sept. 2, 1952

### G. R. STIBITZ

2,609,143

ELECTRONIC COMPUTER FOR ADDITION AND SUBTRACTION Filed June 24, 1948 7 Sheets-Sheet 3

# Sept. 2, 1952

ELECTRONIC COMPUTER FOR ADDITION AND SUBTRACTION

Filed June 24, 1948

7 Sheets-Sheet 4

ł BY D. \* ATTORNEYS

2,609,143

ELECTRONIC COMPUTER FOR ADDITION AND SUBTRACTION

Carlon, Pityan, Hubbard & Worfs ATTORNEYS

## Patented Sept. 2, 1952

# 2,609,143

## UNITED STATES PATENT OFFICE

#### 2.609.143

**ELECTRONIC COMPUTER FOR ADDITION** AND SUBTRACTION

George R. Stibitz, Burlington, Vt.

Application June 24, 1948, Serial No. 34,968

44 Claims. (Cl. 235-61)

The present invention relates to electronic digital computers and more particularly to a device for performing the addition or subtraction of binary numbers.

1

It is an object of the invention to provide an improved device for adding and subtracting binary numbers at a rate of speed which is far in excess of present day commercial calculators.

It is another object of the invention to provide an improved sequential computer in which binary 10 numbers are added by successive operation on each ordinal place with provision for automatically carrying a digit from one order to the next. It is a more specific object to provide a computer which acts in turn on each of the digits compris- 15ing a binary number, and which includes a novel delay circuit which is synchronized to cause a carried digit to be precisely delayed until the instant of summation of digits in the next high-20 est order.

It is still another object to provide an adding and subtracting device which is simple and inexpensive to construct, which is compact, and which may be advantageously utilized as a building block in the construction of computers for  $^{25}$ other mathematical operations, such as multiplication and division. Neither the mechanical nor the electrical components need be constructed with extreme precision and the electrical components are, for the most part, of the standard 30 type used in radio receivers. The number of tubes and other parts is small as compared to conventional computers of comparable speed.

It is a further object to provide an improved computer employing the binary system of num- 35 bers and utilizing devices having two stable conditions of operation in which the order of the two conditions or voltages to which the devices are subjected rather than any single instantaneous condition or voltage determines which of the two 40 binary digits is represented. As a result the computer may be made self-checking and of great accuracy in spite of relatively wide variations in voltage, phasing and wave form in the various portions of the circuit and notwithstand- 45 integrator circuit employed herein. ing changes in the electrical characteristics of tubes and other component parts.

It is a related object to provide a novel delay and comparing circuit for sounding an alarm whenever one of the two conditions comprising 50 ployed in the present invention. a digit is lacking.

It is a still further object to provide an improved means for the magnetic storage of information and a drive therefor which enables synchronization not only between various prob- 55 the main data signals. lem data but also with control impulses acting

upon such data and in spite of wide variations in driving speed.

It is an object to provide a computer of the sequential type which is capable of performing addition operations upon successive pairs of long binary numbers in rapid sequence without danger that a carry signal from the highest order in one sum will be carried over to the lowest order of the next sum. It is an allied object to provide a computer in which the complement of a binary number may be readily derived for purposes of subtraction and in which the complement is so compensated that the difference obtained is absolutely accurate regardless of the number of binal places the device may be equipped to handle.

It is an aim of the invention in one of its aspects to provide an improved summing circuit including alternative embodiments thereof which is capable of producing write and carry voltages in response to voltages representative of binary digits to be added and in accordance with the rules governing binary addition.

Other objects and advantages of the invention will become apparent upon studying the following discussion and inspection of the drawings, in which:

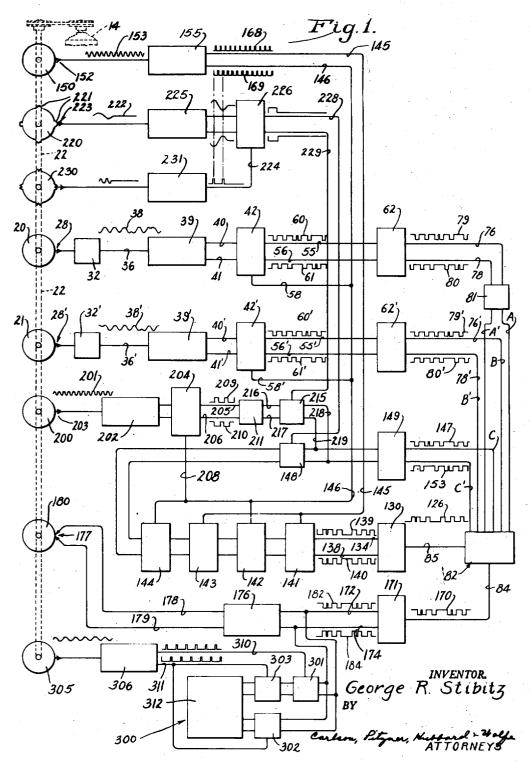

Figure 1 is a block diagram of a computer constructed in accordance with the present invention and suitable for adding or subtracting numbers stored in binary notation.

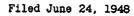

Fig. 2 is a fragmentary view of one of the storage disks disclosed in Fig. 1 and showing magnetic material distributed about the periphery thereof together with a cooperating recording or pickup head.

Fig. 2a is similar to Fig. 2 but shows the use of separate magnetic elements for storage purposes.

Fig. 3 is a fragmentary view showing the pulsing disk employed in Fig. 1.

Fig. 4 is a schematic diagram of a dual pulse generator controlled by the pulsing disk of Fig. 3. Fig. 5 is a schematic diagram of a preferred

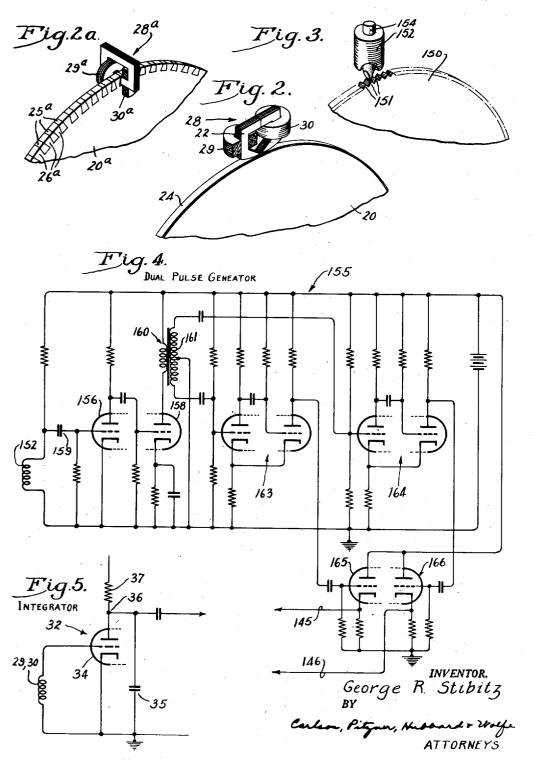

Fig. 6 shows a comparing and alarm circuit for detecting possible errors in the operation of the system of Fig. 1.

Fig. 7 shows a modified flip-flop circuit em-

Fig. 8 shows a clamping and impedance changing circuit.

Fig. 9 shows a preferred form of phase inverter used to produce an inversion or complement of

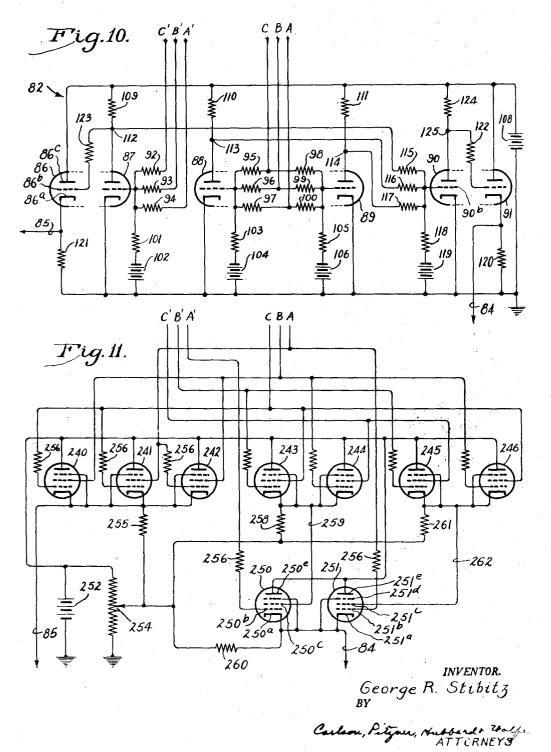

Fig. 10 discloses a summing circuit in accord-

#### 2

5

**3** ance with the present invention and employing three-element vacuum tubes.

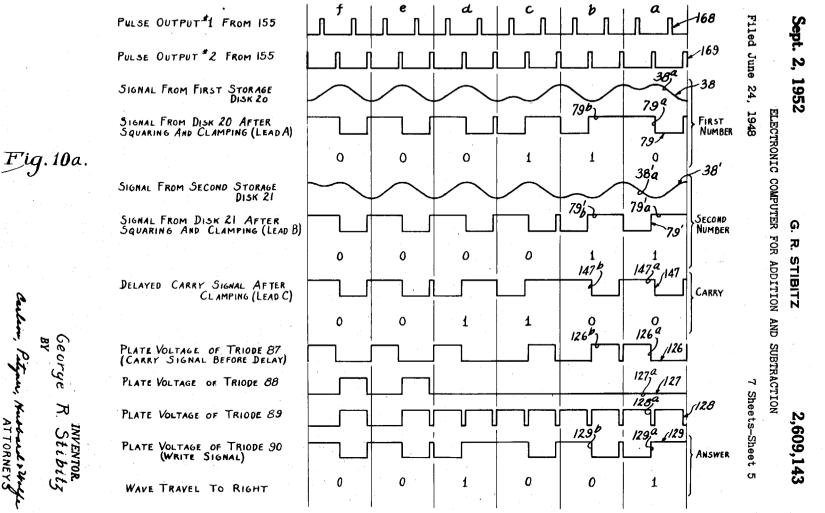

Fig. 10a is a set of wave forms existing at various significant points in the circuit of Fig. 10 and the system of Fig. 1.

Fig. 11 is an alternative summing circuit which differs from that of Fig. 10 in that multi-grid tubes are used.

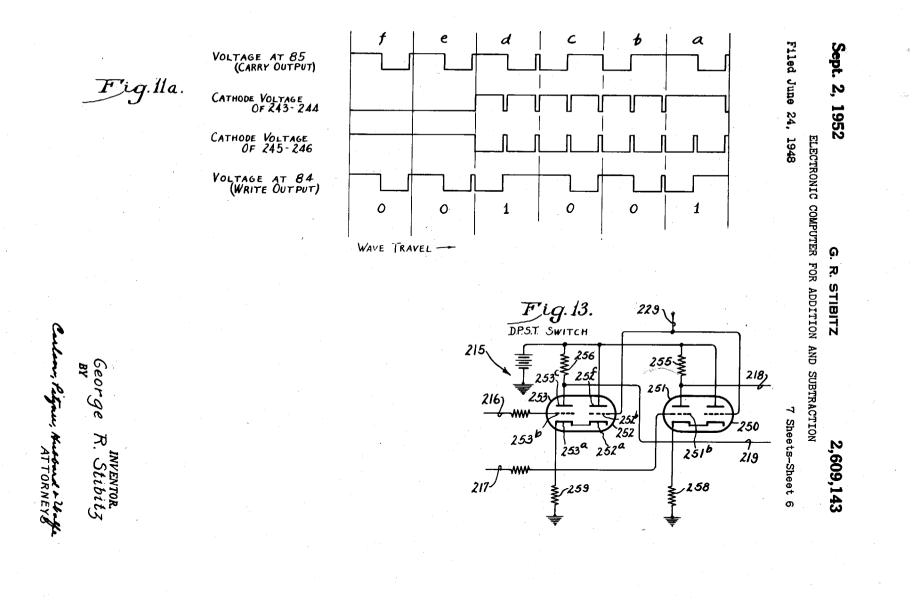

Fig. 11*a* is a set of wave forms of the same general type as shown in Fig. 10 but applicable to 10 the circuit of Fig. 11.

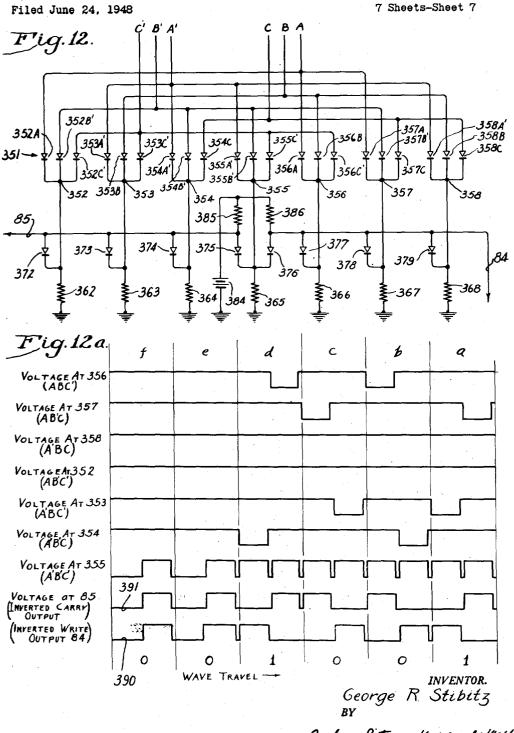

Fig. 12 is another alternative summing circuit. Fig. 12a is a set of wave forms for assistance in understanding the operation of the circuit of Fig. 12.

Fig. 13 is a double pole single throw electronic switch employed in the system for insertion of digits in the lowest order.

While the invention is susceptible of various modifications and alternative constructions and 20 uses, I have shown in the drawings and will herein describe in detail only certain preferred embodiments of the invention. It is to be understood, however, that I do not intend to limit the invention by such disclosure but aim to cover all modifications and alternative constructions and uses falling within the spirit and scope of the invention as expressed in the appended claims.

The computer to be described employs the binary system of numbers and it will be assumed <sup>30</sup> that such system is sufficiently well known to any persons skilled in the computer art as not to require discussion. Complete information on the binary system may be obtained from the various mathematical texts and texts concerning the <sup>35</sup> theory of numbers. As is conventional, the two binary digits employed will be referred to as 0 (zero) and 1 (one) in the discussion which follows.

Electronic computers employing binary numbers are known and have been useful for calculating trajectory and for solving other lengthy mathematical problems. They have for the most part been relatively complicated and expensive, requiring so many vacuum tubes and related components and occupying so much space as to be completely unsuited for use in the average business establishment. As a result, problems involving payroll calculation, the solution of engineering design problems, and the like have been performed either manually or by the use of computers of the mechanical or electromagnetic relay types.

One of the reasons for the inherent complexity of prior art electronic computers is the manner 55 in which the terms making up a lengthy binary number are treated. Conventionally binary computers have used two-condition devices such as flip-flop circuits in which each term of a binary number is represented by one of the two condi-60 tions. That is to say, representation of a lengthy binary number has required the use of a series of two-condition devices, one for each binary place. Since binary numbers have more than three times as many ordinal places as their deci-65 mal equivalents, the number of tubes required quickly reaches an impracticable level. Further, since tubes are subject to failure and erratic operation after extended periods of use, servicing is a difficult matter and it is almost impossible to 70 obtain continued accuracy without resorting to elaborate checking schemes.

In the computer to be discussed two-condition devices are used to represent each digit with the order of the two conditions determining which 75

binary digit is represented. Assuming that the digit is to be represented by plus or minus voltages on a certain lead, it has been found desirable to arbitrarily represent a binary 1 by a plus voltage followed at a predetermined interval by a minus voltage and, conversely, to represent a binary 0 by a minus voltage followed at a predetermined interval by a plus voltage. Novel means are provided for timing the computation so that there is no possibility of reading the second condition as the first condition of a pair. In order to simplify the description, this two-condition representation of a digit will be referred to as a "couple" or "wave." The terms "plus-minus couple" and "minus-plus couple" indicates the nature of the pulse, i. e., the direction of polarity change in pulses constituting a 1 and a 0 respectively on the main data leads. The two-condition couples may be stored in a variety of forms without departing from the invention. I prefer to store the couples magnetically.

One of the advantages of the manner of representing a digit as employed herein and as later covered in detail, is that it enables a simple and reliable check on each digit of the answer. Thus, if trouble develops at any point in the device which would cause one of the two condition devices to remain in one of its conditions, such fact is made immediately apparent, whereas in more conventional systems, failure of a single twocondition device simply produces an error in the answer without warning that an error existed.

As an additional characteristic, the device disclosed herein operates upon the terms of a binary number sequentially or serially rather than simultaneously. If it is assumed, for example, that two binary numbers are to be added, the computer, as a first step, adds the terms of lowest order (normally the first digit to the left of the binal point) progressing order by order to the highest term in each number. The lowest order digits of the two numbers are fed into a summing circuit. The sum of the two digits exists as a couple at the output of the summing circuit, the courle representing a digit which is then stored as the lowest order digit of the answer. There also appears at the output of the summing circuit a carry signal in the form of a couple the nature of which indicates whether a 1 or a 0 is to be carried to the next highest order. The sum of the digits in the next highest order is then obtained with the carry signal added thereto. The output of the summing circuit in the second operation is likewise in the form of a couple representing a digit which is recorded as the second term of the answer together with a carry signal which is added to the sum obtained in the third order. The summation of two binary numbers thus progresses until each term has been acted upon and the final answer is recorded. In the event that subtraction rather than addition is required, the device incorporates provision for obtaining the complement of the subtrahend, which is compensated in a particular manner, and thereafter performing the process of addition as outlined above.

The invention is also concerned with a novel means for storing the binary numbers to be operated upon and for recording the sum. Such storing means is of an improved form in which synchronization is substantially perfect not only as between the various storage and recording components but also with respect to the electrical circuit components. Further, synchronized means are provided for delayed insertion of the tarry signal obtained from the summation of the digits in one order into the sum of the digits of the next highest order. Delay circuits are employed in the latter which are unlocked at precisely synchronized intervals with respect to 5 functions performed by the remaining components and under optimum input conditions so that there is substantially no possibility of error.

Prior to discussing the complete computer shown in block form in Fig. 1, it will be helpful to 10 consider the various subcombinations into which It may be conveniently divided. Such subcombinations include (a) means for storing the binary numbers to be added or subtracted, (b) means for deriving a data signal in the form of couples 15 conditions. of alternating polarity and for shaping the same, (c) means including a summing circuit controlled by the couples and producing the answer in the form of couples at the output thereof, (d) a delay circuit for "carrying" from one order to the next, 20 and (e) means for storing the complete answer. As ancillary but none the less important features, provision is made for (f) producing timing or unlocking pulses, (g) for reversing the couples comprising a number to be subtracted thereby obtain- 25 ing its complement and (h) for eliminating difficulties caused by the "fugitive one" arising in both addition and subtraction. Finally there is provided an alarm circuit (i) of novel and improved design for detecting failure of the above 30 portions of the device to perform their intended functions.

The diagram of Fig. 1 has been simplified to facilitate understanding and bring out the operative relationships between the various subcom- 35 The circuit connections between the binations. blocks are intended primarily to show the routing of the control signals. Ground leads have been eliminated and it will be assumed that means are provided for supplying appropriate anode and 40 filament voltages to the vacuum tubes. Further, in the case of the blocks in Fig. 1, it will be understood that the circuits are disclosed from an operational standpoint and that circuit details may be added in a practical embodiment in accord-45 ance with established radio and electronic practice. Wave forms are represented at the significant points in the circuit as traveling waves to emphasize the continuous flow of intelligence from the data or input disk to the output or 50 answer disk. The waves shown denote the addition of two six digit binary numbers as will be more fully covered in a later section.

#### STORAGE OF BINARY NUMBERS

For purposes of ready understanding of the system it will be assumed that the computer will be fed directly from binary storage devices, such intelligence having previously been recorded thereon by any desired means. In the practice of the 60 invention each binary term is stored in the form of a magnetized area made up of successive spots of magnetism having unlike polarity and forming what may be termed a "magnetic couple." While it is possible to excite the computer by spots of 65 magnetism on any movable magnetic element, it has been found advantageous to store the intelligence on rapidly rotating disks having a magnetizable periphery. Referring now to the block diagram of Fig. 1, magnetic storage disks 20 and 70 21 are shown mounted on a shaft 22 which is rotated by a driving motor 14. The disks are preferably constructed as shown in Fig. 2 with a continuous strip 24 of retentive finely divided magnetic material bonded firmly to the circular body. 75.

55

6

Alternatively, the disks may be made as disclosed at  $20^{a}$  in Fig. 2a. In the latter construction the magnetic elements  $25^{a}$  are separated and held in place about the periphery by non-magnetic spacers or teeth  $26^{a}$ . In either embodiment, the disk body is preferably made of a non-magnetic material such as brass. In the case of the alternate embodiment, the elements  $25^{a}$  may be formed of sintered slugs of magnetizable material pressed into place or may be built up by spraying, using metal spraying apparatus commercially available. If desired, the slots containing the magnetic material may be undercut as shown in order to hold such material firmly in place under high-speed conditions.

The magnetic strip 24 may be magnetized by means of a recording head or armature 28 having a pair of coils 29, 30 mounted on a C-shaped magnetic core 22. During recording of data the two coils 29, 30 are preferably connected in the recording circuit in such a way that only one coil at a time will be energized. They are wound so that they tend to send flux in opposite directions around the magnetic circuit. Thus, as the disk 20 rotates and the strip 24 passes adjacent the pole faces, the magnetic material is subjected to a magnetizing force in one direction or the other depending upon which coil is energized. This results in spots of magnetism which are retained until it is desired to read them off.

In the case of the alternate embodiment, the recording head designated 28ª is also C-shaped and is equipped with coils 29ª, 30ª, but since the head is differently oriented, the magnetic elements are magnetized in a direction parallel to the axis of rotation of the disk. In operation an adjacent pair of magnetic elements 25° is employed to represent one binary digit, the first magnet of the pair having one polarity and the second magnet having the opposite polarity. In a practical embodiment it has been found convenient to store four binary numbers on a disk at one time. Assuming that each of such numbers is composed of up to twenty-five digits, two hundred individual magnets per disk are sufficient.

In reading the previously recorded numbers off the disk a pick-up head may be used which is identical to the recording head **28** or **28**<sup>a</sup>, the coils being connected in series to increase the magnitude of the voltage generated. As the magnetic spots pass adjacent the pole faces, they set up a flux in the core generating a voltage in the coils which is proportional to the rate of change of this flux.

#### DERIVING AND SHAPING OF PULSE COUPLES

In order to excite the summing circuit to be later discussed, it is desirable that the signal obtained from the storage disks 20, 21 be formed into a square wave voltage composed of couples of plus and minus pulses of alternating polarity corresponding to the polarity of the magnets on the disk.

As a first step in obtaining the desired wave form, the voltage generated in the head 28 is integrated to obtain a voltage which is proportional to flux and which, at any instant, has a polarity which is representative of the polarity of the magnetic spot lying adjacent the pole faces at that instant. The integrator for accomplishing this is indicated generally at 32 in Fig. 1 and set forth in greater detail in Fig. 5. Referring to the latter figure it will be seen that the coil 29. 30 is connected to the grid of a vacuum tube 34 having a capacitor 35 in shunt with the plate circuit thereof. The output of the tube 34 appears at the plate terminal 36, the tube being supplied from any suitable high-voltage source 5 through a load resistor 37. The capacitor 35 in conjunction with the tube resistance and load resistor 37 (which may be considered to be in parallel) serve as an RC integrator. The voltage across the capacitor is substantially the in-10 tegral, with respect to time, of the voltage applied to the circuit, or in this case, the voltage generated in the pickup coils. Stated another way, the voltage is substantially proportional to flux in the disk. Since the pickup coils are not required to carry current, any inductance drop therein is substantially eliminated and a high order of accuracy is achieved.

As indicated at 38 (Fig. 1) the wave at the output lead 36 of the integrator consists of a series of direct and reversed cycles of substantially sinusoidal shape. For convenience in representation the wave 38 may be thought of as traveling, here to the right, into the succeeding stages. This convention will be adhered to in all other wave representations to which reference is made. Assuming that a minus-plus wave indicates the binary digit 0 and assuming that a plus-minus impulse corresponds to the binary digit 1, it will be seen that the wave 38 at the output of the 20 integrator represents the binary number 000110, being the electrical equivalent to the number recorded magnetically on the disk 20.

Means are next provided for deriving a supplementary signal which is the inversion of the main control signal. Such inverted signal is fed along with the main signal but on a separate lead through the succeeding stages. In the present instance this is accomplished by a vacuum tube amplifier 39 which has a phase inverter stage to obtain push-pull output from a single Since such an amplifier may input signal. readily be constructed by one skilled in the art, it is not necessary to set forth the circuit in detail. Suffice it to say that the voltage wave existing at an output lead 40 will be the same as that existing at the input lead 36 except greater in magnitude while the voltage on a second output lead 41 is the inverted image thereof.

To convert the sine wave couples to square 50 wave couples and to obtain a uniform properly synchronized voltage wave for all digits regardless of the magnitude of the signal obtained from the disk, a flip-flop device 42 having provision for periodic unlocking is employed. The 55 circuit of the latter is set forth in Fig. 7 where it will be seen that it includes two triodes 44, 45 which may be included within the same envelope, if desired. Such triodes include cathodes 44<sup>a</sup>, 45<sup>a</sup>; grids 44<sup>b</sup>, 45<sup>b</sup>; and plates 44<sup>c</sup>, 45<sup>c</sup>, respectively. The circuit is arranged so that there are two stable conditions of operation: (a) with the grid 44<sup>b</sup> at zero potential and with grid 45<sup>b</sup> below cutoff, and (b) with the grid 45<sup>b</sup> at zero potential and grid 44<sup>b</sup> below cutoff. To this 65 end the grids and plates are cross-connected by resistors 46, 48 and respectively grounded through grid resistors 49, 50 and bias source 53. The triodes are fed respectively through plate resistors 51, 52 from a high voltage source 54. The 70 output of the flip-flop circuit is taken directly from the plates via output leads 55, 56.

When the first stable condition (a) exists, the triode 44 conducts and draws plate current from

voltage drop across the resistor 51 which decreases the potential of the output lead 55 relative to ground. Similarly, when the second condition (b) exists, triode 45 conducts to decrease the potential of the output lead 56 relative to ground. When the flip-flop circuit is in one of its stable conditions, it will remain in that condition due to the above-mentioned cross connection. Thus, if triode 45 is non-conducting, the potential of its plate will be high and due to its connection with the grid of triode 44 (through resistor 48) it will maintain the potential of that grid on the positive side of cut-off and cause the latter tube to conduct heavily. Conversely, 15 if triode 45 is conducting, it will maintain the grid of triode 44 beyond cut-off for the full range of voltages on input lead 40. To cause the flipflop circuit to remain locked in one condition, the output of the amplifier-inverter 39 is lim-20 ited to a moderate level.

8

In order to enable the flip-flop circuit to be converted from one stable condition to another. means are provided for unlocking the tubes, i.e., for rendering both tubes momentarily non-conducting. This is preferably accomplished by connecting cathodes 44<sup>a</sup>, 45<sup>a</sup>, by a line 58, to a source generating positive pulses synchronized with the signals received at the input leads 40, 41. The means for generating such pulses will be referred to in detail at a later point. Suffice it to say that a positive pulse applied to the cathodes makes both tubes non-conducting, and when such voltage is removed the tube which starts conducting will be determined by the then 35 existing voltage at the input terminals. The output voltage is independent of the input under normal locked conditions but may be considered to "aline itself" with the input voltage which obtains during the instant that the circuit is un-40 locked. It will be apparent to one skilled in the art that the present invention is not limited to the use of flip-flop circuits 42 having a pair of input leads and the circuit may be operated successively with one of the input leads eliminated. cessful with ine of the input condtions would The opposite grid under such conditions would receive its voltage only from the plate of the first tube.

Referring again to Fig. 1, it will be seen that the output signal from the flip-flop circuit 42 consists of a train of square waves 60 on lead 55 with their inverted counterparts 61 on lead 56. As stated above, all of the units in the block diagram have a common ground connection and it is therefore desirable that the signal voltage bear a predetermined relationship to ground potential. It is further desirable that the source be changed from high impedance to one of relatively low impedance for feeding into the summing portion of the device to be discussed. Accordingly, the dual signal is fed into a clamp and impedance changer 62, the circuit of which is set forth in detail in Fig. 8. This device includes a double diode 64, 65 and a double triode 66, 68. The diode circuits include input capacitors 69, 70 which are, in effect, shunted to ground through plate resistors 71, 32. It will be apparent, therefore, that the diode circuits serve as conventional clamping devices, maintaining the positive portions of the input signals at a positive potential determined by battery 73. The triodes 66, 68 are excited by the outputs of the clamping circuits and include cathode resistors 74, 75 across which the output is taken on leads 16, 78. The source 54 through resistor 51. This produces a 75 latter tubes thus serve as conventional cathode

7

followers. As a result of the clamping, the output waves 79, 80 of the device 62 have substantially the same envelope as the input signal but bear a definite relationship to ground potential.

In the above discussion only a single input channel has been discussed, namely, that leading from the disk 20. In order to obtain a sum it is, of course, necessary to have a second channel which is substantially the equivalent but which carries intelligence corresponding to a second 10 number. The second channel will be found in Fig. 1 directly below that previously discussed and corresponding primed reference numerals have been employed to indicate that the components are equivalent. Square output waves 79', 15 80' are also obtained for feeding into the summing circuit.

Included within the first channel is a reversing switch 81 which, as will later appear, is employed in subtraction and which for present 20 purposes may be disregarded.

#### DIGIT ADDER CIRCUIT

The apparatus thus far described has been for the purpose of obtaining reliable and accurately 25 phased square wave couples representative of a binary number. The purpose of the digit adder circuit indicated generally at 82 (Fig. 1) is to utilize such voltage couples to produce a sequence of couples on each of two output leads, one se- 30 quence representing the answer of the summation, and the other sequence representing a series of carry digits. The adder portion of the apparatus to be discussed utilizes three input voltages and their inverted counterparts, the first two of 35 such voltages being supplied from the channels controlled by the disks 20, 21. It will be found convenient to designate the main output wave of the first channel as A, its inversion as A' and the output of the second channel as B having an 40 inversion B'.

In practicing the invention three alternative circuits are provided as set forth in Figs. 10, 11 and 12 to act upon two simultaneously received input couples in a predetermined manner which  $_{45}$ satisfies the requirements of binary addition as the same is carried out order by order. Thus, if one of the input signals represents a binary 1, and the other 0, the summing circuit should write 1 and nothing should be carried over to the 50next higher order. If both of the inputs A (and its inversion A') and B (with its inversion B') carry a couple representative of a binary digit 1 the summing circuit should write a 0 and carry a 1. 55

In order to insert a carry signal from the previously summed order, a third input C having an inversion C' is employed. The couple fed to the summing circuit at C, C' is supplied from a novel delay circuit to which more detailed refer-60 ence will later be made. Suffice it to say that the carry signal always arrives at the input of the summing circuit just one order or cycle delayed or "late." Thus all three of inputs A, A'; B, B'; and C, C' may at any instant be carrying a couple 65 corresponding to a binary 0 or a binary 1. It will be apparent, then, that when all three inputs are a binary 1, both outputs should be a binary 1.

By this point in the discussion it will be clear that the function of the adder circuits, for ex- 70 ample that shown in Fig. 10, is to respond to the coincidence of voltages on the input leads. In the latter figure it will be seen that the six input leads may be divided into two sets of three cor-

grouped respectively A, B, C, and A', B', C'. The output leads include a write lead 84 and a carry lead 85. It will be understood hat the word "write" is used in a broad sense to indicate that the output signal on lead 84 is recorded as part of the sum. Preferably such recording is accomplished magnetically as will later appear. The actual printing of the information is not specifically covered in the present application.

The adder circuit as disclosed in Fig. 10 includes six valves in the form of triodes, adjacent ones of which are included within the same glass envelope. Such triodes are designated by the numerals 86-91. The cathodes, grids and plates of each of the triodes carry the corresponding numeral with the respective subscript a, b, or c. Referring in greater detail to the input portion of the adder circuit 82 it will be seen that the leads A', B', C' are all conneced to the control grid of the tube 87 through grid resistors 92, 93, 94. Similarly, the input leads A, B, C, are connected to the grids of the triodes 88, 89 through grid resistors 95, 96, 97 and 98, 99, 100. Each of the triodes 87-89 includes a source of bias comprising a grid resistor and grid battery which have been designated respectively by the numerals 101, 102; 103, 104; and 105, 106. The plates of the triodes 87-89 are connected to a source of high voltage 108 via dropping resistors 109, 110, 111. Because of the grid connections and the plate dropping resistors, the voltages existing at the plate terminals 112, 113, 114 swing through relatively wide limits determined by the signal voltages existing at the input. The tubes 87-89 may thus be conveniently referred to as "primary" control or input tubes.

In accordance with one of the aspects of the invention, the plate potentials of the primary control tubes existing at terminals 112, 113, 114 are applied through grid resistors to the grid 90<sup>b</sup> of a "secondary" control tube 90. Such resistors are designated 115, 116, 117 respectively. The grid 90<sup>b</sup> is further connected to a source of bias including a resistor 118 and a battery or the like 119. On the plate side, a dropping resistor 124 permits the plate terminal voltage to swing over relatively wide limits.

Through the action of the circuit thus far discussed, the voltages existing at the input leads are employed in combination to control the conductivity of the primary control tubes 87-89 while the resulting states of conductivity act jointly to control the conductivity in the secondary control tube 90 and the voltage at its output terminal 125. As shown in Fig. 10, the primary control tube 87 serves to control the conductivity in a carry output tube designated at 86 while the secondary control tube 90 controls the conductivity in a write output tube 91. The state of conductivity of such output tubes in turn determines the instantaneous potential on the write and carry output leads. Comp'eting the circuit, it will be noted that the output tubes have associated grid resistors 122, 123 and cathode resistors 120, 121 respectively, causing the stages to function as low impedance cathode followers.

In practicing the invention the bias on the grid of the primary control tube 87 is of such a value that it maintains the grid of triode 87 below cutoff unless two or more of the three leads A', B', C' are positive. Since the inverse voltages appear at the input leads A, B, C, this is equivalent to saying that the triode 87 is maintained beyond cut-off unless one or none of the leads A, B, C responding to the direct and inverted signals and 75 are positive. In order that the effect of such

40

45

bias condition may be ascertained at a glance, the following Table I has been prepared, listing the grid voltages and approximate plate voltages on all of the control tubes under the various combinations of input voltage at the input leads A, 5 Table I B. C.

11

12

positive at the beginning of a digit space. It is apparent that this fulfills one of the conditions of binary addition, namely, a binary 1 must be "written" only when the total of the numbers added is 1 or 3.

At first glance it might appear that the volt-

| Number of leads<br>A. B. C. which |      | 87              |      | 88              |      | 89                |             | 90        | <br>          |              |

|-----------------------------------|------|-----------------|------|-----------------|------|-------------------|-------------|-----------|---------------|--------------|

| A, B, C, which are positive       | Griđ | Plate           | Griđ | Plate           | Grid | Plate             | Grid        | Plate     | Write         | Carry        |

| D                                 | ZZ   | 10<br>10<br>105 | Czz  | 105<br>10<br>10 | CCC  | 105<br>105<br>105 | Z<br>C<br>Z | 10<br>105 | minus<br>plus |              |

| <b>5</b>                          | ę    | 105             | ž    | 10              | ž    | 105               | ő           | 10<br>105 | minus<br>plus | plus.<br>Do. |

Z=Zero, C=Cut-off.

For purposes of convenience Z has been used to designate the fact that a particular grid is at 20 zero potential (corresponding to flow of plate current). while C has been employed to designate the fact that a given grid is biased beyond cutoff thereby to prevent the flow of plate current. In a practical circuit using conventional receiv-25 ing-type triodes it has been found that a plate swing of from 10 to 105 volts is readily obtained between the conducting and non-conducting conditions respectively. These values have accordingly been used in the table as representative.

$\mathbf{30}$ In utilizing Table I it will be seen in the case of primary control triode 81 that the grid bias is zero and the plate voltage correspondingly low with none or one of the leads A, B, C positive; while the triode is cut-off and the plate voltage 35 correspondingly high when either two or three of the leads A, B, C are positive.

Turning attention now to the control triode 88, the bias derived from the source 104 is so adjusted that a positive voltage at any one of the leads A, B, C, is sufficient to cause the tube to conduct. When none of the leads A, B, C is positive, such tube is non-conducting and the plate terminal voltage is correspondingly high.

In the case of the primary control triode 89 the voltage of the associated grid battery 106 is of such value that all three of the leads A, B, C must be positive for conduction to take place. With less than three leads positive the tube is nonconducting and the plate voltage is high.

The function of the secondary control tube 90 50 differs from that of the control tubes previously discussed in that the grid 90<sup>b</sup> is controlled not by the input voltages directly but by the state of conductivity of the primary control tubes. To obtain the desired output signal the triode 90 has its 55 bias set by the battery 119 so that the tube is cutoff until two of the three leads supplying the grid network become appreciably positive. This is equivalent to saying that the secondary control tube 90 is cut-off unless at least two of the 60 primary control triodes are cut-off and, therefore, non-conducting. From inspection of the table, it is apparent that the secondary control triode will conduct only when none of the input leads A, B, C are positive or when two of such 65 leads are positive. Under conditions in which either one or three of the leads A, B, C are positive, the triode 90 is biased to cut-off and, therefore, non-conducting. The write output tube 91 is arranged to apply a positive voltage to the 70 write output lead **84** only when the secondary control tube 90 is non-conducting. Thus a write 1 signal will exist at the output lead 84 only under two conditions: When one of the leads A, B, C is

ages on the input leads would have very little individual effect due to the paralleling of the grid resistors 92-94, 95-97, and 98-100 respectively. It has been found as a practical matter that the arrangement shown causes the grid voltage to exist in desired well-defined steps and circuit complications encountered in any attempt to add the input voltages serially are avoided.

Referring now to the carry output tube 86 (at the left-hand portion of Fig. 10) it will be seen that a positive voltage will be applied to the carry output lead \$5 only when the primary control tube 87 is cut off. As will be apparent from the first column of the table a positive signal is produced at the carry output lead only when two or three of the input leads A, B, C are positive. Thus a carry 1 signal will be obtained only when two or three of the input leads A, B, C are positive for the first half of the cycle. This fulfills the second requirement for binary addition, namely, carrying (to the next highest order) whenever the binary sum exceeds 1. In short, the circuit of Fig. 10 satisfies the requirements for sequential binary addition except for delaying the carry signal until the next highest order is being summed.

#### DELAY CIRCUIT

In the preceding section it has been assumed that the appropriate carry signal derived from the summation in a previous order has been appropriately delayed so that it may be added to the signals existing at the A, A', and B, B' input leads. It has further been assumed that the carry signal appearing at the carry output lead 85 is suitably delayed to appear at the leads C, C' upon summing the signals corresponding to the binary digits of the next higher order. In accordance with the present invention, novel means are provided between the output lead 85 and the input lead C, C' for delaying the signal over a space of time corresponding to one couple, in other words, for one summing cycle. This is accomplished by providing a series of flip-flop circuits which are successively unlocked by pulses generated in accurately timed synchronization with respect to the stored data. As employed in the preferred embodiment illustrated in Fig. 1 the flip-flop circuits are of the same type previously discussed in connection with circuits 42 and 42' and set forth in detail in Fig. 7. It will be recalled that a positive pulse applied to the cathodes serves to unlock the circuit thereby enabling it to respond to the then existing voltage at its input terminals.

Prior to being fed through the flip-flop devices the signal on the carry lead 85 is inverted by positive or when three of the leads A, B, C are 75 means of a phase inverter 130. The specific circuit as set forth in Fig. 9 will be seen to be of more or less conventional design including a pair of triodes 131, 132 having cathodes, grids and plates carrying corresponding subscripts a, b, c. The grid [31<sup>b</sup> of the triode [31 is excited directly from the line 85 to produce a corresponding output signal on an output lead 134. The grid of the triode 132 is oppositely excited by a diagonally-connected resistor 135 and series capacitor 136 leading to the plate of the first triode. It 10 will be apparent to one skilled in the art that a positive voltage applied to the grid of the first triode 131 will cause a corresponding negative voltage to be applied to the grid of the second triode 132. As a result the voltage appearing at 15 the second output lead 138 will be opposite in phasing to the voltage appearing at the output lead 134 as shown by the typical waves 139, 140.

From this point the carry signal passes through four serially arranged flip-flop circuits 141, 142, 20 143, 144. Those circuits are, in general, unlocked individually and in regularly recurring sequence to pass the information "down the line" one step at a time. Preferably the flip-flop devices are arranged in two alternating groups 141, 143 and 25 142, 144 and unlocking pulses are fed to the groups alternately. In the present instance the pulses are supplied to flip-flop circuits 141, 143 through an unlocking lead 145 and are supplied to flipflop devices 142, 144 through an unlocking pulse 30 lead 146 at a rate of two pulses per cycle. Such pulses are furthermore timed with the data fed into the summing circuit to insure that a complete unlocking cycle occurs which is synchronized with successive cycles of data. Specifically, 35 at the start of a cycle comprising one wave or couple, the flip-flop circuits 142, 144 are first unlocked. This feeds into the summing circuit the carry signal from the previous summation. One-quarter of a cycle later the flip-flop circuits 40141, 143 are unlocked so that 141 may respond to the then existing output of the summing circuit. In a similar fashion the flip-flop circuits 142 and 143 are unlocked at the middle and threequarter points of the cycle respectively. At the 45 start of the next cycle, the signal then existing at the output of the flip-flop circuit 144 is applied to the input leads C, C', such signals corresponding exactly to the carry signal which appeared at the carry lead 85 just one cycle before.

From the foregoing it is seen that the four serially connected flip-flop circuits 141-144 are unlocked successively at quarter cycle intervals to provide a complete cycle or digit space delay for the carry signal. In addition, the specific 55 delay arrangement enables a maximum amount of reliability since it operates substantially independently of the wave form and in spite of relatively wide variations in the amplitude of the wave. In this connection note that the first flip- 60 flop circuit, which is the most critical since it determines the signal to be passed along by the remainder of the flip-flop circuits, is unlocked at the first and third quarter points of a couple. These points are approximately centered within 65 the regions of maximum amplitude. Thus, if the magnitude of the wave should decrease for any reason, positive response of the first flip-flop circuit is still assured. Operation is likewise reliable in spite of considerable inaccuracy in the 70 phasing of the data signal and in spite of sloping or rounding off of the wave front. In short, the circuits are kept synchronized by the unlocking pulses so that construction of the computer as a whole is not unduly critical.

Inserted in the line between the flip-flop circuit 144 and the C, C' input terminals of the summing circuit are a switch 148 and a clamp and The latter is in all impedance changer 149. respects similar to the clamp and impedance changer 62, 62' previously discussed in detail in connection with Fig. 8. The output waves of the latter are designated 147, 153. As to the switch 148, this may be assumed to remain closed and may be disregarded for the present, serving a function which will later be discussed in detail. In summarizing, it will be apparent that the circuit loop starting at lead 85 and ending at leads C. C' serves to transport a carry signal from one order to the next, and may be thought of as a feed-back circuit with a single cycle (or digit) delay.

#### GENERATION OF UNLOCKING PULSES

Reference will next be made to the preferred means for applying pulses to the leads 145, 146 for unlocking flip-flop circuits 141-144. To. insure synchronism the unlocking pulses preferably originate in a pulsing disk 150 which is shown in the upper left-hand corner of Fig. 1 and mounted on the shaft 22 which drives the storage disks 20, 21 previously referred to. As shown in Fig. 3, the disk 150 has on its periphery a plurality of closely spaced teeth 151 which cooperate with a pickup coil 152 having a core The core preferably has a chisel-shaped 154. tip which extends within a short distance (about .005 inch) of the crests of the teeth 151. A direct current is passed through the coil 152 and as the teeth on the rotating disk pass beneath the core, the reluctance of the magnetic circuit is changed, inducing an alternating voltage 153 in the coil which is then peaked, inverted, and amplified. The device for accomplishing the latter is termed the dual pulse generator 155, the preferred circuit being disclosed in detail in Fig. 4 to which reference is now made.

As shown, the pulse generator includes a pair of cascaded amplifying tubes 156, 158, the signal from the pickup coil 152 being conveyed to the grid of the first tube through a capacitor 159. The amplified signal from the tube 158 is then passed through the primary of a saturable transformer 160 having a center tapped secondary 161. Due to saturation a voltage is obtained at each side of the center tap which is very peaked. Such voltages, oppositely phased, are separately amplified by amplifiers indicated at 163, 164 respectively. The latter serve to excite respective cathode follower stages 165, 166 which supply the output leads 145, 146 previously referred to. For purposes of clarity the peaked unlocking waves on the leads 145, 146 are shown in Fig. 1 as 168, 169, the pulses occurring at the rate of two on each line per cycle. While each of the lines 145, 146 carries only two unlocking pulses per cycle, it is to be noted that the pulses supplied on one line alternate with those in the other so that a total of four unlocking pulses per cycle are supplied to the delay channel as a whole.

Since the pulsing disk 150 is rigidly coupled for rotation with the data disks 20 and 21, the unlocking pulses will be in step with the data signals. The angular relationship between the 70 data disks 20, 21 and the pulsing disk 150 is not depended upon, however, for exact synchronization between the data signals and the unlocking of the delay circuit. On the contrary it will be noted that the data flip-flop devices 42, 42' 75 are unlocked by the same set of pulse leads which

unlock the delay circuit, being connected thereto by lines 58, 58' (Fig. 1). As a result synchronization is positive and the assembling of the disks on the shaft 22 need not be a high precision operation. To insure that the delayed carry 5 signal is fed into the summing circuit in step with the incoming data, still another precaution is taken. This has to do with the timing of the unlocking pulses in the delay circuit relative to the wave form of the signal being acted upon. As pointed out above, the unlocking pulses are applied to the first flip-flop circuit 141 near the center of each half of the input wave or couple. Since the wave is substantially rectangular, it will be apparent that considerable departure on 15 Pulse output #1 from dual pulse generator 155 one side or the other of the center point may be tolerated without causing misphasing difficulties.

While the preferred circuit includes four serial flip-flop devices unlocked with four pulses per 20 cycle, it will be appreciated by one skilled in the art that a greater number could be used if desired without departing from the present teachings, always keeping in mind that the number of unlocking pulses should be sufficient to cause a delay of exactly one cycle or digit space.

#### RECORDING OF WRITE SIGNAL

As previously stated, the signal appearing on 30 the write lead 84 consists of a succession of couples of the same general wave form as those applied at the input of the summing circuit, the wave form being shown at 170 (Fig. 1) for purposes of convenience. The signal is then pref-35 erably passed through a phase inverter 171 appearing in both the direct and inverted form at leads 172, 174. At this point an alarm circuit may be employed to which detailed reference will later be made. The direct and inverted waves 182, 184 are next amplified by any suit-40 able amplifier 176. The output of the amplifier is then passed through the coils of a recorder head at 177 to record the sum magnetically on an output disk 180. The latter is preferably of 45 the same type as the storage disks 20, 21 and is synchronized therewith by mounting on the same shaft 22. The recorder head may likewise be of the same type discussed in detail in connection with Fig. 2. The individual coils 29, 30 50 thereof being supplied through the leads 178, 179. The recorded data corresponding to the binary sum of the binary numbers appearing on the disks 20, 21 may then be read off of the disk 180 by any suitable pickup head (not shown). 55When the adder is employed as part of a more complete computer capable of multiplying and the like, additional numbers may be continuously recorded on the disks 20, 21 and their sums only temporarily stored on the disk 180. The present 60 device is thus seen to be eminently well suited for continuous high speed operation.

While it is true that the signals 182, 184 to be "written" are square waves, it has been observed that the resulting magnetism impressed  $^{65}$ on the disk 180 is more nearly sinusoidal. This is believed due to the fact that a certain amount of neutralization or averaging of the flux takes place on the disk at the boundaries between the 70 fluxes of opposite sign. In any event the signal subsequently picked up from the output disk 180 as the answer is "read" will be found to be substantially of the same wave form as that "read" from the input disks 20, 21.

#### 16 SUMMARY OF OPERATION AND WAVE FORMS

While the complete computer contains additional meritorious features requiring discussion, it will be found convenient to review the operation of the components thus far discussed in order to show more clearly the manner in which the information picked up from the storage disks 20, 21 is recorded as a binary sum on the output disks 180. Turning to Fig. 10a, the wave forms of the signal as they exist at a number of significant points in the circuit are shown and may be conveniently grouped as follows:

Pulse output #2 from dual pulse generator 155 Signal from first storage disk 20

Signal from first storage disk after squaring and clamping (lead A to summing circuit)

- Signal from second storage disk 21

- Signal from second storage disk after squaring and clamping (lead B to summing circuit)

- Delayed carry signal after clamping (lead C to summing circuit)

- 25 Plate voltage of triode 87 (carry signal before delay)

Plate voltage of triode 88

Plate voltage of triode 89

Plate voltage of triode 90 (write signal as applied to recording coil)

All of the waves have been vertically alined with respect to a common time axis so that it is possible to trace the effect of digit couples fed into the circuit from the storage disks 20, 21 from beginning to end. Since the waves may be considered as "flowing" progressively to the right, the first digit space or order is along the righthand edge of Fig. 10a and has been designated a. The couples corresponding to digits in the next highest order operated upon in the computer occupy a space b. Successive orders have been designated as c, d, e, and f. Individual couples are denoted by a corresponding subscript.

The over-all operation of the computer may be understood by observing what occurs during solution of a practical problem: the addition of 000110 to 000011 previously recorded and stored on disks 20, 21. Both of these numbers together with their sum, 001001, are placed in Fig.  $10\alpha$ immediately below the couples which represent them. As a first step the first (lowest order) digit read off of the storage disk 20 is 0 (zero). The couple corresponding to this first digit signal has been designated 38° in Fig. 10a, and after shaping and clamping produces a square minusplus couple 79ª which is fed into the summing circuit on lead A. The lowest order digit of the second binary number is 1 (one) and appears in magnetic form on the second storage disk 21. The electrical couple corresponding thereto is designated 38's, which after shaping and clamping appears as the plus-minus couple 79's on lead B.

It will be assumed that the carry signal C is 0, the first couple of the carry signal being minus-plus and indicated at 147<sup>a</sup>.

Under the above conditions the only one of the signals A, B, C having an initial positive portion is B. The resulting voltages appearing at the plates of the triodes 87-90 may be determined merely upon inspection of the previously discussed Table I. These voltage waves are rep-75 resented in the drawing as 126-129 with the

55

first or leading couples designated 126-129\*. Turning attention to the voltage 129a (triode 90) it is seen that the voltage is high during the initial portion of the first cycle and low during the final portion. This causes a similar variation 5 at the cathode of the cathode follower triode \$1. The latter results in a plus-minus couple leading the wave on the write output lead 84 which is amplified and recorded as a 1 (one) on the output disk 188. 10

The carry signal is dependent upon the output voltage of triode 87. Since the sum for the first order (as seen above) is 1, the carry signal is 0 (zero) as represented by the minus-plus couple 125\*. Because of the delay circuit this 15 carry signal is carried over into the next order b as the minus-plus couple 147b on input lead C.

Having observed the sequence of operations in the first order a, attention is next directed to the second column from the right in Fig. 10a 20 which shows the operation of the computer during the second order b. In the second order the digit on each of the storage disks 20, 21 is 1 (one). This results in the application of the plus-minus pulses 79<sup>b</sup> and 79'b to the summing 25 input leads A and B respectively. The voltage variation at the plate of tube 90 constitutes a minus-plus couple 129<sup>b</sup> which is fed at low impedance to the write lead 84. 0 is thereupon written magnetically on the output disk 180. 30 The voltage variation at the plate of tube 87 on the other hand during this cycle is a plus-minus couple 126<sup>b</sup>. This corresponds to carrying a binary 1 to the next order. After delay it will be seen that this carry signal is fed into the sum- 35 ming circuit at C in the next higher order C. The above process is repeated for the orders  $c_i$ . d, e and f resulting in the writing of digits 0, 1, 0 and 0 on the disk 180 to complete the answer, namely, 001001.

While a six digit binary problem has been taken as representative, a practical computer employing the present teachings is not so limited. Computers may be readily constructed with a capacity of 25 or more binal places which 45 takes care of the great majority of problems arising in business. When using a machine of larger capacity for a relatively simple problem. such as that outlined above, the higher orders on the disks 20, 21 should be completely occupied **5**Ö by zeros and corresponding zeros will thus be written in the higher orders of the answer on disk 180.

#### LOW ORDER DIGIT INSERTER FOR CARRY CIRCUIT

In the above discussion it has been assumed that the initial information fed from the carry delay circuit represented a binary digit 0 so that, in effect, there was nothing carried in summing the digits of the first order. If the computer 60 were used to perform but a single problem of addition, this would in general be true. However, since the computer is normally called upon to perform a large number of problems of addition in quick succession, the addition of the first 65 digits of a given pair of numbers follows directly after the addition of the last digits of the preceding number. It is, therefore, quite possible that the carry for the first digits added might not always be zero as it should to obtain the 70 correct answer. In accordance with one of the aspects of the invention, therefore, means are included in the carry circuit for disabling the carry circuit during the addition of the first digit.

in the carry input leads C, C'. Preferably this is accomplished by a simple switching arrangement which causes a minus-plus couple to be applied during the summation of digits in the first orders and the carry signal to be applied normally during the remainder of the number.

Prior to a discussion of the manner in which. the initial zero signal is inserted in the carry leads it will be helpful to refer to that portion of the apparatus used for generating the inserted zero. As disclosed in Fig. 1 a zero generating disk 200 is employed which is mounted on shaft 22 and is rotated in synchronism with the storage gears 20, 21. The disk 200 is comstructed substantially the same as disk 150 ercept that the pitch of the teeth on disk 260 is twice the pitch of the teeth on disk 150. A direct current: is passed through the pick-up coil 208: which is similar to coil 152. As the reluctance of the magnetic circuit is changed by the movement of the teeth past the tip of the core, an alternating voltage representative of a series of binary 0's is produced as indicated at 201. This signal is then amplified in a vacuum tube amplifier 202 which is conventional in design.

Next, the wave is shaped and inverted by passing it through a flip-flop device 204 having output leads 205, 296 and an unlocking lead 296. Such flip-flop device is equivalent to the devices 42, 42' and shown in detail in Fig. 7. The shaped output signal 209 and its inversion 210 are next. fed through a reversing switch 211 having output. leads 216, 211. The reversing switch may be passed over for the present since it is not normally employed in the process of simple addition. Subsequently the signal passes through a double. pole single throw switch 215 which is identical to the single throw switch 148 previously referred to and which is contained at the output of the carry delay circuit. It will be apparent that with the switch 148 closed and with the switch. 215 open, zeros from the zero generating disk 266 will be blocked off and the circuit will operate in the manner previously described. However, with the reverse condition existing, that is, with the switch 148 in the carry delay circuit open and with the switch 215 from the zero generating: disk 200 closed a constant stream of couples representative of binary 0's will be fed into the input leads C, C' of the summing circuit. But: as pointed out above, it is desirable that a sero be fed into the carry input leads C. C' only daring the first cycle or digit space.

Accordingly, means are provided for operating the switch 215 in such a manner that the switch is closed only during the first digit space of a summation. In the present instance this is accomplished by a switch control disk 229 having teeth or equivalent magnetic irregularities 221 at spaced intervals about the periphery thereof and corresponding in positioning to the beginning of the binary numbers on the storage disks 26, 24. A pick-up head 223 cooperates with the disk 220 to detect such irregularities and may be of the same type as shown at 152 in Fig. 3. The head thus produces pulses 222 which are fed into an amplifier 225 of conventional design to produce. direct and inverted output waves having initial peaks synchronized with the initial or lowest order digits of the two binary numbers fed from the storage disks 20, 21. The amplifier output is used to excite a flip-flop device 226 having output leads 228, 229 and of the same general type previously discussed in connection with Fig. and inserting a zero signal (minus-plus couple) 75 The unlocking pulses for the device 226 are ob-

2,609,143

tained from an auxiliary disk 230 having magnetic irregularities thereon and fitted with a cooperating pick-up head just as in the case of disk 220. To steepen and amplify the wave front, the pulses are fed through a peaking amplifier 5 231 of a type well known to those skilled in the art before being applied to the pulse lead 224 of the flip-flop circuit. As shown, disks 220, 230 preferably carry the peripheral teeth in groups of two with the first producing a control pulse at 10 the very beginning and the second producing a control pulse near the end of the first binary digit space. The first pulses are effective to change the flip-flop device 226 to its alternate or switched condition and the other to restore it 15 to its normal condition. The output of the flipflop device is then applied to the switches 148 and 215 so that 215 conducts only during the first digit space and 148 conducts only during the remainder of the spaces comprising a binary 20 number.

While a number of different switch circuits may be used to perform the above-outlined function without departing from the invention, the preferred form of electronic switch is disclosed in 25 detail in Fig. 13. The circuit includes four triodes 250, 251, 252, 253, having cathodes, grids, and plates bearing corresponding reference numerals with the subscript a, b, or c respectively. In the plate circuits of the triodes 251, 253 are 30 included plate dropping resistors 255, 256 respectively. The cathodes are connected together in pairs and are grounded through cathode resistors 258, 259. Referring to the left-hand portion of the circuit, it can be seen that if the grid 35 252<sup>b</sup> has a relatively large potential applied to it, current will flow through a circuit including the cathode resistor 259, cathode 252ª and plate 252° thus producing a relatively large voltage drop across the cathode resistor. This raises the cath-40 ode potential sufficiently to bias the triode 253 to cut-off for all values of voltage normally applied to the input lead 216. Thus normal variations in the signal voltage applied to the input lead 216 cannot affect the current through plate 45 resistor 256 and the potential at plate 253° thus remains fixed.

If now the voltage applied to the grid 252<sup>b</sup> by the control lead 229 is materially reduced, the current drawn by the triode 252 is also materially 50 reduced. The effect of the latter is to lower the potential of the cathode 253ª to the point where voltage swings applied to the grid 253° by the input lead 216 will cause corresponding variations in the plate current. These plate current varia-65 tions will result in a varying voltage drop across the plate resistor 256 and the input signal will be reproduced at the output lead 219. Inherent in the latter operation is a 180° phase reversal. The latter may, however, be readily compensated for 60 merely by interchanging the two output leads 218, 219, such cross connection being set forth in the circuit shown in Fig. 13. From the foregoing it is evident that with a negative potential applied to the pulse lead 229 the switch is ef- 65 fectively closed, that is, the output voltage corresponds to the then existing value of the input voltage. Conversely, with a relatively high positive voltage on the pulse lead 229 the switch is 70blocked and no signals are permitted to pass through

While only the left-hand portion of the circuit disclosed in Fig. 13 has been described in detail, it will be appreciated by one skilled in the art that the right-hand portion operates in 75

exactly the same manner. In short, the input signal at lead 217 produces a corresponding output signal at lead 218.

As a result of the action of the flip-flop control circuit 226 acting on the double pole single throw switches 215, 148, the switch 215 is ex-clusively closed only during the first digit space, allowing one of the zero digit signals from the disk 200 to be applied to the carry input leads C. C' of the summing circuit. During the remainder of the digit spaces switch 215 is open and the carry delay circuit operates through switch 148 to apply a carry signal to the summing circuit as has been previously described. The summing of a given pair of binary numbers thus takes place independently of the sums taken immediately before or after.

#### SUBTRACTION

Subtraction is accomplished in a manner quite similar to addition. The primary difference is that instead of adding the first number to the second, the complement of the first number is added to the second number. Broadly this complement is obtained by inverting the signal of the subtrahend in order to reverse the sense of all of the couples which make up the number to be subtracted. In the present instance such reversal has been accomplished in the channel leading from the storage disk 20 by inclusion of the reversing switch 81. In its simplest aspect this switch may be a simple manually operated double-pole double-throw toggle switch. Or, as will be apparent to one skilled in the art, an electromagnetic reversing switch or even an electronic reversing switch of conventional design may be used. Where the computer disclosed herein is to be used as a larger and more complete calculating device, an electronic switch automatically controlled by a pulsed control line is preferred. Such an arrangement is disclosed in applicant's copending application Ser. No. 76,088 filed February 12, 1949.

The effect of operating the reversing switch in the present circuit is to substitute at the input terminals A, A' of the summing circuit 1's for 0's and 0's for 1's. This gives the complement with respect to 111 . . . 11 or the largest number that the machine will hold. Actually, in order to obtain a correct result it is necessary to use the complement with respect to a number 1 greater than the capacity of the machine or 1000 . . . 00. The true complement is obtained in the practice of the present invention by adding 1 to the complement formed by inverting the signal. In accordance with the present invention this 1 is obtained from the same channel (associated with the zero generating disk 200) which is used to insert the initial 0 in the carry input leads C, C'. This is accomplished in the present instance by inserting the reversing switch 211 in such channel preferably between the flip-flop circuit 204 and the zero control switch 215. The reversing switch 211 is of the double-pole double-throw type and may be identical with the reversing switch 81 in the A, A' leads and to which reference has previously been made. The reversing switch will cause an initial 1 rather than an initial 0 to be inserted in the carry leads when the summing circuit 82 operates upon the first binary order. This in effect makes the complement 1 greater than it otherwise would be thus producing a true complement and causing the true difference to be "written" on the output disk 180.

#### ALTERNATIVE DIGIT ADDER CIRCUIT USING MULTIGRID TUBES

As previously covered, an adder circuit is disdosed in Fig. 10 which produces a carry signal at its output when either two or three of the input leads A, B, C are positive and which further produces a write signal when either one or three of the input leads are positive. It will be apparent to one skilled in the art that the invention is by no means limited to the specific 10 urcuit of Fig. 10 but includes alternative and equivalent circuits utilizing the same basic teachngs. One such alternative scheme has been set of the in Fig. 11 with the input and output leads abeled just as in Fig. 10.

This circuit also employs cascaded control ubes blased in accordance with the voltages appearing at the leads A. B. C and A', B', C'. The minary difference between the circuit of Fig. 11 and that in Fig. 10 previously discussed is that 20 multigrid tubes rather than triodes are employed. such tubes may be conventional receiving-type schodes having control, screen, and suppressor prids.

Referring in greater detail to Fig. 11 it will be 25een that it includes primary control tubes 40-246 inclusive and secondary control tubes 50, 251. Just as in the previous embodiment the econdary control tubes include control elements esponsive to the plate current flow in the prinary control tubes. In the case of each of the ubes the electrodes progressing outwardly from he cathode toward the plate may be designated by the subscripts a-e inclusive.

To begin with it will be helpful to observe 35 he manner in which a carry signal is applied t the output lead 85 when two or more of the nput leads A, B, C are positive. In the practice I the invention the three input leads A, B, C are istributed among the primary control tubes 240, 41, 242 such that each of such tubes is controlled y two of the input leads. In each instance the uppressor grid is connected directly to the cathde. Thus, tube 240 is controlled by lines B, C, 41 by lines A, C, and 242 by lines A, B. Bias is 45 erived from a battery or the like 252 which is hunted by a bias adjusting potentiometer 254. The blas is adjusted so that both the control and creen grids in any one tube must be made posiwe before such tube passes plate current. With 59 hly one of the control electrodes positive the the remains cut off. In order that the carry utput lead 85 may be responsive to the state of unductivity of any one of the tubes 240, 241, 242, he cathode potential of the tubes is caused to 55 wing through a relatively wide range. This is fected by means of a cathode resistor 255 which common to all of the above-mentioned tubes. a effect, therefore, the tubes 240, 241, 242 conitute a cathode follower responsive to certain 60 mbinations of input voltages.

To prevent the control tubes from drawing rid current, grid resistors 256 are placed in result it has been found that the control grids <sup>65</sup> result it has been found that the control grids <sup>65</sup> re never driven appreciably above cathode pomtial. If all three of the input leads A, B, C re made positive with respect to ground (correbonding to an input of three binary 1's) all three ? the tubes are conductive. However, the cathie resistor 255 preferably has a value such that hen one tube is conducting the voltage drop pross the tube is small as compared to the voltje drop across the resistor 255. Thus, the voltje drop across the resistor and the voltage of 75

output lead 85 will be substantially the same, whether one, two or three tubes are conducting. It is clear, then, that this portion of the circuit fully meets the condition that a positive output signal be produced when either two or three of the input leads A, B, C are positive.

Attention will next be given to the right-hand portion of Fig. 11 which applies a positive voltage to the write output lead so when either one or three of the input leads A, B, C are positive. It will be noted that the remaining primary control tubes are paired, the cathodes of tubes 243, 244 and 245, 246 being respectively connected together. The control electrodes of tubes 243 are connected to leads C, B' while those of tube 244 are connected to B, C'. The cathodes are connected to a cathode resistor 258 which enables the cathode output lead 259 to swing with respect to ground. With the circuit connected as shown it will be apparent that the cathode output lead 259 will swing positively only when C, B' or B, C' are positive. In terms of B and C alone, an output signal will be produced at the lead 259 when either B or C are positive but not when both are positive.

Reference may next be made to the secondary tube 250 having its screen 250° connected to the output of tubes 243, 244. The control grid 250<sup>b</sup> is connected to the input terminal A'. The tube 250, similar to the other tubes in the present embodiment, is connected as a cathode follower having a cathode resistor 260. The write output lead 84 is connected directly to the cathode of this stage. Here again it is necessary for both grids to be positive for plate current to flow. That is to say, it is necessary for A' to be positive and for either B or C (but not both) to be positive. The latter condition, it will be recalled, is due to the conductivity conditions set up for tubes 243, 244. In summary, therefore, conduction will take place in the secondary output tube 256 producing a positive output signal on the write lead 84 when the following conditions are met:

| A-minus        |

|----------------|

| <b>B-plus</b>  |

| C-minus        |

|                |

| A-minus        |

| <b>B-minus</b> |

| C-plus         |

or

In order to satisfy the remaining requirements, additional primary control tubes 245, 246 are used feeding into secondary control tube 251. In the case of tube 245 the grids are controlled by input lines B', C' while the grids of tube 246 are connected to the input leads B, C. These tubes have a common cathode resistor 261 and are likewise biased so that both of the grids must be positive to produce conduction. The cathodes are jointly connected to an output lead 262. A positive signal is applied to the latter output lead only when B and C are both positive or both negative, and under such conditions a positive voltage is applied to the screen grid 251° of the tube 251. The control grid 251<sup>b</sup> on the other hand is connected directly to input line A. The cathode of this tube is directly connected to the write output lead 84 which shares the cathode resistor 260. It will be apparent from the foregoing that the tube 251 conducts to produce a positive write signal when A is positive and when B and C are both positive or both negative. The two conditions of conductivity may be summarized as follows:

| B-minus<br>C-minus |  |

|--------------------|--|

|                    |  |

| A-plus<br>B-plus   |  |

| C-nlug             |  |

Adding these two conditions to the two conditions previously set forth in connection with the secondary output tube 250 we see that a write signal is produced when either a single one of the input leads A, B, C is positive or when all three are positive. In terms of function, a binary 1 is "written" when either one or three binary 1's appear at the input.

In order that the parallel between the circuit described immediately above and that previously  $_{20}$  discussed may be more clearly drawn, a table of over-all operating characteristics may be set up which corresponds generally to Table I as follows:

Table II

2,609,143

ly, at the cathodes of tubes 243, 244 and 245, 246 and at the write and carry output leads 84, 85. The pulse and data signals derived from the data disks and shown in Fig. 10*a* apply here equally and consequently need not be repeated. In both circuits the signal at the write output lead 84 consists of couples representative of the binary number 001001.

#### ALTERNATIVE DIGIT ADDER CIRCUIT USING DIODE RECTIFIERS

In accordance with one of the more detailed aspects of the invention another alternative adder circuit using unidirectional electronic devices is the form of diodes instead of grid controlled rectifiers is disclosed in Fig. 12. The wave forms applicable to the circuit of Fig. 12 are to be found in Fig. 12a.

Just as in the case of the previous two summing circuits (Figs. 10 and 11) input leads A, B, C are provided on which are respectively received couples corresponding to first and second data signals together with a carry signal all representative of binary digits. The inverse or comple-

| Leads, positive | Tube      | Tube     | Tube     | Tube                                                               | Tube              | Tube                                                                                             | Tube      | Tube 250                                            | Tube 251          | Wrlte                                             | Carry                                                     |

|-----------------|-----------|----------|----------|--------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------|-------------------|---------------------------------------------------|-----------------------------------------------------------|

|                 | 240       | 241      | 242      | 243                                                                | 244               | 245                                                                                              | 246       | (A-243,                                             | (A-245,           | Out-                                              | Out-                                                      |

|                 | (B-C)     | (A-C)    | (A-B)    | (C-B')                                                             | (C'-B)            | (C'-B')                                                                                          | (C-B)     | 244)                                                | 246)              | Put                                               | Put                                                       |