# Inside the TC2000<sup>™</sup> Computer

**Revision: First Release**

Part No. A370014G10 Document Rev: A

BBN Advanced Computers Inc.

#### Copyright © 1990 by BBN Advanced Computers Inc. ALL RIGHTS RESERVED

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise without the prior written permission of BBN Advanced Computers Inc. (BBN ACI).

#### **RESTRICTED RIGHTS LEGEND**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227–7013.

BBN Advanced Computers Inc 10 Fawcett St. Cambridge MA 02138

#### **RELEASE LEVEL**

This manual conforms to the February 1990 TC2000™ multiprocessor hardware..

#### NOTICE

BBN ACI has prepared this manual for the exclusive use of BBN customers, personnel, and licensees. The information in this manual is subject to change without notice, and should not be construed as a commitment by BBN ACI. BBN ACI assumes no responsibility for any errors that appear in this document.

### TRADEMARKS

Butterfly is a registered trademark of Bolt Beranek and Newman Inc.

Chrysalis, TC2000, nX, Uniform System, Xtra, Gist, and TotalView are trademarks of Bolt Beranek and Newman Inc.

UNIX is a registered trademark of AT&T Bell Laboratories.

DEC, VAX, and VT are registered trademarks of Digital Equipment Corporation.

VMS, VAX/VMS, MicroVAX, Ultrix, and DECnet are trademarks of Digital Equipment Corporation.

IBM and IBM PC are registered trademarks of International Business Machines Corporation.

Multibus and Intel are registered trademarks of Intel Corporation.

The X Window System is a trademark of the Massachusetts Institute of Technology.

MC68000, MC68020, MC68881, MC68882, MC68851, MC88000, MC88100, MC88200, and VMEbus are trademarks of Motorola Semiconductor Products, Inc.

QTC and Math Advantage are registered trademarks of Quantitative Technology Corporation.

pSOS, pSOS<sup>+</sup>, pSOS<sup>+</sup><sup>m</sup>, pRISM, pUCP, pREP/C, pROBE, and pHILE are trademarks of Software Components Group, Inc.

MS-DOS is a registered trademark of Microsoft Corporation.

TeleSoft and TeleGen2 are trademarks of Telesoft.

Sun Microsystems and Sun Workstation are registered trademarks of Sun Microsystems, Inc.

OSN, ONC, NeWS, and NFS are trademarks of Sun Microsystems, Inc.

4.2BSD and 4.3BSD are trademarks of the Trustees of the University of California.

Ethernet is a registered trademark of Xerox Corporation.

BBN ACI thanks the following contributors for their efforts in developing this manual:

Author: Michael Beeler

Designers and Reviewers: Dave Barach Tom Downey Jim Gibson John Goodhue Phil Herman Kent Hoult Larry Kaplan Becky Mercuri Rich Schaaf Julie Tiao

# Contents

| _ |  |   |  |   |  |   |  |

|---|--|---|--|---|--|---|--|

| = |  | _ |  | = |  | = |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

|   |  |   |  |   |  |   |  |

| Ch  | apter                 | F                                               | Page |

|-----|-----------------------|-------------------------------------------------|------|

| Но  | w to Use <sup>-</sup> | This Manual                                     | xiii |

| 1   | Structure             | of the TC2000 Computer                          | 1    |

| 1.1 | Basic (               | Characteristics                                 | 1    |

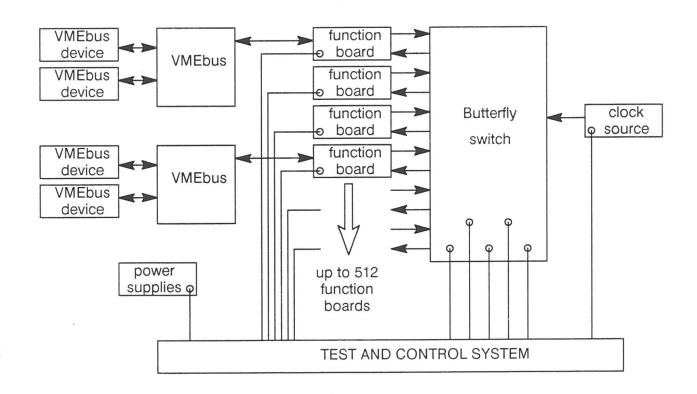

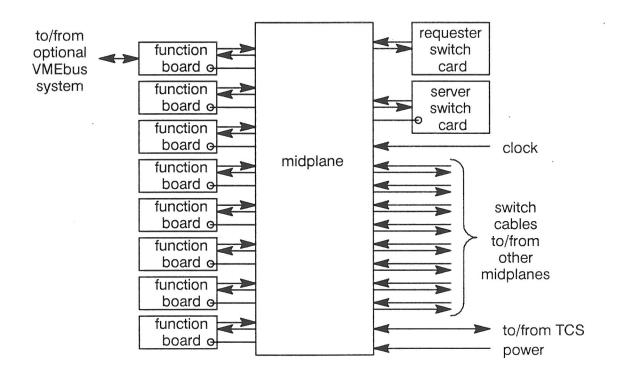

| 1.2 | Archite               | ecture                                          | 2    |

| 1.3 | System                | Components                                      | 4    |

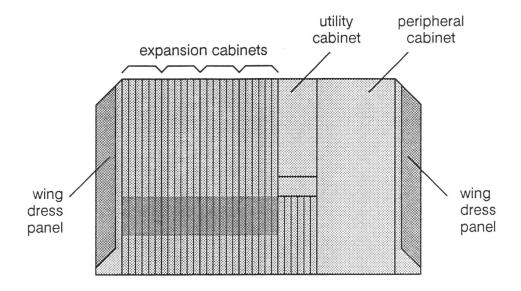

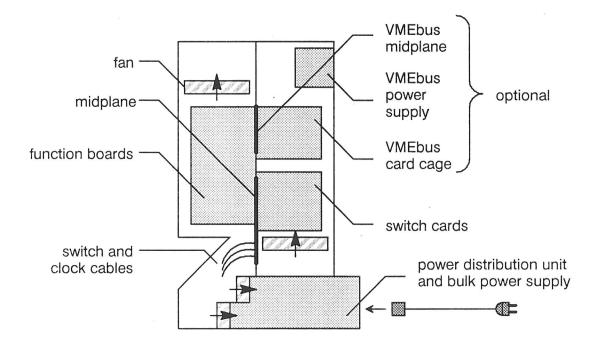

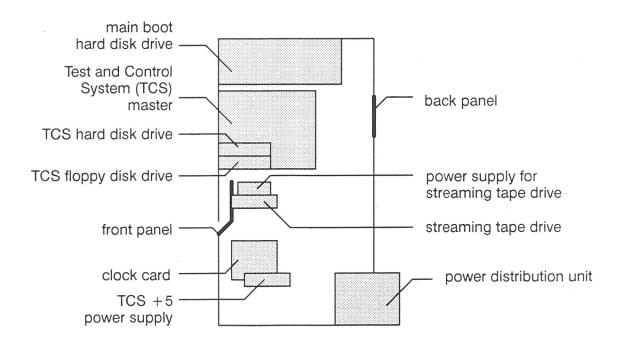

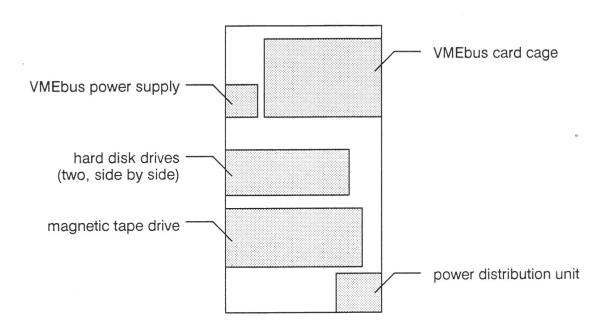

|     | 1.3.1                 | Physical Structure                              | 4    |

|     | 1.3.2                 | Logical Structure                               | 10   |

| 1.4 | Machin                | ne Specifications                               | . 24 |

|     | 1.4.1                 | Computational Specifications                    | 24   |

|     | 1.4.2                 | Environmental Specifications                    | 25   |

| 1.5 | Equiva                | lent but Distinct Function Boards               | 26   |

|     | 1.5.1                 | The nX Master Function Board                    | 26   |

|     | 1.5.2                 | Clusters                                        | 27   |

|     | 1.5.3                 | Physical Slots                                  | 27   |

|     | 1.5.4                 | Slot Numbering                                  | 28   |

| 2   | The TC/F              | PV Function Board                               | 31   |

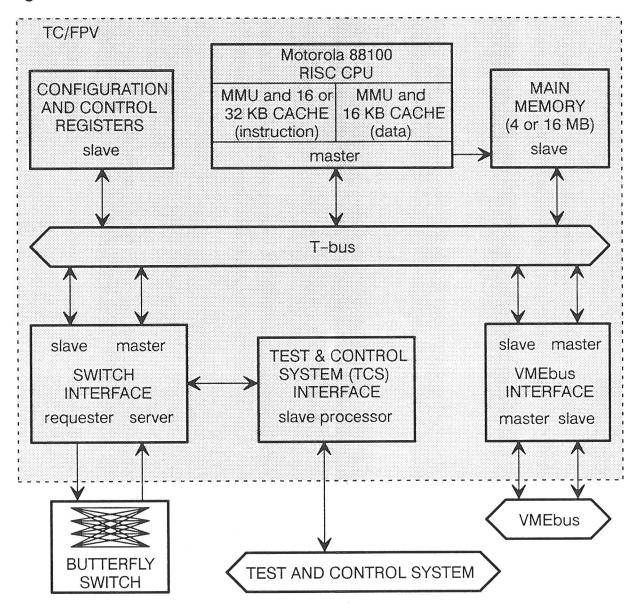

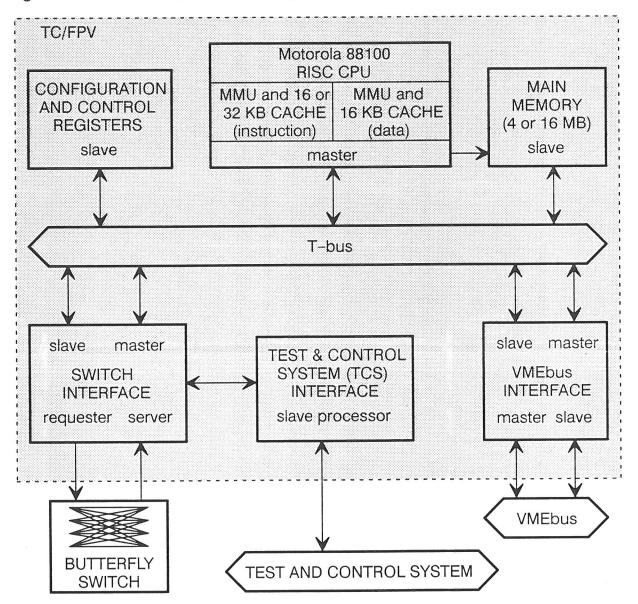

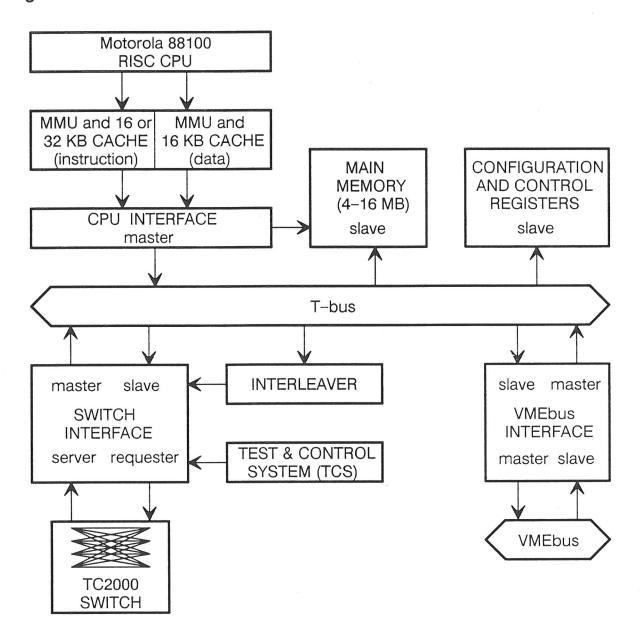

| 2.1 | Organi                | zation                                          | 31   |

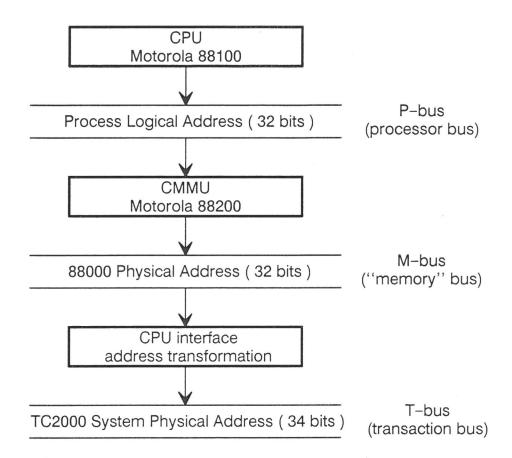

| 2.2 | Proces                | sor, CMMU and CPU Interface                     | 33   |

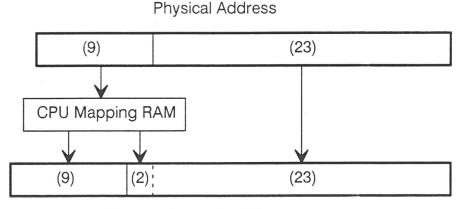

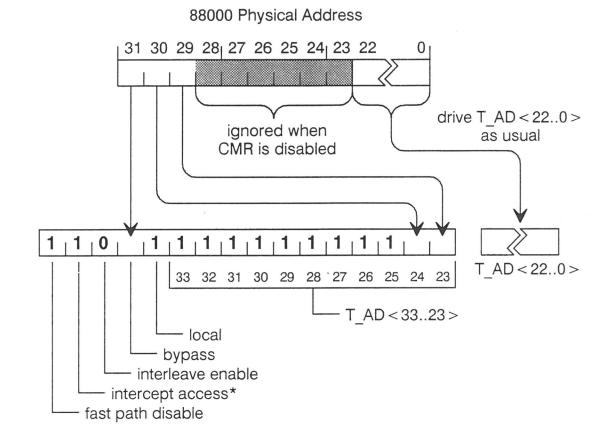

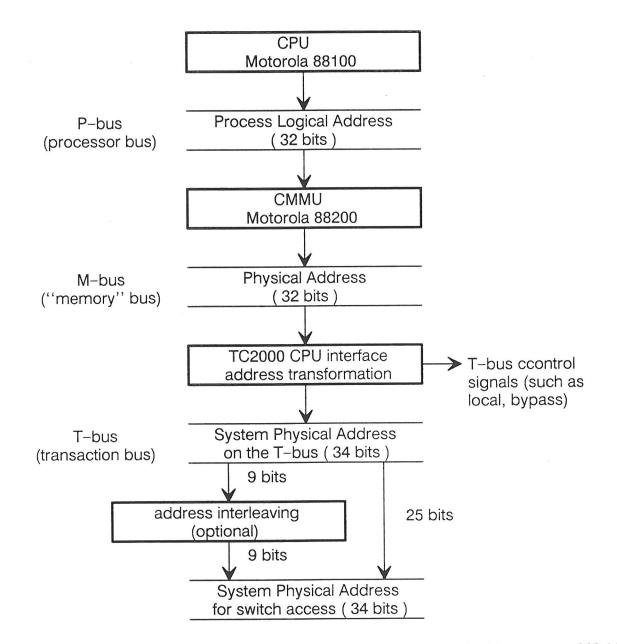

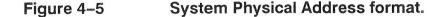

|     | 2.2.1                 | TC2000 Physical Address Space                   | 33   |

|     | 2.2.2                 | 88000 Access to Global Memory                   | 34   |

|     | 2.2.3                 | Block Transfer and the CMR Intercept Access Bit | 36   |

|     | 2.2.4                 | The Local Bit in the CMR                        | 37   |

|     | 2.2.5                 | The Interleave Enable Bit in the CMR            | 38   |

|     | 2.2.6                 | The Bypass Bit in the CMR                       | 39   |

|     | 2.2.7                 | The Fast Path Disable Bit in the CMR            | 39   |

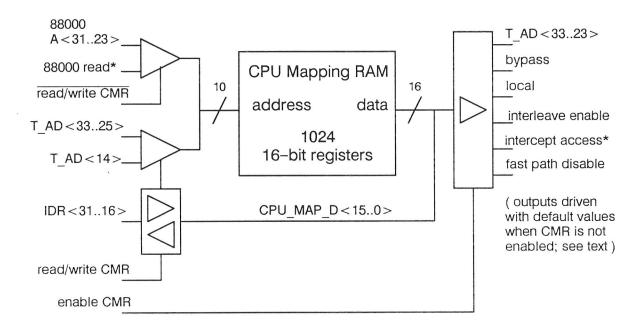

|     | 2.2.8                 | CMR Block Diagram                               | 40   |

|     | 2.2.9                 | CMR Power-up and Disabled State                 | 40   |

|     | 2.2.10                | CMMU and CPU Interface Affect Address Use       | 41   |

| 2.3 | Memo                  | ry                                              | 42   |

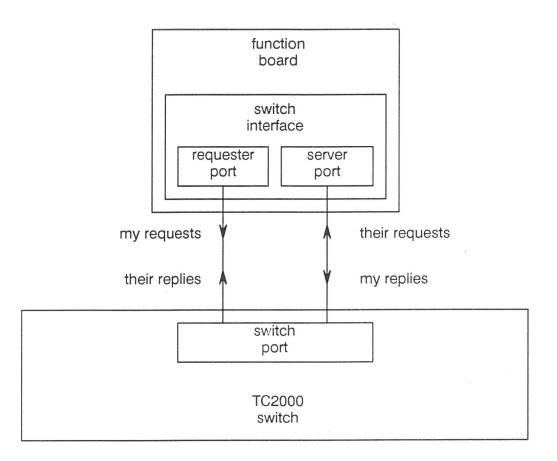

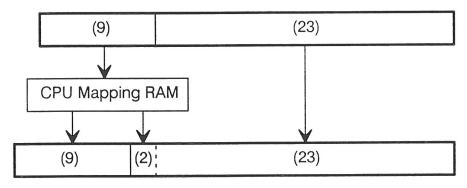

| 2.4 | Switch                | Interface                                       | 42   |

|     | 2.4.1                 | References to Remote Function Boards            | 43   |

|     | 2.4.2                 | References from Remote Function Boards          | 43   |

|      | 2.4.3   | More Switch Interface Features           | 44       |

|------|---------|------------------------------------------|----------|

|      |         |                                          | 44       |

| 0.5  | 2.4.4   | Interleaver                              |          |

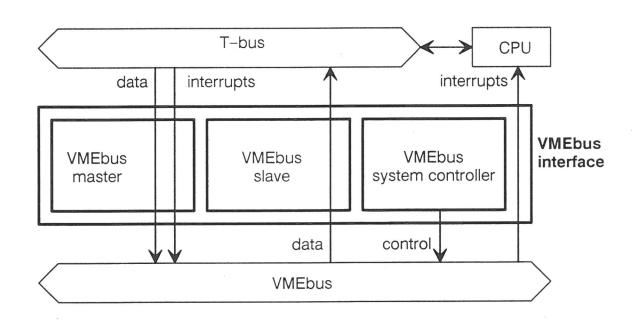

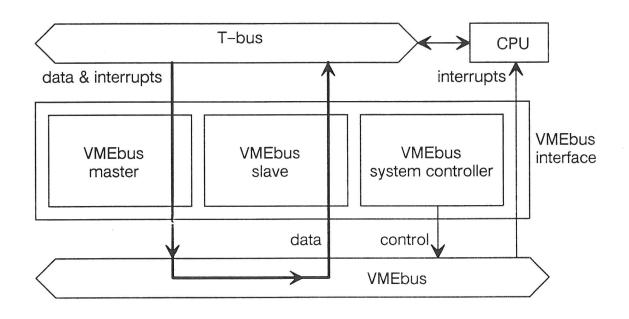

| 2.5  |         | Is Interface                             | 45       |

|      | 2.5.1   | VMEbus Master Mapper                     | 46       |

|      | 2.5.2   | VMEbus Slave Mapper                      | 47       |

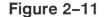

|      | 2.5.3   | VMEbus Interrupt Handling and Generation | 48       |

|      | 2.5.4   | VMEbus System Controller Functions       | 49       |

| 2.6  |         | ave                                      | 49       |

| 2.7  | 0       | aration and Control Registers            | 50       |

|      | 2.7.1   | User Registers                           | 50       |

|      | 2.7.2   | Configuration Registers                  | 51       |

|      | 2.7.3   | Interrupt System Registers               | 51       |

|      | 2.7.4   | (T-bus) Bus Error Register               | 52       |

|      | 2.7.5   | Latency Control Registers                | 52       |

|      | 2.7.6   | VMEbus Interface Registers               | 53       |

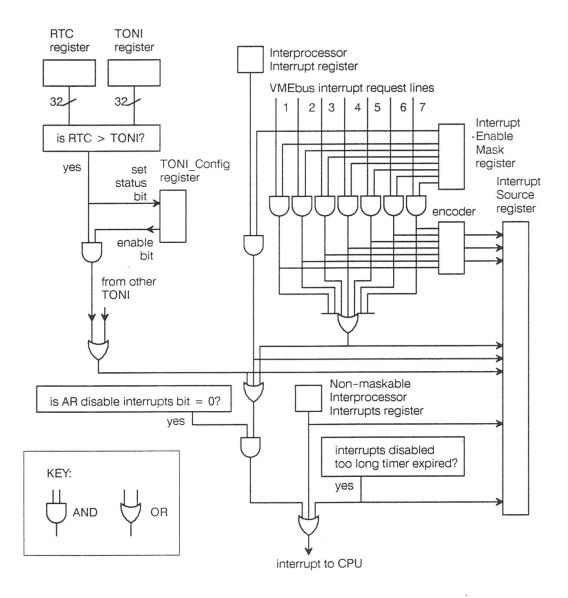

|      | 2.7.7   | SIGA Registers                           | 53       |

|      | 2.7.8   | Interleaver Control Registers            | 54       |

|      | 2.7.9   | CPU and CMMU Registers                   | 54       |

| 2.8  |         | d Speed of References                    | 55       |

| 2.0  | 2.8.1   | What Path an Access Takes                | 55       |

|      | 2.8.2   | CPU Memory Access Timing                 | 59       |

|      | 2.8.3   | Intercept Access and Timing              | 63       |

| 2.9  |         | ity and Locking                          | 63       |

| 2.7  | 2.9.1   | Race Conditions                          | 63       |

|      | 2.9.1   | Two Sides of a Coin                      | 64       |

|      |         | The xmem Instruction                     | 67       |

|      | 2.9.3   | Atomic Functions Based on xmem           | 68       |

|      | 2.9.4   |                                          | 68       |

|      | 2.9.5   | Atomic System Calls                      | 08<br>70 |

|      | 2.9.6   | Atomicity of Memory Accesses             | 70       |

|      | 2.9.7   | TC2000 Locking Protocol                  | 71       |

| 2.10 |         | and Interrupts                           |          |

| 2.11 | Bus Er  | rors                                     | 80       |

|      |         | м                                        |          |

| 3 Th | e Butte | rfly Switch                              | 81       |

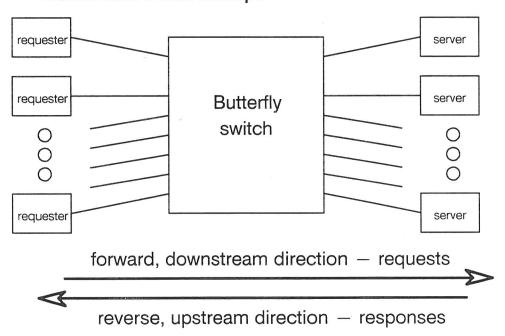

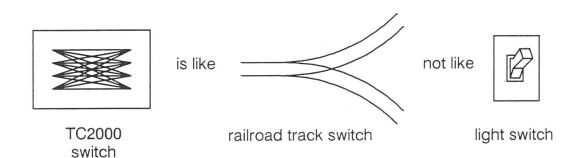

| 3.1  |         | ance and Name                            | 81       |

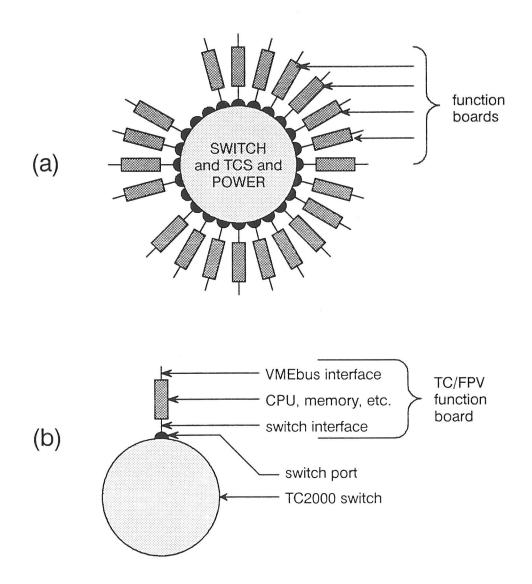

| 3.2  |         | on and General Structure                 | 82       |

|      |         | Provide Access to Remote Boards          | 82       |

|      | 3.2.2   | Also Distribute Signals                  | 82       |

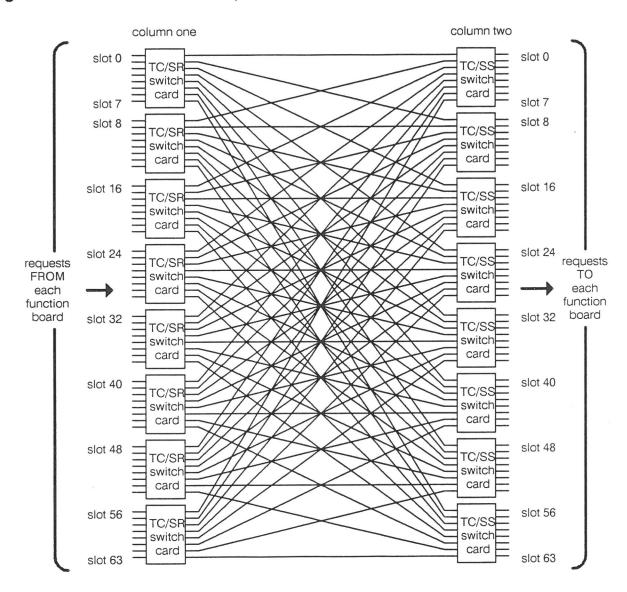

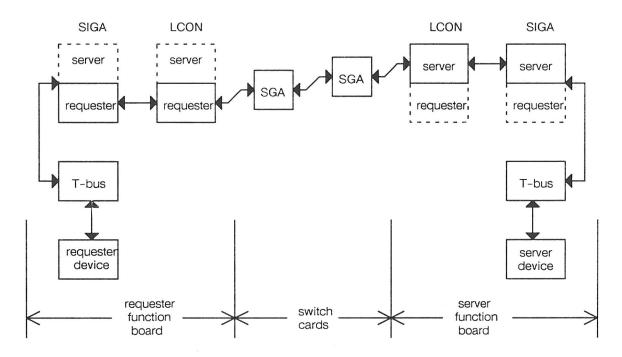

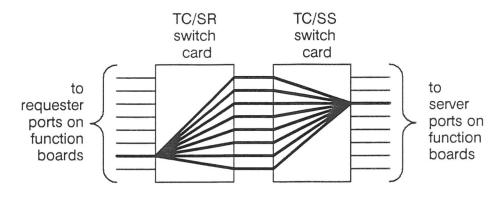

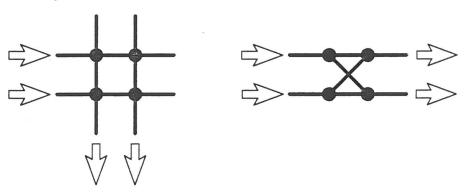

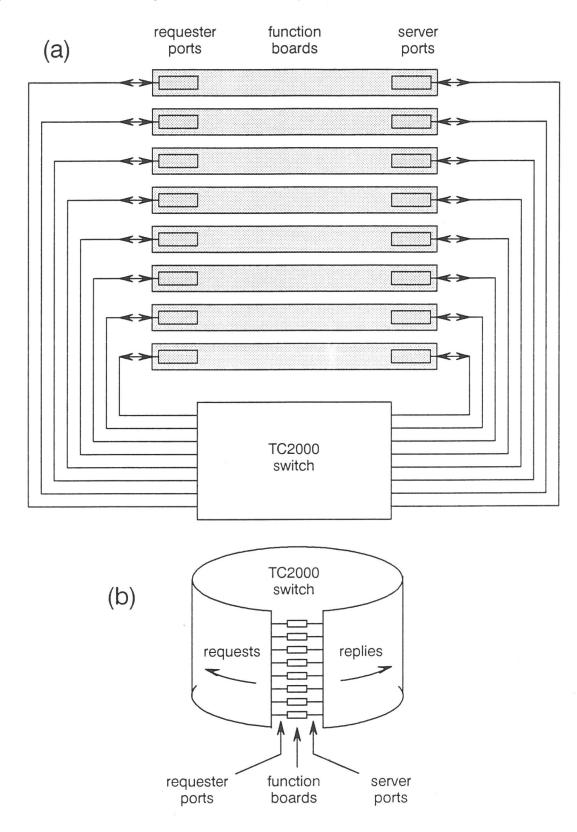

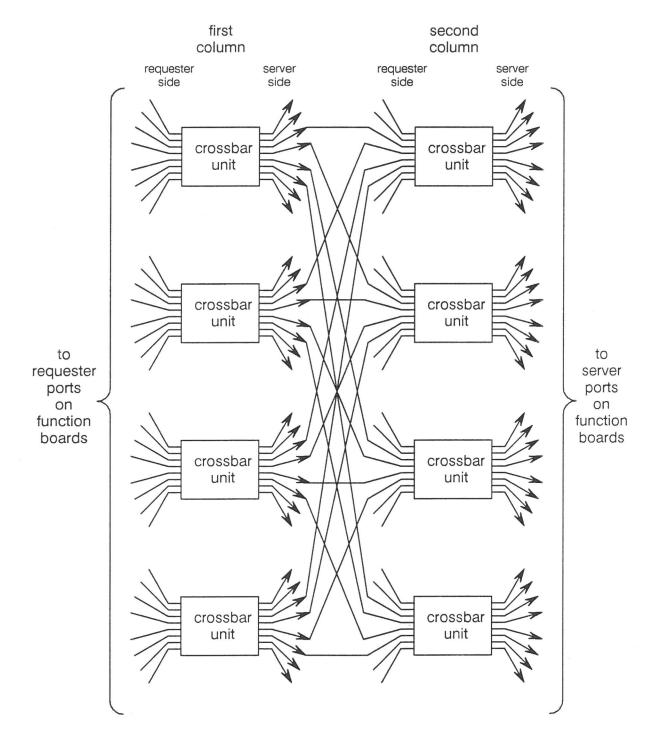

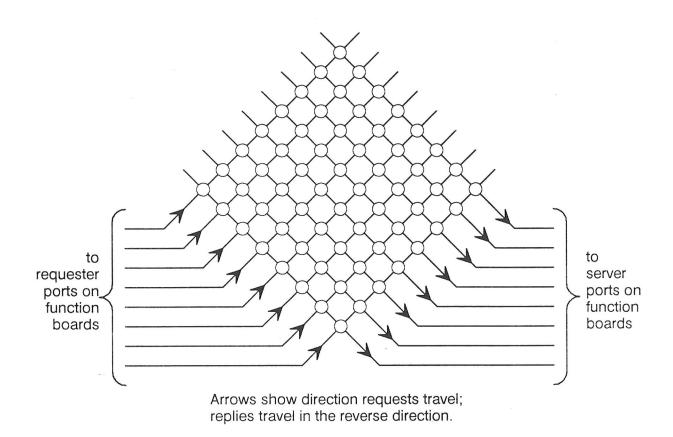

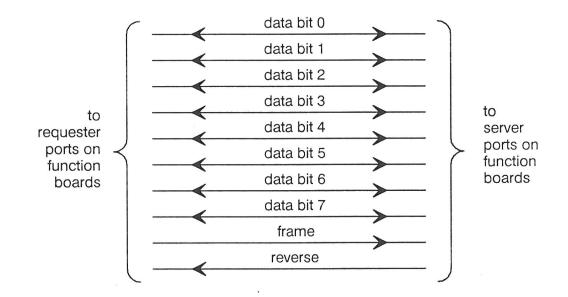

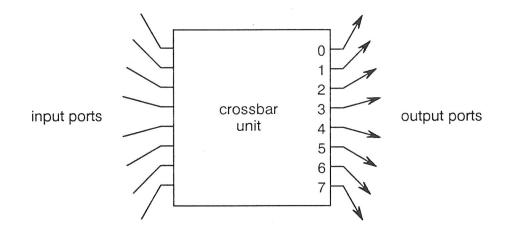

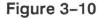

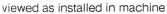

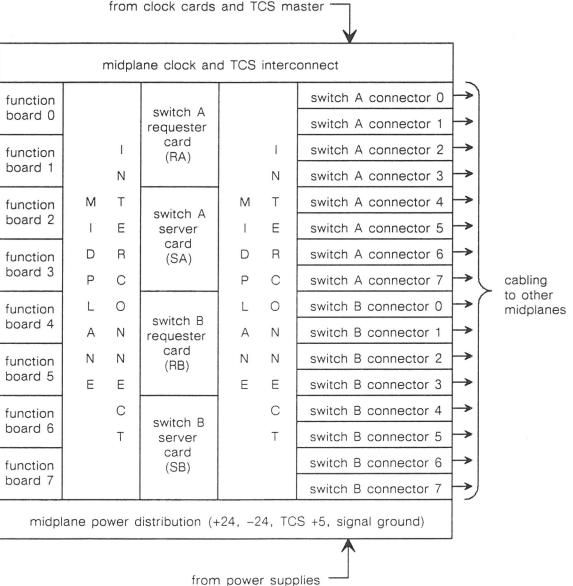

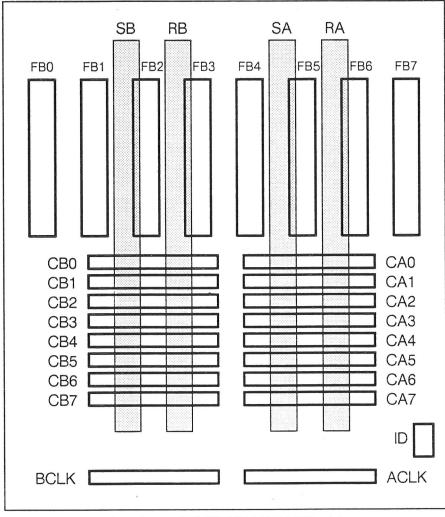

|      | 3.2.3   | Structure of the Switch                  | 83       |

| 3.3  |         | of Operation                             | 93       |

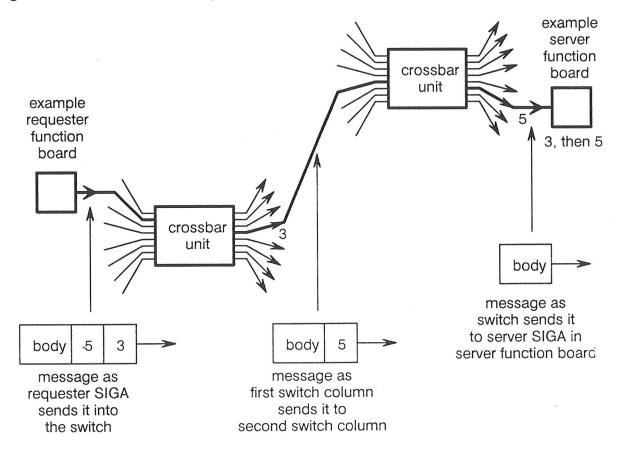

| 5.5  | 3.3.1   | Switch Message Contents                  | 93       |

|      | 3.3.2   | Routing a Message, Making a Path         | 93       |

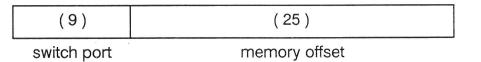

|      | 3.3.3   | Route Format and Use                     | 96       |

|      | 3.3.4   | Use of Alternate Paths                   | 98       |

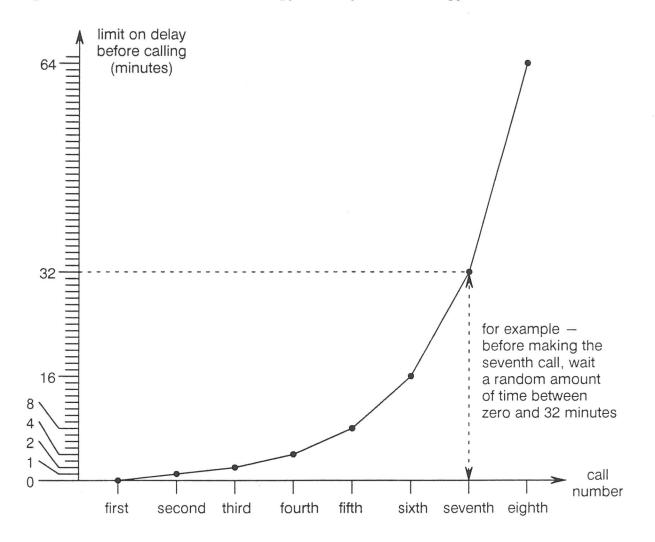

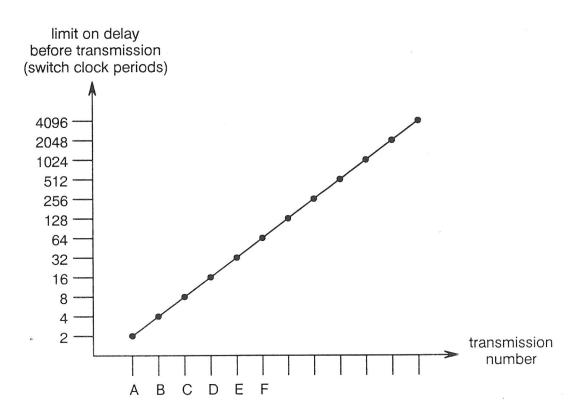

|      | 3.3.4   | Reject and Retry                         | 99       |

|      |         |                                          | 106      |

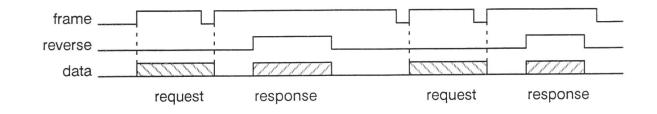

|      | 3.3.6   | Reply Messages — Bidirectional Path      | 100      |

|      | 3.3.7   | Multiple Messages per Connection         | 100      |

| 2.4  | 3.3.8   | Error Detection                          | 107      |

| 3.4  |         | es Important to the User                 |          |

|      | 3.4.1   | Locking                                  | 109      |

|      | 3.4.2   | Automatic Retry                          | 111      |

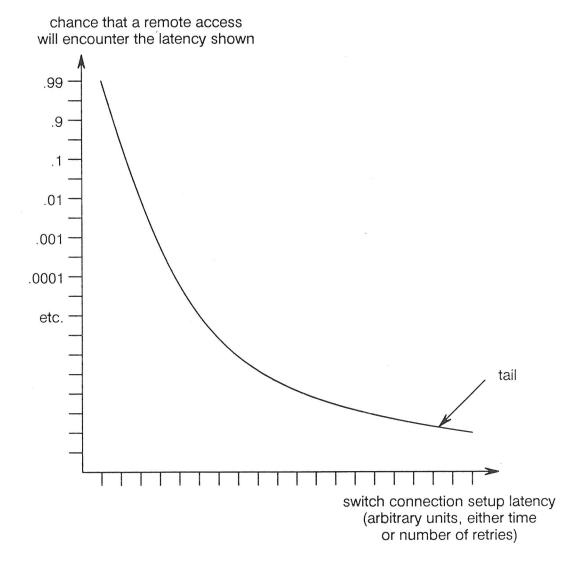

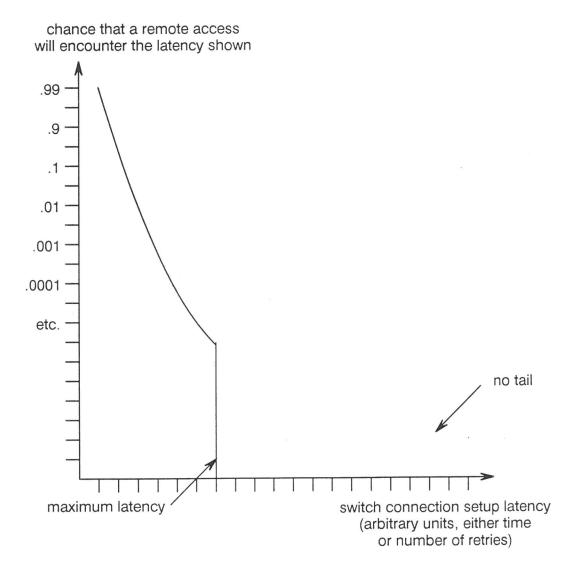

|      | 3.4.3   | Latency Control                          | 111      |

| 4    | emory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 19         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.1  | Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 119        |

| 4.2  | Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 122        |

|      | 4.2.1 Global Address Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 122        |

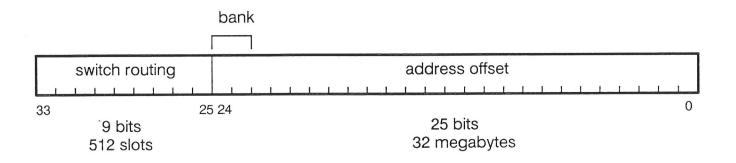

|      | 4.2.2 Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 123        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 126        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 126        |

| 4.3  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 127        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 129        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 132        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 133        |

| 4.4  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 133        |

|      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 133        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 134        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 135        |

|      | 1 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 137        |

| 15   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 142<br>142 |

| 4.5  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 142        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 142        |

|      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 145        |

|      | $B_{1}$ and $B_{2}$ and $B_{2$ | 145        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 148        |

|      | L L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 157        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 157        |

| 5    | O and the VMEbus Interface 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 59         |

| 5.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 159        |

| J.1  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 159        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 160        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 160        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 162        |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 165        |

| 5.2  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 166        |

|      | A Contraction of the second seco                                                                                                                                                                                                                                             | 166        |