| <br>CONFIDENTIAL |                                 | CONFIDENTIAL |  |

|------------------|---------------------------------|--------------|--|

|                  | TURBO MAC : HARDWARE MEMORY MAP |              |  |

|                  |                                 |              |  |

|                  | Burrell Smith and Brian Howard  |              |  |

|                  |                                 |              |  |

|                  | 17 October 1984                 |              |  |

| <br>CONFIDENTIAL |                                 | CONFIDENTIAL |  |

| Page 1                     | 1. INTRODUCTION                                                                                                                                        |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page 2<br>Page 3<br>Page 5 | <ul><li>2. THE TURBO MAC ADDRESS SPACE (Overview)</li><li>2.1 More Detailed Map of Turbo Mac Address Space</li><li>2.2 Address Line Decoding</li></ul> |

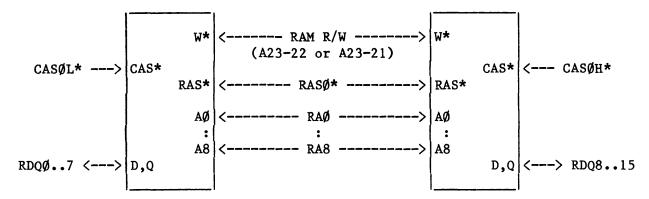

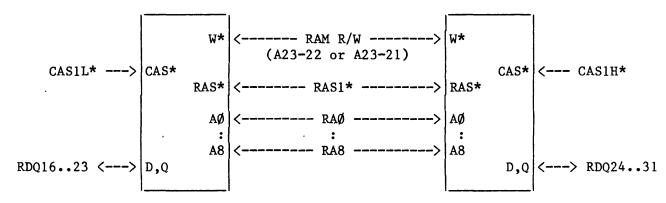

| Page 7                     | 3. RAM 3.1 Address Decoding to Activate RAMs                                                                                                           |

| Page 8                     | 3.2 Further RAM Address Decoding                                                                                                                       |

| Page 9                     | 3.3 Some Useful RAM Addresses                                                                                                                          |

| Page 10                    | 3.4 Use of RAM by Hardware                                                                                                                             |

|                            | 3.4.1 Map of RAM on Power-Up                                                                                                                           |

| Page 11                    | 3.4.2 Normal Map of RAM                                                                                                                                |

| Page 12                    | 3.5 Use of RAM by System and Application Software                                                                                                      |

| Page 13                    | 3.6 Hardware Exception Vectors                                                                                                                         |

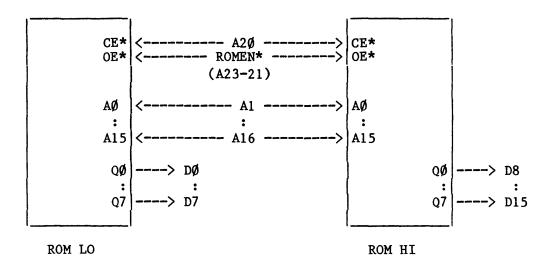

| Page 14                    | <ul><li>4. ROM</li><li>4.1 Address Decoding to Activate ROMs</li><li>4.2 Some Useful ROM Addresses</li></ul>                                           |

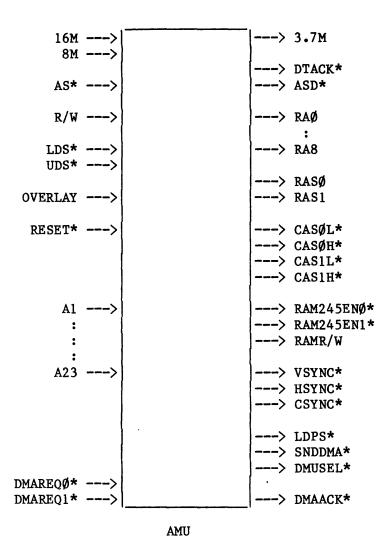

| Page 15                    | 5. AMU 5.1 Address Decoding to Activate AMU                                                                                                            |

| Page 16                    | 5.2 Further AMU Address Decoding<br>5.3 Some Useful AMU Addresses                                                                                      |

| Page 17                    | 5.4 Information About AMU Registers 5.4.1 DMA Address Registers                                                                                        |

| Page 19                    | 5.4.2 DMA Control Register                                                                                                                             |

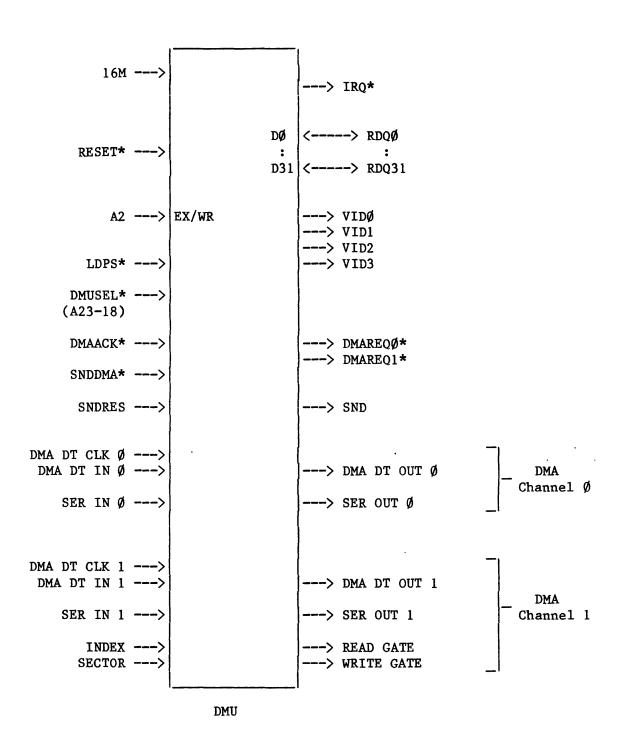

| Page 20                    | 6. DMU                                                                                                                                                 |

| Page 21                    | <ul><li>6.1 Address Decoding to Activate DMU</li><li>6.2 Further DMU Address Decoding</li><li>6.3 Some Useful DMU Addresses</li></ul>                  |

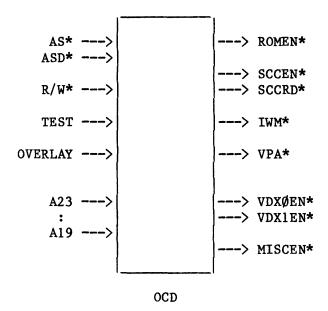

| Page 22                    | 7. RANDOM LOGIC CONTROL (VDXO, VDX1 and MISC) 7.1 Address Decoding to Activate Random Logic Control                                                    |

|                            |                                                                                                                                                        |

| Page 23                    | 7.1 Address becoding to Activate Random Logic Control 7.2 Some Useful Random Logic Control Addresses                                                   |

Daga 24

| Page | 24 | 8. SCC                                                    |

|------|----|-----------------------------------------------------------|

|      |    | 8.1 Address Decoding to Activate SCC                      |

| Page | 25 | 8.2 Further SCC Address Decoding                          |

|      |    | 8.3 Some Useful SCC Addresses                             |

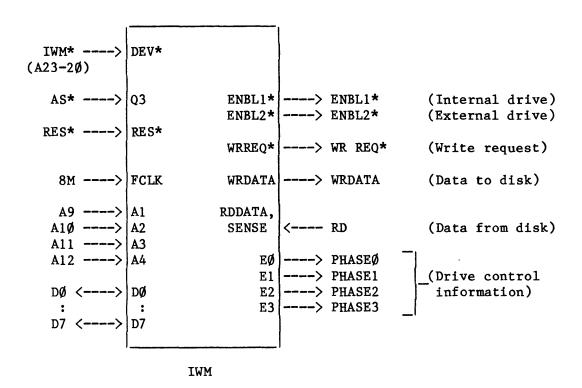

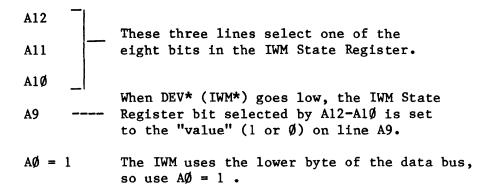

| Page | 26 | 9. IWM                                                    |

|      |    | 9.1 Address Decoding to Activate IWM                      |

| Page | 27 | 9.2 Further IWM Address Decoding                          |

|      |    | 9.3 Some Useful IWM Addresses                             |

| Page | 28 | 10. VIA                                                   |

|      |    | 10.1 Address Decoding to Activate VIA                     |

| Page | 29 | 10.2 Further VIA Address Decoding                         |

|      |    | 10.3 Some Useful VIA Addresses                            |

| Page | 30 | 10.4 Turbo-Mac-Specific Information about VIA Registers   |

|      |    | 10.4.1 Port A Input, Output, and Data Direction Registers |

|      |    | 10.4.2 Port B Input, Output, and Data Direction Registers |

| Page | 31 | 10.4.3 Control Registers                                  |

|      |    | 10.4.4 Interrupt Flag and Enable Registers                |

| Page | 32 | 11. AUTO-VECTOR "READ" ADDRESSES                          |

| _    |    | 10 000 000 000                                            |

| Page | 33 | 12. SOME USEFUL DECODING EQUATIONS                        |

Previous Document Versions: 19-Sep-84, 10-Sep-1984.

#### 1. INTRODUCTION

The principle portions of Turbo Mac's address space consist of volatile read/write memory (RAM) and permanent read-only memory (ROM). In addition to RAM and ROM, several input/output functions are also selected using address lines, so that they appear to occupy portions of the Turbo Mac "memory". These include the 6522 Versatile Interface Adapter (VIA), the 8530 Serial Communications Chip (SCC), the disk interface chip (IWM), the Address Management Unit (AMU), the Data Management Unit (DMU), and the Random Logic Control.

When the Turbo Mac is first turned on, ROM appears at the bottom (lowest addresses) portion of the address space. This is useful for the ROM-stored software which starts the system running. After startup, the OVERLAY signal from the VIA is changed to a low (zero), mapping RAM into its normal place at the bottom of the address space.

Selection of RAM, ROM, or other devices is done by from two to seven of the highest-order address lines, A23-A17. The VIA and IWM also use the four address lines A12-A9 for further internal decoding and register selection, while the SCC uses the three lowest-order address lines A2-AØ for internal decoding. When selecting certain AMU registers, the information on address lines A12-Al or A8-Al is used as data for the selected register. When selecting the DMU, address line A2 determines how the DMU control register is used.

# 2. THE TURBO MAC ADDRESS SPACE (Overview)

| Map on Power- | Up (OVERLAY = 1) | _\$100        | ØØØØ        | Normal Map | (OVERLAY = Ø)    |

|---------------|------------------|---------------|-------------|------------|------------------|

|               |                  | :<br>:_ \$FØ  | ØØØØ        |            |                  |

|               | VIA              | \$EØ          | ØØØØ        |            | VIA              |

|               | IWM              | \$DØ          | ØØØØ        |            | IWM              |

| MISC          | ENABLE           |               | ØØØØ        | MIS        | C ENABLE         |

| VDXØ an       | d 1 ENABLE       |               | øøøø –      | VDXØ a     | nd 1 ENABLE      |

| scc           | WRITE            | and           | aaaa        | SC         | C WRITE          |

| VDX1          | ENABLE           | <b>-</b> [-   | ØØØØ        | VDX        | 1 ENABLE         |

| VDXØ          | ENABLE           | 1             | ØØØØ        | VDX        | Ø ENABLE         |

| SC            | C READ           | _<br>\$9ø     | ØØØØ _      | S          | CC READ          |

|               |                  | :<br>_: \$7Ø  | 9000 :      |            | :<br>:           |

| RAM Row 2     | (512 K bytes)    | \$68          | :<br>ØØØØ : |            | :                |

|               | (512 K bytes)    |               | :<br>ØØØØ : |            | :                |

| DMU           | SELECT           | _ _ \$5C<br>: | ØØØØ :      |            |                  |

| AMU registers | Duplicate ROM    |               | ØØØØ :      |            | ROM (128K bytes) |

| on writes     | image on reads   | \$40          | ØØØØ _      |            | on_reads         |

|               |                  | :<br>: \$10   | ØØØØ        |            |                  |

|               |                  | :             |             | RAM Row 2  | (512 K bytes)    |

|               |                  | : \$Ø8<br>:   | ØØØØ _      |            |                  |

| AMU Reset     | ROM (128K bytes) | -i- \$Ø2      | ØØØØ        | RAM Row 1  | (512 K bytes)    |

| on writes     | on reads         | _ _ \$ØØ      | ØØØØ _      |            |                  |

# 2.1 More Detailed Map of Turbo Mac Address Space (two pages)

| (Auto-Vector Read) (AØ=Ø) |                                                            | FFFØ _                                                                                                 | : (Auto-Vector<br>:Read):<br>:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | No<br>device               |

|---------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                           | :<br>:<br>:                                                | :                                                                                                      | :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |

| (AØ=Ø)                    | :<br>:<br>:_ \$FØ                                          | dddd                                                                                                   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 00011                      |

| (AØ=Ø)                    | :<br>- \$FØ                                                | dddd                                                                                                   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | assigned                   |

| (AØ=Ø)                    | - \$FØ                                                     | dddd -                                                                                                 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |

| (A∅=∅)                    | ł                                                          | שששש                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|                           |                                                            |                                                                                                        | VIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (AØ=Ø)                     |

| 6 registers)              | _ \$EØ                                                     | ØØØØ                                                                                                   | (A9-12 select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | l6 registers               |

| (AØ=1)                    |                                                            |                                                                                                        | IWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (AØ=1)                     |

| 8 register                |                                                            |                                                                                                        | (A1Ø-12 select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8 register                 |

| bit value)                | [                                                          |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|                           | _ \$DØ                                                     | ØØØØ _                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|                           |                                                            |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|                           |                                                            |                                                                                                        | MISC ENABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

|                           | _ \$C8                                                     | 0000 _                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| ENARLE                    | ł                                                          |                                                                                                        | אצעה מאף ואטה אטאען                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ENARLE                     |

| JIMADEL                   | scø                                                        | ØØØØ                                                                                                   | VDXI IND VDXV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

| (10, 1)                   |                                                            |                                                                                                        | COC UDITAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | (14 1)                     |

| (AØ=1)                    |                                                            |                                                                                                        | SCC WRITE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $(A\emptyset=1)$           |

| =Data/Ctrl)               |                                                            | 1                                                                                                      | (A1=Ch.A/B. A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2=Data/Ctrl)               |

| 2000, 0021,               | \$BØ                                                       | ØØØØ                                                                                                   | (112 01111-7 2 , 11-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | - 2000, 0011,              |

| <del></del>               | - '                                                        |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|                           | 1                                                          |                                                                                                        | VDX1 ENABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

|                           | _ \$A8                                                     | ØØØØ _                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|                           | <b>\</b>                                                   |                                                                                                        | UDUA ENABEE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

|                           | CAG                                                        | dddd                                                                                                   | I ADYÑ ENVRTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

|                           | - SAW                                                      | שששש                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

| (AØ=1)                    | 1                                                          |                                                                                                        | SCC RESET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $(A\emptyset=1)$           |

| ` /                       |                                                            |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | · · · · · ·                |