# TECHNICAL MANUAL AM-600/T MAGNETIC TAPE FORMATTER INTERFACE

DWM-00607-00 REV. A00

## **FIRST EDITION**

May 1984 E.N. 01700

## **REVISIONS INCORPORATED**

REVISION

DATE

#### ©1984 ALPHA MICROSYSTEMS

THE INFORMATION CONTAINED IN THIS MANUAL IS BELIEVED TO BE ACCURATE AND RELIABLE. HOWEVER, NO RESPONSIBILITY FOR THE ACCURACY, COMPLETENESS OR USE OF THIS INFORMATION IS ASSUMED BY ALPHA MICRO.

This document may contain references to products covered under the following U.S. Patent Number(s): 4,530,048

### **PROPRIETARY NOTICE**

This document and the information herein disclosed is the confidental information and proprietary property of ALPHA MICRO, 3501 Sunflower, Santa Ana, California 92799. Any person or entity to whom this document is furnished or having possession thereof, by acceptance, assumes custody thereof and agrees that the document is given in confidence and will not be copied or reproduced in whole or in part, nor used or revealed to any person in any manner except to meet the purposes for which it was delivered. Additional rights and obligations regarding this document and its contents may be defined by a separate written agreement with ALPHA MICROSYSTEMS, and if so, such separate written agreement shall be controlling.

ALPHA MICROSYSTEMS 3501 Sunflower P.O. Box 25059 Santa Ana, Ca 92799

## Table of Contents

| CHAPTER | 1 | GENERAL | DESCRIPTION |  |

|---------|---|---------|-------------|--|

| UNAFIER | 1 | GENERAL | DESCRIPTION |  |

;

÷

| 1.1 | INTRODUCTION              | 1-1 |

|-----|---------------------------|-----|

|     | CIRCUIT BOARD DESCRIPTION |     |

| 1.3 | APPLICATION               | 1-5 |

## CHAPTER 2 OPERATING DATA

| 2.1<br>2.2<br>2.3        | CAPABILITI            | ES AND SPECIF<br>DESCRIPTION A<br>Alpha Micro B<br>Tape Transpor<br>Wiring and Co<br>User Options<br>2.3.4.1<br>Interrupts<br>DMA Options<br>CPU Compatibi<br>2.3.7.1<br>2.3.7.2 | ICATIONS<br>ND WIRING<br>us Interface<br>t Formatter Interface<br>nnections<br>Addressing<br>Lity<br>AM-100 CPU Compatibility<br>AM-100/T CPU Compatibility<br>AM-100/L CPU Compatibility | 2-1<br>2-3<br>2-10<br>2-12<br>2-16<br>2-16<br>2-16<br>2-18<br>2-18<br>2-18<br>2-18<br>2-19<br>2-19 |

|--------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| CHAPTER 3                | PROGRAMMI             | ٧G                                                                                                                                                                               |                                                                                                                                                                                           |                                                                                                    |

| 3_1<br>3_2<br>3_3<br>3_4 | I/O PORTS<br>DMA DATA | TRANSFER                                                                                                                                                                         |                                                                                                                                                                                           | 3-1<br>3-12                                                                                        |

| CHAPTER 4                | FUNCTIONAL            | L THEORY OF OP                                                                                                                                                                   | ERATIONS                                                                                                                                                                                  |                                                                                                    |

| 4.1<br>4.2               |                       | OARD OPERATION                                                                                                                                                                   | us Interface<br>J/O Port Decoding and Command<br>Generation<br>Datain Bus Interface<br>DATAOUT Bus Interface                                                                              | 4-2<br>4-23<br>4-23<br>4-23                                                                        |

|                          | 4.2.2                 |                                                                                                                                                                                  | Formatter Interface<br>Data Request Logic<br>Interrupt Logic<br>Lost Data Detector<br>Miscellaneous Latches                                                                               | 4-25<br>4-25<br>4-26<br>4-26                                                                       |

|                          | 4.2.3                 |                                                                                                                                                                                  | Control<br>Standard Alpha Micro bus<br>Exchange Timing (AM-100/T,<br>AM-100/L Systems)                                                                                                    | <b>4-</b> 27                                                                                       |

Page ii

|           | 4.2.3.2 AM-100 Compatible Bus Exchange<br>Timing                                               |                  |

|-----------|------------------------------------------------------------------------------------------------|------------------|

|           | 4.2.3.3Data Transfer Sequence4.2.3.4Processor Ready Detect Logic                               |                  |

|           | • •                                                                                            |                  |

|           | 4.2.4 DMA Address Generator/Byte Count Circuitry _<br>4.2.5 Test Jumper Blocks and Test Points |                  |

| 4.3       | • • • • • • • • • • • • • • • • • • • •                                                        |                  |

| 4         | 4.3.1 DMA Address Generator                                                                    |                  |

|           |                                                                                                |                  |

|           | 4.3.1.1 Architecture                                                                           |                  |

|           | 4.3.1.3 Instructions                                                                           |                  |

|           |                                                                                                | - 4-42           |

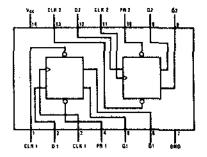

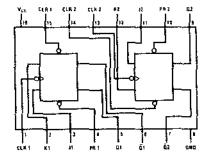

|           | 4.3.2 Dual D Positive-Edge-Triggered Flip-Flops<br>with Preset and Clear                       | 4-45             |

|           | 4.3.3 Dual J-K Negative-Edge-Triggered Flip-Flops                                              | 3 <b>4</b> ~4J   |

|           | with Preset and Clear                                                                          | 4-45             |

|           | 4.3.4 Decoder                                                                                  |                  |

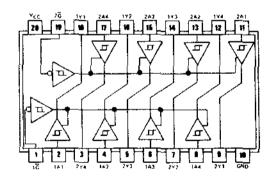

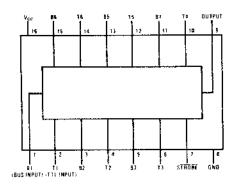

|           | 4.3.5 Inverting Octal Bus Driver                                                               |                  |

|           | 4.3.6 Noninverting Octal Bus Driver                                                            |                  |

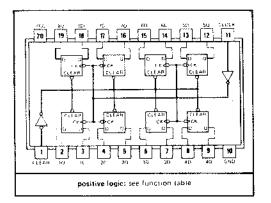

|           | 4.3.7 Octal D Register With Reset                                                              |                  |

|           | 4.3.8 Set-Reset Latches                                                                        |                  |

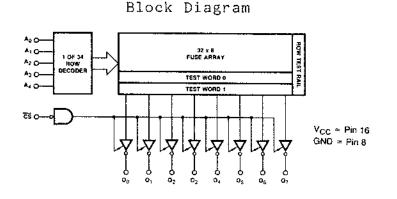

|           | 4.3.9 Bipolar PROM                                                                             |                  |

|           | 4.3.10 Tri-State D Flip-Flops                                                                  |                  |

|           | 4.3.11 Bus Comparator                                                                          |                  |

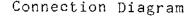

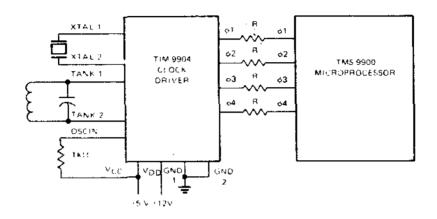

|           | 4.3.12 Four-Phase Clock Generator                                                              |                  |

|           |                                                                                                |                  |

| CHAPTER 5 | MAINTENANCE AND TROUBLESHOOTING                                                                |                  |

| 5.1       | INTRODUCTION                                                                                   | . 5-1            |

| 5.2       | CIRCUIT BOARD CHECKOUT                                                                         |                  |

| 5.3       | WARRANTY PROCEDURES                                                                            |                  |

|           |                                                                                                | ,, ,, <u>,</u> , |

CHAPTER 6 COMPONENT CROSS REFERENCE LIST

APPENDIX A PARTS LIST

APPENDIX B SCHEMATICS

INDEX

## LIST OF ILLUSTRATIONS

## Figure

1 - C

ŕ

· •

.

.

· · ·

<u>.</u> (

.

## Page v

## LIST OF TABLES

| Tab | le |

|-----|----|

|-----|----|

**1** 2

| Pa | g | e |

|----|---|---|

|----|---|---|

| 2-1<br>2-2 | AM-600/T Specifications                                   |      |

|------------|-----------------------------------------------------------|------|

| 2-3        | Tape Transport Formatter Interface Signals                |      |

| 2-4        | Adapter Wire List (sheet 1 of 2)                          | 2-14 |

| 3-1        | I/O Port Definitions                                      | 3-3  |

| 3-2        | External Control Register (Output Function)               | 3-4  |

| 3-3        | Transport Status Register (Input Function)                | 3-5  |

| 3-4        | Formatter Command Register (Output Function)              | 3-6  |

| 3-5        | Formatter Status Register (Input Function)                | 3-7  |

| 3-6        | Internal Control Register (Output Function)               | 3-8  |

| 3-7        | DMA Register Instructions                                 | 3-9  |

| 3-8        | Formatter Command Summary                                 | 3-11 |

| 4-1        | AM-600/T Signal List (sheet 1 of 9)                       | 4-5  |

| 4-2        | AM-600/T Magnetic Tape Interface Signals (sheet 1 of 7) . | 4-15 |

| 4-3        | DMA Register Instructions                                 | 4-43 |

5

Ĺ

#### CHAPTER 1

#### GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

This manual provides operating and maintenance instructions for the AM-600/T Magnetic Tape Transport Formatter Interface circuit board manufactured by Alpha Microsystems located in Irvine, California. Circuit board description, operating and usage instructions, programming, theory of operation, and maintenance instructions are included to provide the user with the information necessary to use this circuit board to its full capability.

#### 1.2 CIRCUIT BOARD DESCRIPTION

The AM-600/T circuit board provides a general purpose, single board interface capability between the Alpha Micro bus and the industry standard 1/2 inch magnetic tape formatter. The main features of the AM-600/T are as follows:

DWM-00607-00 REV A00

GENERAL DESCRIPTION

- \* Fully compatible with all Alpha Micro CPU boards (except AM-1000)

- \* Full DMA data transfer capability

- \* Interrupt capability provided

- \* Interfaces up to two formatters (eight transports total)

- \* Controls both seven and nine track tape transports

- Controls transports with densities of up to 3200 bytes per inch and tape velocities up to 37.5 ips

- \* Easy cabling interface via two 50-conductor flat ribbon cables

- Software control over virtually all standard formatter modes and operation

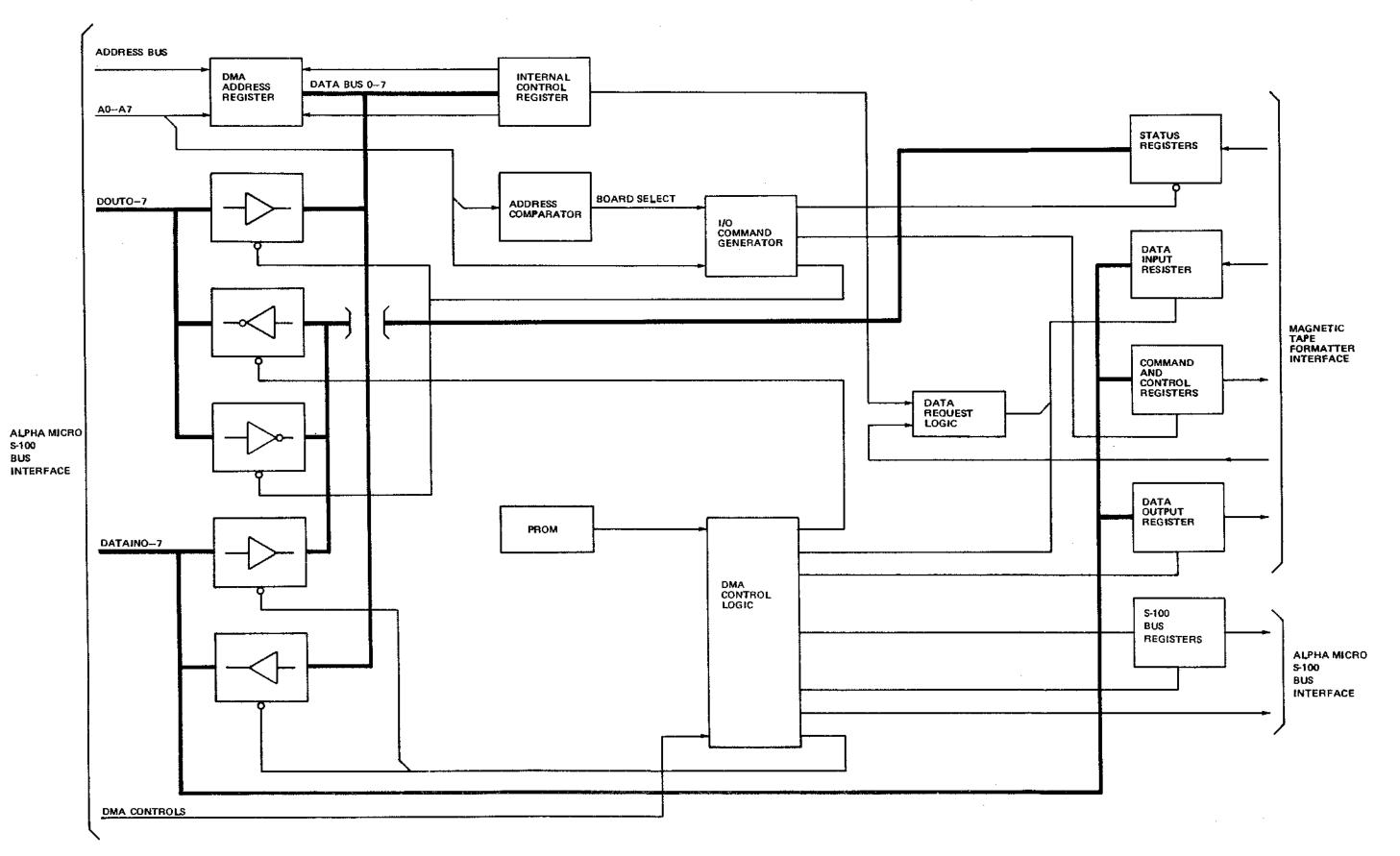

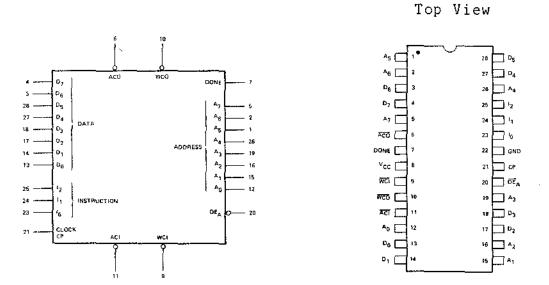

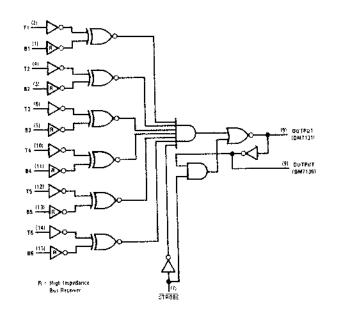

A simplified block diagram of the AM-600/T is shown in Figure 1-1. For a complete detailed description of circuit board operation, see Chapter 4 of this manual.

۰.

GENERAL DESCRIPTION

۴

i.

AM-600/T Simplified Block Diagram

, , ,

.

1

Sec. 40

· .... ·

\*

,

#### 1.3 APPLICATION

The AM~600/T is fully compatible with the standard Alpha Micro bus-based systems. Jumpers on the circuit board that provide for user selection are described in Chapter 2. The AM~600/T formatter interface directly controls both seven and nine track tape transports with 1/2 inch tape.

. .

1

· · ·

z Aj

#### CHAPTER 2

#### OPERATING DATA

#### 2.1 INTRODUCTION

This chapter contains information on the use of the AM-600/T Magnetic Tape Transport Formatter Interface circuit board. Capabilities, specifications, interface wiring, and user option descriptions are provided for the successful integration of the board into the user's system.

#### 2.2 CAPABILITIES AND SPECIFICATIONS

The AM-600/T circuit board provides general purpose, single board interface capability between the Alpha Micro bus and the industry standard 1/2 inch magnetic tape formatter. A maximum of two formatters can be used with each AM-600/T for a total of eight tape transports. Specifications for the AM-600/T circuit board are contained in Table 2-1.

DWM-00607-00 REV A00

.

. . .

į

| TABLE 2-1. AM | -600/T | Specifi | cations |

|---------------|--------|---------|---------|

|---------------|--------|---------|---------|

| PARAMETER     | SPECIFICATION                                                                                  |

|---------------|------------------------------------------------------------------------------------------------|

| Interface     | Alpha Micro bus for CPU, a maximum<br>of eight tape transports through<br>two formatter units. |

| Interrupts    | Multiple level interrupt capability, user selected.                                            |

| Tape Format   | Controls both 7 and 9 track tape formats.                                                      |

| Tape Density  | Controls transports with densities of up to 1600 bytes/inch.                                   |

| Tape Speed    | Controls transports with tape velocities<br>up to 37.5 inches/sec.                             |

| Data Transfer | Full DMA data transfer capability of<br>data blocks up to 65K bytes.                           |

| Board Control | Software control over virtually all standard formatter modes and operations.                   |

| Cables        | Two 50-conductor flat ribbon cables interface with formatter unit.                             |

| Circuit Board | Standard 9" x 10" with 100 pin connector<br>to interface with CPU bus system.                  |

| Power         | +8 V a 2.1 Amps                                                                                |

| Environmental | Temperature 10 to 30 degrees (Centigrade)<br>Humidity 10% - 80% (non-condensing)               |

#### OPERATING DATA

#### 2.3 INTERFACE DESCRIPTION AND WIRING

The AM-600/T circuit board provides interface capability between the standard Alpha Micro bus and magnetic tape transport formatter units.

#### 2.3.1 Alpha Micro Bus Interface

The AM-600/T circuit board is fully compatible with all Alpha Micro bus-oriented systems. The board and its associated tape transports are addressed through the address lines, and data is transferred through the standard data in and data out lines. The board is compatible with both the 8-bit bus configuration and also the 16-bit CPU configuration. See Paragraph 2.3.4 for selection of the various available user options.

Only DMA data transfers are accommodated for maximum data transfer rates. The Alpha Micro bus connections are made via the bottom edge connector and are listed in Table 2-2. See Chapter 4 for complete descriptions of all interface signals. OPERATING DATA

ć

į

| SIGNAL     | NAME                                                                                                      | J1<br>PIN NO. |

|------------|-----------------------------------------------------------------------------------------------------------|---------------|

| +8         | 8 Volts                                                                                                   | 1             |

| <u>V10</u> | Vectored Interrupt O                                                                                      | 4             |

| VIT        | Vectored Interrupt 1                                                                                      | 5             |

| VI2        | Vectored Interrupt 2                                                                                      | 6             |

| VIJ        | Vectored Interrupt 3                                                                                      | 7             |

| VI4        | Vectored Interrupt 4                                                                                      | 8             |

| VI5        | Vectored Interrupt 5                                                                                      | 9             |

| VIG        | Vectored Interrupt 6                                                                                      | 10            |

| <u>V17</u> | Vectored Interrupt 7                                                                                      | 11            |

| A18        | Address 18                                                                                                | 15            |

| A16        | Address 16                                                                                                | 16            |

| A17        | Address 17                                                                                                | 17            |

| STATDSB    | Status Bus Disable. A low<br>indicates a 16-bit transfer;<br>a high indicates an Address<br>bus transfer. | 18            |

| C/CDSB     | Command/Control Bus Disable                                                                               | 19            |

TABLE 2-2. Alpha Micro Bus Interface Signals (Sheet 1 of 6)

,

| SIGNAL | NAME                 | J1<br>PIN NO. |

|--------|----------------------|---------------|

| GND    | Ground               | 20            |

| ADDDSB | Address Bus Disable  | 22            |

| DODSB  | Data Bus Disable     | 23            |

| 02     | Phase 2 Clock        | 24            |

| STVAL  | Status Valid         | 25            |

| PHLDA  | DMA Acknowledge Line | 26            |

| PWAIT  | CPU Wait             | 27            |

| A5     | Address 5            | 29            |

| A4     | Address 4            | 30            |

| A3     | Address 3            | 31            |

| A15    | Address 15           | 32            |

| A12    | Address 12           | 33            |

| A9     | Address 9            | 34            |

| D01    | Bits 0-7             | 35            |

| DOO    | Data Out Bus         | 36            |

| A10    | Address 10           | 37            |

Table 2-2. Alpha Micro Bus Interface Signals (Sheet 2 of 6)

| SIGNAL  | NAME                     | J1<br>PIN NO. |

|---------|--------------------------|---------------|

| D04     | Data Out Bus             | 38            |

| D05     | Data Out Bus             | 39            |

| D06     | Data Out Bus             | 40            |

| DATAIN2 | Data In Bus              | 41            |

| DATAIN3 | Data In Bus              | 42            |

| DATAIN7 | Đata In Bus              | 43            |

| SM1     | Bus Master OP Code Fetch | 44            |

| SOUT    | I/O Output Cycle         | 45            |

| SINP    | I/O Input Cycle          | 46            |

| SMEMR   | Memory Read Cycle        | 47            |

| SWLTA   | Halt Acknowledge         | 48            |

| GND     | Ground                   | 50            |

| +8      | +8 Volts                 | 51            |

| DMAO    | Direct Memory Access     | 55            |

| DMA 1   | Direct Memory Access     | 56            |

Table 2-2. Alpha Micro Bus Interface Signals (Sheet 3 of 6)

.

.

| SIGNAL NAME |                                                                                                        | J1<br>PIN NO. |

|-------------|--------------------------------------------------------------------------------------------------------|---------------|

| DMA2        | Direct Memory Access                                                                                   | 57            |

| SXTRQ       | 16-bit Request                                                                                         | 58            |

| A19         | Address 19                                                                                             | 59            |

| A20         | Address 20                                                                                             | 61            |

| A21         | Address 21                                                                                             | 62            |

| A22         | Address 22                                                                                             | 63            |

| A23         | Address 23                                                                                             | 64            |

| ADVAL       | Optional signal which indi-<br>cates that the upper byte<br>address information is on<br>the data bus. | 65            |

| WRDIS       | Prevents write execution                                                                               | 66            |

| DMARCVD     | DMA Received                                                                                           | 69            |

| GND         | Ground                                                                                                 | 70            |

| PRDY        | Ready                                                                                                  | 72            |

| PHOLD       | DMA Request Line                                                                                       | 74            |

## Table 2-2. Alpha Micro Bus Interface Signals (Sheet 4 of 6)

DWM-00607-00 REV A00

|        |                                        | · · · · · · · · · · · · · · · · · · · |

|--------|----------------------------------------|---------------------------------------|

| SIGNAL | NAME                                   | J1<br>PIN NO.                         |

| PSYNC  | Processor Sync, Start of<br>Bus Cycle. | 76                                    |

| PWR    | Write Strobe                           | 77                                    |

| PDBIN  | Data Bus Input Command                 | 78                                    |

| AO     | Address D                              | 79                                    |

| A1     | Address 1                              | 80                                    |

| A2     | Address 2                              | 81                                    |

| A6     | Address 6                              | 82                                    |

| A7     | Address 7                              | 83                                    |

| A8     | Address 8                              | 84                                    |

| A13    | Address 13                             | 85                                    |

| A14    | Address 14                             | 86                                    |

| A11    | Address 11                             | 87                                    |

| D02    | Data Out Bus                           | 88                                    |

Table 2-2. Alpha Micro Bus Interface Signals (Sheet 5 of 6)

.

f

| SIGNAL  | NAME                    | J1<br>PIN NO. |

|---------|-------------------------|---------------|

| DÇ3     | Data Qut Bus            | 89            |

| D07     | Data Out Bus            | 90            |

| DATAIN4 | Data In Bus             | 91            |

| DATAIN5 | Data In Bus             | 92            |

| DATAIN6 | Data In Bus             | 93            |

| DATAIN1 | Data In Bus             | 94            |

| DATAINO | Data In Bus             | 95            |

| SINTA   | Interrupt Acknowledge   | 96            |

| SWO     | Bus Master Output Cycle | 97            |

| GND     | Ground                  | 100           |

Table 2-2. Alpha Micro Bus Interface Signals (Sheet 6 of 6)

#### 2.3.2 Tape Transport Formatter Interface

The tape transport formatter circuit board interfaces with a maximum of eight tape transports through two formatter units. Interface signal connections are made through J2 and J3 on the top edge of the circuit board and are listed in Table 2-3. See Chapter 4 for a complete description of interface signals. 7

| TABLE 2-3. Tape Transport Formatter Interface Signals |               |     |            |     |            |     |       |

|-------------------------------------------------------|---------------|-----|------------|-----|------------|-----|-------|

| J2                                                    |               | J3  |            |     |            |     |       |

| PIN                                                   | NAME          | PIN | NAME       | PIN | NAME       | PIN | NAME  |

| 1                                                     | G             | 26  | ਯਤ         | 1   | RP         | 26  | NRZI  |

| 2                                                     | FBY           | 27  | G          | 2   | RO         | 27  | G     |

| 3                                                     | G             | 28  | <b>W</b> 6 | 3   | R1         | 28  | RDY   |

| 4                                                     | LWD           | 29  | G          | 4   | LP         | 29  | G     |

| 5                                                     | G             | 30  | <u>W2</u>  | 5   | G          | 30  | RWD   |

| 6                                                     | <del>W4</del> | 31  | G          | 6   | R4         | 31  | G     |

| 7                                                     | G             | 32  | W5         | 7   | G          | 32  | FPT   |

| 8                                                     | GO            | 33  | G          | 8   | R7         | 33  | G     |

| 9                                                     | G             | 34  | WRT        | 9   | G          | 34  | RSTR  |

| 10                                                    | WO            | 35  |            | 10  | RG         | 35  | G     |

| 11                                                    | G             | 36  |            | 11  | G          | 36  | WSTR  |

| 12                                                    | ₩1            | 37  | G          | 12  | HER        | 37  | G     |

| 13                                                    |               | 38  | EDIT       | 13  | G          | 38  | DBY   |

| 14                                                    | SGL           | 39  | G          | 14  | FMK        | 39  |       |

| 15                                                    |               | 40  | ERASE      | 15  | G          | 40  | SPEED |

| 16                                                    |               | 41  | G          | 16  | <u>ccs</u> | 41  |       |

| 17                                                    | G             | 42  | WFM        | 17  | G          | 42  | CER   |

| 18                                                    | REV           | 43  |            | 18  | FEN        | 43  | G     |

| 19                                                    | G             | 44  |            | 19  | G          | 44  | ONL   |

| 20                                                    | REW           | 45  | PAR        | 20  | R5         | 45  |       |

| 21                                                    |               | 46  |            | 21  | G          | 46  | TAD   |

| 22                                                    | WP            | 47  | G          | 22  | EOT        | 47  |       |

| 23                                                    | G             | 48  | RZ         | 23  | G          | 48  | FAD   |

| 24                                                    | W7            | 49  | G          | 24  | OFL        | 49  |       |

| 25                                                    | G             | 50  | RJ         | 25  | 77K        | 50  | DEN   |

TABLE 2-3. Tape Transport Formatter Interface Signals

G = Ground

: .\_.

#### 2.3.3 Wiring and Connections

For formatters with flat cable interface, the connections are straight forward since no pin translations are required. The maximum overall cable length is 20 feet. If two formatters are daisy-chained together, terminating resistors should be left only in the formatter at the end of the chain.

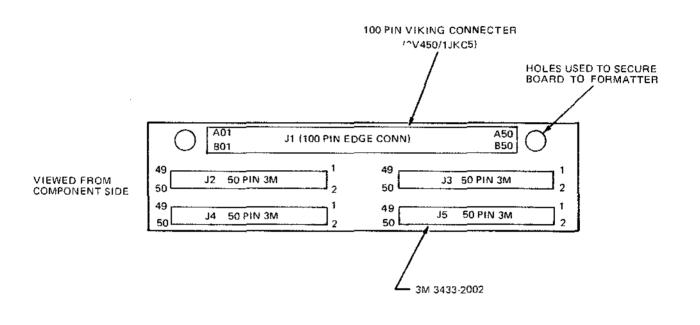

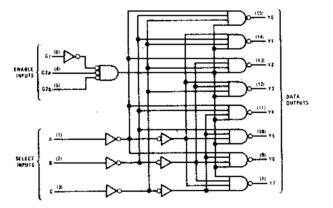

Formatters with a 100 pin PC edge connection require an adapter board (DWB-00601-00) to connect the flat cable to the edge connector. One adapter board is required for each formatter unit, and the formatters can be daisy-chained as described in the previous paragraph. The adapter board is shown in Figure 2-1, and the wire list is given in Table 2-4.

•

.

¥

- J2, J4: ALL ODD PINS EXCEPT 1, 3, 45 ARE TIED TO GROUND. J3, J5: ALL ODD PINS ARE TIED TO GROUND EXCEPT PIN 25 J1: THE FOLLOWING PINS ARE TIED TO GROUND: A02, B02, A05, B05, A09, B09, A11, B11, A14, B14, A17, B17, A20, B20, A23, B23 A26, B26, A29, B29, A32, A35, A39, B38, A41, B41

FIGURE 2-1. Adapter for 100 Pin Edge Connector to Flat Cables

;

ŝ

ŝ

|        | r               | ······ |                |

|--------|-----------------|--------|----------------|

| SIGNAL |                 |        |                |

| NAME   | FRÓM            | то     | то             |

|        |                 |        |                |

| TADO   | J1-A01          | J2-46  | J4-46          |

| FAD    | J1-B01          | J3-48  | J5 <b>-</b> 48 |

| 60     | J1-A03          | J2-8   | J4-8           |

| TAD1   | J1-803          | J3-46  | J5-46          |

| WRT    | J1-A04          | J2-34  | J4-34          |

| REV    | J1-в04          | J2-18  | J4-18          |

| EDIT   | J1-A06          | J2-38  | J4-38          |

| WFM    | J1-ВО6          | J2-42  | J4-42          |

| THR1   | J1-A07          | J2-44  | J <b>4-44</b>  |

| ERASE  | J1-B07          | J2-40  | J4-40          |

| DEN    | J1-A09          | J3-50  | J5-50          |

| THR2   | <b>ј1-</b> ВО9  | J2-36  | J4-36          |

| N/C    | J1~A10          | N/C    | N/C            |

| PAR    | J <b>1-</b> B10 | J2-45  | J4-45          |

| OFL    | J1-A12          | J3-24  | J5-24          |

| REW    | J1-B12          | J2-20  | J4-20          |

| FEN    | J1-A13          | J3-18  | J5 <b>-1</b> 8 |

| LWD    | J1-B13          | J2-4   | J4-4           |

| WP     | J1-A15          | J2-22  | J4-22          |

| N/C    | J <b>1-</b> В15 | N/C    | N/C            |

| ₩1     | J1-A16          | J2-12  | J4-12          |

| WO     | J1-816          | J2-10  | J4-10          |

| ₩3     | J1-A18          | J2-26  | J4-26          |

| W2     | J1-B18          | J2-30  | J4-30          |

| W3     | J1-A18          | J2-26  | J4-26          |

| W4     | J1-819          | J2-6   | J4-6           |

| W7     | J1-A21          | J2-24  | J4-24          |

| W6     | J <b>1-</b> В21 | J2-28  | J4-28          |

| DBY    | J1-A22          | J3-38  | J5-38          |

TABLE 2-4. Adapter Wire List (sheet 1 of 2)

٩,

÷

1

|             |                 |       | <u> </u>       |  |

|-------------|-----------------|-------|----------------|--|

| SIGNAL      |                 |       |                |  |

| NAME        | FROM            | то    | то             |  |

|             |                 |       |                |  |

| FBY         | J1-B22          | 75-5  | J4-2           |  |

| HER         | J1-A24          | J3-12 | J5-12          |  |

| CCG         | J1~B24          | J3~16 | J5-16          |  |

| FMK         | J1-A25          | J3-14 | J5-14          |  |

| CER         | J1-825          | J3-42 | J5-42          |  |

| ONL         | J1-A27          | J3-44 | J5-44          |  |

| RDY         | J1-827          | J3-28 | J5-28          |  |

| FPT         | J1-A28          | J3-32 | J5 <b>-</b> 32 |  |

| RWD         | J1-B28          | J3-30 | J5-30          |  |

| EOT         | J1-A30          | J3-22 | J5-22          |  |

| LP          | J1-B30          | J3-4  | j5-4           |  |

| NRZI        | J1-A31          | J3-26 | J5-26          |  |

| N/C         | J1-831          | N/C   | N/C            |  |

| SGL         | J1-A33          | J2-14 | J4-14          |  |

| <b>7</b> TK | J1-B33          | J3-25 | J5-25          |  |

| WSTR        | J1-A34          | J3-36 | J5-36          |  |

| SPEED       | J1-834          | J3-40 | J5-40          |  |

| RP          | J1-A36          | J3-1  | J5-1           |  |

| RSTR        | J1-B36          | J3-34 | J5-34          |  |

| R1          | J1-A37          | J3-3  | J5-3           |  |

| RŪ          | J1-837          | J3-2  | J5-2           |  |

| R3          | J1-A39          | J2-50 | J4-50          |  |

| R2          | J1-B39          | J2-48 | J4-48          |  |

| 85          | J1-A40          | J3-20 | J5-20          |  |

| R4          | J1-B40          | J3-6  | j5-6           |  |

| R7          | J1-A42          | J3-8  | J <b>5-</b> 8  |  |

| RŐ          | J <b>1-</b> B42 | J3-10 | J5-10          |  |

| LOL         | N/C             | J2-16 | J4-16          |  |

| RG          | J <b>1-</b> B42 | J3-10 | J5-10          |  |

Table 2-4. Adapter Wire List (Sheet 2 of 2)

ł

2.3.4 User Options

The AM-600/T circuit board accommodates several options that are selected by the user for specific requirements. These options are for addressing, interrupts, DMA selections, CPU type, memory addressing, and tape formatter options. The following sections describe these jumper options in detail.

#### 2.3.4.1 Addressing

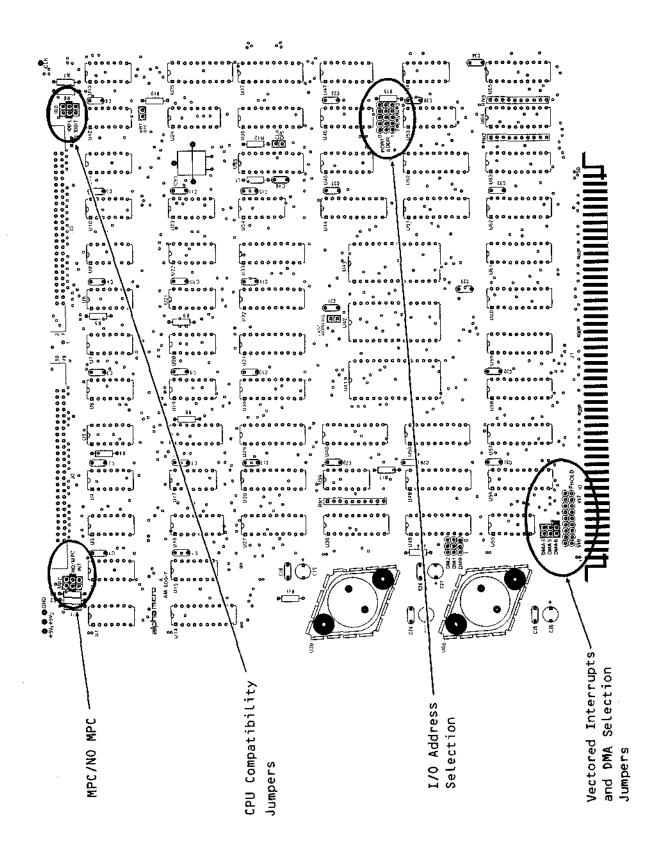

The standard I/O address block for the AM-600/T is A3 through A7 and is etched on the printed circuit board. If a different address block is desired, cut the appropriate etch on the component side of the board and jumper the board for the desired address (see Figure 2-2).

FIGURE 2-2. Jumper Options

#### 2.3.5 Interrupts

The interrupt signal from the AM-600/T ( $\overline{INTR}$ ) can be jumpered to any of the vectored interrupt lines  $\overline{VIO}$ - VI7. The standard configuration is with no jumpers connected. If required, the jumpers are located in the lower left section of the board as shown in Figure 2-2.

#### 2.3.6 DMA Options

Two modes of DMA operation are possible with the AM-600/T. The first mode releases the bus to the CPU after every read or write cycle. With this mode of operation, the AM-600/T must re-acquire control of the bus as each byte of data is ready for transmission. This is the recommended mode for magnetic tape drives.

The second mode of operation retains control of the bus until the entire command has been completed. Therefore, if a large block of data were to be read from memory and stored on the tape, all the data would be transferred without the CPU regaining control of the bus. This mode should only be used when the data transfer speed is high enough such that re-acquiring the bus in between data byte transfers results in insufficient data transfer rates. This mode of operation can be selected under software control. See Chapter 3.

#### 2.3.7 CPU Compatibility

The AM-600/T is compatible with the Alpha Micro AM-100 CPU, Alpha Micro AM-100/T and AM-100/L 16-bit CPUs. Some of these boards may require jumper modifications or etch cuts for purposes of compatability. The following paragraphs describes these modifications on a board by board basis. 2.3.7.1 AM-100 CPU Compatibility

To provide AM-600/T compatibility with the Alpha Micro AM-100 CPU, jumpers must be installed in both the AM-600/T and the AM-100 board No. 2.

On the AM-600/T board install the following jumpers as required. (Refer to Figure 2-2.)

Set DMA level 5. This may be accomplished by cutting the etch at DMA 6 (used for AM-100/T and AM-100/L systems) then jumpering the board for DMA 5.

NO/MPC is the standard setting and should not require modification.

CPU jumper should be set for AM-100.

The following jumpers are required on the AM-100 Circuit Board No. 2 for system compatiblity. Refer to the <u>AM-100 Technical Manual</u>, DWM-00100-00, for further information.

a. DMAGRANT5 jumper.b. DMA Request 5 jumper (VI5).

2.3.7.2 AM-100/T CPU Compatibility.

Verify the following jumper settings. (Refer to Figure 2-2.)

DMA level 6 has been assigned to the AM-600/T interface. The board is etch strapped for this assignment and should require no modification.

DWM-00607-00 REV A00

NO/MPC is the standard setting and should require no modification. However, if your system should contain an AM-700 board in combination with the AM-100/T, this jumper should be set to the MPC position. For further jumper information regarding the AM-700 board refer to the AM-700 Installation Instructions, PDI-00700-00.

Set the CPU selection jumper to AM-100/T.

2.3.7.3 AM-100/L CPU Compatibility

No AM-600/T jumper modifications are required with the AM-100/L CPU, although you may wish to verify these settings. (Refer to Figure 2-2.)

DMA level 6. This is the standard setting as it comes from Alpha Micro.

NO/MPC is the standard setting.

CPU jumper should be configured for the AM-100/L.

CHAPTER 3

PROGRAMMING

#### 3.1 INTRODUCTION

This chapter describes the programming requirements for the AM-600/T circuit board. I/O ports and data transfer and controls are described for integration into the user's system.

#### 3.2 I/O PORTS

Eight I/O ports are required by the AM-600/T circuit board as shown in Table 3-1 through 3-7. The I/O port address is jumper selectable by a series of jumpers as described in Chapter 2 of this manual. The standard I/O address range is: A3-A7. Table 3-1 summarizes the functions of each I/O port.

s 2 .

The function of each of the I/O registers is as follows:

- External Control Register. Selects address and controls for selected tape transport. See Table 3-2 for a description of control bits.

- Transport Status Register. Indicates mode and status of selected tape transport. See Table 3-3 for a description of status bits.

- Formatter Command Register. Selects tape mode and motion to the selected transport. See Table 3-4 for a description of control bits.

- Formatter Status Register. Indicates status of formatter. See Table 3-5 for a description of status bits.

- 5. <u>Internal Control Register</u>. Contains enables and DMA register instructions. See Table 3–6 for a description of control bits.

- 6. <u>Formatter Command Summary</u>. See Table 3-8 for a description of various legal commands.

- 7. <u>DMA Address Register/Word Count Register</u>. A 24 bit DMA controller is contained in the DMA logic and may be programmed as outlined in the following paragraph.

The command for all 8-bit bytes may be set up by loading bits 5-7 of the internal control register. After the command has been set up, the appropriate byte may be clocked by an output to either I/O port A4 (low byte), A5 (middle byte), or A6 (high byte). After all parameters of the DMA controller have been set up, the DMA controller must be enabled (command = 111) before performing any DMA operation (READ or WRITE from mag tape). After completing a READ block command, the DMA Word Count Registers may be read to determine the data block size. See Table 3-7 for a summary of DMA controller instructions. See Chapter 4 for detailed specifications of the DMA address generator circuit.

DWM-00607-00 REV A00

| I/O PORT* | INPUT                                   | OUTPUT                                  | COMMENTS               |

|-----------|-----------------------------------------|-----------------------------------------|------------------------|

| хO        | Transport Status                        | EXT Control Register                    | See Tables<br>3-2, 3-3 |

| X1        | Formatter Status                        | Formatter Command<br>Register           | See Tables<br>3-4, 3-5 |

| X2        |                                         |                                         | Not used               |

| Х3        | Not Used                                | INT Control Register                    | See Table<br>3-6       |

| X4        | DMA Register Low Byte<br>(A0-A7)        | DMA Register Low Byte<br>(A0-A7)        | See<br>Chapter 4       |

| x5        | DMA Register<br>Middle Byte<br>(A8-A15) | DMA Register<br>Middle Byte<br>(A8-A15) | See<br>Chapter 4       |

| X6        | DMA Register<br>High Byte<br>(A16-A23)  | Data Register<br>High Byte<br>(A16-A23) | See<br>Chapter 4       |

| X7        |                                         |                                         | Not used.              |

TABLE 3-1. 1/0 Port Definitions

$\star$  I/O port address is jumper selectable to any even block of I/O addresses. :AO-:A7 is the standard I/O address range.

· . ·

÷.

1

TABLE 3-2. External Control Register (Output Function)

| віт    | FUNCTION                                   | COMMENTS                                                                                 |

|--------|--------------------------------------------|------------------------------------------------------------------------------------------|

| 0<br>1 | Transport Address O<br>Transport Address 1 | Binary address for up to four transports.                                                |

| 2      | Formatter Address 1                        | Selects one of two formatters.                                                           |

| 3      | Read Threshold 1                           | Specifies high threshold for read after write operation.                                 |

| 4      | Read Threshold 2                           | Specifies an extra low threshold<br>level for the real electronics in<br>the tape drive. |

| 5      | Low Density Select                         | Selects lower data transfer<br>packing density.                                          |

| 6      | Not Used                                   |                                                                                          |

| 7      | Not Used                                   |                                                                                          |

PROGRAMMING

7

Page 3-5

| BIT | FUNCTION     | COMMENTS                                                                |

|-----|--------------|-------------------------------------------------------------------------|

| D   | 7 Track      | Indicates transport is in 7 track mode.                                 |

| 1   | NRZI Mode    | Indicates transport is in NRZI mode.                                    |

| 2   | End of Tape  | Indicates end of tape has been<br>detected during the previous command. |

| 3   | Load Point   | Indicates load point on tape.                                           |

| 4   | File Protect | Indicates file protect status.                                          |

| 5   | Rewinding    | Indicates transport is rewinding.                                       |

| 6   | On-Line      | Indicates transport is on line.                                         |

| 7   | Ready        | Indicates transport ready status.                                       |

TABLE 3-3. Transport Status Register (Input Function)

DWM-00607-00 REV A00

PROGRAMMING

Page 3-6

• •

.

ł,

.

| TABLE 3-4. Formatter Com | and Register | (Output | Function) |

|--------------------------|--------------|---------|-----------|

|--------------------------|--------------|---------|-----------|

| BIT | FUNCTION        | COMMENTS                                                                                                                                                         |

|-----|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Reverse         | Determines direction of tape motion.                                                                                                                             |

| 1   | Write           | Specifies write mode when asserted,                                                                                                                              |

| 2   | Write File Mark | File mark written on tape, or in<br>read mode, this bit is set to skip<br>to the next block.                                                                     |

| 3   | Edit            | Edit mode of operation.                                                                                                                                          |

| 4   | Erase           | Selects erase mode.                                                                                                                                              |

| 5   | Rewind Pulse    | Setting and then resetting this bit<br>causes the selected transport<br>to rewind to load point.                                                                 |

| 6   | Off-Line Pulse  | Setting and then resetting this bit<br>causes the selected transport to go<br>off-line and into local mode.                                                      |

| 7   | Go Pulse        | Setting and then resetting this bit,<br>while holding the other bits stable,<br>will initiate a command to the for-<br>matter. See Command Summary in Table 3-8. |

ć

| TABLE 3-5. | Formatter | Status | Register | (Input | Function) |

|------------|-----------|--------|----------|--------|-----------|

|------------|-----------|--------|----------|--------|-----------|

| BIT | FUNCTION       | COMMENTS                                                                                                                            |

|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Done           | Indicates that the pre-programmed<br>byte count has been satisfied by<br>the appropriate command.                                   |

| 1   | Hard Error     | Indicates detection of uncorrectable<br>read error. This bit must be ignored<br>if filemark is detected (bit 2).                    |

| 2   | Filemark       | Indicates detection of a tape filemark.                                                                                             |

| 3   | PE Tape        | Indicates the presence of a phase<br>encoded tape, if transport is in<br>phase encoded mode. (Not latched<br>on interface).         |

| 4   | Data Request   | Indicates interface is ready for<br>additional READ or WRITE byte<br>operations.                                                    |

| 5   | Lost Data      | Indicates data lost during either a<br>READ or WRITE command.                                                                       |

| 6   | Interrupt      | Indicates that an interrupt has been<br>generated by the AM-600/T. This bit<br>is only valid after a GO command has<br>been issued. |

| 7   | Formatter Busy | Indicates that formatter is processing a command.                                                                                   |

۲

## TABLE 3-6. Internal Control Register (Output Function)

| BIT         | FUNCTION                | COMMENTS                                                                                                                                                                                                                                                                    |

|-------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0           | Not Used                |                                                                                                                                                                                                                                                                             |

| 1           | HDG                     | This bit is used to select the DMA mode of operation. See Chapter 3.3.                                                                                                                                                                                                      |

| 2           | Internal MPC<br>Control | If the MPC shorting block is positioned to<br>internal, this bit allows software control of<br>the MPC jumpers. O = No MPC 1 = MPC                                                                                                                                          |

| 3           | Interface Enable        | Enables interface logic and formatter<br>logic.                                                                                                                                                                                                                             |

| 4           | Interrupt Enable        | Enables interrupt logic.                                                                                                                                                                                                                                                    |

| 5<br>6<br>7 | IO<br>I1<br>I2          | DMA Register instructions. See detailed<br>description of command codes contained<br>in Table 3-7. Before issuing any READ<br>or WRITE command to the formatter, the<br>DMA registers must be enabled (111 code).<br>See paragraph 4.3.1.2 for control mode<br>description. |

÷.,•

ł

| ۱ <sub>2</sub> | կ   | I <sub>0</sub> | Octal<br>Code | Function                     | Mnemonic | Control<br>Mode                                        | Word<br>Reg. | Word<br>Counter | Address<br>Reg.         | Address<br>Counter | Control<br>Register   | Data<br>D <sub>0</sub> ·D <sub>7</sub>         |

|----------------|-----|----------------|---------------|------------------------------|----------|--------------------------------------------------------|--------------|-----------------|-------------------------|--------------------|-----------------------|------------------------------------------------|

| Ļ              | L   | L              | 0             | WRITE<br>CONTROL<br>REGISTER | WRCA     | 0, 1, 2, 3                                             | HOLD         | HOLD            | HOLD                    | HOLD               | D <sub>0'</sub> D₂→CR | INPUT                                          |

| L              | L   | н              | 1             | READ<br>CONTROL<br>REGISTER  | ROCR     | 0. 1. 2. 3                                             | HOLD         | HQLD            | HOLD                    | HOLD               | HOLD                  | CR +D <sub>0</sub> -D <sub>2</sub><br>(Note 1) |

| L              | н   | L              | 2             | READ<br>WORD<br>COUNTER      | ROWC     | 6 1, 2, 3                                              | HOLD         | HQLD            | HOLD                    | HOLD               | HOLD                  | ₩C→D                                           |

| L              | н   | н              | з             | AEAD<br>ADDRESS<br>COUNTER   | RDAC     | 0, 1, 2, 3                                             | HOLD         | HOLD            | HOLD                    | HOLD               | HOLD                  | AÇ →D                                          |

|                |     |                |               | <b>BEINITIALIZE</b>          | REIN     | 0, 2, 3                                                | HÖLÖ         | WCR-+WC         | HÔLĐ                    | AR→AC              | HOLD                  | Z                                              |

|                |     | ι,             | -             | COUNTERS                     | rugun -  | 1                                                      | HOLD         | ZERO-+WC        | HOLD                    | AR→AC              | HOLD                  | z                                              |

| Ĥ              | L   | н              | 5             | LOAD                         | LDAD     | 0, 1, 2, 3                                             | ноцо         | HOLD            | D→AR                    | D⊶AC               | HOLD                  | INPUT                                          |

|                | н   | L              | 6             |                              |          | 0, 2, 3                                                | D-⊷WA        | D→₩C            | HOLD                    | HOLD               | HOLD                  | INPUT                                          |

| н              | •   | L              | 6             | COUNT                        | LUWC     | }                                                      | D→WR         | ZERO→WC         | HOLD                    | HOLD               | HOLD                  | INPUT                                          |

|                | н   |                | 7             | ENABLE                       | ENCT     | 0.13                                                   | ного         | ENABLE<br>COUNT | HOLD                    | ENABLE<br>COUNT    | HOLD                  | z                                              |

| -1             | _   | п              |               | COUNTERS                     |          | 2                                                      | HOLD         | HOLD            | HOLD                    | ENABLE<br>COUNT    | HOLD                  | Z                                              |

|                | א = | Ac             |               | Reg.<br>Reg.<br>Counter      |          | <ul> <li>Word</li> <li>Word C</li> <li>Wata</li> </ul> |              | leg.            | L = L<br>H = F<br>Z = H |                    | ance                  |                                                |

| TABLE | 3-7. | DMA | Register | Instructions |

|-------|------|-----|----------|--------------|

|-------|------|-----|----------|--------------|

Note 1:

Data Bits D<sub>3</sub>-D<sub>7</sub> are high during this instruction.

DWM-00607-00 REV A00

· · · · · · · · ·

|                                                                                                                                                                                                                                                                                                                                |       | 3    | AND BIT | COMM. |     |                  |                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------|-------|-----|------------------|------------------|

| COMMEN                                                                                                                                                                                                                                                                                                                         | ERASE | EDIT | WFM     | WRITE | REV | DESCRIPTION      | COMMAND<br>TYPE* |

| Length of data block pr<br>in DMA registers.                                                                                                                                                                                                                                                                                   | 0     | Х    | 0       | 1     | 0   | Write Data Block | Write            |

| Write filemark on tape.                                                                                                                                                                                                                                                                                                        | 0     | 0    | 1       | 1     | 0   | Write Filemark   | Write            |

|                                                                                                                                                                                                                                                                                                                                | 1     | 0    | 1       | 1     | 0   | Erase 3.75"      | Write            |

| Length of erase function<br>in DMA registers.                                                                                                                                                                                                                                                                                  | 1     | 0    | 0       | 1     | 0   | Erase Programmed | Write            |

| Data block size may be<br>reading the byte count of<br>the DMA controller. To<br>maximum size block to be<br>Count Register should be<br>the maximum number of by<br>ferred plus one. Writing<br>cease when the WCR=WCH+<br>size will be contained a<br>software timer function<br>vided to guard against<br>read blank tapes. | 0     | Х    | 0       | 0     | х   | Read Data Block  | Read             |

|                                                                                                                                                                                                                                                                                                                                | 1     | 1    | 0       | 0     | Х   | Skip Data Block  | Skip             |

|                                                                                                                                                                                                                                                                                                                                | 0     | 0    | 1       | 0     | X   | Skip File        | Skip             |

| These commands do not c                                                                                                                                                                                                                                                                                                        |       | :    |         |       |     | Formatter Reset  | Misc.            |

| to go busy.                                                                                                                                                                                                                                                                                                                    |       |      |         |       |     | Rewind           | Misc.            |

|                                                                                                                                                                                                                                                                                                                                |       |      |         |       |     | Off Line         | Misc.            |

\*Read and Write commands are initiated by pulsing the GO bit (see Table 3-4).

. • •

INTS rogrammed on programmed determined by registers within o control the be read, the Word be programmed with bytes to be transting to Memory will i+1. The total block in the WC. A on should be proattempting to cause formatter

.

. \_

·

.

·

#### PROGRAMMING

#### 3.3 DMA DATA TRANSFER

DMA data transfer is initiated by signal (DRQ) from the control logic indicating that it is ready for more data, or has received data from the drive. If no other DMA controller in the system has control of the bus, a DMA service request is generated by the controller and transmitted to the CPU via one of the prioritized DMA request lines. The DMA controller will then wait until the DMA arbitration signals are received from the CPU indicating bus mastership for the controller.

Upon receiving the DMA arbitration signals, the DMA controller places the DMA address register contents on the system address bus and begins either a READ or WRITE sequence to the mag tape drive, depending upon Bit 1 of the Formatter Command Register.

Two modes of DMA operation are possible with the AM-600/T. The first mode releases the bus to the CPU after every read or write cycle. With this mode of operation, the AM-600/T must re-acquire control of the bus as each byte of data is ready for transmission and is the recommended mode for magnetic tape drives.

The second mode of operation retains control of the bus until the entire command has been completed. Therefore, if a large block of data were to be read from memory and stored on the tape, all the data would be transferred without the CPU regaining control of the bus. This mode should only be used when the data transfer speed is high enough such that re-acquiring the bus in between data byte transfers results in insufficient data transfer rates. This mode of operation is selected by Bit 1 of the Internal Control Register. See Table 3-6.

· · ·

.

## 3.4 INTERRUPT OPERATION

Interrupt operation is enabled by Bit 4 of the Internal Control Register. If enabled, an interrupt will be generated after completion of a READ or WRITE command when the tape begins to decelerate. The interrupt flip-flop will be reset by a GO command to the formatter. CHAPTER 4

#### FUNCTIONAL THEORY OF OPERATIONS

#### 4.1 INTRODUCTION

The AM-600/T Magnetic Tape Transport Formatter Interface circuit board contains the integrated circuit elements necessary for the data processing functions described in Chapters 1, 2, and 3 of this manual. This Chapter describes the functional theory of operation of the circuit board and also provides information for each of the integrated circuit elements.

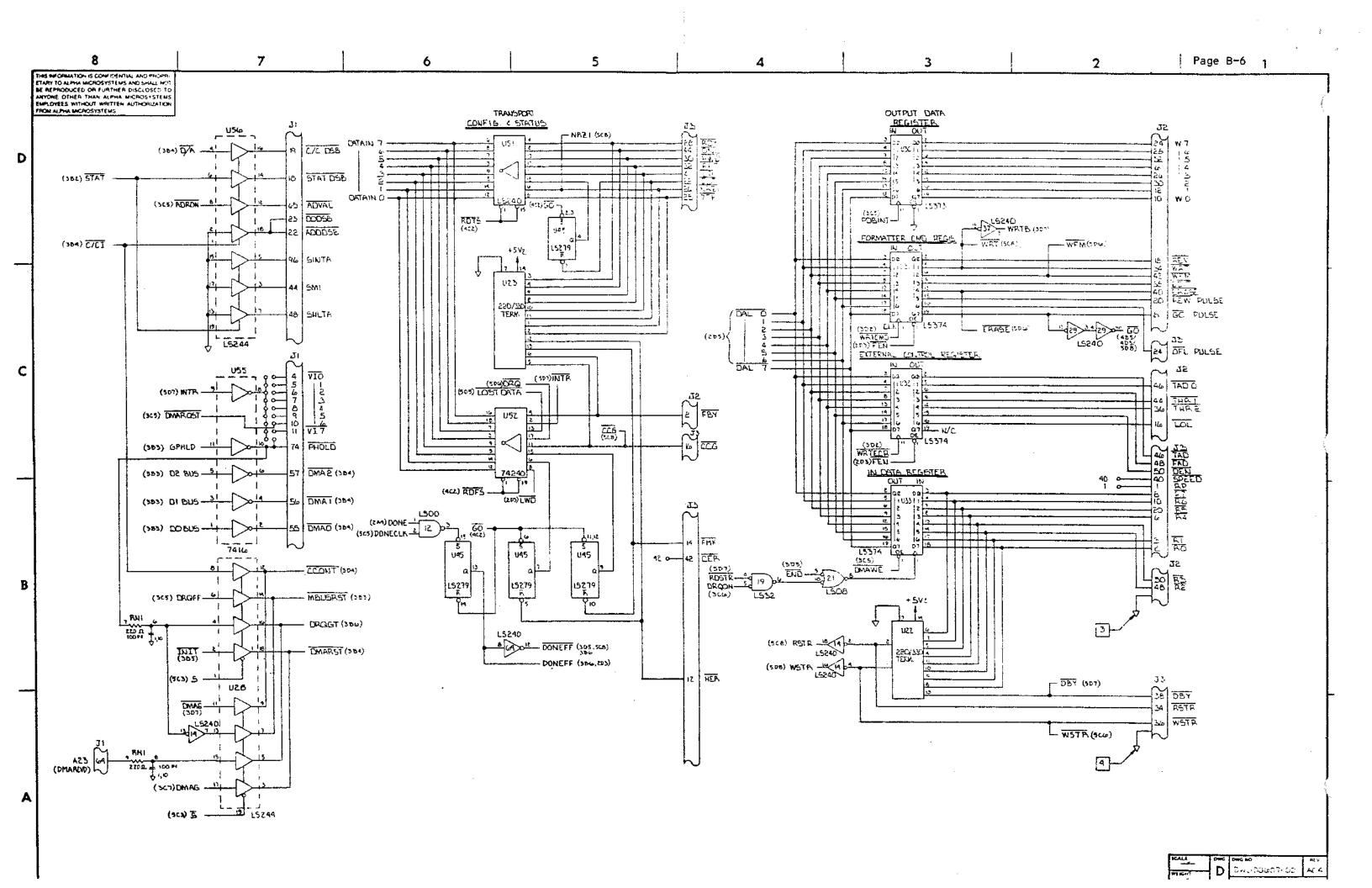

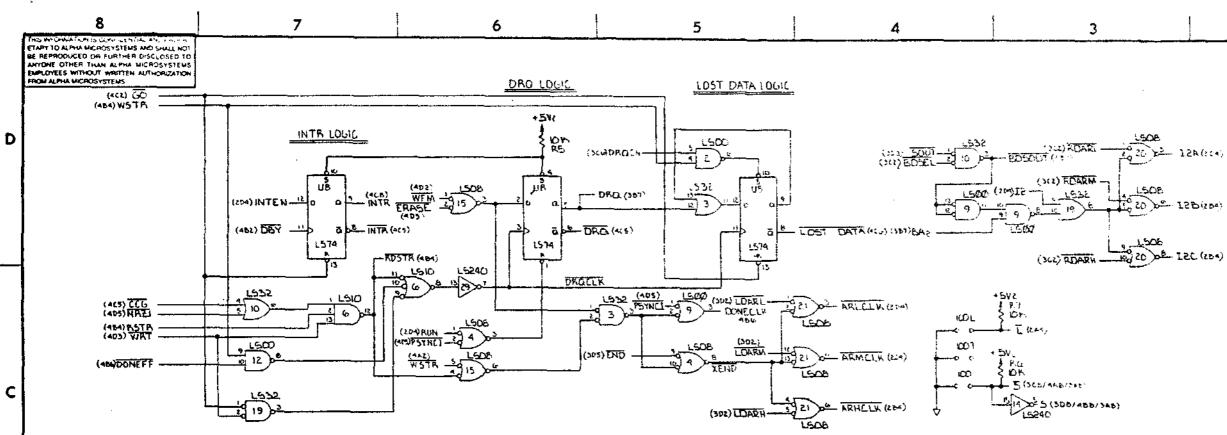

### 4.2 CIRCUIT BOARD OPERATION

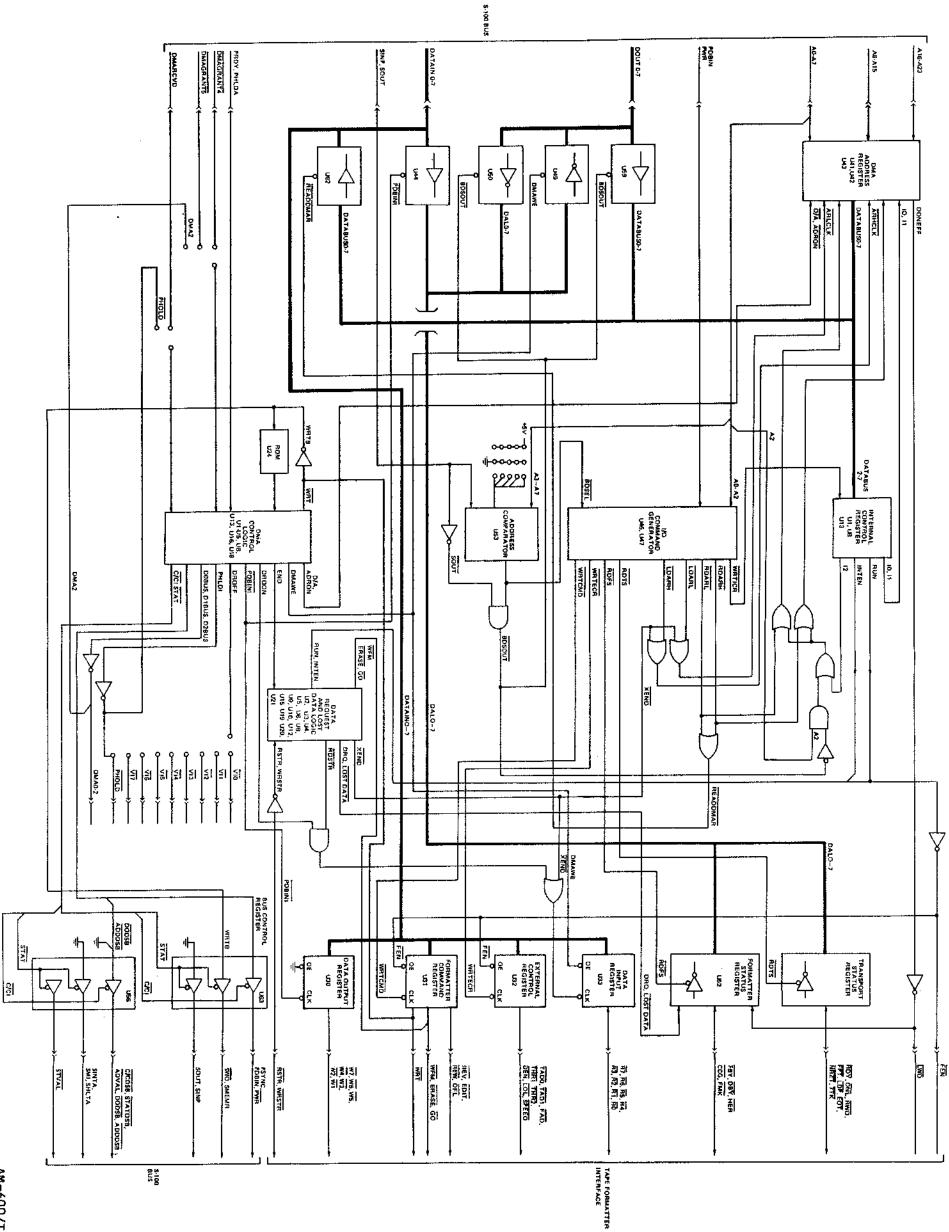

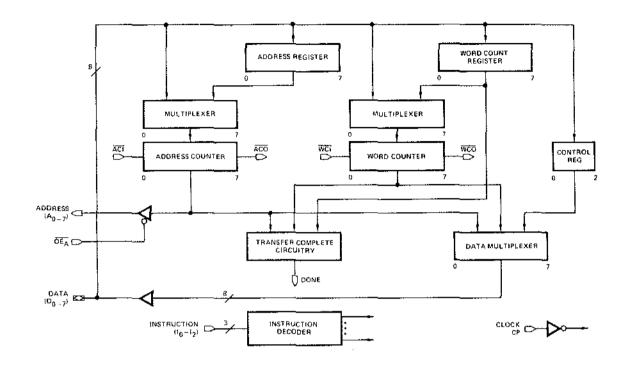

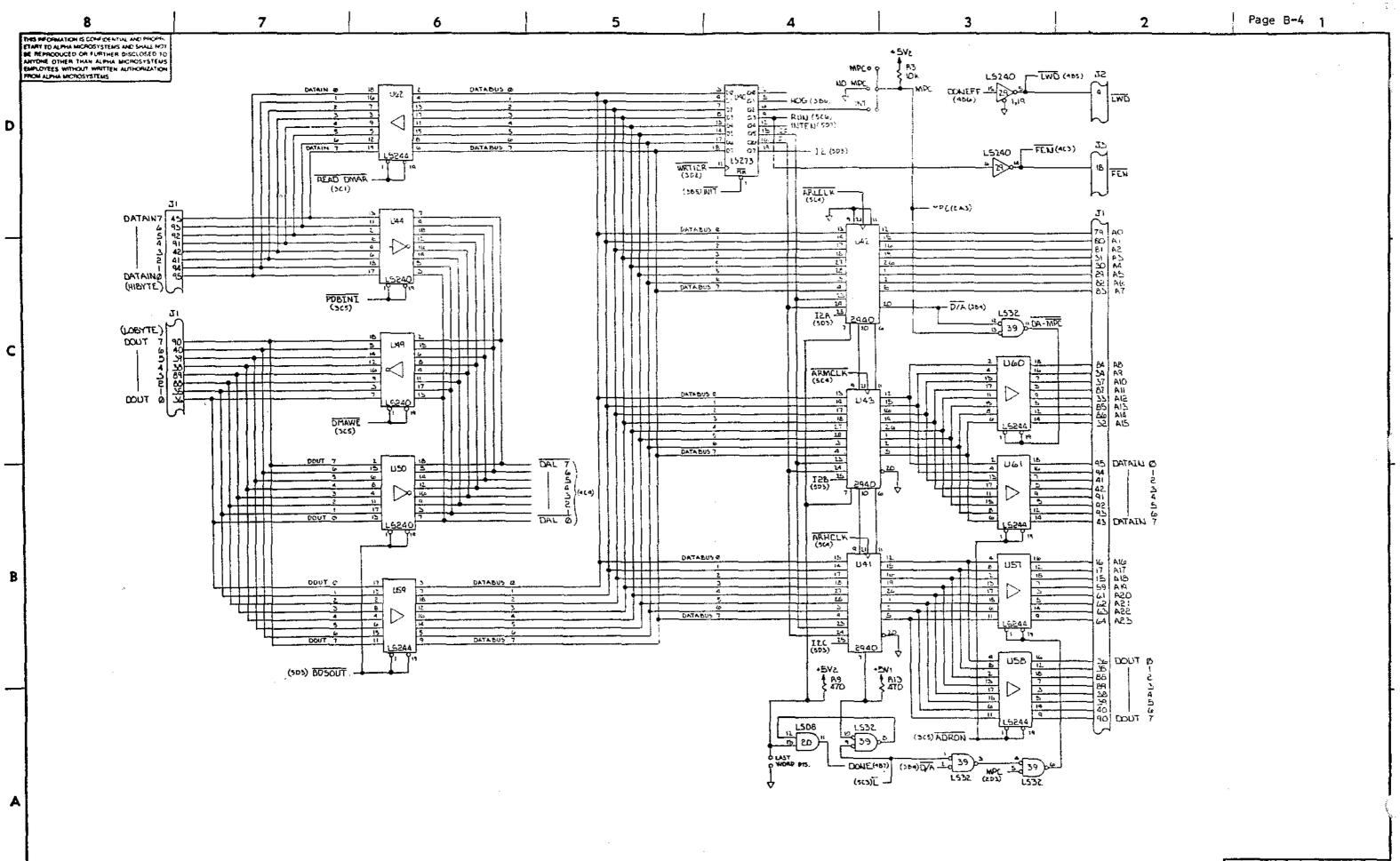

This circuit board provides control and interface capability between the Alpha Micro S-100 bus and an industry standard 1/2" Magnetic Tape Transport Formatter. The functional block diagram of the circuit board is shown in Figure 4-1, and the circuit board schematic is contained in Appendix B of this manual. Table 4-1 contains a list of the signals used in this circuit board with descriptions of their functions. Reference Table 2-2 for a list of bus interface signals. For formatter interface signals see Table 4-2. DWM-00607-00 REV A00

anting The

# FIGURE 4-1. AM-600/T Functional Block Diagram

Page 4-3

. • "\*\*\*\* · · · ·

. . .

.

•

÷

## TABLE 4-1. AM-600/T Signal List (sheet 1 of 9)

| SIGNAL | NAME                                  | FUNCTION                                                                                                                  |

|--------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| ADRON  | Address Register Output<br>Enable     | Places address data from DMA<br>address register onto Data Bus                                                            |

| ARHCLK | Address Register High<br>Byte Clock   | Clock input to the counters and<br>registers in the DMA address<br>registers for the upper eight bits<br>of address data. |

| ARMCLK | Address Register Middle<br>Byte Clock | Clock input to the counters and<br>registers in the DMA address<br>register for the middle eight bits<br>of address data. |

| ARLCLK | Address Register Low<br>Ryte Clock    | Clock input to the counters<br>and registers in the DMA address<br>register for the lower eight bits<br>of address data.  |

| BDSEL  | Board Select                          | Output of board address comparator.<br>Asserted when Alpha Micro I/O<br>address matches I/O address wired<br>in jumpers.  |

| BDSOUT | Board Select Output<br>Cycle          | Asserted when AM-600/T is addressed<br>and an output cycle is selected<br>(BDSEL SOUT).                                   |

\$

## TABLE 4-1. AM-600/T Signal List (sheet 2 of 9)

| SIGNAL       | NAME                   | FUNCTION                                                                                                                                                                 |

|--------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| во2 .        | Buffered Phase 2 CLock | Buffered phase 2 clock from phase 2<br>on Alpha Micro Bus.                                                                                                               |

| CCG          | Check Character Gate   | Input from formatter set true when<br>the read information being transmit-<br>ted to the AM-600/T is a CRC character<br>or a longitudinal redundancy check<br>character. |

| C/CI<br>C/CI | Controller Command     | Disables the processor address and<br>data bus drivers while enabling the<br>DMA controller command drivers. Sets<br>D/A at O2 leading edge.                             |

| D/A<br>D/A   | DMA Address Enable     | Places address data from DMA address<br>register onto Data Bus (optional for<br>8-bit format).                                                                           |

| DBY          | Data Busy              | Input from formatter when the trans-<br>port tape is up to speed.                                                                                                        |

| DAWE         | DMA Write Enable       | Generated during a write cycle to<br>gate data onto the data bus and en-<br>sure its validity before, during, and<br>after PWR.                                          |

| DONE         | Done                   | Asserted when the DMA register reaches its terminal count.                                                                                                               |

# TABLE 4-1. AM-600/T Signal List (sheet 3 of 9)

| SIGNAL           | NAME                | FUNCTION                                                                             |

|------------------|---------------------|--------------------------------------------------------------------------------------|

| DONECLK          | Done Clock          | Clock input to combine with DONE to set DONEFF.                                      |

| DONEFF<br>DONEFF | Done Signal         | Signifies the completion of the DMA<br>data transfer.                                |

| DRQ<br>DRQ       | Data Request        | Initiates a DMA cycle indicating that the controller requires DMA service.           |

| DRQCLK           | Data Request Clock  | Clocks the Data Request flip-flop.                                                   |

| DRQFF<br>DRQFF   | Data Request Signal | Generated from DRQ to directly generate PHOLD.                                       |

| DRQON            | Data Request On     | Generated from DRQ to enable tape read logic.                                        |

| END<br>END       | End                 | Generated by the sequencer to ter-<br>minate the entire DMA cycle.                   |

| ERASE            | Erase               | Output to formatter. When asserted<br>with WRT, executes a write command<br>no data. |

.

ć

# TABLE 4-1. AM-600/T Signal List (sheet 4 of 9)

| SIGNAL        | NAME                              | FUNCTION                                                                                                                              |

|---------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| FEN           | Formatter Enable                  | Output to tape transport generated<br>from RUN. Enables formatters. When<br>false, causes formatters to revert to<br>quiescent state. |

| GO            | Initiate Command                  | Output to formatter to initiate any command specified by the command lines.                                                           |

| INIT          | Initialize                        | Circuit board reset signal generated<br>by PRESET from Alpha Micro bus.                                                               |

| INTEN         | Interrupt Enable                  | Enables the INTR flip-flop.                                                                                                           |

| INTR          | Interrupt                         | Provides jumper output to vectored interrupt lines VIO-VI7 (not used).                                                                |

| 10, 11,<br>12 | Instruction Codes                 | Instruction code inputs to the DMA<br>Address Register.                                                                               |

| 1.            | AM-100/L                          | Activated when the AM-100/L CPU is selected.                                                                                          |

| LDARH         | Load DMA Register<br>High Byte    | Generates a clock to load data bits<br>16-24 into the high byte of DMA<br>Address Register.                                           |

| LDARM         | Load DMA Register<br>Middle Byte. | Generates a clock to load data bits 8-<br>15 into the middle byte of DMA Address<br>Register.                                         |

÷ , v

ł,

# TABLE 4-1. AM-600/T Signal List (sheet 5 of 9)

| SIGNAL               | NAME                           | FUNCTION                                                                                                                                                  |

|----------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| LDARL                | Load DMA Register<br>Low Byte. | Generates a clock to load data bits O <del>-</del><br>7 into the low byte DMA address<br>generator.                                                       |

| LOSTDATA<br>LOSTDATA | Lost Data Error                | Set when a Read data request is gen—<br>erated with DRQ still set or if a<br>a Write data request is generated with<br>prior DMA cycle still in progress. |

| LWD                  | Last Word of Data              | Output to Tape Transport generated from DONEFF.                                                                                                           |

| MBUS                 | My Bus                         | Enables the AM-600/T to take control of system busses.                                                                                                    |

| MPC                  | Memory Partition<br>Controller | Indicates presence of a Memory<br>Partition Controller                                                                                                    |

| NRZI                 | NRZI                           | Input from formatter indicating trans-<br>port configuration.                                                                                             |

| 0802                 | On-board two-phase<br>clock    | Select for the two phase on-board clock                                                                                                                   |

| PDBINI<br>PDBINI     | Data Bus In                    | Used to generate PDBIN output to Alpha Micro<br>Bus when gated by the Bus Control<br>Register.                                                            |

i (

TABLE 4-1. AM-600/T Signal List (sheet 6 of 9)

| SIGNAL           | NAME                                    | FUNCTION                                                                                                                  |

|------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| PSYNCI<br>PSYNCI | Processor Sync                          | Used to generate PSYNC output to Alpha Micro<br>Bus when gated by the Bus Control<br>Register.                            |

| PWRI             | Write Strobe                            | Used to generate PWR on Alpha Micro Bus when<br>gated by WRDIS and Bus Control<br>Register.                               |

| RDARH            | Read DMA Address<br>Register High Byte. | Provides instruction input (I2) to upper byte DMA address register.                                                       |

| RDARL            | Read DMA Address<br>Register Low Byte.  | Provides instruction input (I2) to<br>lower byte DMA address register.                                                    |

| RDFS             | Read Formatter Status                   | Gates the contents of the Formatter<br>Status Register onto the DATINO-7 bus.                                             |

| RDSTR            | Tape Read Strobe                        | Enabled by DRQON to clock tape read                                                                                       |

| RDTS             | Read Transport Status                   | Gates the contents of the Transport<br>Status Register onto the DATINO-7 bus.                                             |

| RDYCLK           | Ready Clock                             | Clock signal jumpered to BO2 for stan-<br>dard S-100 bus or BO2 for Alpha<br>Micro bus.                                   |

| RDARL            | Read Address Register<br>Low Byte       | Read input to the counters and reg-<br>isters in the DMA address register<br>for the upper eight bits of address<br>data. |

Page 4-11

|          | · · · · · · · · · · · · · · · · · · ·  |                                                                                                                                                                                    |

|----------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SIGNAL   | NAME                                   | FUNCTION                                                                                                                                                                           |

| RDARM    | Read Address Register<br>Middle Byte 3 | Read input to the counters and reg-<br>isters in the DMA address register<br>for the middle eight bits of address<br>data.                                                         |