#### TAKING THE MYSTERY OUT OF LOGIC SYNTHESIS

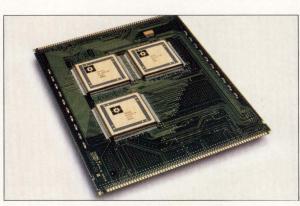

# With the right ASIC par

Why shop around at different ASIC suppliers when you can get it all from Fujitsu.

But we'd rather you didn't think of us as just another ASIC supplier. Because, frankly, we don't want to be your ASIC supplier. We want to be your ASIC partner. The only one you'll ever need.

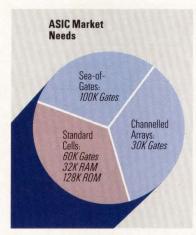

As the industry's most experienced volume producer of ASIC devices, we can provide you with the broadest options in ASIC.

Like standard and compiled cells. Over 70 types of channeled and channeless arrays. And 60 packages. All available now. All from one source.

You're also assured of the most advanced process and manufacturing technologies in the industry. Such as high-speed, silicon-gate 3-layer metal CMOS. Advanced ECL featuring 0.5 and 1.0 micron, 3-layer metal process. And a robust LSTTL bipolar process and design.

We've even taken advantage of our expertise in bipolar and CMOS to develop BiCMOS. A process marriage featuring high-performance ECL and highdensity CMOS.

All of which means you can always count on getting the optimum solution to your VLSI needs. Whether you expand to larger gate counts or migrate from arrays to standard cells.

Take packaging, for example. You can choose from PGAs or DIPs. Ceramic or plastic. Through-hole and surface-mount. PLCCs and flatpacks. Even PGAs and flatpacks with heatsinks. All designed, built and backed by Fujitsu.

As your ASIC partner, we expand your design team, providing you with coast-to-coast technical resource centers, fully equipped with easy-to-use design tools.

You also get ASIC sales and marketing support to help you smooth out all the administrative wrinkles. Plus local training and technical support. And twenty-four hour design facilities, so you can work whenever inspiration strikes.

It all adds up to just one name. Fujitsu. The one ASIC partner you need. The only one you'll ever need. Which, after all, is everything an ASIC partner should be.

#### FUJITSU MICROELECTRONICS, INC.

#### Everything an ASIC partner should be.

Fujitsu Microelectronics, Inc. • 3545 North First Street, San Jose, CA 95134-1804 • (408) 922-9000.

**CIRCLE NUMBER 1**

# tner, you only need one.

## Contents

#### RTICLES

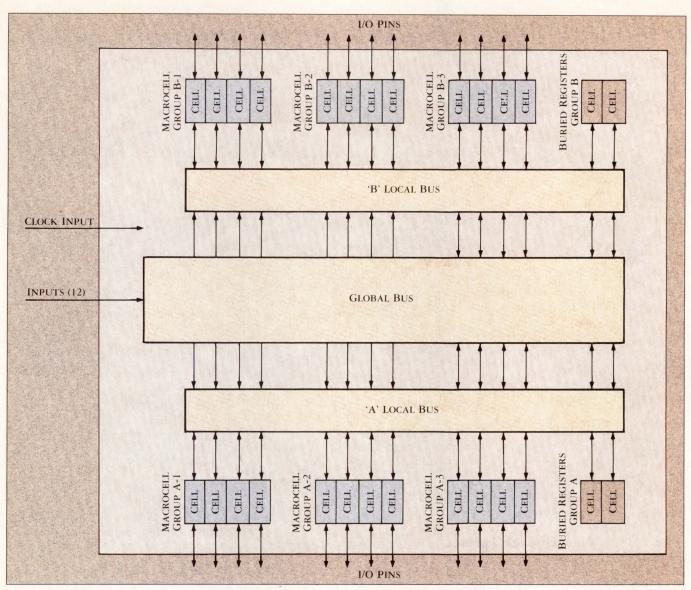

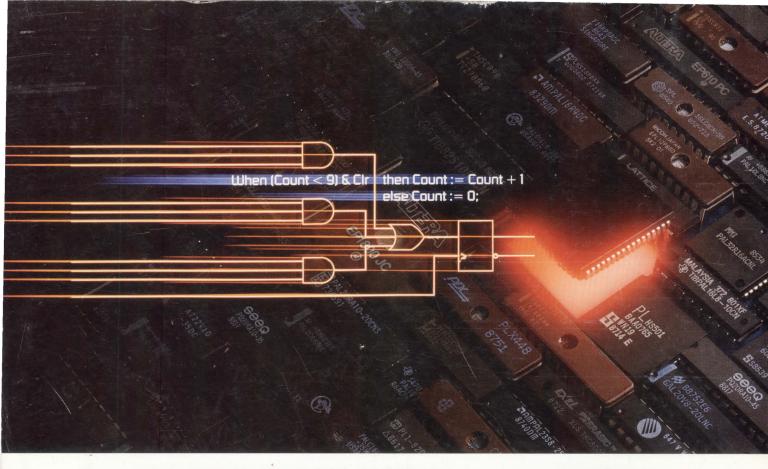

Logic synthesis, the latest design automation buzzword, has different meanings to different CAE/CAD suppliers

#### T OOLS

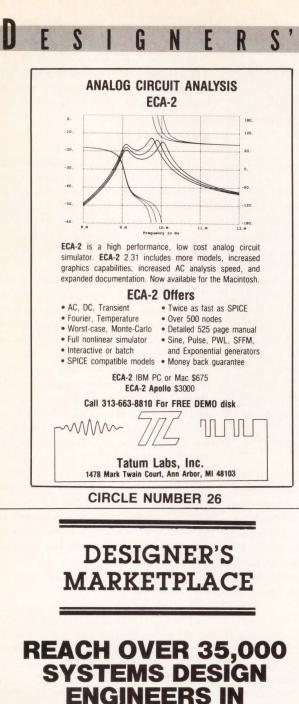

#### **18** WHAT IS LOGIC SYNTHESIS?

DAVID SMITH, VLSI Systems Design

The latest tool available to designers of logic circuits is logic synthesis, which unfortunately has been hidden in a cloud of confusion. This article attempts to shed some light on the topic.

#### T OOLS

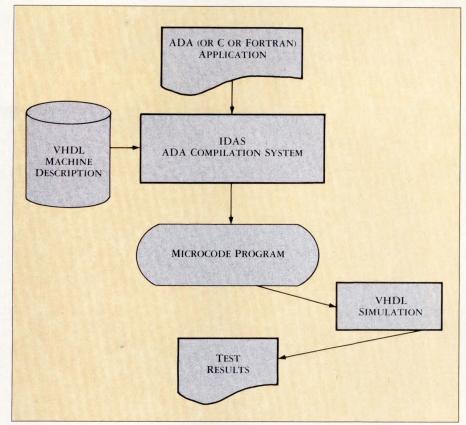

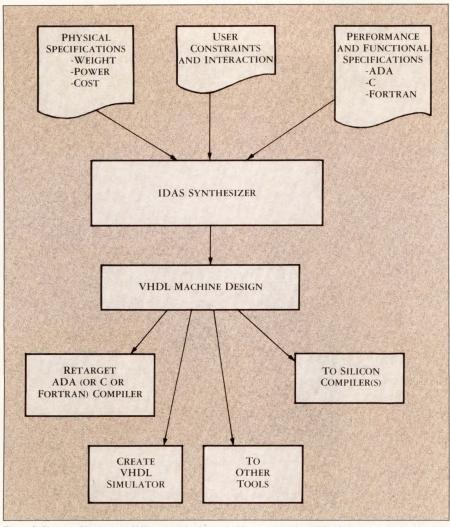

#### **30** SYNTHESIZING ADA'S IDEAL MACHINE MATE

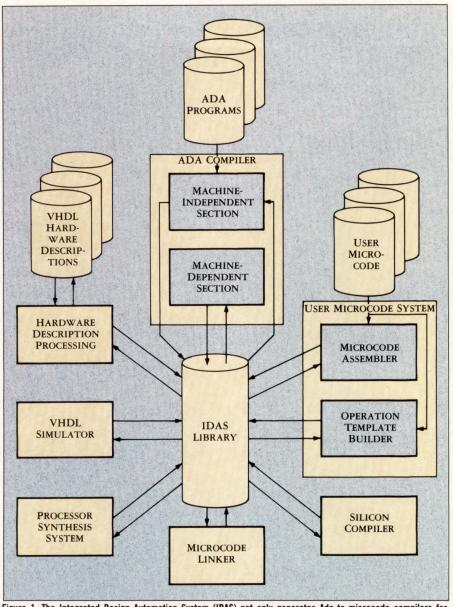

**DEBORAH W. RUNNER AND ERWIN H. WARSHAWSKY**, *JRS Research Laboratories, Inc.* Among its many attributes, this new development environment boosts design efficiency by automatically designing a machine to match a given ADA program. The machine is described in VHDL.

#### TOOLS

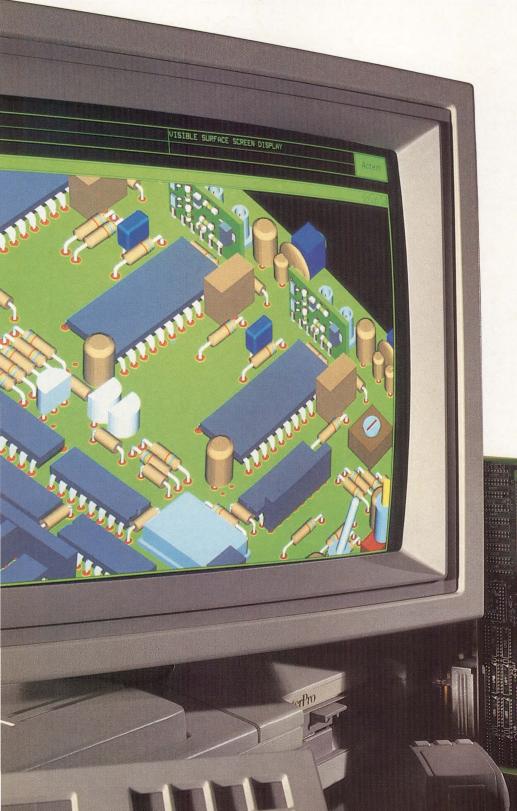

#### 42 A SURVEY OF PCB-CAD VENDORS

VLSI SYSTEMS DESIGN STAFF

This annual survey of printed circuit board design systems vendors has shown the effects of the continuing consolidation in the design automation industry.

#### C HIPS

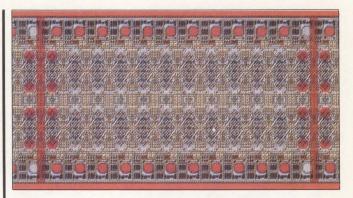

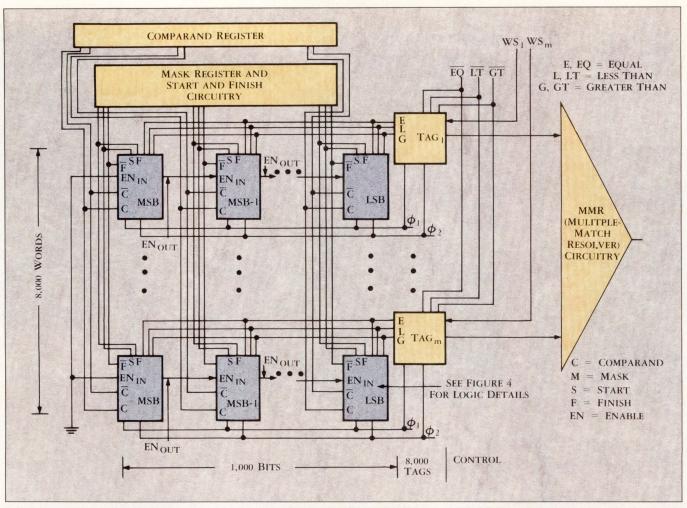

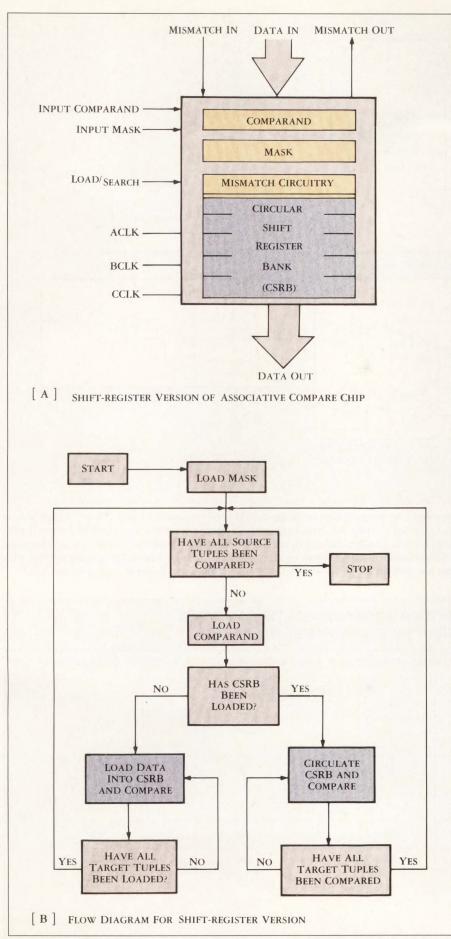

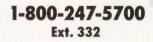

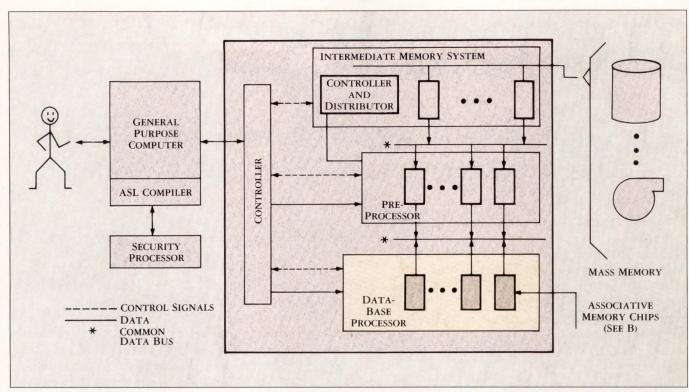

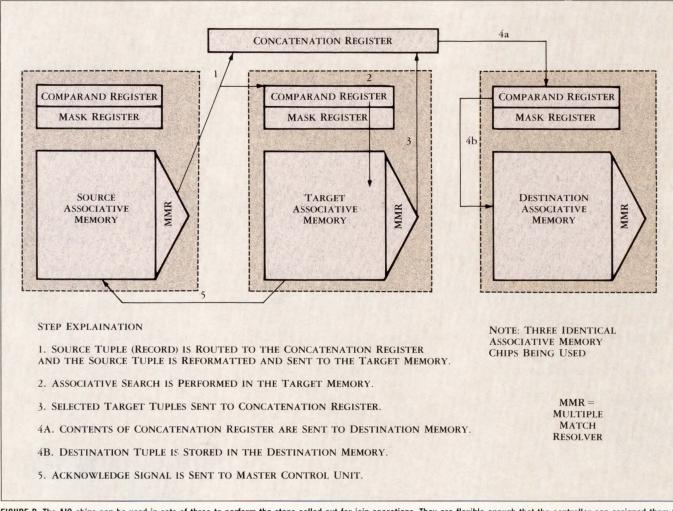

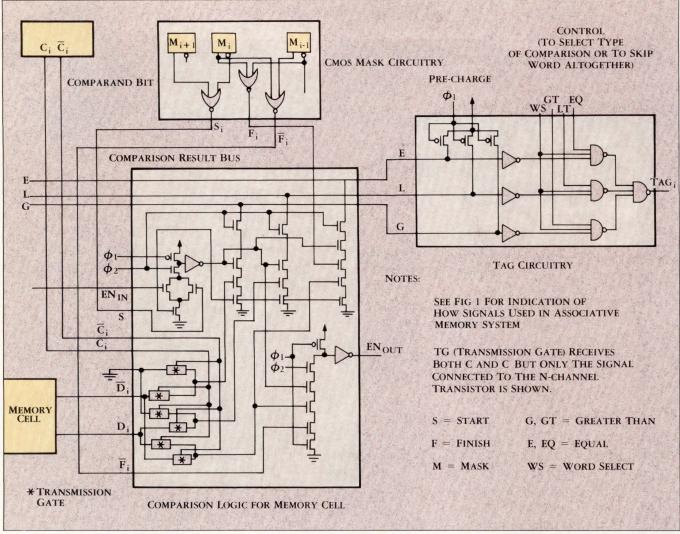

#### **46** A VLSI JOIN MODULE

C.R. PETRIE AND A. R. HURSON, Pennsylvania State University

Searching databases calls for massive parallelism. This join module is the beginning of a VLSI implementation of a memory that uses this parallelism to provide the intelligence necessary to internally perform its own associative search.

#### METHODS

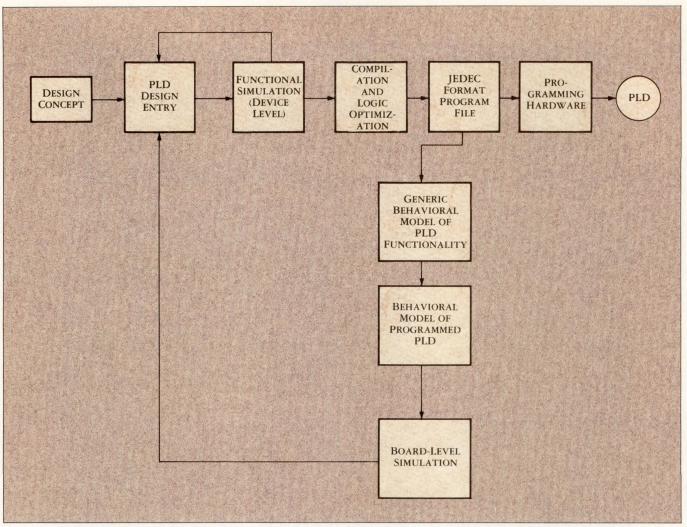

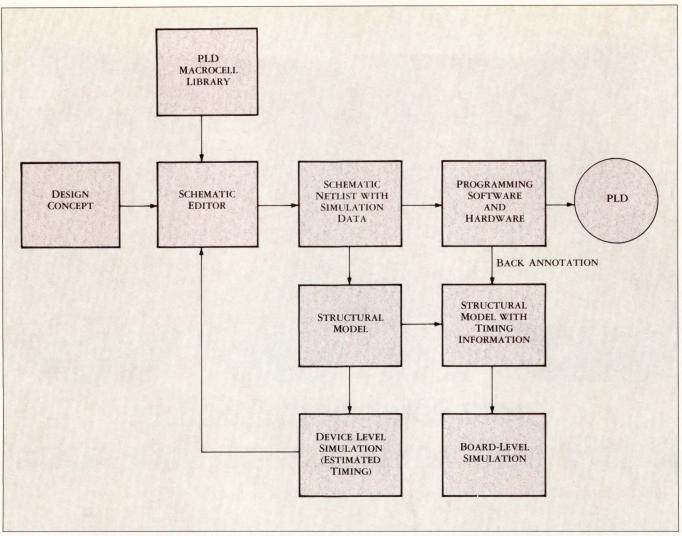

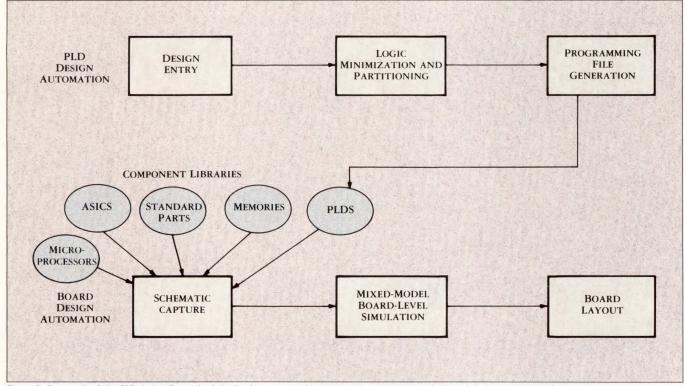

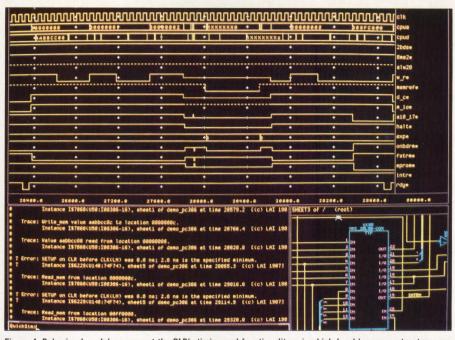

#### 62 PLDS In BOARD-LEVEL SIMULATION

#### KENT MOFFAT, Mentor Graphics Corp.

The final performance of a PLD can best be predicted by simulating the programmed PLD in the system. This board-level simulation can be facilitated by properly modeling the devices.

#### METHODS

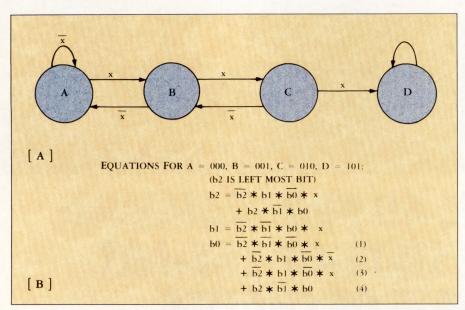

#### **70** SQUEEZING STATE MACHINES INTO PLDS

#### DAVID SHARP AND GEORGE BARBEHENN, Hewlett-Packard Co.

There a number of rules that must be followed in order to optimize the minimization of a state machine so that it can fit into an appropriate PLD chip. The authors also describe a number of practical techniques to aid this process.

The new IDAS design environment matches hardware to software

30

#### 46

VLSI technology can help solve some of the growing database problems

#### 6 FROM THE EDITOR Analog Revives in a World of Digital Electronics

#### 8 CALENDAR

#### **10** BIT STREAM

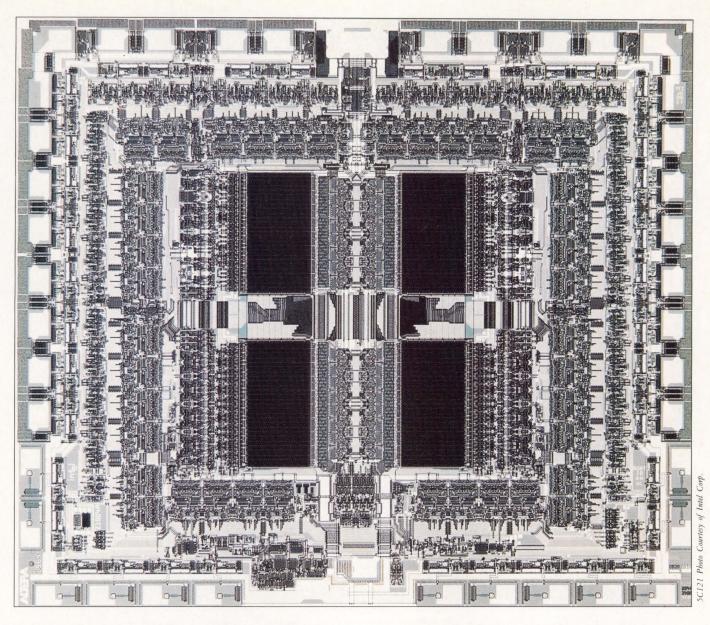

RISC Microprocessor Sales to Top \$500 Million

SPARCs Fly

Cut Your Analog/Digital Arrays to Size

Tektronix Testers Toil at 200 MHz GaAs for the Masses

Communications Controller Fits ISDN

TriQuint Toggles 4,200 GaAs Gates at 100 GHz

Dataprobe Creator Builds 1.2-GHz Test System

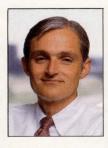

**14 PEOPLE**

Teradyne's Joe Lassiter Makes Up His Mind Fast

#### **16** INDUSTRY INSIGHTS

Does Logic Synthesis Work For Multi-Chip, High-Gate-Count Systems?

#### **80** PRODUCT SHOWCASE

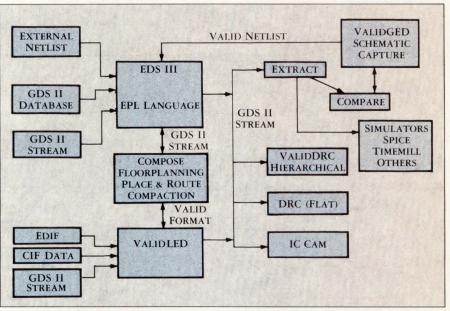

Valid Pulls Itself Together

88 AD INDEX

COVER PHOTOGRAPH BY WILLIAM DUKE

#### A CMP Publication

EDITORIAL DIRECTOR Robert W. Henkel **EDITOR-IN-CHIEF** Roland C. Wittenberg MANAGING EDITOR Mike Robinson SENIOR EDITOR Bob Cushman SOLID STATE EDITOR Roderic Beresford WESTERN REGIONAL EDITOR David Smith DIRECTORIES EDITOR Michelle A. Losquadro **TECHNICAL ADVISERS** John A. Darringer Jeffrey T. Deutsch Edward J. McCluskey Alan F. Podell Daniel G. Schweikert

Susan L. Taylor EDITORIAL PRODUCTION Patricia L. Gaynor, Sr. Production Editor Deborah Porretto, Ass't Production Editor

EDITORIAL ART Sharon Anderson, Art Director Marie D'Ippolito, Design Director

MANUFACTURING Marie Myers, Production Manager James Pizzo, Production Supervisor Jane Mahoney, Asst. Production Supervisor Vance Hicks, Coordinator

#### PUBLISHER Norm Rosen

VLSI SYSTEMS DESIGN (ISSN 0279-2834) is published monthly with an extra issue in September by CMP Publications, Inc., 600 Community Drive, Manhaset, NY 11030. (516) 562-5000. VLSI SYSTEMS DESIGN is free to qualified subscribers. One year subscriptions to others; US and Canada \$60. Mexico, Europe, Central and South America: \$120.00. Asia, Australia, and Africa: \$135.00. Second-class postage paid at Manhaset, NY and additional mailing offices. POSTMASTER: Send address changes to VLSI SYSTEMS DESIGN. Box No. 2060. Manhaset, NY 11030. Copyright 1988, CMP Publications, Inc. All rights reserved.

#### **CMP ELECTRONICS GROUP**

Kenneth D. Cron Vice President/Group Publisher Electronic Buyers' News Electronic Engineering Times VLSI Systems Design

CMP PUBLICATIONS, INC. 600 Community Drive Manhasset, New York 11030 (516) 562-5000

Malifiasset, Jeew Fork 11050

(516) 562-5000

*Publisher of:* Electronic Buyers' News, Electronic Engineering Times, VLSI Systems Design,

Computer Systems News, Computer Reseller News, VARBUSINESS,

UNIX Today<sup>1</sup>, Information WEEK, CommunicationsWeek,

CommunicationsWeek International, Business Travel News,

Tour & Travel News, Long Island Monthly, HealthWeek

Michael S. Leeds, President Pearl Turner, Vice President/Treasurer Daniel H. Leeds, Vice President

Lilo J. Leeds, Gerard G. Leeds Co-Chairpersons of the Board

#### TI SYNDIAS DOG UTINOZZIOS UTINOZZIO UTINOZZIOS UTINOZZIO UTINOZZIO

10

**New VLSI** chip testers

support 512 pins with

200 MHz data rates

#### 18

Silicon compilation, logic optimization and logic synthesis have many features based on common technological roots

# Daisy's standard now runs on an

#### Introducing the Advansys Series<sup>™</sup> of high performance CAE workstations.

Now the electronic design environment you've dreamed of is here.

Because the most advanced design tools in the world now run on the world's most advanced standard platform.

The Sun 386i™

We call it the Advansys Series.

And it encompasses some of the most powerful design tools ever developed. Plus a variety of affordably priced workstations. Including the 20 MHz and 25 MHz Sun 386*i*, as well as Daisy's own LOGICIAN\* 386 and the newly enhanced Personal LOGICIAN<sup>™</sup> 386. All share a standard system level environment, featuring UNIX,<sup>™</sup> advanced X Window System graphics, Sun's NFS<sup>™</sup> distributed file system and standard TCP/IP communications.

Now you can get the workstation performance and flexibility you've demanded for your desktop. Including up to 5 MIPS of processing power, high resolution graphics display and an integrated UNIX/ DOS environment.

Even better, all these advanced workstations run Daisy's fieldproven Advansys software packages. Eight turnkey tool sets that meet all the demands of real world electronic design. Everything from design entry to digital and analog simulation, IC and PCB layout, fault simulation and test tools.

But with Advansys, your capabilities don't stop at your desktop. Because Daisy's unique network computing concept lets you create an affordable team design environment incorporating a wide range of powerful network resources.

Like Daisy's MegaLOGICIAN\*– the most widely used simulation accelerator ever created. Or the

brand new GigaLOGICIAN<sup>™</sup> with up to 30 times greater performance.

For complex system simulations, there's Daisy's PMX,<sup>™</sup> the most popular physical modeling system in use today.

You can also link with network servers like the Sun-4<sup>™</sup> based XL Server for analog simulation or PCB routing. And Daisy lets you access all this power simply by opening a window on your Advansys desktop workstation. Eliminating file transfers and other time consuming bottlenecks.

To find out more about the new Advansys Series, call Daisy today at 1 (800) 556-1234, ext. 32. In California: 1 (800) 441-2345, ext. 32.

We're raising the standard of excellence for electronic design.

*European Headquarters*: Paris, France (1) 45 37 00 12. *Regional Offices*: England (256) 464061; West Germany (89) 92-69060; Italy (39) 637251.

# of excellence excellent standard.

Lorus

© 1988, Daisy Systems Corporation. Sun386i, NFS and Sun-4 are trademarks of Sun Microsystems, Inc. Ethernet is a trademark of Xerox Corporation. UNIX is a trademark of Bell Laboratories.

dates Advansys

Advansvs

#### ROM THE EDITOR

It seems that the more things change, the more they remain the same

#### Analog Revives in a World of Digital Electronics

number of events during the past few years started me thinking about the fortunes of analog engineers and the changing environment that they live in. These included the growth of mixed-signal analog/digital systems, high-speed digital circuits that obsoleted simple logic simulators as far as timing and glitch behavior was concerned, and the increasing number of reader requests for more analog articles.

However, before continuing, I must confess that I started out in the analog world, which might explain my bias. Analog has always served industry and humanity well—from radio and TV to auto-pilots and industrial controls. But when digital electronics became a practical technology, many people started touting digital as the only way to go—anything you could do in analog, you could do better in digital. Well, not quite. The first digital replacements for analog systems were extremely costly, bulky, and slow compared to their analog cousins. However, the foresight of the digital proponents was eventually recognized when reliable, faster, denser, and cheaper digital chips became available. Digital was the winner and the digital engineer was king.

But the tide has turned again. As improvements in VLSI and ASIC technology accelerated, more and more of complex systems were put into the same box, or on the same board, or even on the same chip. It became evident that it was inefficient and costly to keep the analog components and systems separate. So they moved in with the digital domain. The situation was compounded by digital's move into traditionally analog worlds. Added to that was the fact that high-speed digital circuits were beginning to look like RF/microwave circuits, where careful consideration of transmission line effects, stray impedances, matching terminations, and stability were of crucial importance to a successful design.

Suddenly, there seemed to be a dearth of analog engineers, particularly RF/microwave specialists, who thrived on these kinds of problems. This has raised the visibility-level of the analog engineer, who may never be king again, but perhaps a prince consort to the world of digital electronics.

C.U

ROLAND WITTENBERG EDITOR-IN-CHIEF

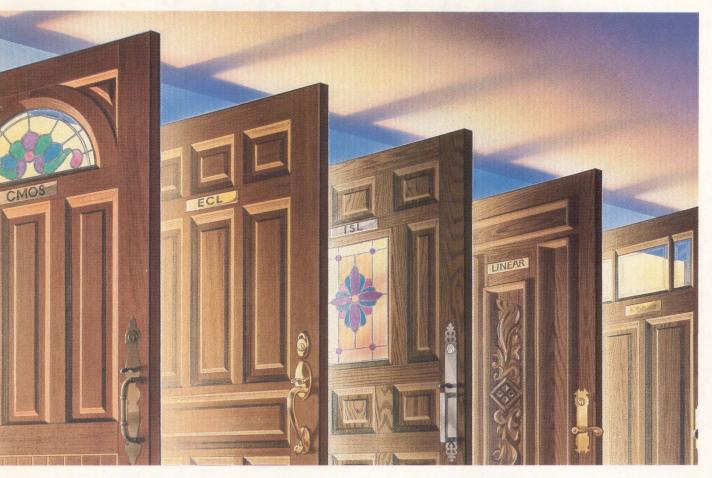

### Access to the Right Technology

Whatever your application, Raytheon can open the door to the appropriate ASIC technology. With over 14 years' experience in semicustom design, Raytheon offers you many choices— CMOS, low power ECL and digital bipolar, as well as linear arrays.

CMOS arrays: Raytheon's lowpower CMOS arrays to 20,440 gates have a 1.0 μm effective channel length and rad hard capability. Both our VHSIC-approved and standard families have the lowest power consumption in the industry. The 2 μm RL7000 array is a second source for LSI's LL7000 series. Standard cell solutions are also available. □ Low-power ECL arrays: The ECL products available from Raytheon have densities comparable to 1.5 μm CMOS arrays and I/Os compatible with ECL, TTL (10K or 100K), and CMOS. These ECL arrays also deliver the industry's lowest power dissipation per gate. Their superior speed/power performance— <0.1pJ—provides the ASIC designer with state-of-the-art semicustom capabilities.

□ Digital bipolar arrays: Our many years of experience in ISL array design and production give Raytheon a solid foundation for expanding ASIC technology.

#### **Raytheon offers you choices**

□ Linear arrays: Raytheon's bipolar macrocell arrays with 8, 12 or 15 gain blocks and FET input arrays with 4 or 12 gain blocks utilize precision thin-film resistors. They can be configured into a variety of analog functions, including voltage references, switches, comparators, op amps, and VFCs.

Let Raytheon open the door to a world of ASIC choices, with our proven track record in multiple ASIC technologies.

Raytheon Company Semiconductor Division 350 Ellis Street Mountain View, CA 94039-7016 (415) 966-7716

# C alendar

design techniques, high-level synthesis, timing simulation, channel routing, device simulation and modeling, performance issues for VLSI, circuit verification, row-based CMOS cell generation, automatic test pattern generation, and analog layout. For additional information, contact MP Associates Inc., 7490 Clubhouse Rd., Suite 102, Boulder, Colo. 80301. (303) 530-4562.

#### 1988 GOVERNMENT Microcircuit Applications Conference

November 8-10 Riviera Hotel Las Vegas, Nev.

MAC '88 is a govern-G ment-sponsored conference established primarily to review developments in microelectronics applications for government systems. This year's conference, with the theme, "International Competitiveness: Its Impact on Government Electronics," will feature technical sessions on such topics as radiation effects in electronics, signal processing, VHSIC technology and applications, MIMIC, reliability, digital systems applications, packaging, discontinued parts, systems, and testability. For more information, contact C. Edward Holland Jr., GO-MAC-88 Technical Program Chairman, Semiconductor Research Corp., 4501 Alexander Dr., P.O. Box 12053, Research Triangle Park, N.C. 27709. (919) 541-9400.

#### CUSTOM INTEGRATED CIRCUITS CONFERENCE

May 15–18, 1989 San Diego, Calif.

C ICC '89 is sponsored by the IEEE's Electron Devices Society, and Solid State Circuits Council, and co-sponsored by the IEEE Rochester Section. Its goal is to bring together designers and manufacturers of circuits and systems, and users of custom ICs to discuss new developments and future trends in custom integrated circuits. Papers are invited on such topics as digital signal and data processing applications, fabrication technology, physical design techniques, simulation and modeling, custom and semi-custom circuits, CAD systems and methodologies, custom interfaces and packaging, testing and reliability, and analog circuit techniques. By November 11, 1988, authors should submit 25 copies of a review package which includes a 1-page summary, a 35-word abstract clearly describing the work, and a maximum of 2 pages of figures, drawings and references. Submit review packages to Mrs. Roberta Kaspar, Technical Program Coordinator, CICC '89, 20 Ledgewood Dr., Rochester, N.Y. 14615. (716) 865-7164.

#### 26th Design Automation Conference

June 25–29, 1989 Las Vegas Convention Center Las Vegas, Nev.

AC '89, which is devoted D solely to the field of design automation, will offer tutorials, panel discussions, and technical presentations. Areas of interest include electrical and discrete simulation. timing verification, test validation and testability analysis, floorplanning and placement, global and detailed routing, physical module generation, symbolic layout and compaction, logic synthesis and optimization, behavioral and hardware description languages, design systems and databases, and computer aids for manufacturing. Interested authors should submit, by November 7, 1988, one cover page and 8 copies of a complete manuscript to MP Associates Inc., Att: A. Richard Newton, Program Chairman 26th DAC. 7490 Clubhouse Rd., Suite 102, Boulder, Colo. 80301. For additional information call (303) 530-4333.

#### 1988 WORKSHOP ON VLSI Signal Processing

November 2–4 Monterey Plaza Hotel Monterey, Calif.

Providing a forum for the discussion of new theoretical, and applied developments in signal processing for very large scale ICs is the objective of this workshop. Topics will be discussed in such areas as analog/digital circuits, cell/ silicon compilers, design methodologies, testability, algorithms, languages, simulation, functional mapping, architectures, fault tolerance and testing, coding, radar, telecommunications, and data communications. Additional information may be obtained by contacting Paulette E. Powell, University of California, Electronics Research Laboratory, 520 Cory Hall, Berkeley, Calif. 94720.

#### ICCAD-88

November 7-10 Santa Clara Convention Center Santa Clara, Calif.

This international conference, sponsored by the IEEE Computer Society and the IEEE Circuits and Systems Society, in cooperation with the IEEE Electron Devices Society and the ACM Special Interest Group on Design Automation, is oriented toward the electrical engineering CAD professional. It will feature tutorials, and panel discussions, as well as technical sessions. Session topics will include statistical

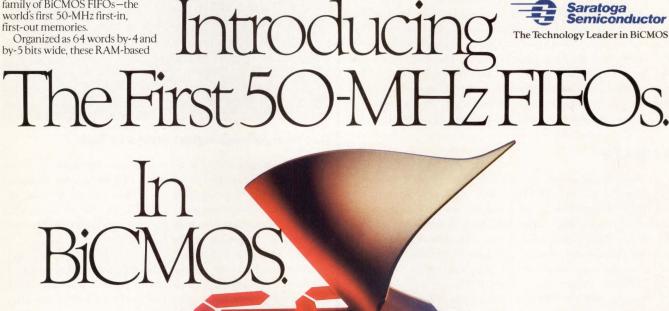

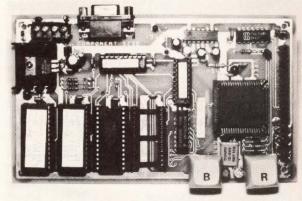

# Saratoga FIFC

**Our new FIFOs** are the world's fastest. Available now in 10, 15, 25,40 and 50 MHz.

Slow interprocessor communication headaches. You thought you'd tried every buffering remedy in the book to get rid of them.

But here's one you haven't: raw FIFO speed. Using Saratoga's new family of BiCMOS FIFOs—the world's first 50-MHz first-in,

Organized as 64 words by-4 and by-5 bits wide, these RAM-based

devices deliver performance unmatched in the industry-at 10, 15, 25, 40 and 50 MHz.

Even so, they consume no more power than CMOS FIFOs, while offering high output drive that's TTL compatible. And they can be cascaded to expand in word width and depth. Plus they're available in both commercial and military temperature ranges, in industrystandard pin-outs.

This new generation of FIFOs

will soon include 64 by 9 and larger density 512, 1K and 2K by 9 devices. Joining Saratoga's existing lines of high-performance TTL and ECL static RAMs-also among the fastest now available. And all made possible by our proprietary BiCMOS technology-SABIC<sup>™</sup>-which combines the best of both the bipolar and CMOS worlds.

So if system timing headaches have got you down, take one of our new FIFO buffers. And call us in

the morning: (408) 864-0500. Or write: Saratoga Semiconductor, 10500 Ridgeview Court, Cupertino, CA 95014.

| Saratoga FIFO Memories    |                             |  |  |

|---------------------------|-----------------------------|--|--|

| Clock Frequency           | 50 MHz (40 MHz<br>military) |  |  |

| Data Access Time          | 15nsec                      |  |  |

| Data Set-up and Hold Time | 3 nsec                      |  |  |

| Bubble-through Time       | 25 nsec (max)               |  |  |

| Power Consumption         | 385mW                       |  |  |

| Output Drive              | 16mA                        |  |  |

# tream

#### **RISC Microprocessor Sales to Top \$500 Million**

otal revenues for 32-bit RISC chips are predicted to grow from \$17 million in 1987 to \$505 million in 1992, a compound average growth rate (CAGR) of 96.3 percentaccording to a recently published study by The Information Network, a San Francisco-based market research company. This is four times the growth rate (24.7 percent) expected for 32-bit CISC chips, over the same period of time. The study also found that the manufacturers of RISC chips, both 16- and 32-bit implementations, have focused their attention on embedded controller applications, where the increased response speed of RISC-based systems is a must for realtime operation.

.....

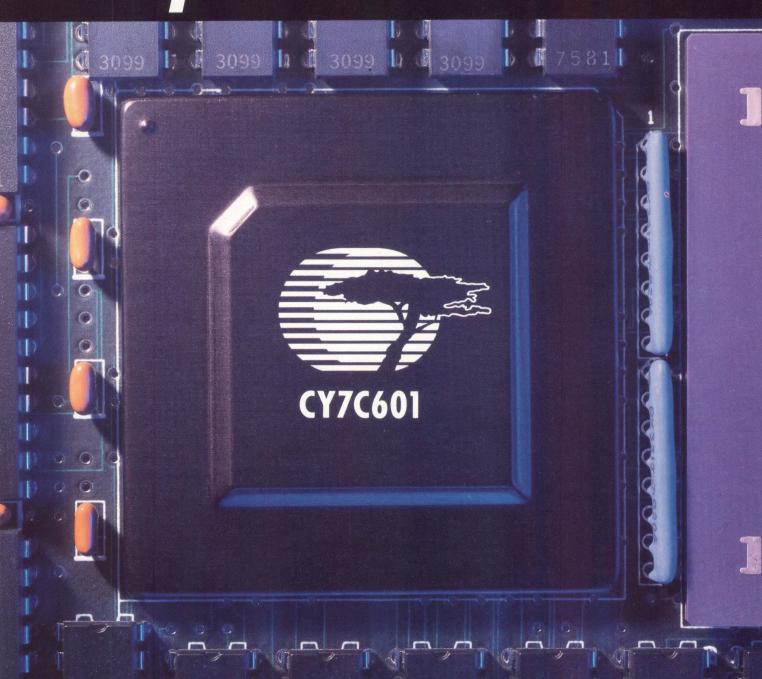

#### **SPARCs Fly**

otorola has sued the developer of its 88000 chips, Roger Ross, and received a restraining order preventing Ross from using Motorola proprietary information when creating variations of the SPARC architecture.

Competition in the SPARC arena has intensified with Texas Instruments' licensing of-

SPARC from Sun Microsystems. TI's now an alternate source for Cypress Semiconductor's SPARC implementations. In addition, startup Solbourne Computer (Longmont, Colo.) announced that it will be developing a 64-bit implementation of SPARC with the help of Matsushita Electric Industrial Co. of Japan.

#### **Cut Your Analog/Digital Arrays to Size**

.......

xar Corporation (San Jose, Calif.) has enhanced its Flexar Series of analog/digital arrays to provide programmable die sizes. Exar fixes only the vertical dimension of the die and places bonding pads and I/O circuits at the vertical extremes. No bonding pads interrupt the horizontal rows of active components that result. After the design is laid PNP transistors.

out across the rows, bonding pads and scribe lines are placed at either end of the layout. Finally, the die are cut to size, achieving close to 100 percent die utilization.

The new Flexar Delta Family of arrays use active components, which are individually programmed with metal interconnects to operate as NPN or

#### **Tektronix Testers Toil at 200 MHz**

wo new VLSI test systems-targeted at high speed, high pin count CMOS, ECL, and GaAs chips-were unveiled by Tektronix Inc. (Beaverton, Ore.). Both new testers, the LT-1100 and LT-1100 +, support up to 512 pins and deliver pattern rates at 100 and 200 MHz, respectively. The LT-1100+

> can deliver 100 MHz stimulus signals without multiplexing, and with an overall placement accuracy of  $\pm 275$  ps, while the LT-1100 delivers 50 MHz signals with  $\pm 500$  ps accuracy. Priced from \$1.6 million, the new Vista Series of semicon-

ductor testers were designed to compete with the Advantest 3381 and Ando 9037.

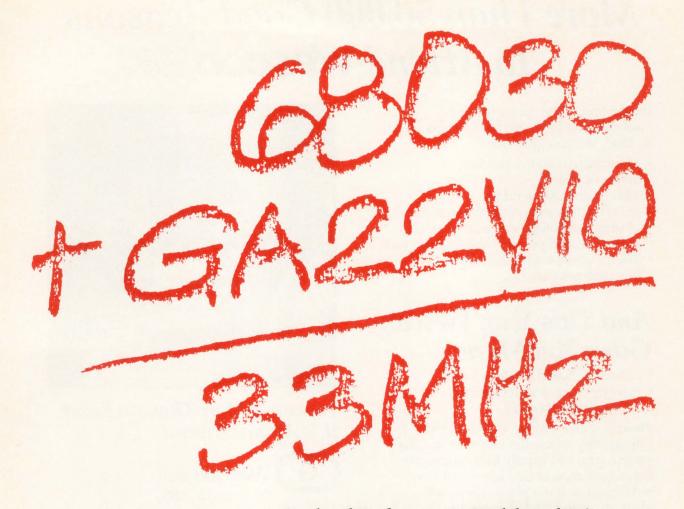

#### **GaAs for the Masses**

o convince designers that GaAs will be economically competitive with silicon, Gazelle Microcircuits Inc.

(Santa Clara, Calif.) has forecast that its 10 nsec GA22V10 GaAs PLD will be priced at \$13 each in 1990. This price is

based on 10,000piece orders, and represents a 58 percent drop from today's prices, which were reduced 27 percent just last month. David MacMil-

lan, Gazelle co-founder and vice president of marketing, said, "This lower price reflects the first step on our learning curve for gallium arsenide. While the silicon industry is nearing the end of its learning curve, we are just beginning to

accelerate on ours." For example, GaAs requires only half of the critical mask steps as silicon does.

Gazelle is wasting no time making faster and more flexible PLDs as well. The company's new GA22V10-7,

> quantity priced at \$37, has a maximum propagation delay of 7.5 ns allowing the chip to operate with clock frequencies to 110 MHz.

Gazelle's new

GA22VP10-7 is functionally compatible with the silicon 22VP10 from Texas Instruments Inc., but has less delay. The 22VP10 adds internal feedback paths to the 22V10 design to make registered outputs bidirectional.

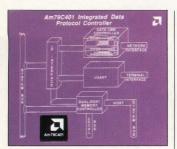

#### **Communications Controller Fits ISDN**

he Am79C401 Integrated Data Protocol Controller (IDPC) from Advanced Micro Devices Inc. (Sunnyvale, Calif.) integrates key components for building communications processors and terminal adapters for HDLCbased packet networks, including ISDN, X.25, the System Network Architecture (SNA), and the Digital Multiplexed Interface (DMI). It is designed to work seamlessly with AMD's current family of ISDN devices.

The IDPC includes a Highlevel Data Link Controller (HDLC), a USART, and a dual-port memory controller. Comprehensive software development packages from AMD, such as its AmLink3, help designers implement the layertwo functions, according to the seven-layer ISO model of ISDN (with LAPD protocols) and X.25 (LAPB) applications. It comes in a 68-pin PLCC or LCC package for \$18 in 100 quantities. A plug-in evaluation board for personal computers is also available from AMD for \$1,750.

#### TriQuint Toggles 4,200 GaAs Gates at 100 GHz

U p to 4,200 equivalent gates are available in TriQuint Semiconductor Inc.'s (Beaverton, Ore.) new GaAs gate array family that can operate in applications requiring toggle rates as high as 1 GHz. The three new arrays, which are fabricated in a 1 micron Enhancement/Depletion MESFET process, provide 2,000, 3,000, or 4,200 gates with internal support for 40, 64, or 84 dedicated high-speed I/O pins, respectively. The I/O pins can be programmed to interface with TTL, CMOS, or ECLlogic.

.....

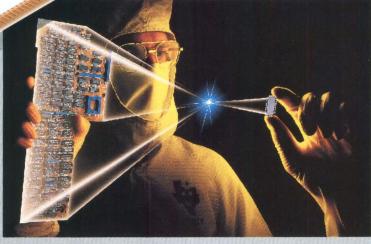

#### **Dataprobe Creator Builds 1.2-GHz Test System**

Using electro-optical connections to a device under test, the System E/O from Photon Dynamics Inc. (San Jose, Calif.) is able to test devices at speeds of 1.2 GHz, with an overall timing accuracy of 50 psec and resolution of 10 psec. Creator Francois Hen-

BARR

ley, shown with Photon Dynamics President Dick Barr, was the developer of Mitsui's laserbased Dataprobe engineering characterization test systems. Based on Henley's Ph.D. work, the System E/O uses a Nd:YAG laser and electro-optical sampling techniques to determine output voltage without an electrical connection to the DUT pins.

HENLEY

# Odds are 50-50 your perfect ASIC is a perfect dud the first time you plug it in.

#### That's why Mentor Graphics lets you combine ASIC and board circuitry in a single simulation.

#### Trouble in ASIC paradise.

The big day has arrived.

Your first gate array is back from the foundry. With high expectations, you plug it into your board and power up.

It doesn't work.

Don't feel alone. Over 50% of ASICs aren't operational when first installed in their target system. Even though 95% pass their foundry tests with flying colors.

#### An immediate solution.

Mentor Graphics shifts these even odds heavily in your favor with our QuickSim<sup>™</sup> logic simulator, which lets you simulate both your ASIC and board circuitry in a single run.

With QuickSim, you not only track the internal operations of your ASIC circuitry, but also its transactions with the system at large. If there's a problem, you see precisely where it's located, either inside or outside your ASIC. All in a single, interactive simulation environment, where you can view and graphically "probe" the circuitry created by our NETED<sup>™</sup> schematic editor.

#### Check out our libraries.

Library support is an ideal benchmark to gauge the true worth of an electronic design automation system. The more diverse and plentiful the component modeling libraries, the greater the design capability. It's as simple as that.

By this simple, yet decisive measure, Mentor Graphics brings you unequaled design capability. While other EDA vendors scurry to produce their own ASIC libraries (with little guarantee of accuracy), more ASIC vendors put their libraries on Mentor Graphics workstations than any other. And in most cases, we're the first workstation supported, which means you have the first shot at exploiting new chip technologies.

With Mentor Graphics, you get a breadth of LSI and VLSI component models, both hardware and software based. All of which can be mixed with ASICs in a single simulation that cuts your run time to an absolute minimum.

#### To be continued.

So much for the present. We're already developing new systems EDA tools that will extend to every dimension of electronic product development. From high-level systems descriptions to CASE. It's what our customers expect. It's what we'll deliver.

It's all part of a vision unique to Mentor Graphics, the leader in electronic design automation. Let us show you where this vision can take you.

Call us toll-free for an overview brochure and the number of your nearest sales office.

Phone 1-800-547-7390 (in Oregon call 284-7357).

> Sydney, Australia; Phone 612-959-5488 Mississauga, Ontario; Phone 416-279-9060 Nepean, Ontario; Phone 416-279-9060 Sal-139-46-9604 Munich, West Germany; Phone 49-57096-0 Neu-Isenburg, West Germany; Phone 49-6102-25092-94 Hong Kong; Phone 852-566-5113 Givalayim 53583, Israel; Phone 972-777-719 Milan, Italy; Phone 39-824-4161 Asia-Pacific Headquarters, Tokyo, Japan; Phone 813-505-4800 Tokyo, Japan; Phone 813-505-4820 Osaka, Japan; Phone 813-589-2820 Osaka, Japan; Phone 816-308-3731 Seoul, Korea; Phone 826-248-6333 Spanga, Sweden; Phone 468-750-5540 Zurich, Switzerland; Phone 411-302-64-00 Taipei, Taiwan; Phone 846-2-776-2032 Haltweg, Netherlands; Phone 31-2907-7115 Singapore; Phone 547-791-111 Bracknell, England; Phone 44-344-48248 Livingston Scotland; Phone 445-06-412222 Middle East, Far East, Asia, South America; Phone 503-626-7000 Helsinki, Finland; Phone 358-0-45571 Madrid, Spain; Phone

Yourideas. Our Exp

#### EOPL

ATE and EDA challenge an Ocean Engineer

E was only nine vears old when he first made up his mind about his future. "From the minute I saw that movie in the Rialto Theatre in El Darado, Ark., I knew what I wanted to do," said Joe Lassiter, vice president and general manager of the Electronic Design Automation Group at Teradyne Inc. (Boston). The movie was "Twenty Thousand Leagues Under the Sea," a Walt Disney production based on the Jules Verne novel. "There's nothing as magic as the ocean if you live in a town like El Darado," he added.

Joe Lassiter kept his career on a steady nautical course until 1974, when—as an assistant professor of Ocean Engineering at MIT—he again made up his mind quickly, and decided that Teradyne, a leading ATE manufacturer, was the new course he should follow.

His perseverance in keeping to his chosen course was very evident—even when he was 13. By this time his family had moved to Houston, Tex. and Joe had signed up as a deck hand on a research vessel operated by Texas A&M University's Oceanography department. He spent the first of many Summers working in the Gulf of Mexico. But in later years his activities were in more exotic locations like the Red Sea and the Persian Gulf.

Joe continued working at his first love and in 1969 received a BS in Engineering from MIT, quickly followed by an MS and PhD. in Ocean Engineering.

During the time he spent on the Gulf of Mexico, he was fascinated

Teradyne's Joe Lassiter

Makes Up His Mind Fast

by the reduced wave activity in certain offshore areas when hurricanes slammed into the Gulf. Apparently a muddy bottom helped disperse the waves' energy. This phenomena was still on his mind ten years later and it became the topic of his Ph.D. thesis.

While teaching Ocean Engineering at MIT, he met Alex d'Arbeloff—president of Teradyne Inc. (Boston), an MIT alumnus, and a member of MIT's committee on the future of engineering education. d'Arbeloff convinced him to spend his sabbatical at Teradyne. "It only took me about six or seven weeks to make up my mind that my future was here with Teradyne," Lassiter observed.

While employed in ocean engineering, he made many technical and economic studies of projects such as off-shore drilling platforms. Later at Teradyne, this combination of engineering and economics served him well. The international aspects of his ocean engineering career also helped prepare him for the worldwide role that Teradyne products now play.

At his new company, he found a "tremendous opportunity to do a lot of things that can make a big difference to customers in terms of the value they get out of their

#### **F**ROM THE MINUTE I SAW THAT MOVIE

IN EL DARADO I KNEW WHAT I WANTED TO DO.' investments. That means there are opportunities to try things that are interesting technically, opportunities to figure interesting ways to sell the customer, and opportunities to help the customer apply the product. It's a very rare combination.," said an enthusiastic Lassiter.

A Ph.D. and an academic background didn't inhibit Joe at Teradyne. He quickly rolled up his sleeves and worked as a technician for six months to get acquainted with electronics from the ground up. He soon became product manager of the board test group, where he was involved in board testing, backplane testing, laser trimming, and simulation.

But most of his activity was concentrated in the marketing arena, where he had the chance to bring new products to the market and work with the engineering and sales departments. "I helped in getting products that met the customers' needs and also in getting feedback to the engineers so they could make the right technical trade-offs," he added.

Joe now oversees the company's design automation as well as the board test business. This includes Teradyne's recent acquisitions— Aida, Case Technology and Zehntel—moves that he strongly urged as a board member at Teradyne.

Fortunately, the challenge of his new career excites him enough so that he's never looked back at his ocean engineering days. But, whenever he gets a chance for a vacation, he always takes his wife and two young daughters to a spot near the water—because he still remembers that movie and still "loves to snorkel and fish."

-Roland Wittenberg.

## Trying to design tomorrow's ASICs with yesterday's tools? Now there's ChipCrafter.

ChipCrafter<sup>™</sup> is the integrated design tool that takes your complex CMOS ASIC design out of the stone-age and into the future.

High-level compilers, configurable libraries, process independence, and logic synthesis make ChipCrafter designs efficient. Automatic place and route, buffer sizing, and timing analysis at your Mentor Graphics<sup>™</sup> workstation makes them easy, and as dense as hand-packed.

#### FREE. ASIC Estimating Kit.

What will it take to do your design with our cutting-edge design tool? Our free ASIC Estimating Kit lets you analyze design trade-offs, including performance and cost implications, in a variety of processes. Find out how ChipCrafter and Seattle Silicon chip away at design restrictions to deliver the next generation of ASICs. Call for your free kit: 1-800-FOR-VLSI ext. 500.

3075-112th Ave N.E., Bellevue, WA 98004, (206) 828-4422. Copyright 1988, Seattle Silicon. ChipCrafter is a trademark of Seattle Silicon Corp. Mentor Graphics is a trademark of Mentor Graphics Corporation.

**CIRCLE NUMBER 4**

The effectiveness of logic synthesis is determined by more than speed and size

Automation Conference, Andy Rappaport of the Technology Research Group Inc. said that logic synthesis represents the new frontier in electronic design automation, opening the way for a quantum increase in system complexity with only a small increase in design complexity. Looking at the crop of programs at this year's Design Automation Conference, the current product offerings don't fulfill that promise for high-density, multi-chip system designs.

The high-performance systems designer is looking for design tools that can significantly reduce the complexity of design while maintaining control of any variables that impact performance. Local optimizations that reduce logic are desirable but do not deliver the full benefits that logic synthesis is capable of. At Integrated CMOS Systems we have been applying logic synthesis approaches to high-performance systems for more than five years. We have identified three key leverage points that logic synthesis must observe to be beneficial in solving system design problems.

Logic synthesis can be focused on minimization of combinatorial logic, sequential logic (finite state machines), and hierarchical structures such as chip interconnects and functional boundaries. Today's logic synthesis tools optimize the combinatorial and sequential logic for each functional blocks within an individual chip.

#### Does Logic Synthesis Work For Multi-Chip, High-Gate-Count Systems?

#### TOM MILLER, VICE PRESIDENT, SALES AND MARKETING, INTEGRATED CMOS SYSTEMS, INC., SUNNYVALE, CALIF.

The key leverage points for highperformance, multiple-ASIC systems, however, are found in the optimizations at the boundaries of each functional block.

The first leverage point applies both global and local optimizations interactively to achieve the system design objectives. For this purpose, user-programmable scripting lets the user change the order of application of optimization routines and introduce applicationspecific transformations. User scripts tune the synthesis to the target system, reduce the time to process the logic, and help ensure that the synthesizer uses the same optimum sequence of operations each time it is invoked (an issue called repeatability).

The second leverage point is the importance of *traceability* of the original logic functions and signal names during the logic synthesis transformations. When logic networks take on different forms, engineering changes become a challenge if the original design disappears. In addition, designation of high-level structures such as multiplexers, tri-states and adders can be used for global transformations if the information is **FOR COMPLEX** DESIGNS, LOGIC SYNTHESIS

DEPENDS ALMOST Exclusively on Heuristics' not lost during synthesis.

The third leverage point is the intelligent application of logic synthesis to prevent synthesis from taking excessively long. Because the speed of processing increases with the number of gates, designers of systems with high gate counts must apply logic synthesis carefully to avoid excessive costs and project delays. For even a few thousand gates, the processing can take several hours. The best approach applies local transformations first, and then explores global optimizations in the remaining problem areas.

Logic synthesis can be an important addition to the designer's toolbox, controlling complexity while allowing exploration of more design options. Automation of combinatorial logic minimization is applied successfully today to the design of PLAs, PLDs and even some low-density gate-array and standard-cell designs.

But for more complex high-level designs, logic synthesis depends almost exclusively on heuristics. Unfortunately, significant development in heuristics still remains before logic synthesis can deliver the capabilities required for multichip, high-gate-count system design.

**TOM MILLER** is the vice president for Marketing and Sales at Integrated CMOS Systems, Inc. (Sunnyvale, Calif.). Previously, he was director of Strategic Marketing at Fairchild Semiconductor, director of VLSI at NCR Corporation, and also a product-line manager at Texas Instruments. He holds a BS in Computer Science from the State University of New York at Stony Brook.

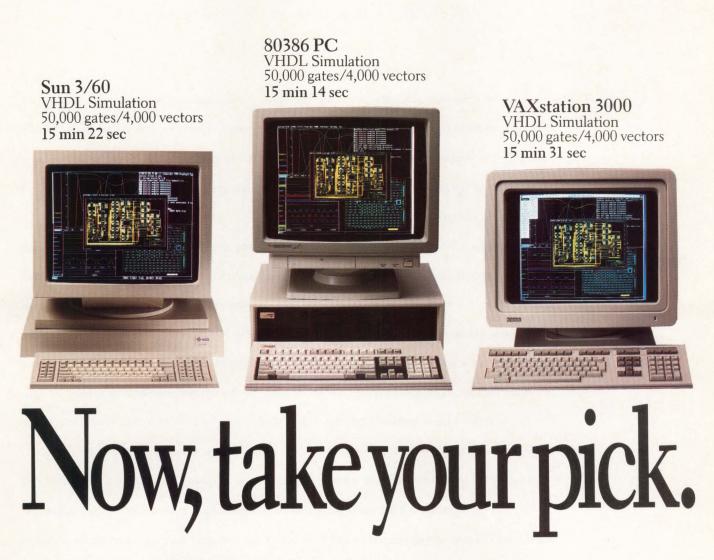

#### Previously, the best CAE tools were available on only one platform.

From the leader in desktop CAE solutions comes a new concept in electronic design: you pick the platform.

Viewlogic<sup>®</sup> was the first to deliver a premium CAE solution on 286/386 PCs through "native mode" technology. Now we've ported the entire Workview<sup>®</sup> suite of CAE solutions—including VHDL simulation, a mixed analog/digital simulator, and ASIC vendor kits—to Sun and VAX<sup>™</sup> workstations. For example, you can run a VHDL circuit simulation of 50,000 gates in minutes on a 386/PC, Sun Workstation<sup>®</sup> or VAX station. Standardize on one, or pick a combination and design complex ICs, ASICs, and systems in a multiple platform environment—and retain a common user interface and shared database.

With Workview, you have access to superior CAE solutions on today's three most popular workstations in electronic design. For more information, call: 1-800-CAE-VIEW; in Massachusetts, 1-508-480-0881.

VIEWlogic

#### desktop CAE and beyond

Viewlogic Systems Inc., 313 Boston Post Road West, Marlboro, MA 01752

Viewlogic and Workview are registered trademarks of Viewlogic Systems Inc., VAX and VMS are trademarks of Digital Equipment Corp., Sun Workstation is a registered trademark of Sun Microsystems Inc.

**CIRCLE NUMBER 5**

# What is Logic Synthesis?

#### DAVID SMITH, SENIOR EDITOR, VLSI SYSTEMS DESIGN

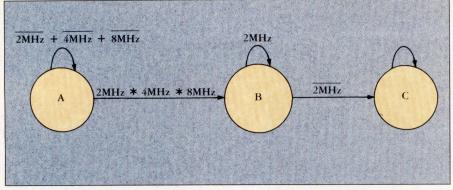

he generally held definition for the term "synthesis" is the combining of parts or elements to form a whole, or compound. In electronics, synthesis has come to mean the building, by computer program, of a description of all or part of an electronic design—be it a chip, board or system. A logic synthesis tool, therefore, builds a logical description of an electronic design.

The confusion currently involving logic synthesis has several causes. First, the term "logic synthesis" is used popularly to represent a synthesis tool that constructs any type of electronic design, ranging from a PLD fuse map to a register-transfer block diagram. The second source of confusion concerns the term "logic." A gate-array logic design is composed of gates; a PLD logic design may be a fuse map; and a logic diagram of a board design contains 7400-series logic packages. A logic-synthesis program, therefore, can use any of these elements to build a design. Finally, as soon as logic synthesis became a buzzword, many vendors of design automation tools hung out the "logic synthesis" shingle simply by renaming existing products.

Since logic ranges from fuses to packages, and synthesis spans PLA mapping to algorithmic development programs, it's not surprising that logic synthesis is such a potent, and misunderstood, term. To the designers who stand to benefit from this relatively recent addition to design automation, the question is more than, "What is logic synthesis?" The question is, "What does

Synthesis

and

compilation:

mutual

subsets?

IS LOGIC SYNTHESIS A BREAKTHROUGH FOR DESIGN PRODUCTIVITY?

# OurASIC line-u is on half the story.

When it comes to delivery of high-quality, reliable ASICs, S-MOS wrote the book.

We did it in collaboration with our manufacturing affiliate, Seiko Epson. With 18 years of CMOS experience, Seiko Epson is one of the world's most advanced CMOS IC manufacturers.

Through Seiko Epson's high-yield manufacturing technology, we ship millions of ASIC units a month, and with a reject rate of less than .0001%. That's our quality story.

Now we've added a new chapter on design. At our advanced R&D design facility, engineers from S-MOS and Seiko Epson are developing new software to simplify circuit design, simulation and the creation of new megacells for our extensive cell library.

Of course, you can still take advantage of our established design

tools because S-MOS supports such workstations as Daisy, Mentor, Calma and PC-based systems using FutureNet, OrCAD and ViewLogic.

Our proprietary LADS simulator will speed up the design process. The S-MOS engineering team will support you from concept to production.

If you are looking for an ASIC program that can make your designs best sellers, call us. (408) 922-0200.

| Paner<br>Person |  |  |

|-----------------|--|--|

|                 |  |  |

|                 |  |  |

|                 |  |  |

|                 |  |  |

| CMOS Gate Arrays                                                                                                                                                                                                                    | CMOS Standard Cells                                                                                                                                                | Compiled Cell Custom                                                                                                                                                                                                                                                                                                                                              |                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Up to 38,550 available gates<br>SLA8000 (800 ps)*,<br>1.2µ drawn, 1.0µ Leff.<br>SLA7000 (1.0 ns)*,<br>1.5µ drawn, 1.2µ Leff.<br>SLA6000 (1.8 ns)*,<br>2.0µ drawn, 1.5µ Leff.<br>SLA700B High Drive<br>Output<br>SLA100L Low Voltage | Complexities to 16K gates**<br>• SSC1000 (1.4 ns)*,<br>1.8µ drawn, 1.4µ Leff.<br>• Fully migratable from<br>S-MOS gate arrays<br>• RAM and ROM<br>blocks available | <ul> <li>The Alternative to Full Custom</li> <li>1.8μ CMOS process</li> <li>Can utilize dissimilar<br/>cell geometries</li> <li>3-button approach<br/>to custom design</li> <li>Currently over 300<br/>fully characterized cells</li> <li>Fast 14-week<br/>implementation time</li> <li>Timing-driven TANCELL<sup>®</sup><br/>place-and-route software</li> </ul> | SYSTEMS<br>S-MOS SYSTEMS, INC<br>2460 North First Street |

IANCELL is a registered trademark of langent systems. "Typical propagation delay of 2-input NAND gate driving 2 internal loads with 1mm of interconnect. "Maximum gate utilization depends on amount of interconnect used.

#### **CIRCLE NUMBER 6**

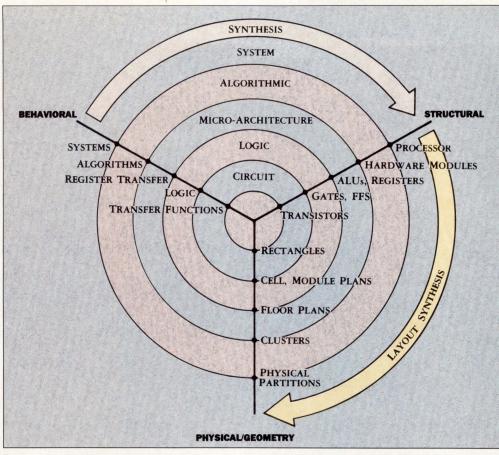

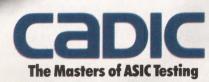

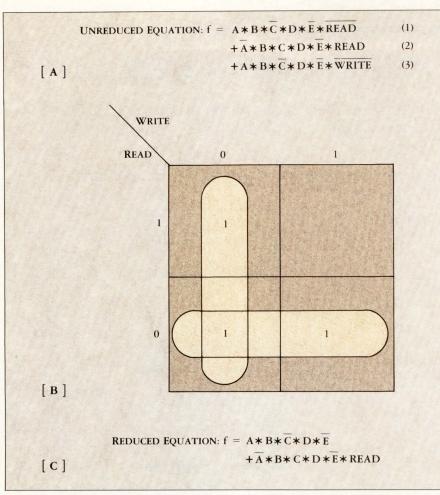

Figure 1. The Y chart proposed by Gajski and Kuhn plots the evolution of an electronic design through three domains of description—behavioral, structural, and physical. Levels of detail are represented by concentric circles. Creating a structural description from a behavioral one is popularly called synthesis or logic synthesis; creating a physical description from a structural one is referred to as layout synthesis.

#### this program do for me?"

#### MOVING ON THE Y CHART

To understand how logic synthesis is perceived, it's helpful to consult the Y chart (Figure 1) first proposed by Daniel Gajski and Robert Kuhn (Gajski and Kuhn, 1983). It contains three axes representing domains of electronic design description: behavioral, structural, and physical. The concentric circles represent levels of detail, such as micro-architectural, register-transfer level, and logic level. The end-result of any design is its physical implementation, e.g. for an IC, a fabrication database would be expressed in polygons.

The Y chart maps the progress of a design through different types of descriptions (domains on the axes) and progressive levels of detail (circles). For example, if a design is expressed as a set of Boolean equations, it can be translated into a netlist made up of logic gates from a gate array library. The process would be represented by an arrow from the behavioral to the structural domain, starting and ending on the logic circle. The design could then be placed and routed by layout programs, cess taking the design from the structural to the physical domain. "Fracturing" the design database for manufacture move the design to the circuit circle.

The Gajski chart, therefore, plots the evolution of a design through domains of description and levels of detail. It is conceptually useful in discussing logic synthesis because it provides a visualization of the mechanics and purpose of a proposed logic synthesizer. It indicates where the synthesizer starts, what its intermediate steps are, and what its output is.

The term "synthesis," in electronic design, means the

building of a structure for a design based on its behavioral description. This can be shown as an arrow from the behavioral to the structural domain on the Y-chart. "Logic synthesis" is often used synonymously with "synthesis" to represent an entire class of tools that builds designs in the structural domain.)

Developers of CAD tools often use the word synthesis in the context of automatic generation of an IC layout, known as layout synthesis. This usage suggests that the modifier "logic" was coined to differentiate synthesis tools that build structural descriptions from those that build layouts.

The "building structure" definition is supported by such industry leaders as the Technology Research Group, Jeff Fox of Silc Technologies, and Gajski himself. The definition seems convenient when attempting to distinguish tools that build structure from those that improve it—optimization programs—and from those that create a physical design from a structural one—layout synthesis (which many perceive as silicon compilation).

Unfortunately, the type of *input* that a logic-synthesis tool accepts is not as cut-and-dried. For example, Professor Giovanni de Micheli at Stanford University's Center for Integrated Systems agrees that the term "synthesis" implies the creation of a structure. He adds, however, that the design input may not necessarily be behavioral: "Synthesis is closely related to structure, [generated] from either a function or another structure".

De Micheli is alluding to the fact that most designs are a combination of behavioral and structural descriptions rather than pure behavioral. Art de Geus, of Synopsys Inc., says that adding structural information directs the tools to produce efficient designs. "What we are is an RTL-level down system," says de Geus, referring to the register-transferlevel input (which has behavand structural ioral components) that Synopsys' Design Compiler breaks down into a logic-level output.

Structural input is also important when the designer is using certain functions with well-known, dense implementations that logic synthesizers don't recognize. For example, Howard Moscovitz of AT&T explains that "logic synthesis tools can't yet select appropriate DSP-architectures, such as bit-serial, bit-parallel, or serial parallel" (Moscovitz, 1988). Structural statements can be used to preserve the structure when partitioning designs.

According to these experts, logic synthesis generates a structural design description from an input specification containing behavioral and structural information. But if the input is primarily structural, synthesis is when a more detailed structural design results, such as a flip-flop schematic resulting from a register-file input. A design tool is

# COUNTROS COUNTCOS CALLCADIO

#### ...FOR ASIC TESTING

This is the ASIC tester many Fortune 100 companies count on when they want to control costs. Capacities range from 32 to 352 pins, at prices as low as \$163,000 for a 256 pin system.

#### **BASIC ASIC**

The CADIC STM5200 is straightforward, simple to learn and easy to use. A special utility, which generates test vectors from simulator output, makes testing even easier.

#### **POWER AT THE PIN**

All pins are fully bidirectional. A patented SoftWire<sup>™</sup> system eliminates fixture building, makes all pins usable and expensive personality cards obsolete.

#### **COST AND EFFECT**

ASICs make your products competitive. They make ours competitive too. In fact, they're the secret to the low cost of this 25 MHz dynamic tester.

#### **PIN US DOWN!**

Free demo disk. Call 1-800-824-1617, ext. 5200.

**CIRCLE NUMBER 7**

Figure 2. In addition to building structure from behavior, synthesis is also used to describe the creation of more detailed levels of description. If a tool begins and ends with the same type of description and level of detail, it's an optimizer. All synthesis and optimization tools are usually lumped within silicon compilation.

actually performing optimization (Figure 2) if its input and output have the same level of detail.

#### ■ IS IT LOGICAL?

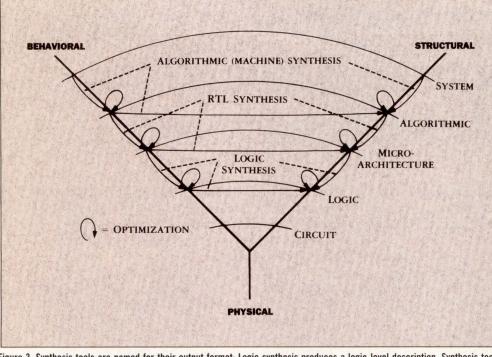

The modifier "logic" introduces other nuances to the term "synthesis." Specifically, the circle on the Y chart labeled "logic" represents a level of detail at which semicustom IC users develop design specifications. These users require the logic synthesis tools' output in a logic-level (Figure 3) structural form: either a netlist or a schematic. The definition that logic synthesis creates logic-level descriptions is bolstered by an analogy to the term "silicon compilation," the automated design of siliconlevel circuits.

However, Gajski views logic synthesis as working strictly at the logic level, accepting logic-level *input*, such as Boolean equations, and creating a logic-level structural output. Similarly, Jeff Fox points out that logic synthesis starts with "a low-level behavioral description."

But Fox is trying to differentiate his company's tool, SilcSyn, from those that accept only logic-level inputs. Silc-Syn is labeled as a "behaviorallevel synthesis tool" because its primary mode of *input* is a behavioral language. Its output, however, is a structural design composed of gate-array or standard-cell *logic* elements. If the output defines the synthesizer, then SilcSyn should be a logic synthesizer.

The Ascyn Synthesizer from Algorithmic Systems Corp (Braintree, Mass.) supports this conclusion. This product accepts a behavioral description similar to that used with SilcSyn (they share the same progenitor: the MacPitts silicon compiler system). Still, Ascyn is presented as a logic synthesizer, creating logic-level netlists for gate arrays, standard-cell ICs, and full-custom ICs.

Users should beware when any other word besides "logic" appears before "synthesis." For instance, "behavioral synthesis" would seem to contradict the idea that synthesis creates structure. According to Fox, the term is used to indicate a logic synthesizer with a behavioral-language input.

On the other hand, de Micheli defines "behavioral synthesis" as *creating* a behavioral description, "making transformations which are independent of the structural model." In this case, the input and output may be of the same type, with synthesis creating a more detailed version.

In a related vein, "structural synthesis" can be viewed as creating structural descriptions that are composed of elements more abstract than logic-level elements. The JRS synthesis tool (see page 30), for example, can build a structural-design description using off-the-shelf ICs. But, the definition remains cloudy. For example, Misha Burich, vice president of engineering at Silicon Compiler Systems (San Jose, Calif.), writes that behavioral synthesis begins with a behavioral description of a system and "results in a structural description of a design, consisting of high-level logic elements, like registers and memories (Burich, 1988)." What, then, is structural synthesis?

These definitions may seem like exercises in semantics, but for the designer's sake, inputs should be distinguished from outputs. Given the analogy to silicon compilation, structural descriptions should issue from structural synthesizers, and behavioral synthesizers don't exist. Designers should ask, "What are the input and the output formats? What levels of detail is the program creating?"

#### ■ COMPILATION

The third area of confusion results from the fact that many of the capabilities already found in compiler products are associated with logic synthesis. Gajski looks at the entire design process, from behavioral through structural and on to physical domains, as falling under the term "compilation"— with logic synthesis is a subset of silicon compilation.

SCS agrees. It's LogicCompiler is joined by VLSI Technology's Logic Synthesizer and Seattle Silicon's Finesse software in the synthesis-from-compiler product category. According to Burich, logic synthesis "provides an additional

# Great things happen when System HILO<sup>™</sup> is your simulation choice... design and test efficiency soar!

1122222222Ch

GenRad has solved the common dilemmas of design and test groups...which simulation system to buy for IC design?...which for PCB design?...can the test group use it?...does it all work together?

Now, for the first time, your design and test people can work with a common, integrated simulation tool set, regardless of whether they're working on design verification or test development for integrated circuits or printed circuit boards.

With GenRad's System HILO, design verification and test development for both chips and boards can take place at the same time. And this means optimum working efficiency between your design and test people. The result is tremendous savings in time and money, as well as better designs and more comprehensive test programs.

The key to System HILO is a new, modular architecture. It lets your design and test people solve a broad range of chip and board problems that cannot be addressed with any single tool. It enables design to proceed in parallel with test development. Utilizing System HILO's Test Waveform Language, the test engineer can use the same simulation data as the designer. The test program can then be downloaded

and run without translation on GenRad's 275X board test systems. The result is faster, more comprehensive program development with maximum diagnostic effectiveness.

There are many more great aspects about this new simulation system from GenRad. Find out more by calling 1-800-4-GENRAD.

The difference in software is the difference in test<sup>TM</sup>

LESTER

Figure 3. Synthesis tools are named for their output format: Logic synthesis produces a logic-level description. Synthesis tools creating more abstract descriptions should do the same, though this has not always been the case so far.

mechanism for synthesizing layout of parts of a chip or an entire chip."

The input specifications for SCS's logic-synthesis tool consist of RTL languages and finite state-machine descriptions. The structure of the design is largely specified, and the tool replaces a structural description with a more detailed structural description in "the primitives in a particular cellbased technology." The tool creates a logic-level design from a less-detailed structural description. Similarly, the Finesse program accepts equations, state machines and truth tables. The Logic Synthesizer outputs schematics just like the Design Consultant logic synthesizer from Trimeter Technologies Corp (Pittsburg, Pa.). Thus, these subsets of compiler environments may be viewed as legitimate synthesis programs.

A different perspective results from from the work of users closer to front-end, CAE design. Earl Reinkernsmeyer, director of software products for NCR's Microelectronics Division, has worked with Silc to bring SilcSyn into NCR's CAE tool kit. Because contemporary logic synthesizers can produce designs for a variety of custom/semicustom implementations—such as silicon compilation—then synthesizing a logic design can be considered a superset of compilation. "When silicon compilation has a high-levellangauge input, it's a subset of logic synthesis," Reinkernsmeyer says.

The choice of semicustom or custom implementations is often used to distinguish logic synthesis from silicon compilation. Silicon compilation must produce an output for a particular full-custom process. Logic synthesis produces netlists for gate arrays, cell-based ICs, or full-custom ICs (including compiled ones). Alice Parker of the University of Southern California concurs (Parker, 1984), saying that a silicon compiler accepts "logic-level, register-transfer or abstract behavior specification and produces an integrated circuit layout." She adds that they focus on IC layouts rather than synthesis.

De Micheli considers compilation and synthesis "just a question of terminology." SCS's Dan Payne says, "different words come into vogue in the marketing battle." Designers should expect the terms "synthesis" and "compilation" to be used synonymously, because eventually the products which come from both of these processes will offer many of the same features.

#### USING SYNTHESIS

Synthesis and compilation products will eventually form two legs of an overall IC design methodology. A particular design system at AT&T, for example, positions logic synthesis as just one element out of many (such as compilers, generators, and processor cores)in an overall system for designing custom DSP chips (Moscovitz, 1988). What distinguishes logic synthesis from silicon compilation in this system is the type of circuits produced. Synthesis is best for "less-common DSP functions or for random logic functions." Compilers are most effective for for highly regular structures like registers and data paths.

Logic synthesis' most important characteristic is how it fits in with the methods of the designer. According to Nancy Madison of Valid Logic Systems, her customers most often ask how it can eliminate certain steps in the design process. In addition to filling in the blanks regarding input format and output format and the level of detail under consideration, this question can best be answered by understanding how well logic synthesis will be working with the designer's other tools, such as compilers, in his or her overall IC design methodology.

Tom Waugh of Xilinx stresses the importance of productivity in deciding what logic synthesis is. "If a set of tools provides an open system that lets the designer choose the methods of design entry that best express a design, and if the set of tools provides optimization software that frees the designer from worrying about architectural details to concentrate on higher-level design issues, then these tools are logic synthesis tools," he explains. Although convenience and management of design detail may not be the best definition of logic synthesis, they may be the most concrete impressions designers get from logic-synthesis tools.

#### REFERENCES

- BURICH, M., 1988, "The Role of Logic Synthesis in Silicon Compilation," VLSI Systems Design, Semicustom Design Guide, September, 1988, pg 56.

- GAJSKI, D. and KUHN, R., 1983, "Guest Editor's Introduction: New VLSI Tools," IEEE Computer, December, 1983, pg 11.

- MOSCOVITZ, H., 1988, "A Hybrid Approach to Application-Specific DSP Design," VLSI Systems Design, Semicustom Design Guide, September, 1988, pg 32.

- PARKER, A., 1984, "Automated Synthesis of Digital Systems," IEEE Design and Test, November, 1984, pg 75.

- TECHOLOGY RESEARCH GROUP LETTER, Vol2, no. 11, February, 1987.

- TREVILLYAN, L., 1987, "An Overview of Logic Synthesis Systems," Proceedings of the Design Automation Conference, June, 1987, pg 166.

We're eliminating the competition with something everyone else seems to have forgotten you need...

# ...the maximum performan

#### Plessey - Unsurpassed Process Technology

As system design becomes more and more challenging, and product life cycles become increasingly shorter, design flexibility and getting it right the first time have become critical factors in gaining and maintaining that maximum performance edge you've been looking for.

Plessey's investment in advanced process technology is unequaled in the industry. Successive reductions in feature size and continued improvement in process techniques are at the heart of leading-edge Plessey products.

$\ensuremath{\mathsf{PLESSEY}}$  and the Plessey symbol are trademarks of the Plessey Company, PLC.

#### Plessey - The Ultimate in ASIC Technology

Our broad range of ASIC products has grown to the point where we are now able to meet all the needs of ASIC users. We offer a full ASIC product range with a variety of options for digital, analog and mixed analog/digital applications, in gate arrays, standard cells, and full-custom. Advanced, stateof-the-art processes in fine geometry, high-density CMOS, bipolar and ECL technologies give you the highest levels of performance and system integration available today.

#### Plessey - Unparalleled CAD Support

The Plessey Design System (PDS) is a comprehensive suite of software em-

bracing the design, simulation and implementation of gate arrays, standard cell and compiled ASICs in CMOS and bipolar technologies.

Customers who want to use their own CAD workstations or simulators are accommodated by flexible design interfaces at various stages into PDS.

#### Plessey - Standard Products And Discrete Components

Plessey's standard product family offers the highest performance product range available in the world today. Capabilities range from CMOS DSP devices operating in excess of 20MHz to the world's most advanced 1.3GHz monolithic log amplifier.

High performance solutions are also offered in radio communications, digital

# nce that gives you the edge.

#

#### PLESSEY KEY PROCESS TECHNOLOGY

| BIPOLAR                                                        |                                   |               |               |               |                 |  |  |  |

|----------------------------------------------------------------|-----------------------------------|---------------|---------------|---------------|-----------------|--|--|--|

| DESCRIPTION                                                    |                                   | Ft            |               | TTER<br>DTH   | METAL<br>LAYERS |  |  |  |

| Industry standa                                                | rd                                | 400MHz 14µm   |               | μm            | 1               |  |  |  |

| High voltage                                                   |                                   | 400MHz        | 20            | μm            | 1               |  |  |  |

| High speed line                                                | ar                                | 4.5GHz 4µm    |               | um 🛛          | 2               |  |  |  |

| High speed digi                                                | tal                               | 6GHz          | z 3µm         |               | 2               |  |  |  |

| Ultra-high spee                                                | d                                 | 14GHz         | 0.6           | iμm           | 3               |  |  |  |

|                                                                |                                   |               |               |               |                 |  |  |  |

| MOS                                                            |                                   |               |               |               |                 |  |  |  |

| PROCESS FAMI                                                   | LY                                | fclock        |               | MUM           | VSUPPLY         |  |  |  |

| KC Industry standard CMOS                                      |                                   | 20MHz         | 4             | ım            | 3-10V           |  |  |  |

| JG Double SiGate NMOS                                          |                                   | 10MHz         | 64            | m             | 9-18V           |  |  |  |

| VB High speed CMOS                                             |                                   | 40MHz         | 24            | ım            | 3-5V            |  |  |  |

| VJ Very fast CMOS                                              |                                   | 50MHz         | 1.5µm         |               | 3-5V            |  |  |  |

| VQ Ultra fast CMOS                                             |                                   | 75MHz         | 1.2µm         |               | 3-5V            |  |  |  |

| MH/MA SiGate CMOS                                              |                                   | 30MHz         | 4µm           |               | 3-15V           |  |  |  |

| BIPOLAR (CDI)                                                  |                                   |               |               |               |                 |  |  |  |

| PROCESS                                                        | EMITTER<br>WIDTH/<br>FEATURE SIZE | GRID<br>PITCH | MAX.<br>Speed | MAX.<br>POWER | MIN.<br>POWER   |  |  |  |

| ORIGINAL CDI                                                   | 5µm                               |               |               |               |                 |  |  |  |

| CDI FAB I                                                      | 3.75µm                            | 11.5µm        | 10ns          | 2.4pJ         | 1.5pJ           |  |  |  |

| CDI FAB IIa                                                    | 2.5µm                             | 8µm           | 4ns           | 1.2pJ         | 0.8pJ           |  |  |  |

| Geometry change (utilizing multi-level differential logic-DML) |                                   |               |               |               |                 |  |  |  |

| CDI FAB IIb                                                    | 2.5µm                             | 8µm           | 800ps         | 0.8pJ         | 0.54pJ          |  |  |  |

| CDI FAB III                                                    | 1.5µm                             | 6µm           | 400ps         | 0.4pJ         | 0.27pJ          |  |  |  |

| CDI FAB IV                                                     | 1.2µm                             | 4.5µm         | 200ps         | 0.2pJ         | 0.14pJ          |  |  |  |

|                                                                |                                   |               |               |               |                 |  |  |  |

frequency synthesis, data conversion, telecommunications, data communications and consumer products.

Complementing the standard IC family, Plessey manufactures a complete line of discrete components including FETs, transistors and diodes available in SOT-23 and TO-92 packages.

#### Plessey - Over Two Decades Of Quality Commitment

For more than 20 years, Plessey Semiconductors has been commited to supplying the latest technology, highest quality, and highest performance semiconductor products in the industry. With our unique combination of CAD support, major advances in process technology, and the most advanced research facility in the world, Plessey Semiconductors is, today, a totally commited leader in the industry.

To learn more on how Plessey can help you achieve the maximum performance that gives you the edge, send for our new comprehensive, full color, 72-page short form brochure, or call Plessey Semiconductors today.

In North America call 1-800-441-5665. Outside North America call 44-793-726666. For further information you can write to us at one of the following addresses:

Plessey Semiconductors 1500 Green Hills Road Scotts Valley, CA 95066 U.S.A.

Plessey Semiconductors Ltd. Cheney Manor, Swindon Wiltshire SN2 2QW United Kingdom

# Synthesizing a d a's i d e a l machine mate

DEBORAH W. RUNNER AND ERWIN H. WARSHAWSKY, JRS RESEARCH LABORATORIES, INC., ORANGE, CALIF.

**Embedded** computer applications can demand performance that is beyond the current capabilities of standard microprocessor systems. The capabilities of a computer designed for these applications is measured by the execution speed of the actual problem set on the real machine. Design inadequacies are determined by the difference between actual performance and that optimum performance that can result from mapping software algorithms onto hypothetical hardware systems.

For such design considerations, the JRS IDAS tool set automatically derives relevant performance indices about hardware and software designs. It maps Ada programs onto machines described in VHDL, synthesizes machines described in VHDL from specifications expressed as Ada programs, retargets microcode compiler tools from a VHDL machine description, and guides users in rapidly evaluating numerous design alternatives and comparing the alternative approaches objectively and quantitatively.

Embedded computer applications such as signal processing, real time

programs mapped onto VHDL

ADA

described

machines

artificial intelligence, and image processing, have unlimited computing performance requirements—the more performance, the better the solution that is possible or the larger the problem that may be attacked. Furthermore, these embedded computer applications are usually severely constrained by other factors such as power, weight, size, schedule, reliability objectives and cost. The JRS Integrated Design Automation System (IDAS) focuses on solving the design and programming problems inherent in this type of system.

Embedded computer design and application problems are bound problems and are well-suited, therefore, for the application of design automation and design optimization techniques. They have known, specific requirements to solve one distinct problem. Computational requirements are known and may be explicitly characterized by specifications or program benchmarks or both. Non-computational requirements, such as power and cost, may also be known and explicitly specified. Valid solutions to the design problems must simultaneously satisfy all of the design requirements and constraints. Finally, everything is subject to change without notice.

The number of stringent criteria that must be simultaneously met make these high-performance embedded-computer applications extremely difficult to design effectively without tools; in fact, these designs are still a great challenge with an effective automation system. Fortunately, the specificity of the embedded applications provides focus and explicit success criteria to the design process, characteristics of great value in design automation.

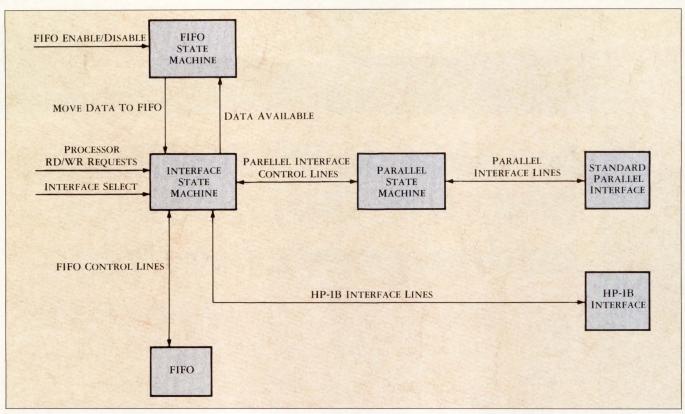

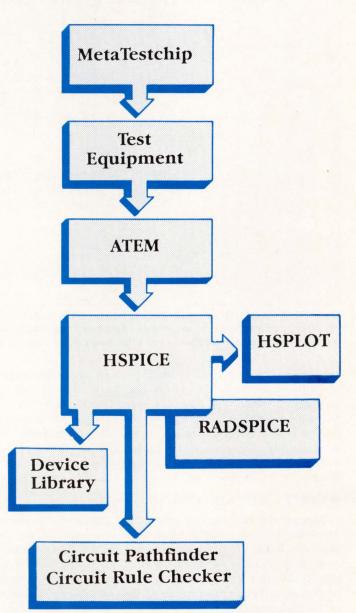

Using that focus and conscious of the design criteria, JRS has integrated the major functional blocks in Figure 1 into the JRS IDAS embedded-computer design and programming environment. Machine (computer) and component descriptions expressed in VHDL (VHSIC hardware description language) are stored in the IDAS library, which is an object-oriented database. JRS IDAS has two major functions: generation of an Ada-to-microcode compilation environment for a machine specified in VHDL and creation of a machine expressed in VHDL that executes a user-supplied Ada program.

The Ada compiler block at the top of Figure 1 compiles Ada programs into microcode for a selected machine described in VHDL. User-written microcode can be merged into the automatically generated microcode and linked together for execution on a VHDL simulator for the target machine. The VHDL simulator is automatically generated, based on the VHDL machine description, and is then available for simulations of Ada applications.

IDAS has the capability of synthesizing a machine that is uniquely suited to a given application expressed in an Ada program. The machine is synthesized using library components within the IDAS database. The VHDL description of the synthesized machine may be used to automatically generate an Ada compilation environment and a VHDL simulator. It can also be transferred to a silicon compiler to produce an ASIC design compatible with a VHSIC-class semiconductor fabrication line.

IDAS has several other functions as well to support design and analysis of embedded computers. The user interacts with the synthesizer to manage software/hardware trade-offs, allowing the designer to create and analyze alternative architectures using actual applications code. Feedback from the system allows objective measurement of design trade-offs, removing some of the guesswork. IDAS allows designers to reuse existing code and machine descriptions in new applications, simplifying technology transfer and getting the most use out of existing designs. In short, it makes design more of a science and less of an art.

#### ADA COMPILATION

For input of Ada programs, IDAS provides an Ada compiler capability that generates microcode for an arbitrary horizontal processor; it translates application programs written in Ada directly into microcode that executes at the "microengine level" of a target machine (Figure 2). By so doing, it obtains substantial performance advantages over compilers that compile to target macro-languages or instruction set architectures (ISAs). The ability to use Ada as the application program-

# TEXAS INSTRUMENTS REPORTS ON SYSTEMS LOGIC

# IN THE ERA OF INTHE ERA OF INTHE ERA OF

Systems logic in the Era of MegaChip Technologies:

# No system should ever be limited by its to help your design perform at its best.