# Daisy's standard now runs on an

# Introducing the Advansys Series<sup>™</sup> of high performance CAE workstations.

Now the electronic design environment you've dreamed of is here.

Because the most advanced design tools in the world now run on the world's most advanced standard platform.

The Sun 386i™

We call it the Advansys Series.

And it encompasses some of the most powerful design tools ever developed. Plus a variety of affordably priced workstations. Including the 20 MHz and 25 MHz Sun 386*i*, as well as Daisy's own LOGICIAN\* 386 and the newly enhanced Personal LOGICIAN<sup>™</sup> 386. All share a standard system

level environment, featuring UNIX," advanced X Window System graphics, Sun's NFS™ distributed file system and standard TCP/IP communications.

Now you can get the workstation performance and flexibility you've demanded for your desktop. Including up to 5 MIPS of processing power, high resolution graphics display and an integrated UNIX/ DOS environment.

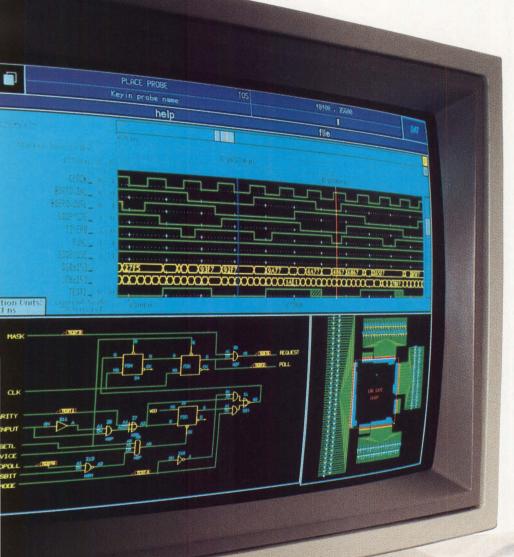

Even better, all these advanced workstations run Daisy's fieldproven Advansys software packages. Eight turnkey tool sets that meet all the demands of real world electronic design. Everything from design entry to digital and analog simulation, IC and PCB layout, fault simulation and test tools.

But with Advansys, your capabilities don't stop at your desktop. Because Daisy's unique network computing concept lets you create an affordable team design environment incorporating a wide range of powerful network resources.

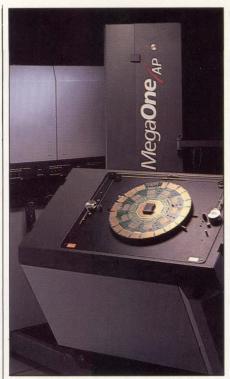

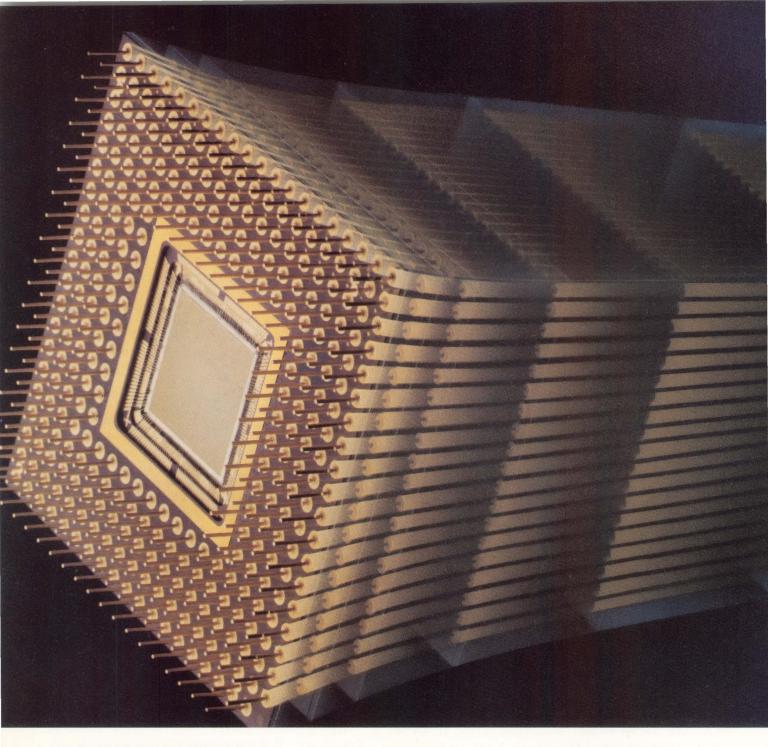

Like Daisy's MegaLOGICIAN®– the most widely used simulation accelerator

ever created. Or the brand new GigaLOGICIAN<sup>™</sup> with

up to 30 times greater performance. For complex system simulations,

there's Daisy's PMX,<sup>™</sup> the most popular physical modeling system in use today.

You can also link with network servers like the Sun-4<sup>™</sup> based XL Server for analog simulation or PCB routing. And Daisy lets you access all this power simply by opening a window on your Advansys desktop workstation. Eliminating file transfers and other time consuming bottlenecks.

To find out more about the new Advansys Series, call Daisy today at 1 (800) 556-1234, ext. 32. In California: 1 (800) 441-2345, ext. 32. We're raising the standard of excellence for electronic design.

*European Headquarters*: Paris, France (1) 45 37 00 12. *Regional Offices*: England (256) 464061; West Germany (89) 92-69060; Italy (39) 637251.

# of excellence excellent standard.

© 1988, Daisy Systems Corporation. Sun386i, NFS and Sun-4 are trademarks of Sun Macrosystems, Inc. Ethernet is a trademark of Xerox Corporation. UNIX is a trademark of Bell Laboratories.

duter Advansys

Advansvs

# jontents

# RTICLES

SystemsDesign

GaAs and RISC combine to offer the promise of

new levels of micropro-

cessor performance

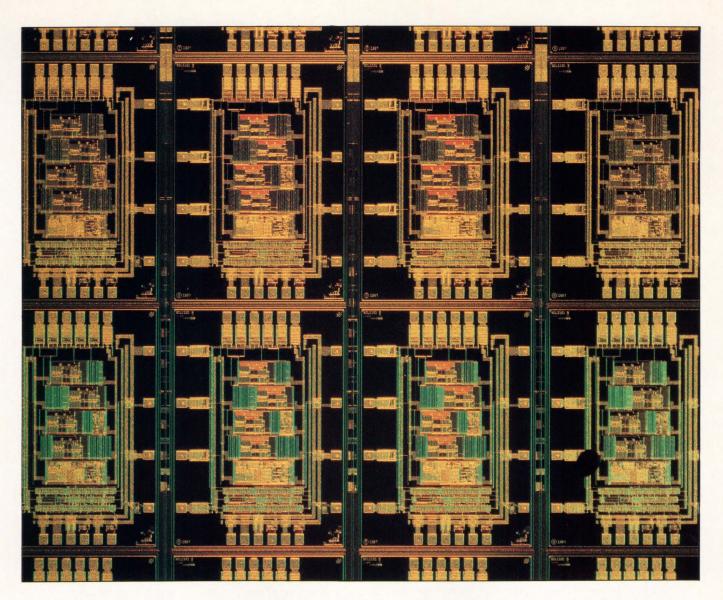

# **18** VERSATILE BROADBAND ANALOG IC

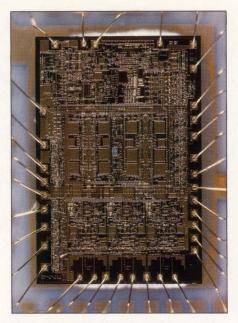

JOHN ADDIS, *Tektronix*. Inc. With more than 700 transistors, this precision analog IC is almost a complete oscilloscope plug-in on a chip.

# T OOLS

# **32 HARDWARE MODELERS**

VLSI SYSTEMS DESIGN STAFF

Our recent survey covered the hardware modeling systems from six vendors.

# TOOLS

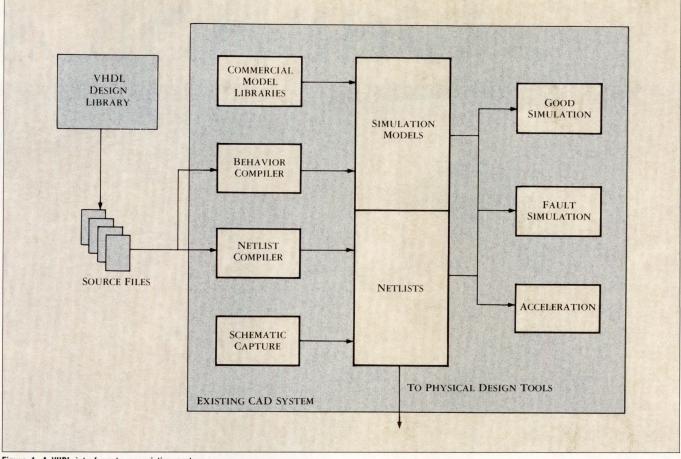

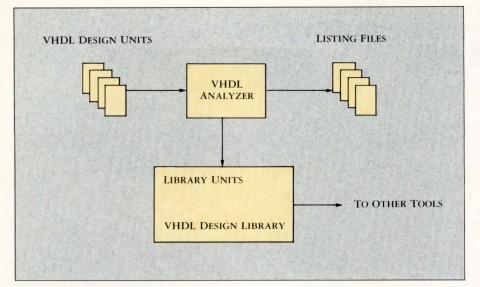

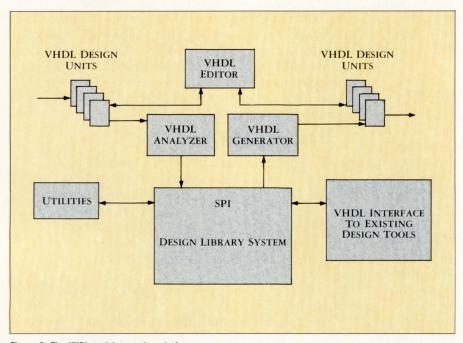

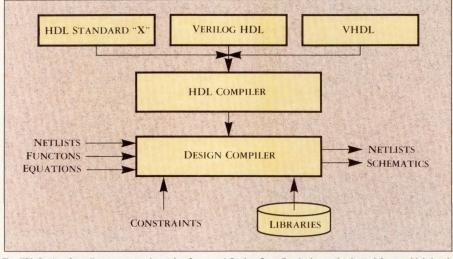

# 40 A VHDL DESIGN ENVIRONMENT

**ERICH MARSCHNER**, CAD Language Systems Inc. There is a pressing requirement to integrate VHDL with existing hardware description languages.

# METHODS

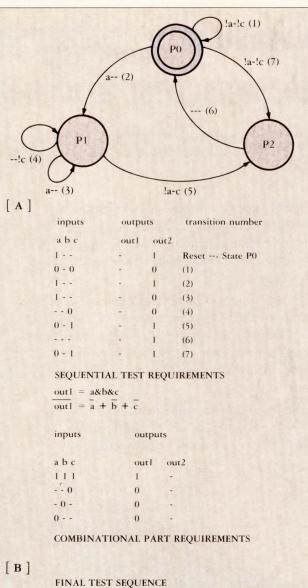

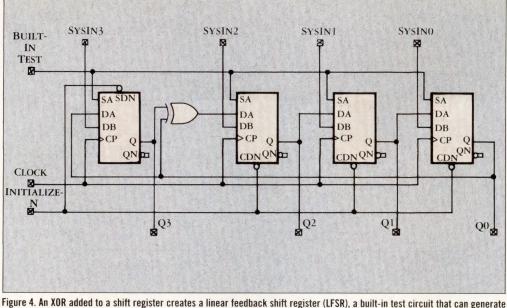

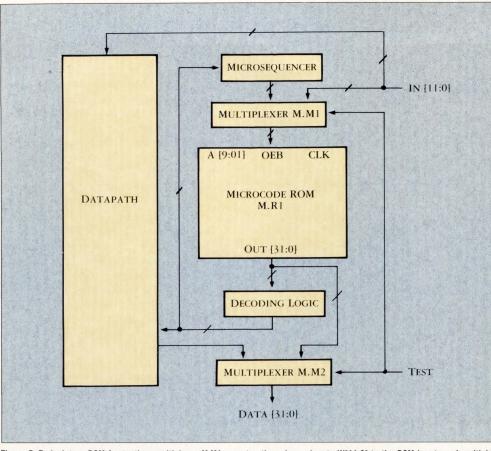

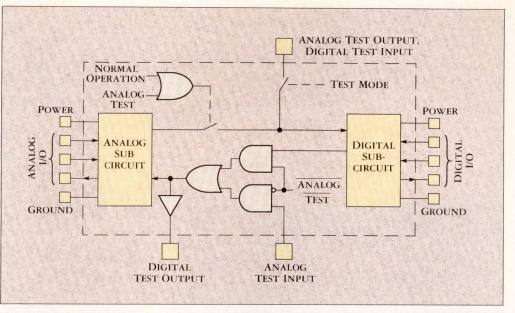

# 50 ASIC TESTING WITH HIGH FAULT COVERAGE

THERESA BUTZERIN, ARIS SAMAD, AND ERIC ARCHANBEAN, VLSI Technology Inc. This test methodology considers ASICs as an integrated collection of functional blocks.

# METHODS

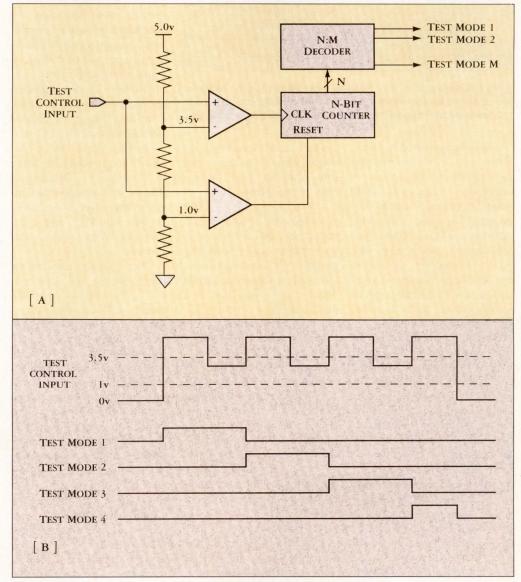

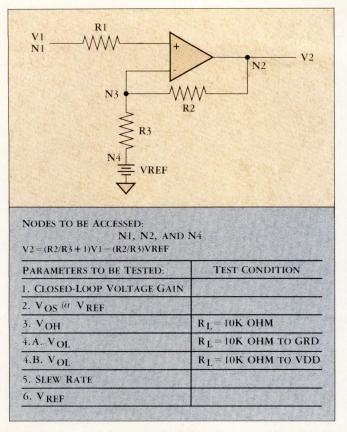

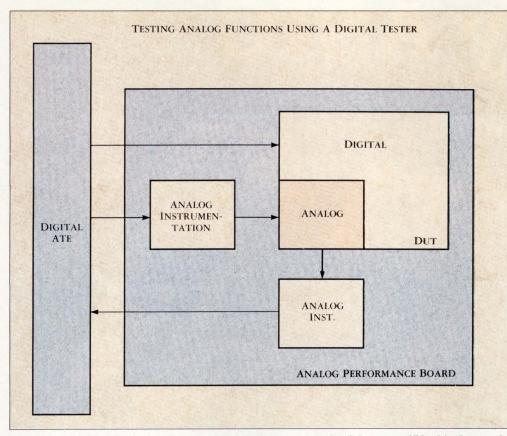

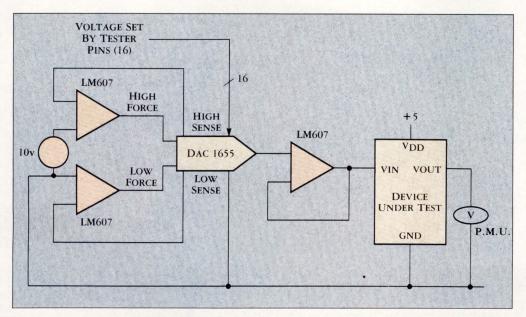

# **60** MIXED ANALOG/DIGITAL ASICS

**KEN DUBROWSKI AND THOMAS WONG**, *National Semiconductor Corp.* Adding analog circuitry to primarily digital ASICs forces the designer to adopt a new test philosophy.

# S TRUCTURES

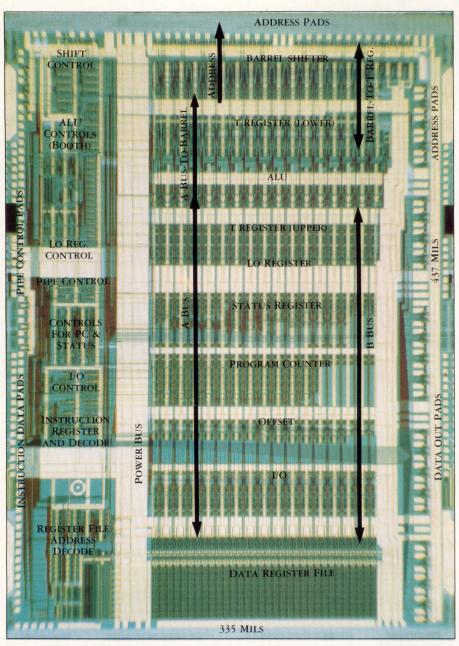

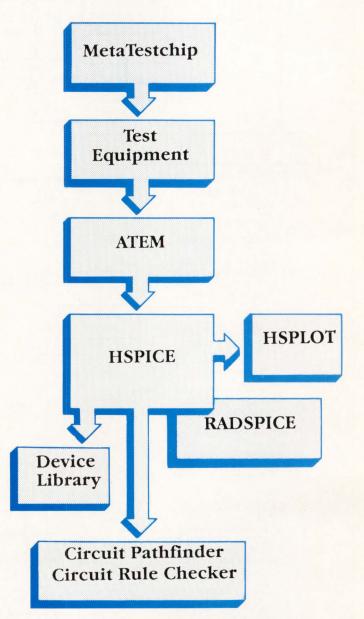

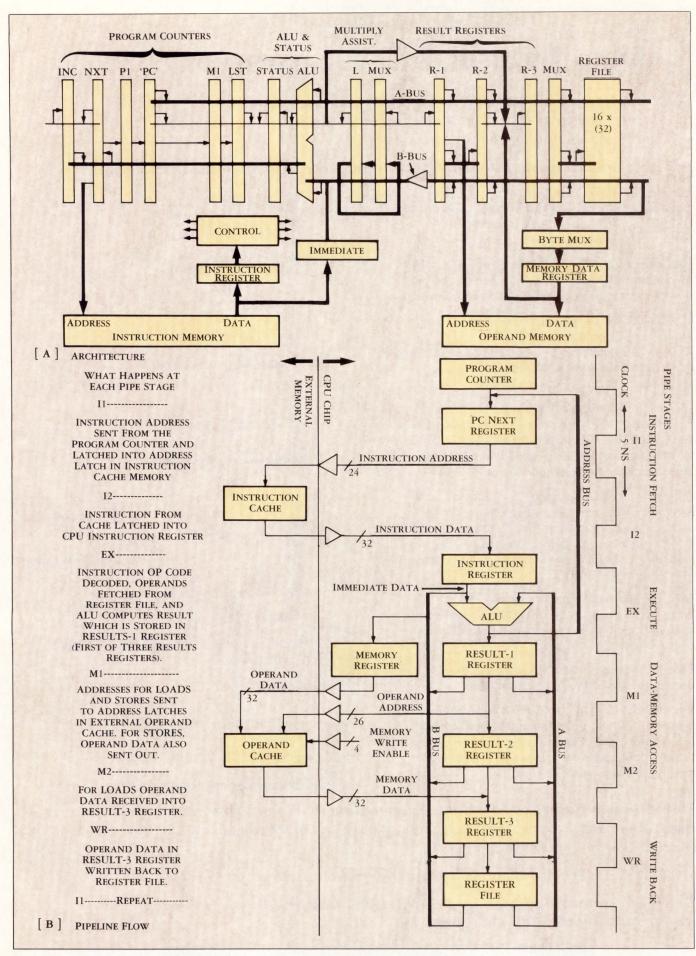

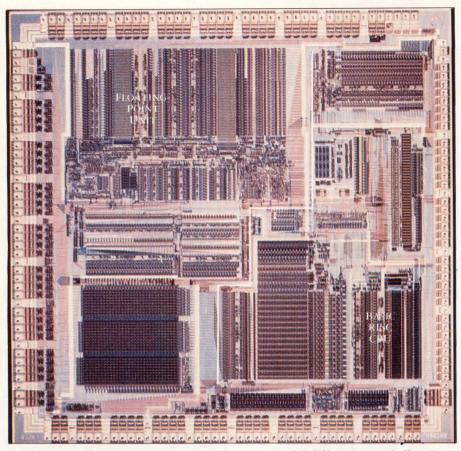

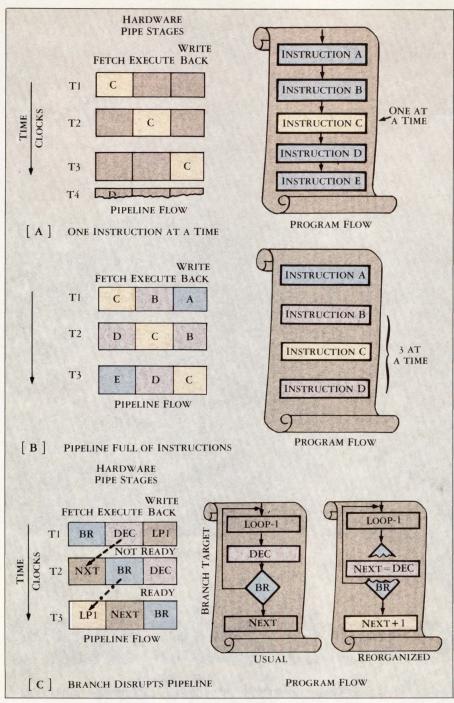

# 68 GaAs TECHNOLOGY MEETS RISC ARCHITECTURES

### BOB CUSHMAN, Senior Editor

The teaming GaAs technology with RISC architectures promises new highs in microprocessor performance.

# **C**ONFERENCE PREVIEW

# 80 INTERNATIONAL CONFERENCE ON COMPUTER DESIGN

## VLSI SYSTEMS DESIGN STAFF

This annual conference will focus on the various design, test, and VLSI technology interrelationships that exist in the CAD industry.

An ASIC test methodology uses functional block tests to build the overall chip test

11

get many worksta

# DEPARTMENTS

# **6** FROM THE EDITOR

Has the ATE industry reached a plateau?

# **8** CALENDAR

# **10** BIT STREAM

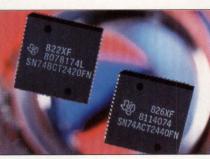

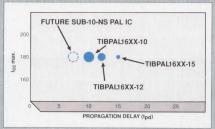

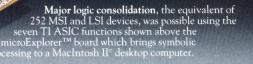

GE Solid State Heads South to Harris News PLDs Cut Power, Metastability Vitesse Multiplexer Claims Speed Record VGA Grows Up **TI Chips Build Workstations**

Versatile 700 transistor amplifier IC is a plug-in on a chip

Sun Displays Graphics Choices Full Page Display Color Palette Chip CV Measurements go DOS

# **12 PEOPLE**

The creative urge fires up David Coelho

# **14** INDUSTRY INSIGHTS

The Demanding Relationship Between ASIC Technology And ATE

# **82** PRODUCT SHOWCASE

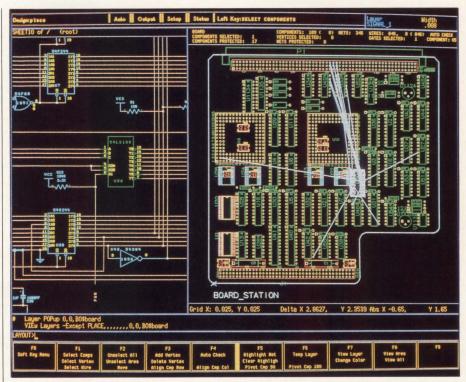

High-Level Designs Feed Logic Synthesizer Greasing the Path to Approved PCB Layouts

# **88** AD INDEX

COVER ILLUSTRATION BY JAVIER ROMERO

### A CMP Publication

EDITORIAL DIRECTOR Robert W. Henkel **EDITOR-IN-CHIEF** Roland C. Wittenberg MANAGING EDITOR Mike Robinson SENIOR EDITOR Bob Cushman SOLID STATE EDITOR Roderic Beresford WESTERN REGIONAL EDITOR David Smith DIRECTORIES EDITOR Michelle A. Losquadro **TECHNICAL ADVISERS** John A. Darringer Jeffrey T. Deutsch Edward J. McCluskey Alan F. Podell Daniel G. Schweikert Susan L. Taylor **EDITORIAL PRODUCTION** Patricia L. Gaynor, Sr. Production Editor Deborah Porretto, Ass't Production Editor EDITORIAL ART Sharon Anderson, Art Director Marie D'Ippolito, Design Director MANUFACTURING Marie Myers, Production Manager James Pizzo, Production Supervisor Jane Mahoney, Asst. Production Supervisor Vance Hicks, Coordinator

> PUBLISHER Norm Rosen

VLSI SYSTEMS DESIGN (ISSN 0279-2834) is published monthly with an extra issue in May by CMP Publications, Inc., 600 Community Drive, Manhasser, NY 11030. (516) 562-5000. VLSI SYSTEMS DESIGN is free to qualified subscribers. Subscriptions to others in the US: one year \$60.00, two years \$95.00; Canada and Mexico: one year \$90.00, two years \$165.00; Europe, Central and South America: one year \$120.00, two years \$225.00. Asia, Australia, Israel and Africa: one year \$150.00, two years \$285.00. Second-class postage paid at Manhasset, NY and additional mailing offices. POSTMASTER: Send address changes to VLSI SYSTEMS DESIGN, Box No. 2060, Manhasset, NY 11030. Copyright 1988, CMP Publications, Inc. All rights reserved.

> **CMP ELECTRONICS GROUP** Kenneth D. Cron Vice President/Group Publisher Electronic Buyers' News **Electronic Engineering Times VLSI** Systems Design

CMP PUBLICATIONS, INC. 600 Community Drive Manhasset, New York 11030 (516) 562-5000 Publisher of: onic Buyers' News, Electronic Engineering Times, VLSI Systems Design, omputer Systems News, Computer Reseller News, VARBUSINESS, UNIX Today', Information WEEK, CommunicationsWeek, CommunicationsWeek International, Business Travel News, Tour & Travel News, Long Island Monthly, HealthWeek

Michael S. Leeds, President Pearl Turner, Vice President/Treasurer Daniel H. Leeds, Vice President Lilo J. Leeds, Gerard G. Leeds Co-Chairpersons of the Board

# **Our ASIC** line-up is only half the story.

When it comes to delivery of high-quality, reliable ASICs, S-MOS wrote the book.

We did it in collaboration with our manufacturing affiliate, Seiko Epson. With 18 years of CMOS experience, Seiko Epson is one of the world's most advanced CMOS IC manufacturers.

Through Seiko Epson's high-yield manufacturing technology, we ship millions of ASIC units a month, and with a reject rate of less than .0001%. That's our quality story.

Now we've added a new chapter on design. At our advanced R&D design facility, engineers from S-MOS and Seiko Epson are developing new software to simplify circuit design, simulation and the creation of new megacells for our extensive cell library.

Of course, you can still take advantage of our established design tools because S-MOS supports such workstations as Daisy, Mentor, Calma and PC-based systems using FutureNet, OrCAD and ViewLogic.

Our proprietary LADS simulator will speed up the design process. The S-MOS engineering team will support you from concept to production.

If you are looking for an ASIC program that can make your designs best sellers, call us. (408) 922-0200.

|                                | - Spend | CTA A   |  |

|--------------------------------|---------|---------|--|

|                                |         | nine in |  |

|                                |         |         |  |

|                                | , /     |         |  |

|                                |         |         |  |

| 43                             |         |         |  |

|                                |         |         |  |

|                                |         |         |  |

|                                |         |         |  |

| 1 Janey<br>V Costs<br>V - Cost |         |         |  |

|                                |         |         |  |

|                                |         |         |  |

|                                |         |         |  |

|                                |         |         |  |

|                                |         |         |  |

|                                |         |         |  |

|                                |         |         |  |

|                                |         |         |  |

|                                |         |         |  |

|                                |         |         |  |

| CMOS Gate Arrays                                                                                                                                                                                                                                  | CMOS Standard Cells                                                                                                                                                | Compiled Cell Custom                                                                                                                                                                                                                                                                                                                                   |                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Up to 38,550 available gates<br>• SLA8000 (800 ps)*,<br>• 1.2μ drawn, 1.0μ Leff.<br>• SLA7000 (1.0 ns)*,<br>• 1.5μ drawn, 1.2μ Leff.<br>• SLA6000 (1.8 ns)*,<br>2.0μ drawn, 1.5μ Leff.<br>• SLA700B High Drive<br>Output<br>• SLA100L Low Voltage | Complexities to 16K gates**<br>• SSC1000 (1.4 ns)*,<br>1.8µ drawn, 1.4µ Leff.<br>• Fully migratable from<br>S-MOS gate arrays<br>• RAM and ROM<br>blocks available | <ul> <li>The Alternative to Full Custom</li> <li>1.8μ CMOS process</li> <li>Can utilize dissimilar<br/>cell geometries</li> <li>3-button approach<br/>to custom design</li> <li>Currently over 300<br/>fully characterized cells</li> <li>Fast 14-week<br/>implementation time</li> <li>Timing-driven TANCELL®<br/>place-and-route software</li> </ul> | Systems<br>Systems<br>Such Systems<br>S-MOS Systems, INC.<br>2460 North First Street |

"Typical propagation delay of 2-input NAND gate driving 2 internal loads with 1mm of interconnect. "Maximum gate utilization depends on amount of interconnect used.

# **CIRCLE NUMBER 1**

The time is ripe for the ATE industry to take inventory

# Has the ATE Industry Reached a Plateau?

he consensus of industry experts is that the total 1988 worldwide sales of automatic test equipment (ATE)will be about \$2.2 billion—with roughly an even split between chip and board testers. That's about seven percent of the anticipated total worldwide sales of semiconductors this year. Seven percent wouldn't be too bad if it represented the cost of testing. Unfortunately, most semiconductor device testing costs are a lot higher, and some have risen to almost half of the total manufacturing costs. That's when all the programming and test labor, fixturing, and overhead costs are added to the amortization costs of the capital invested in the test equipment.

Is the high cost of testing the reason that some industry pundits are predicting a relatively flat growth curve for the ATE industry? Probably not. It's more likely a result of the uneasiness that the electronics industry feels about the economy after the last prolonged downturn.

Instead of feeling down, this could be a great opportunity for the ATE industry to review its strategies for the future. In the past, with business booming, everybody was too busy to plan ahead. They tended to react to the electronics industry's growing testing problems, rather than work within the industry to develop new ways to avoid testing's many pitfalls.

It's time for the members of the ATE industry to get together and jointly start tackling the problems of testing today's and tomorrow's increasingly complex chips, boards, and systems. With a united front, it would be a lot easier to convince their customers of the benefits of planning—at the earliest stage in the design cycle—for standard test buses, BIST techniques, scan systems, or whatever the ATE industry recommended as a solution for slowing down the accelerating cost of testing.

This could boost the ATE industry into orbit again, and at the same time bring the cost of testing back down to Earth.

Colond Uter

ROLAND WITTENBERG EDITOR-IN-CHIEF

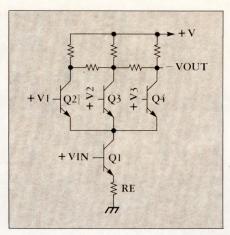

# Access to the Right Technology

Whatever your application, Raytheon can open the door to the appropriate ASIC technology. With over 14 years' experience in semicustom design, Raytheon offers you many choices— CMOS, low power ECL and digital bipolar, as well as linear arrays.

□ CMOS arrays: Raytheon's lowpower CMOS arrays to 20,440 gates have a 1.0  $\mu$ m effective channel length and rad hard capability. Both our VHSIC-approved and standard families have the lowest power consumption in the industry. The 2  $\mu$ m RL7000 array is a second source for LSI's LL7000 series. Standard cell solutions are also available. □ Low-power ECL arrays: The ECL products available from Raytheon have densities comparable to  $1.5 \mu m$  CMOS arrays and I/Os compatible with ECL, TTL (10K or 100K), and CMOS. These ECL arrays also deliver the industry's lowest power dissipation per gate. Their superior speed/power performance— <0.1pJ—provides the ASIC designer with state-of-the-art semicustom capabilities.

□ **Digital bipolar arrays:** Our many years of experience in ISL array design and production give Raytheon a solid foundation for expanding ASIC technology.

# **Raytheon offers you choices**

□ Linear arrays: Raytheon's bipolar macrocell arrays with 8, 12 or 15 gain blocks and FET input arrays with 4 or 12 gain blocks utilize precision thin-film resistors. They can be configured into a variety of analog functions, including voltage references, switches, comparators, op amps, and VFCs.

Let Raytheon open the door to a world of ASIC choices, with our proven track record in multiple ASIC technologies.

Raytheon Company Semiconductor Division 350 Ellis Street Mountain View, CA 94039-7016 (415) 966-7716

Where quality starts with fundamentals.

# C alendar

# **ESSCIRC** '88

September 21–23 University of Manchester Institute of Science and Technology Manchester, UK

The aim of the fourteenth L European Solid-State Circuits Conference is to provide a European forum for the presentation and discussion of recent advances in solid-state circuits. Topics that will be covered include MOS, bipolar, and GaAs circuits; performance limits of integrated structures, data conversion circuits, circuit design in new technologies, design for testability, integrated filters, VLSI architecture and implementation, integrated sensors/optics, high-voltage circuits, and CAD for IC design. Additional information about the conference may be obtained by contacting Dr. Peter J. Hicks, Dept. of Electrical Engineering and Electronics, University of Manchester Institute of Science and Technology (UMIST). P.O. Box 88, Manchester M60 1QD, UK. Phone: 061-236-3311 x2035.

# **ICCD '88**

October 3–5 Rye Town Hilton Port Chester, N.Y.

The annual International Conference on Computer Design is sponsored by the IEEE Computer Society and the IEEE Circuit and System Society in cooperation with the IEEE Electron Devices Society.

It will emphasize the interactions between system and memory design, logic circuit design, architecture, software, CAD, testing, physical design, and VLSI technology. The conference will feature technical sessions on topics that include test generation, advanced system interconnect and packaging, microprocessor architecture, and simulation. Additional information may be obtained by contacting Prathima Agrawal, General Chairman, AT&T Bell Laboratories, 600 Mountain Ave., Room 3D-480, Murray Hill, N.J. 07974. (201) 582-6943.

# 2nd Symposium on the Frontiers of Massively Parallel Computation

October 10–12 George Mason University Fairfax, Va.

This symposium will focus on the increasing importance of massively parallel computer systems and data parallel programming techniques. Topics that will be presented include programming languages, architectures, algorithm development, graph theory, image processing, numerical modeling, database management, interconnection networks, hierarchical structures, neural networks, and new technologies. To receive an advance program with registration information, send your name, address, and phone number to Frontiers '88 Symposium, P.O. Box 334, Greenbelt, Md. 20770.

# 5th International Electronic Manufacturing Technology Symposium

October 10–12 Lake Buena Vista, Fla.

The Fifth International - Electronic Manufacturing Technology Symposium (IEMT) is sponsored by the IEEE's Components, Hybrids and Manufacturing Technology Society. Technical presentations will cover such topics as developments in surface mounting technology equipment, automation applications in manufacturing of semiconductors and electronic products, computer integrated manufacturing applications for electronic products, developments in semiconductor materials and processing, advanced materials and processing applications for packaging interconnections and surface mount, and techniques and examples of designing for automation. For more details, contact Bill Moody, Vice Chairman for Administration, 2529 Eaton Road, Wilmington, Del. 19810. (302) 478-4143.

# 1988 INTERNATIONAL Symposium on Microelectronics

October 17–19 Washington State Convention Center Seattle, Wash.

he 1988 International Symposium on Microelectronics will feature panel discussions and educational tutorials as well as technical presentations on topics including automation, CAD/CAM, cofire tape technology, hybrid design, hybrid microcircuit technology, interconnections, reliability and failure analysis, materials, and multilayers. For more details, contact the International Society for Hybrid Microelectronics, P.O. Box 2698, Reston, Va. 22090. (703) 471-0066.

# INDUSTRY-UNIVERSITY Advanced Materials Conference

March 6–9, 1989 Embassy Suites Hotel Denver, Colo.

S ponsored by the Advanced Materials Institute, the Colorado Advanced Technology Institute, and the Materials Research Society, *Continued on page 16*

# Trying to design tomorrow's ASICs with yesterday's tools? Now there's ChipCrafter.

ChipCrafter<sup>™</sup> is the integrated design tool that takes your complex CMOS ASIC design out of the stone-age and into the future.

High-level compilers, configurable libraries, process independence, and logic synthesis make ChipCrafter designs efficient. Automatic place and route, buffer sizing, and timing analysis at your Mentor Graphics<sup>™</sup> workstation makes them easy, and as dense as hand-packed.

# FREE. ASIC Estimating Kit.

What will it take to do your design with our cutting-edge design tool? Our free ASIC Estimating Kit lets you analyze design trade-offs, including performance and cost implications, in a variety of processes. Find out how ChipCrafter and Seattle Silicon chip away at design restrictions to deliver the next generation of ASICs. Call for your free kit: 1-800-FOR-VLSI ext. 500.

3075-112th Ave N.E., Bellevue, WA 98004, (206) 828-4422. Copyright 1988, Seattle Silicon. ChipCrafter is a trademark of Seattle Silicon Corp. Mentor Graphics is a trademark of Mentor Graphics Corporation.

# Stream

### **GE Solid State Heads South to Harris**

arris Corp. (Melbourne, Fla.) and the General Electric Company have agreed on the acquisition of GE Solid State by Harris. Included in the deal are the RCA and Intersil semiconductor products as well as the original GE power and opto-electronic lines. The acquisition will add approximately \$550 million in

ation, which has annual sales of about \$300 million. The new 14,000 employee operation will come under the wing of Jon E. Cornell, Harris senior vice president and head of the Semiconductor Sector.

### **News PLDs Cut Power, Metastability**

ould Electronics (Pocatello, Ida.) has produced the first CMOS replacements for the PLS 153 and PLS 173 bipolar PLDs from Signetics. Gould's PEEL 153 and PEEL 173 use one-third as much power as the bipolar devices and are reprogrammable.

Six edge-activated programmable flip-flops in the PA-

L22IP6 store signals independently of clock signals, thereby simplifying the design of multi-clock systems and reducing the possibility of metastability-up to four-to-one in a VME bus application. Advanced Micro Devices (Sunnyvale, Calif.) calls the device an Interface Protocol Asynchronous Cell (IPAC).

### Vitesse Multiplexer Claims Speed Record

he world's fastest four-toone multiplexer chip, the VS8004, was rolled out by Vitesse Semiconductor Corp. (Camarillo, Calif.). The new IC, which perks along at 2.5 GHz, will be avilable in sample quantities this month. The VS8004 is targeted at the telecommunications industry. The chip's speed will allow its use at the STS-48 level (2.488 Gb/s) of the Synchronous Optical Network (SONET) standard.

The VS8004 is fabricated in the company's proprietary GaAs, self-aligned gate, E/D MESFET process. It has industry ECL inputs and requires only one -5.2V supply. The new IC will use a 28-pin ceramic package. A companion one-to-four demultiplexer is presently under development.

### **VGA Grows Up**

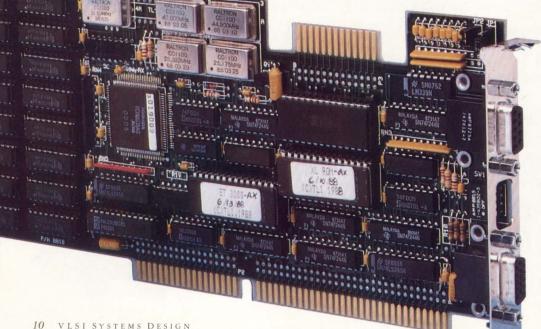

ydin Controls (Fort Washington, Penn.) announced lits Patriot VGA/1024 Graphics board aimed at IBM PC, PC/XT, and compatiblesin addition to the IBM PS/2 Model 30.

Aydin claims that the new video adapter card is 100 percent hardware-registered compatible with the new VGA graphics standard, including CGA, EGA, Hercules, and MDA graphics standards. It incorporates an 8/16-bit data bus, 2/5 CPU/CRTC access, and an extended 1,024 by 768 pixel mode. The VGA/1024, which easily drives Aydin's 20-inch VGA/20 color monitor, is list priced at \$695.

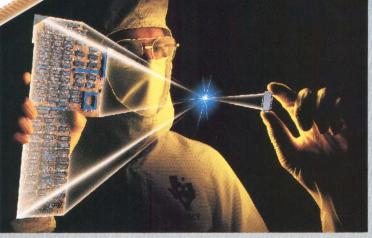

# **TI Chips Build Workstations**

exas Instruments (Dallas, Tex.) has developed highly-integrated chips for designers of engineering workstations and computers. First, a set of NuBus interface chips that reduce board area for Nu-Bus interfaces by 66 percent.

The 32-bit SN74ACT2440 interface controller and 16-bit SN74ACT2420 address/data transceiver satisfy > all requirements for master, slave and combination mas-

ter/slave interfaces in accordance with IEEE P1196 Nu-Bus specifications.at \$24 and \$13 respectively, the 2440 provides signalling protocol, including arbitration, bus locking/unlocking, and status

bits for cycle control, while the 2420 has three 16-bit ports and a comparator for back-plane slot identification.

TI also unveiled its secondgeneration graphics chip, the TMS34020 Graphics Systems Processor (GSP). It will be ob-

> ject-code compatible with the TMS34010, and operate 3 to 20 times faster thanits predecessor largely as a result of its 32-bit address/data bus. Its 512-byte instruc-

tion cache and 10-MHz clock provide 10-Mips peak burst rates for small, iterative instruction loops, and it will draw lines at 200-ns per pixel. Samples at \$500 are due in the first quarter of 1989.

### **Sun Displays Graphics Choices**

un Microsystems (Mountain View, Calif.) broadened the range of graphics options for its workstations. Most important to design engineers is the Sun VGA, an EGA/VGA compatible plug-in card for the Sun 386i workstation. The card completes the capability of the workstation to run all engineering tools developed for IBM-compatible personal computers on the 80386-based Sun platform. The \$895 card plugs into the system's PC/AT expansion bus and co-exists with the system's frame buffer. As many as four EGA/VGA applications may run at once in a window under the SunOS operating system.

For designers involved in low-end image processing, including animation and publishing, the Sun-4/110TC combines the Sun-4 SPARC microprocessor with a 24-bit, color graphics system which sells for as low as \$25,900 (diskless). The desktop system can accommodate as much as 32 Mbytes of main memory (independent of the frame buffer) and 1.3 Gbytes of disk storage; it is rated by Sun at 7-Mips and 0.8-MFlops. .....

# **Full Page Display Color Palette Chip**

A dvanced Micro Devices Inc. (Sunnyvale, Calif.) rolled out its Am81C458 CMOS Color Palette chip, the first in a family of chips that support full page and larger displays. The new chip—which is targeted at image processing, design automation, solid modeling, and animation applications—is offered as an alternate for the Brooktree Bt458 Color Palette chip. AMD's product has also been designed for use in systems that employ the AMD Am95C60 Quad Pixel Dataflow Manager.

# CV Measurements go DOS

Keithley Instruments Inc. (Cleveland, Ohio) has enhanced the capabilities of its semiconductor capacitance versus voltage measuring system by adding the capability to operate with all DOS-based computer systems. Previous models of the company's Package 82 Simultaneous CV System were only compatible with the Hewlett-Packard 9000 Series 200 and 300 programmable controllers. Included in the system are a Keithley Model 590 CV Analyzer, a Model 595 Quasistatic CV Meter, a  $\pm$  100V bias source, and calibration sources. Also included are graphics and analysis software for IBM PC/ATS, PS/2s, compatibles, and the Hewlett-Packard Series 200 and 300 controllers.

EOPLE

Helix's creator works at high levels of abstraction

HOSE who witnessed the Fourth-of-July fireworks show in San Leandro may be surprised to learn that the pyrothenic operator behind that spectacle had also created two of silicon valley's hightech companies. According to David Coelho, licensed pyrotechnic operator and enterpreneur, "I like creating things. That's the driving factor behind everything I do."

It hasn't been easy to fulfill his creative urges. David had to choose between a budding musical career and an aptitude for science and engineering. An active violinist from the age of 2, he was a soloist for his high-school and community orchestras. This selfproclaimed "pretty pragmatic person" hasn't regretted his decision to pursue engineering. Instead, he's focused his creative energy into forming companies with unusual new products.

His diligence in math and computer programming while in high school landed him at Stanford University, where, from his first year, he satisfied his creative needs by pursuing graduate-level research projects. He eventually ended up working for Professor Bill Van Cleemput and, along with two other students, created a program for routing printed circuit boards.

In his senior year (1979) of college, the four of them started Silicon Valley Reseach to create and market a CAD product. David sums up the excitement of that decision by saying, "we had nothing to lose and a lot to gain."

During the start-up phase, Da-

# The Creative Urge Fires Up David Coelho

vid drove himself to the point of becoming ill. Still, he looks back fondly on the creation his first company, saying, "It was a hell of a lot of fun". Unlike many other start-ups in the early 1980's, the company grew out of its own revenues. Luckily, at that time the CAD business was just beginning to "take off like a rocket."

The founders decided they could only be second-tier competitors against the larger, established PCB-CAD vendors. By adapting the software to gate array design, however, they could become leaders in this embryonic market. Their early customers were big companies just starting to experiment with gate arrays, such as Cray Laboratories.

The new company shared an office with a Belgian marketing firm called Leuven Industrial Software Company. It sold standardcell layout software. Because their product lines were complementary, the two companies merged to form Silvar-Lisco.

David then turned to creating a behavioral simulator based on concepts he had developed at Stanford with Dwight Hill (the two ultimately published a textbook on simulation). His effort resulted in Helix, Silvar Lisco's "architecturLIKE CREATING THINGS. THAT'S THE

DRIVING FACTOR BEHIND EVERYTHING I DO.' al-level" simulator.

The Helix approach starts with a good base language (Pascal), and enhances it with features for hardware description modeling. It also adds a user-defined value system for mixed-level simulation capability. This same philosophy was used to define VHDL.

Coelho remained with Silvar-Lisco until April 1986 as manager of simulation products. But, he felt constrained by the larger, more mature Silvar-Lisco, and he was intrigued by an opportunity for VHDL tools that Silvar-Lisco wasn't interested in. He also admits "Tm an enterpreneur at heart".

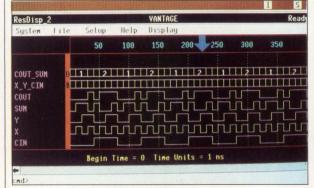

He left to start Vantage Analysis Systems, which has streamlined software development through heavy use of computeraided software engineering. Using such tools as Apollo Computer's Dialogue program generator and Metaware's TWS compiler generator, Vantage achieved "a staggering level of productivity," according to David. A team of roughly twelve people took only two years to develop 850,000 lines of code.

He keeps his creative edge by staying close to the technical aspects of Vantage, although he's now active in strategic marketing. He's also kept busy as the chairman of the Vantages' board and as the "leading advocate" for defining new products.

His off-hour interests take him further afield—from setting off fireworks displays to occasional sky diving and scuba diving excursions. It's his creative activities with computers, however, that may light up the sky for users of design automation.

-David Smith.

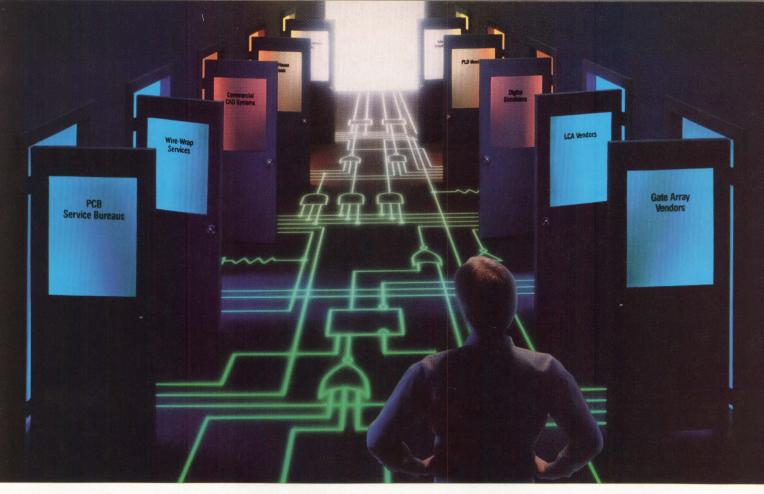

# DASH OPENS DOORS TO MORE VENDORS, SERVICES, AND SYSTEMS.

DASH<sup>™</sup> Schematic Designer from FutureNet® gives you options no other schematic capture package can. With more than one hundred DASH-Partners providing a broad range of complementary products and services, DASH's industrystandard format is accepted virtually everywhere. So you won't end up with just a schematic. When you design with DASH, you'll have more choices in technologies, CAE systems, foundries, and service bureaus. DASH is a universal front end design tool that has already opened doors for thousands of users worldwide.

# AN OPEN DOOR TO ASIC VENDORS.

DASH has won the support of dozens of ASIC vendors, including National Semiconductor, Mitsubishi, Motorola, LSI Logic, MMI, Hitachi, and Xilinx. They provide vendor-specific symbol libraries and/or accept DASH netlists for simulation so you can design

DASH runs on 80386 and 80286 machines, IBM® personal computers, and the Sun-3 Series.

ASICs in DASH. Whatever your choice of vendor or technology— PLDs, LCAs, gate arrays, or other semicustom devices—DASH is the schematic entry software of choice.

# AN OPEN DOOR TO CAD SYSTEMS.

Translators to a wide variety of PCB and simulation systems are available from FutureNet and our DASH-Partners. DASH is the only design entry tool that can be used throughout your company, in multiple CAD environments, regardless of the mix of vendors.

# AN OPEN DOOR TO SERVICE BUREAUS.

When you don't want to do it all yourself, DASH gives you access to outside services. Service bureaus throughout the world accept the DASH netlist as standard input for their design, wire wrap, and PCB manufacturing services.

**FREE DASH-PARTNERS DISKETTE.** Take the first step. Call us today for your free copy of the DASH-Partners

diskette of vendors, services, and systems that support DASH. You're on the threshold of new design freedom.

1-800-247-5700 Ext. 265

© 1988 Data I/O Corporation

**CIRCLE NUMBER 5**

N D U S T R Y I N S I G H T S

**Relationship Between ASIC**

The Demanding

**Technology And ATE**

RONALD H. LECKE, MEGATEST CORP., SAN JOSE, CALIF.

The lack of ASIC pinout standards can be costly

SIC market trends have a tremendous impact on the requirements semiconductor manufacturers place on automatic test equipment (ATE). Many of these trends are obvious to most ASIC users, especially technology-dependent trends such as greater IC complexity, density, and pin count. But, commercial aspects of ASIC technology that drive ATE technology may not be apparent to ASIC users-pressures for faster prototype delivery, lower non-recurring engineering charges, and smaller unit volumes.

With ASICs, IC users and manufacturers can no longer treat chips on a part type basis, but must instead look at the whole design-through-shipment process as the product. This process is characterized by many different part types, each with relatively small volume compared to singletype, standard-part processing. To handle the lower volumes, some leading suppliers integate multiple part types on a single wafer using direct write-on-wafer photolithography technology. Having multiple IC designs on each wafer entails lower risk than devoting an entire low-volume run to a single wafer because, with the former approach, one bad wafer does not obliterate an entire run for a design. Unfortunately, it makes wafer-probe testing more complex.

The integration of multiple designs, coupled with higher design density, requires each tester to hold enormous numbers of test patterns. The tests are made even

# more complex because ASIC wafers depend heavily on wafer monitor structures; the low production volumes don't provide enough feedback on yield parameters. More test monitors are needed per ASIC wafer, and more analysis must be done for each wafer.

Because of the number of designs, test engineers can't pay as much attention to each test program. Test responsibility is placed on the end user or designer. Application of the tests, however, still rests with the ASIC supliers, who need to maintain maximum throughput as well as high test quality. Consequently they need to use larger, more powerful and regretably more expensive VLSI test systems. However, most major players in the ASIC business recognize that total unit test cost is more important than minimum capital spending.

There are alternatives to large ATE systems for this problem, namely verification systems and low-cost modular ATE. These approaches, however, compromise other testing requirements, such as overall timing accuracy, flexibility in producing waveforms, and parametric accuracy. ASIC testers must work over a wide WE MUST LOOK AT THE WHOLE DESIGN-THROUGH-

SHIPMENT PROCESS AS THE PRODUCT.' range of operating speeds and design complexity, and they must be able to satisfy the highest common denominator. The ASIC industry has not traditionally taken the approach of fully testing devices; for example, many suppliers still use only functional test vectors, and they apply them at low frequencies (typically 1 MHz). Industry-wide drives to higher quality and lower PPM levels, however, make thorough testing, at the intended operating frequency, an eventuality.

Another important, but overlooked, ASIC testing problem is the cost of tooling and fixturing. These costs can be very high, especially for cell-based ICs which, unlike gate arrays, have no standard I/O- and power-pad "footprints". Each cell-based chip (including compiled designs) has not only its own test program but also its own probe card for wafer-level test. As ASIC pin counts rise, the cost and manufacturing cycle of the probe cards increases as well, directly impacting prototype cost and delivery cycles.

In addition, package tooling can raise the cost and length of testing. Although some manufacturers have automated the process of fitting die into packages and generating bonding diagrams, few have considered the impact of arbitrary power-pin placement on testing. VLSI test systems can quickly adapt to new I/O pin placement, but test engineers must manually allocate and decouple power connections either on the performance board or at the handler contactor set.

These tooling problems could be alleviated if ASIC manufacturers would trade-off silicon efficien-

# Simple as... pushing a button

| DESIGN<br>ENGINEER | ASIC   |  |

|--------------------|--------|--|

| CSPICE             | PLD    |  |

| HILO               | LAYOUT |  |

Intergraph makes ASIC design easy. We provide a complete solution for ASIC development to help you create optimized and verified electronic circuits.

From your workstation, simply push a button to access...

- □ hierarchical schematic design

- □ online electrical rules checking

- □ leading ASIC model libraries

- user-generated custom libraries

- □ high-speed logic and fault simulation

Resulting verified netlists can be used with a wide selection of physical design tools that Intergraph offers for standard cell, gate array, programmable gate array, and programmable logic device designs.

The ASIC Engineer Series offers schematic symbols, simulation models, netlisters, back-annotation utilities, and simulation vector conversion utilities.

Our 5-MIPS CLIPPER workstations and servers give you the performance to produce advanced ASIC designs with lower part cost and greater architectural flexibility – to get your products to market faster.

Integrating CAE solutions... Call Intergraph...800-826-3515 or 205-772-2700. CAE really is as simple as pushing a button.

# **CIRCLE NUMBER 6**

Intergraph and CLIPPER are registered trademarks of Intergraph Corporation.

# DESKTOP GATE ARRAY DESIGN

Like desktop publishing is revolutionizing publishing, we are revolutionizing gate array design. Our *GATEAID PLUS/PC* gate array design software:

- runs on your PC/XT/AT/386

- matches the power of

- workstation tools, and

- costs \$945.

And unlike the logic supertankers of other suppliers, our gate arrays are *efficient building blocks* tailored for various functions such as:

- O PLD replacement

- RAM and logic integration

- Bus logic integration, etc.

To order GATEAID PLUS/PC, or for more information on it or on our building block gate arrays, mail coupon below. Or call 1-800-338-GATE.

| Mail to: | Matra Design Semiconductor<br>2895 Northwestern Pkwy.<br>Santa Clara, CA 95051                                 |

|----------|----------------------------------------------------------------------------------------------------------------|

| PLU      | ke to order a copy of GATEAID<br>JS/PC on a 30-day trial basis. Bill me.<br>Jude business card or letterhead). |

| Sen      | d me information.                                                                                              |

| Name     |                                                                                                                |

| Signati  | ure (Required)                                                                                                 |

| Phone    |                                                                                                                |

| Compa    | Iny                                                                                                            |

| Addres   | s                                                                                                              |

| DES      | SIGN SEMICONDUCIOR                                                                                             |

| 1-8      | 00-338-GATE                                                                                                    |

|          |                                                                                                                |

**CIRCLE NUMBER 3**

Wafer probing and package fixturing play a major part in total ASIC costs.

cy for *test-fixturing efficiency*. Most suppliers have extensive designfor-testability rules relating to the quality of circuit functionality and performance, but how many have testability design rules controlling the die footprint and packaging parameters? It may be worth sacrificing 10 to 20 percent of the silicon area to gain some footprint standardization to minimize tooling costs for probing, bonding and packaged-IC testing.

ASIC devices are pushing tester technology to satisfy their requirements for more flexibility and lower manufacturing cost. These requirements can be met through close cooperation between ASIC manufacturers and test equipment manufacturers. After all, it is in the best interest of designers of test systems to help the ASIC manufacturer who is not only a customer, but also a supplier of components!

RONALD H. LECKE is Vice President of Engineering for VLSI Test Systems at Megatest Corporation, San Jose, Calif. Prior to joining Megatest, be worked at Signetics Corporation in Sunnyvale, CA, serving as CMOS Product Engineering Manager, Quality and Reliability Manager, and Product Engineering and Test Operations Manager for the Bipolar LSI & Semicustom Division. He had transfered to California from Signetics' facility in Linlithgow, Scotland, where he worked in product engineering, test, yield improvement and customer applications. He received a BS in Electrical and Electronic Engineering from Heriot Watt University in Edinburgh.

### **CALENDAR**

### Continued from page 8

this conference has been designed to review current materials research that is of common interest to academia, industry, and government. Topics will include interfacial phenomena in electronic and nonelectronic materials, metal and ceramic matrix composites, high-speed electronic devices, and superconductivity. Authors should submit, by November 1, 1988, a one-page abstract to Dr. Jerome G. Morse, Director, Advanced Materials Institute, Colorado School of Mines, Golden, Colo. 80401. (303) 273-3852.

# PARLE '89

June 12–16, 1989 Eindhoven, The Netherlands

PARLE '89, the second conference on Parallel Architectures and Languages Europe, is intended to serve as a meeting place for researchers in the fields of theory, design, and applications of parallel computer systems. Papers are solicited on such topics as semantics and models for parallelism; programming environments; memory management, fault tolerance, and real-time aspects; dedicated processors for AI; debugging and monitoring tools; and simulation. By October 21, 1988, interested authors are invited to submit 5 copies of a full paper that does not exceed 6,000 words to Dr. M. Rem, Eindhoven University of Technology, P.O. Box 513, 5600 MB Eindhoven, The Netherlands.

# 9TH INTERNATIONAL Symposium on Computer Hardware Description Languages

June 19–21, 1989 Washington, D.C.

The goal of CHDL '89 is to bring together, from both industry and academia, the leading researchers and the best work in description languages. Papers are invited on such topics as optimization techniques, silicon compilation, EDIF, VHDL, design for verification, high-level simulation, advanced software simulation, graphic tools, databases, and industry methodologies. By October 31, 1988, interested authors should submit five copies of a manuscript, not exceeding 20 pages, to Professor Dr. Franz J. Ramming, Program Chairman, Universitat Paderborn, Warburger Str. 100, D-4790 Paderborn, Federal Republic of Germany.

Z I L 0 G

# Big 8-bit performance. Tiny 18-pin package. Miniscule price.

Introducing the smallest Z8 microcontroller yet, the high-performance Micro8" (Z86C08). Just imagine what you'll be able to do with all this capability, packed into a DRAM-sized chip. For what amounts to pocket change.

# The Z8 Family: Still setting the standards.

From the first, the Z8 microcomputer has been one of the industry's finest examples of simplicity and elegance. The most sophisticated microcontroller family continues to grow.

Today, there is 28 support for every phase of your system development, from prototying to full production. Along with devices you know and trust, there are new parts with an increasing number of options and features for your design. Recently, the Z8 is found in such diverse uses as fans, puppy door controllers, induction bot plates, and high-performance bard

disk controllers, printers, and local area networks (LAN). Since demand for Z8 products, and their importance to the industry continues to increase, we are developing new members of the Family. The Super8" is now clearly established as the high-end Z8, and the Micro8 can be expected to have as much an impact on low-end Z8 applications. Among the other new Z8 Family members you should be keeping an eye on are:

► 286C91 High-performance CMOS ROMless microcontroller

- Low cost 28-pin CMOS, has 22 1/0 lines and 4K bytes ► Z86C10 of on-board ROM

- ► Z86C21 8K ROM Z8, has 32 1/0 lines, 2 levels of security

# Mighty strong performance

First of all, the Micro8 features the high-end Z8 architecture. Then there's 128 bytes of RAM, two counter/timers, two single-supply analog comparators, and low power consumption. Not to mention all the advantages of Superintegration<sup>™</sup> and CMOS technology.

# Mighty powerful protection

The Micro8 may be tiny, but it's as bullet-proof as they come. You get brown-out protect and a watchdog timer, for instance. You get an operating range of 3-5.5V. And you get CMOS I/O levels and hysteresis for noise protection.

### Mighty impressive bit bang for your buck

The Micro8 gives everything you want in an 8-bit microcontroller. In the smallest package you've ever seen. For about a buck and a half. Plus you're working with the familiar software and proven performance of the Z8 Family. And it's all backed by Zilog's solid reputation for quality and reliability.

You really ought to see for yourself just what the mighty Micro8 can mean to your design application. Why wait? Contact your local Zilog sales office or your authorized distributor today. Zilog, Inc., 210 Hacienda Avenue, Campbell, CA 95008, (408) 370-8000.

# Right product. Right price. Right away. Zil

ZILOG SALES OFFICES: CA (408) 370-8120, (714) 838-7800, (818) 707-2160, CO (303) 494-2905, FL (813) 585-2533, GA (404) 923-8500, IL (312) 885-8080, MA (617) 273-4222, MN (612) 831-7611, NJ (201) 288-737, OH (216) 447-1480, PA (215) 653-0230, TX (214) 231-9090, CANADA Toronto (416) 673-0634, ENGLAND Maldenhead (44) (628) 39200, WEST GERMANY Munich (49) (89) 612-6046, JAPAN Tokyo (81) (3) 587-0528, HONG KONG Kowloon (852) (3) 723-8979. Taiwan (886) (2) 731-2420, U.S. AND CANADA DISTRIBUTORS: Anthem Electric, Bell Indus, Hall Mark Elec., JAN Devices, Inc., Lionex Corp., Schweber Elec., Western Microtech. CANADA Future Elec., SEMAD.

# **CIRCLE NUMBER 8**

# VERSATILE Broadband Analog IC

JOHN ADDIS, TEKTRONIX, INC., BEAVERTON, ORE.

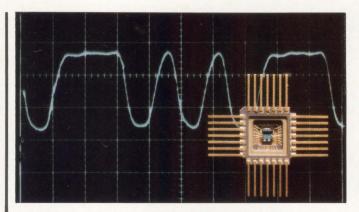

high-speed bipolar analog integrated circuit is the heart of four plug-in amplifiers used in the Tektronix 11000 series oscilloscopes. This IC, internally designated the M377, forms almost the entire signal path in three of the plugins, and a majority of the fourth. With over 700 transistors, it is almost a "plug-in on a chip". A microprocessor and custom logic IC are used to ASIC IS A control the M377 and add a sophisticated calibration routine.

The M377 IC features: gain switching over a 50:1 range in a 1,2,5 sequence of six discrete steps; a continuously variable gain that is proportional to a dc input voltage; multichannel operation with other M377s; three identical outputs that can be independently inverted or

enabled in less than 200 ns; a bandwidth of 800 MHz with 420 ps risetime (for gains between 0.4 and 12) and a bandwidth of 320 MHz at gain of 60; a four-pole, 100 MHz bandwidth limiting filter; a four-pole 20 MHz bandwidth limiting filter; a high common mode rejection differential input configuration; and overdrive recovery to within 0.04 percent in 6 ns.

To dissipate its three watts, the 4.32mm (170 mils) X 2.92mm (115 mils) plug-in amplifier chip is mounted on a 1.22 cm (0.480 inch) square thin film ceramic substrate. No bypass capacitors, resistors, or inductors are required, just a conductor pattern and the monolithic IC on a leadless substrate. The entire amplifier is connected to an etched circuit board using the company's proprietary patented elastomeric connector.

## ■ A PHILOSOPHY CHANGE

The M377's circuitry represents a major departure from earlier wideband oscilloscope amplifiers. Changing industry needs, both for increased precision at high frequencies and for lower assembly costs, dictated a fresh approach. The 1 GHz bandwidth of Tektronix's 7104 oscilloscope (introduced in 1979) was found to be wide enough to satisfy all but a few high frequency needs. However, there were increased requirements for high precision over these bandwidths. The advent of 10- to 16-bit analog to digital and digital to analog converters as well as digital signal processors was part of the driving force behind high-precision, highfrequency oscilloscopes.

The cost of the assembly labor for com-

PLUG-IN **ON A CHIP**

plex instruments such as oscilloscopes was rapidly becoming too high. Designing more of the complex circuitry into ASICs resulted in decreased labor costs for digital circuit board assemblies, and there was no reason that the same philosophy shouldn't work for analog circuits as well. Board space was another factor which dictated an increased level of integration. A fourchannel plug-in was required, but there wasn't enough room on the plug-in circuit board to accept four channels of conventional analog circuitry.

The labor costs for calibration and adjustment were also expensive. This dictated circuit designs that reduced the number of manual adjustments. The entire 11000 oscilloscope calibration is automatic. Only one manual adjustment per channel exists in most of the plug-ins that use

# 17 MIPS. 210K transistors. And one chance to get it right.

a languard

# To build the world's highest performance RISC microprocessor, AMD turned to Mentor Graphics IC layout tools.

It was a bold, ambitious project: build the fastest 32-bit  $\mu$ P in existence. One delivering a 5X to 7X performance improvement over existing 32-bit processors.

So Advanced Micro Devices turned to Mentor Graphics' Chip Station® to get the Am 29000 into silicon in a single iteration. Why? Because Chip Station provided the most advanced capabilities available, yet could also emulate AMD's existing tools.

# Sharpen your competitive edge.

Look inside Chip Station and you'll find features like advanced traversal capabilities that make moves through the hierarchy as simple as point and click. And polygon-based editing that prevents problems like self-intersecting data. Also, programmable stroke recognition, which immediately converts cursor movements into commands. And

now, the industry's fastest VLSI color plotting solution.

# Complete compatibility with your existing environment.

Chip Station's programmable user interface shortens your learning curve by emulating the commands of your current system. At the same time, Mentor Graphics helps you adapt to the rich feature set of Chip Station and graduate to a truly advanced IC layout methodology.

Chip Station also brings you both the capacity and performance to deal with the coming generation of ULSI designs. Structured

1 ATTAC

DRACULA II is a trademark of Cadence

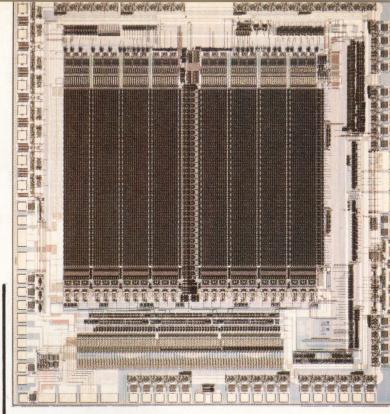

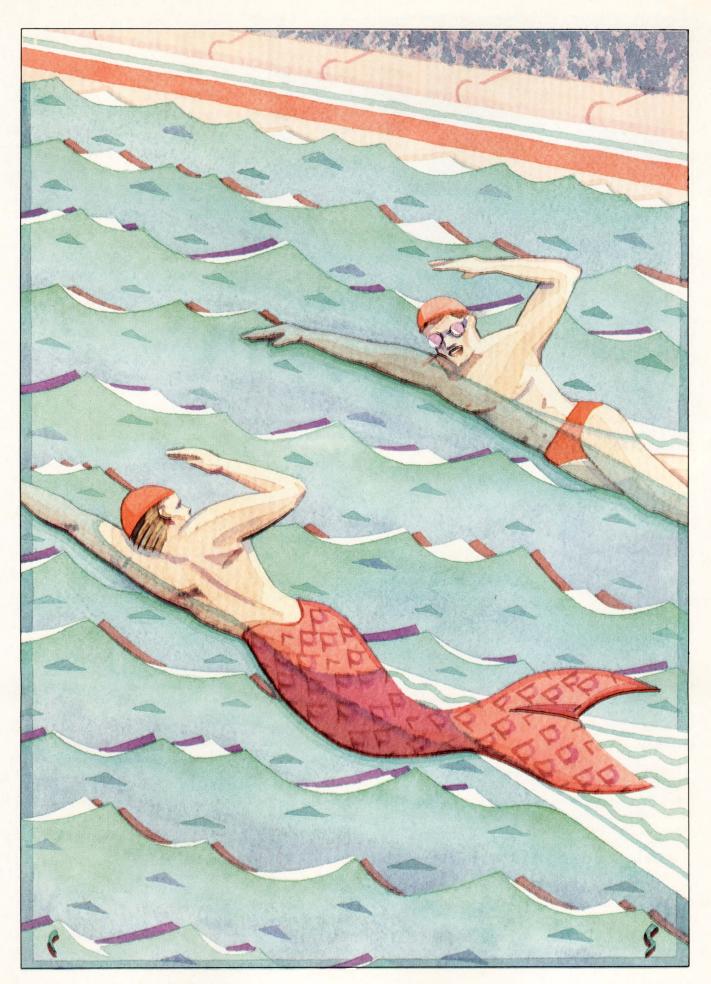

AMD's new RISC-based, 32-bit Am 29000 microprocessor operates at a 25 MHz clock rate with a 40 ns instruction cycle time. It can bit a peak execution rate of 25 MIPS, with a sustained performance of 17 MIPS. Because of its exceptional speed and price-performance ratio, the Am 29000 can be used in a wide range of applications—from embedded controller designs to engineering workstations.

Chip Design lets you represent cells symbolically so the organization and management of large designs is greatly simplified. And REMEDI<sup>™</sup> expands DRACULA II<sup>™</sup> LVS checks to include graphic correlation of errors in both schematics and layouts.

# The emerging standard.

Mentor Graphics' IC design and layout tools have already earned a solid reputation for productivity on large, complex VLSI projects. As a result, we're the world's fastest growing supplier of IC layout systems.

It's all part of a vision unique to Mentor Graphics, the leader in electronic design automation. Let us show you where this vision can take you.

Call us toll-free for an overview brochure and the number of your nearest sales office.

1-800-547-7390 (in Oregon call 284-7357).

Yourideas. Our experience.

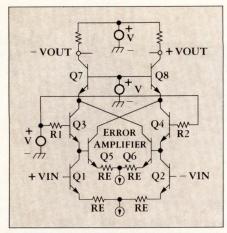

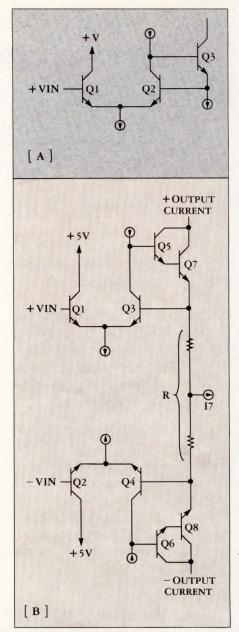

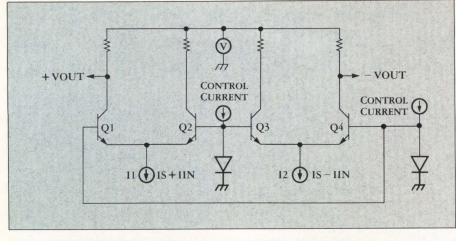

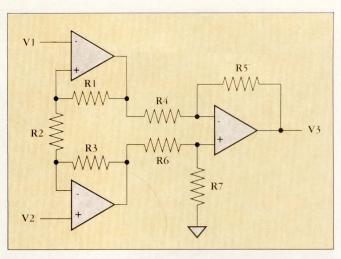

Figure 1. The cascomp (compensated cascode) amplifier was one of the first attempts at broadband precision amplification.

the M377 IC, and that adjustment is for transient response. Even the frequency compensation for the high impedance input attenuators is factory-adjusted by laser trimming under machine control.

### ■ THE CASCOMP AMPLIFIER

Greater precision and fewer adjustments are not necessarily mutually exclusive goals. Indeed, they are compatible goals if the right circuit design choices are made.

The Tektronix 2465 oscilloscope was the first instrument to use this approach. It uses a circuit we call the cascomp (compensated cascode) shown in Figure 1. If the emitter-coupled differential pair is a first generation amplifier, then the cascomp can be considered a second generation amplifier. It is the first attempt at broadband precision amplification, and an improvement on the simple differential pair.

The cascomp senses the error voltage due to the non-linear (logarithmic) junction characteristics and subtracts the error from the final output. The cascomp does not sense the actual error voltage in Q1 and Q2, but instead senses the nearly identical error voltage generated by Q3 and Q4. Q7 and Q8 are added to provide good error amplifier bandwidth. For the same quiescent current, the cascomp demonstrates increased linearity over the uncompensated circuit.

But there is another source of error plaguing the first generation dc-coupled linear amplifier: thermal effects commonly called "thermals" or "thermal tails". These effects occur because the each transistor's operating point and hence power dissipation changes with signal. The power dissipation change causes the transistor's temperature to change, which in turn changes the base-emitter voltage. Since the base-emitter voltage is in series with the input signal, there is a thermally induced error in the amplifier's transient response. The effect can be substantial (5 to 7 percent per stage in extreme cases of very wideband and therefore power hungry amplifiers), and it is especially troublesome because it results in the multiple time constants characteristic of heat flow through silicon. Discrete amplifiers usually have "thermal balance" resistors (between Q1 and Q3, and Q2 and Q4) which nearly eliminate thermals, but integrated circuit amplifiers cannot provide the large capacitors necessary for bypassing these thermal balance resistors. Fortunately, the effects are usually linear and can be compensated. However, first generation IC amplifiers require a large number of manual adjustments to compensate for signalrelated thermal effects. For example, a 7104 with two single channel plug-ins required 32 manual adjustments to correct for thermals.

If the operating points of Q3 and Q4 are chosen carefully, the cascomp cancels thermal errors as well as non-linear errors. By eliminating the need for manual adjustments, the parts costs, board area, and labor costs associated with calibration are all reduced. The calibration labor costs are non-trivial because the adjustments for thermals are among the most difficult and frustrating to make.

The patented (Pat Quinn of Tektronix) cascomp is successfully used in many of the company's oscilloscopes today.

While an improvement over a simple differential pair, the cascomp has some limitations. First, very high gain is not possible from a single stage without loss of all its advantages. Since the error amplifier and the main amplifier have the same gain, non-linearities in the error amplifier become appreciable at high gain (at very high gain, the error amplifier is not able to cancel non-linearities very predictably).

Second of all, the stack of three transistor pairs in the signal path causes the gain to be 1.5 times as sensitive to alpha losses as the standard cascode. As temperature increases, the gain increases as (alpha)<sup>3</sup>. This amounts to about 225ppm/°C in the cascomp for a typical beta of 80 versus 150ppm/°C for a standard cascode. The standard cascode also has a counteracting temperature dependent gain term in the emitter circuit due to the dynamic emitter resistance which the cascomp has eliminated. This term is about -185ppm/°C for an emitter current of 20mA/side at a junction temperature of 60°C and using a 40 ohm emitter resistor. To compensate for alpha effects, two resistors, R1 and R2, may be added. However, it is usually not possible to make R1 and R2 large enough to

Figure 2. The basic amplifier can be considered as a compound transistor (a), however, changing the output transistor to a Darlington (b) improves the gain stability.

compensate for the alpha loss without creating too much high frequency peaking. Thus the standard cascode may have a lower gain temperature coefficient than a cascomp circuit.

Third, the cascomp has a disadvantage to the IC designer in that the three stacked devices use up more of the available supply voltage. In circuits which require level shifting back down toward the negative supply, the voltage shift required is greater with the cascomp than the cascode.

A fourth disadvantage is in the cascomp's ability to handle overdrive signals. Since the error generating devices (Q3 and Q4) do not see the full input signal, the error correction circuitry and the main amplifier generally have different thermal histories in overdrive. However, with some extra circuitry, thermals resulting from overdriving the cascomp can be made about as good as a thermally balanced differential pair.

# ■ THE BASIC AMPLIFIER

The M377 represents a third generation broadband amplifier design. The basic amplifier is shown in Figure 2a. This circuit—whose original design goes back at least to the mid-seventies and is a variation of the LM102 operational amplifier—is a very versatile feedback amplifier. It can be viewed (somewhat imperfectly) as a compound transistor in which a differential pair, Q1 and Q2, compares an input signal with the emitter voltage of an output device, Q3. The compound device has increased gm and beta over Q3 alone when operating at the same current.

When viewed as a compound transistor, it is obvious that the output can be taken from either the emitter or collector of Q3. The analogy with a compound transistor falls apart because the alpha of Q3 is not helped by Q1 and Q2. This flaw can be overcome in several ways. For example, the collector of Q1 could be connected to the emitter of Q3. This not only increases the compound transistor's alpha, but it bootstraps Q1's collector. However, the operating point of Q1 will compromise its F<sub>t</sub>. Additionally, at very high frequencies this design has a negative input impedance, which is potentially unstable. The best technique for high frequency designs is to change Q3 into a Darlington as in Figure 2b and accept the lost bootstrapping advantages as the price for stability and a 1 GHz bandwidth.

When two such voltage followers are connected together as in Figure 2b, the configuration is that of an instrumentation amplifier—the basic amplifier stage used in the M377.

A block diagram of the M377 would show only two stages of gain. In between are a level shift, a Gilbert multiplier variable gain control, and a choice of two bandwidth limiting filters or a full bandwidth path. The input stage and the three identical output stages are all instrumentation amplifiers whose inputs are the bases of Q1 and Q2 and whose outputs are the darlington collectors (Figure 2b). Gain for these stages is set by the resistance R between mirror-imaged voltage followers. To a very high degree of precision, the signal current output is equal to the voltage input between the Q1 and Q2 bases divided by R.

## ELECTRONIC GAIN SWITCHING

The ability to change gain over a wide

Figure 3. Using a passive constant resistance network provides gain changes with minimum effect on bandwidth.

range in precision steps is important for two reasons in oscilloscope preamplifiers. First, it allows the input attenuator to be simplified to just three settings, unity, ten times attenuation, and one hundred times attenuation. This is significant because the input attenuator, which is built with electro-mechanical relays, is inherently expensive and less reliable than welldesigned solid state components. The fewer the components, the more reliable the attenuator will be. Second, the gain changing technique employed should use the best trade-off between gain and noise. For example, if the amplifier needs a maximum sensitivity of 1 mV per division, use of a passive attenuator before the amplifier as the only means of altering the amplification would result in the high gain amplifier's full noise level being displayed at all sensitives. Use of a passive attenuator after amplification increases the dynamic range requirements for the preattenuator amplification. Even at 10:1 attenuation, the cost of increased dynamic range can be severe.

There are several ways of changing the amount of amplification in an IC. One method is to use a passive constant resistance network as shown in Figure 3. The current in Q1's collector will result in a different Vout depending upon whether Q2, Q3, or Q4 is conducting. This method can have very broad bandwidth and has the advantage of minimal change in bandwidth as a function of the attenuations selected. Used alone, it has the disadvantage of requiring the amplifier preceding it to handle the full dynamic range of the lowest gain setting. The input amplifier cannot simultaneously have high gain and wide dynamic range without prohibitive power dissipation, so it must have low gain to handle the largest expected signals. This requires the post attenuator amplifiers to operate at high gain with correspondingly high output noise.

Some means of controlling the input amplifier's gain offers a way around this dilemma. For example, increasing the input transistor's emitter resistor will allow the amplifier to handle large signals at low gain settings, while decreasing the emitter resistor boosts the gain enough to minimize noise from subsequent stages at high gain settings. The disadvantage of this approach is that the bandwidth will change from one gain setting to another.

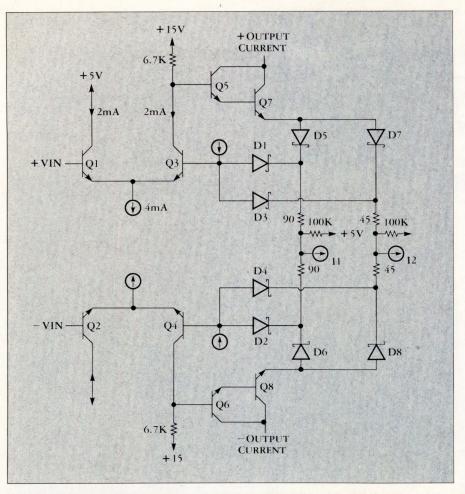

In the M377, discrete gain steps are obtained by changing the first stage gain setting resistor (as shown in Figure 4). TTL logic inputs select one of six current sources such as 11 or 12 which force the first stage quiescent current through the appropriate gain setting resistors and associated diodes. (For clarity, only two gain settings are shown in Figure 4). Diodes D1 and D2 or D3 and D4 close the feedback loop. The idle diodes are back biased by the appropriate 100K resistor. The diodes must withstand the brunt of the full input signal swing. Since the diode-connected high frequency transistor will punch through at about 1.5v reverse bias, Schottky barrier diodes, which can withstand reasonable voltages, are used. Two 6.7K nichrome resistors are used in place of active current sources to reduce noise.

In the linear range, thermal effects are quite small in this amplifier (when compared to a simple differential pair) because the large quiescent current and current swings necessary to produce an output signal are handled by Q7 and Q8. Thermals in these devices are inside the feedback loop and are reduced about 250 times by the voltage gain of Q1 and Q3 or Q2 and Q4. The operating points of Q1, Q2, Q3, and Q4 are virtually unaffected by input signals. The voltage change on these devices is small not only because the input signal is small, but the current change is also small because Q5, Q6, Q7, and Q8 have such high current gain. In fact, Q1, Q2, Q3, and Q4 barely change their operating points up to the level at which the signal cuts off either Q7 or Q8. Tight thermal coupling of Q1, Q2, Q3, and Q4 help to keep the remaining linear (as opposed to overdrive) thermals well below the 0.05 percent level. However, once Q7 or Q8 cuts off, the four input devices quickly go into the overdrive range. Taming the resulting overdrive thermals is a unique accomplishment of the M377.

### ■ FAST OVERDRIVE RECOVERY

Typically, when an amplifier is overdriven, it takes a reasonable amount of time to reestablish its operating point. Unless damage or destruction takes place,

# EEPROM/D COMBINATION F

There are literally thousands of combinations of LAN, security, and industrial applications where you have to integrate EEPROM and digital technologies. Now, you can combine them with the confidence and security that they'll work together, since they come from the same proven source — Sierra.

Our CMOS cell library contains over 20 EEPROM cells, which can be combined with our digital cells in thousands of combinations. So you can get exactly the functionality you need.

Just to give you one example, you can design a software switch that replaces DIP switches in setting board/ID configurations. Whether you're designing a mother board, add-in board, or LAN card, this lets you cut your parts count way down. And give your customers an easier product to use.

Of course, with a library of over 300 cells, we don't limit you to EEPROM/digital combinations. We make it just as easy to combine analog and digital, EEPROM

and analog, or all three on the same chip. Which is the whole idea behind our Triple Technology.™

Not only is that a Sierra exclusive, we also give it to you in CMOS. So you can look for reliable, low-power 5V operation. We give you the most efficient packaging, too. You can choose from low profile surface mount packages in SOIC, PLCC, and PQFP gull-wing versions.

As if that weren't enough, we also give you the kind of training and documentation

that make ASIC solutions easier to design than you ever thought possible. Just write or call for our complete library card. And we'll show you how to easily secure your next application. All you need is the right combination.

2075 North Capitol Avenue, San Jose, California 95132. Telephone (408) 263-9300

Figure 4. TTL logic inputs select one of six current sources such as 11 or 12 which force the first stage quiescent current through the appropriate gain setting resistors and associated diodes (only two gain settings are shown).

all amplifiers will eventually recover their original operating points. However, some amplifiers are better behaved in overdrive than others.

The overdrive specification of an amplifier depends upon its application. For an oscilloscope, the amount of recovery from overdrive is that percentage of the oscilloscope screen that is readily observable. For example, in observing a waveform on a screen, the recovery from overdrive should be between 0.2 and 2.0 percent of the display range. The advantage of fast overdrive recovery becomes apparent when comparing the equivalent number of bits a digitizer needs to observe the same detail. A 20 Megasample/second digitizer (sampling every 50 ns) would require 12 bits of resolution just to have its LSB (least significant bit) equal 0.02%. But installed in a 10 bit digitizer such as the 11401 oscilloscope, 0.02% of a 2 volt signal takes up 0.4 division at 1 mV/div. Each division is displayed with 100 codes of resolution, so each code then represents 10 µv. Ten microvolts is the equivalent of 17.6 bits of resolution of the 2 volt signal.

A 20 Megasample/second digitizer, unless it can be triggered and operated in an equivalent time mode, would be limited to 10 MHz bandwidth by the Nyquist criterion. However, in a realtime oscilloscope or in an equivalent time digitizer, quick overdrive recovery could display signal details in excess of 300 MHz. A real time oscilloscope could display a single event with a resolution limited only by noise to about 12 bits. An equivalent time digitizer, with averaging, could actually improve on the 10 µv (17.6 bits) resolution for repetitive signals. It is ironic that a digital scope is so effective for repetitive, analog-type signals and that analog scopes are so good a finding the single, isolated event frequently found in digital signals.

The M377 is capable of recovering from overdrive signals of up to 2 volts to within 0.04% in about 6 ns. Recovery to the 0.01% level takes 25 ns. This is more than three orders of magnitude faster recovery to the same level than the company's 7A13, a plug-in designed some years ago specifically for fast recovery. It is about 2 orders of magnitude faster than the settling of good modern operational amplifiers, and about five times faster than the best 12 bit DACs.

We became aware of just how good

0.02 percent recovery in 20 ns was when we tried to make the rest of the plug-in signal path support that kind of performance. For example, a 42 inch length of RG 58 coaxial cable, terminated in 50 ohms at each end still exhibits 0.02 percent skin effect loss 200 ns after a transient even though the total transit time of the cable is only 5 ns! The small diameter cable just 10 inches long used to connect the front panel BNC connector to the M377 inside the 11A52 plug-in exhibits 0.02 percent skin effect loss of its own about 20 ns after a step.

These losses for the first time became easy to measure and provided us with more than a few surprises. For example, the small diameter cable paradoxically settled to its final value much more rapidly than larger RG-58 of the same delay. As we thought about our measurements, the reason became apparent. The small cable has a copperweld (copper plated steel) center conductor. The dc loss of this cable is much greater per foot than the RG 58, and the time required to settle to its final (dc) loss is therefore less. An alternative explanation in the frequency domain: The dc loss equals the skin effect loss at a much higher crossover frequency.

Another discovery was a little more painful. The 11A52 plug-in has only a 50 ohm input impedance. This provides greater bandwidth and lower noise than a plug-in which requires a buffer amplifier with a 1 megohm input impedance. In fact, two M377s, one for each channel, are all the amplification the 11A52 has. The 11A52 then requires a 50 ohm attenuator which must be switched via relays. We chose a high reliability version of the popular subminiature style hermeticly sealed relay. These relays require glass to metal seals for hermeticity and use kovar for leads and header because kovar matches the thermal expansion coefficient of glass. But kovar is twenty to fifty times as resistive as copper and is ferromagnetic as well. Kovar is a great candidate for skin effect loss. Most of the kovar is gold plated, but the small segment inside the glass seal is not because the gold must be plated after the very high temperature glass to metal seal is made. It is in this very short section where serious skin effect losses occur. We found that, although the total path length through 5 relays in the attenuator was only 4 inches, the skin effect error did not die out to the 0.02 percent level for a full microsecond! To further complicate matters, when the relays are driven from a high impedance, such as a passive probe, the skin effect almost disappears. The reason for this is that the skin effect loss is an increase in the

series path resistance at high frequencies. When the attenuator is driven by a high impedance, the series loss is swamped out by the source's resistance.

Our solution was to introduce a network of resistors and capacitors in the attenuator which compensated for the skin effect loss. The whole attenuator has an 9 percent dc loss, but is flat from dc to 50 MHz within about 2 percent. The compensated attenuator is flat to within 0.05 percent at 40 ns, compared to about 2 percent at 40 ns before compensation. The attenuator risetime is just 130 ps.

## PRECISION OVERDRIVE RECOVERY IN THE IC

Precision overdrive recovery is a subject of some myth and misunderstanding. Most designers think about preventing transistors from saturating when they think of quick overdrive recovery. True, Schottky TTL switches are made faster than TTL by preventing saturation. But amplifiers are not the same as digital circuits, and transistor saturation is not what prevents a transistor amplifier from recovering quickly to within 0.1 percent.

It is thermal effects which dictate the amplifier recovery time at the 0.5 percent level and less. The faster the amplifier, the more power it dissipates, and the greater the potential for thermals. For example, amplifiers in the 7104 individually have a bandwidth of about 2.5 GHz per stage and thermals of about 6 percent per stage.

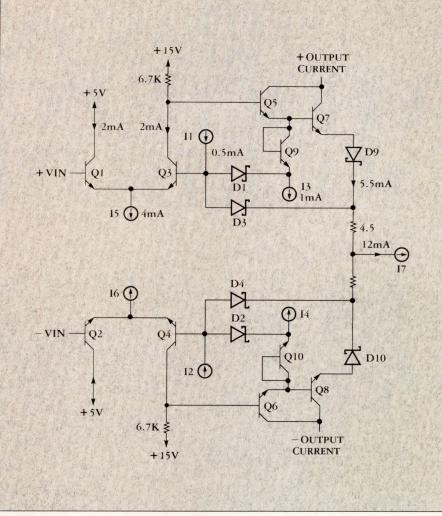

The M377 handles overdrive by using a Schottky diode to change the feedback loop in the input stage during overdrive. Figure 5 shows the input stage with the added components required for fast overdrive recovery. For simplicity, only one gain setting is shown.

In order to follow how the circuit works, you must realize that only the circuit half with the negative input becomes non-linear. This is true for the simple circuit of Figure 2b as well as the new circuit of Figure 5. For positive input signals, the amplifer takes all the current in the current source 17 and remains linear, but the mirror image circuit becomes nonlinear when it gives up all its quiescent current to the positive input side. It is always the side with the more negative input which goes non-linear. Therefore it is only necessary to understand what happens for negative input signals at Q1's base.

The voltage at the cathodes of D3 and D9 will follow + Vin down until D9 and Q7 cut off because the voltage at the junction of D4 and D10 is held by -Vin and its associated amplifier. At that point, D1 conducts because Q5 and Q9 are still con-

Figure 5. The M377 handles overdrive by using a Schottky diode to change the feedback loop in the input stage during overdrive. For simplicity, only one gain setting is shown.

ducting due to current source 13. D1 steals the current flowing through D3 and cuts D3 off. D1 closes a new feedback loop consisting of Q3, Q5, Q9, and D1. Without any loading, this changed circuit will follow the input signal down until 15 saturates or Q5 breaks down.

The linear input range is about 50mV and the gain is very high with the 9 ohm total emitter load. Because of tight thermal coupling, the thermal voltages generated are only 80uV per milliwatt of power difference between Q1 and Q3.

## VARIABLE GAIN CONTROL

Almost every oscilloscope has a continuously variable gain control to allow the user to adjust the size of his trace to fit within the screen area exactly as he chooses. This control is not as frequently used as the coarse (step) control, yet it is a source of several design difficulties. Passive attenuation (use of a potentiometer as a variable voltage divider) works well up to about 50 MHz. The chief advantage of this scheme is low cost. The chief disadvantages are the limited bandwidth and the mechanical constraint tying the potentiometer to the front panel.

Above 50 MHz some form of electronic gain control based upon a Gilbert multiplier is usually used. While the Gilbert multiplier can work well, it is not without its problems. Chief among these are the low bandwidth when compared to other stages in the same IC, the addition of thermals and the generation of a fair amount of noise.