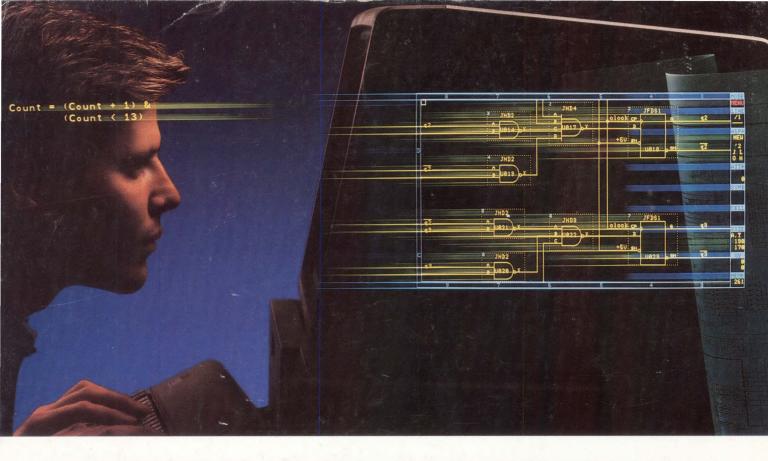

David Hightower on the floorplanner of the future

Layout software for large sea-of-gates designs

Special Report: VLSI in Japan

The Magazine for Systems Design Using VLSI Technology

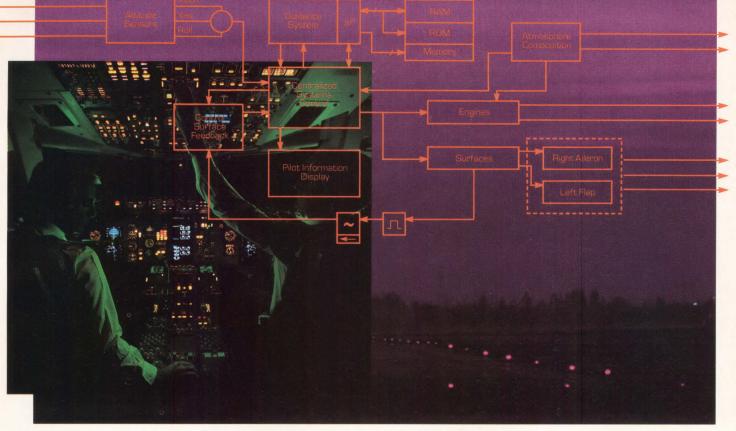

Programmable logic devices are going to work in unexpected places.

When you put a Fujitsu ASIC to work, you can rest assured it will work the way it should. And keep on doing its job for a very long time to come. In fact, when you look at our performance record over the years, you'll be hard pressed to find any field failures at all. This is no empty promise. Product reliability has been a way of life for us for more than 15 years

years.

That's why we always take a conservative approach to the design process. Giving you realistic worst case specs that no production device will exceed.

Guaranteeing a minimum 90% utilization of all gates. And giving you a simulation-to-production correlation of 99%.

It's also why we control every step of the production process. From design to wafer fab to assembly and final test, including 100% AC testing at frequency. So nothing is left to chance.

To us, reliability in the field is everything. And when you remember we've taken over 8,000 ASIC devices from design through mass production, you can see that we'll give you a level of confidence no one else can offer.

So count on parts that have longer life expectancies.

Call our Hot Line today at (800) 556-1234, Ext. 82; in California (800) 441-2345. Look into ASICs you can send out the door. Never to return again.

FUJITSU

FUJITSU

**MICROELECTRONICS. INC** Technology That Works.

#### Editor/Editorial Director

Girish Mhatre Executive Editor Roland C. Wittenberg

Managing Editor Mike Robinson Editor Emeritus

Roderic Beresford Editor-At-Large

Stan Baker

Western Regional Editor David Smith

Directories Editor Michelle A. Losquadro

**Technical Advisers** John A. Darringer Jeffrey T. Deutsch Edward J. McCluskey Alan F. Podell

Daniel G. Schweikert Susan L. Taylor

Editorial Production Patricia L. Gaynor, Sr. Production Editor

Cover Mike Shenon, Art Director

Editorial Art Marie D'Ippolito, Design Director

Manufacturing David Getlen, Dir. of Manufacturing Marie Myers, Production Manager James Pizzo, Production Supervisor Vance Hicks, Coordinator

#### Publisher Norm Rosen

VLSI SYSTEMS DESIGN (ISSN 0279-2834) is published monthly with an extra issue in May by GMP Publications, Inc., 600 Community Drive, Manhasset, NY 11030. (516) 365-4600. VLSI SYSTEMS DESIGN is free to qualified subscribers. Subscriptions to others in the US: one year \$60.00, two years \$95.00; Canada and Mexico: one year \$90.00, two years \$165.00; Europe, Central and South America: one year \$120.00, two years \$225.00. Asia, Australia, Israel and Africa: one year \$150.00, two years \$285.00. Second-class (Requester) postage paid at Manhasset, NY and additional mailing offices. POSTMASTER: Send address changes to VLSI SYSTEMS DESIGN, 600 Community Drive, Manhasset, NY 11030. Copyright 1988, CMP Publications, Inc. All rights reserved.

VLSI SYSTEMS DESIGN was founded to explore, expand, and define the interrelations between very-large-scale integrated circuits (VLSI) and computer architecture, design strategies, costs, and aids, as well as the electronics industry as a whole. VLSI SYSTEMS DESIGN is unique in that it is written by and for the participants in this dynamic field. VLSI SYSTEMS DESIGN intends to be the community, encourage its development, and help define its directions.

Over 41,000 copies of this issue printed.

CMP ELECTRONICS GROUP

Kenneth D. Cron Vice President/Group Publisher Electronic Buyers' News Electronic Engineering Times VLSI Systems Design

**♥BPA**

CMP Publications, Inc. Gerard G. Leeds, President L.J. Leeds, Senior Vice President Michael S. Leeds, Vice President Pearl Turner, Vice President/Treasurer Volume IX, No. 4, April 1988 SYSTEMS DESIGN

The Magazine for Systems Design Using VLSI Technology

#### Cover

Chameleonlike, the latest round of programmable logic devices are adapting to new and unusual applications, thanks to architectures that give them more flexibility than earlier devices. Cover illustration by Dick Oden, Laguna Beach, CA.

## Departments

**6** From the Editor

Are We Still Playing Games?

- 8 Letters A Poorly Executed Benchmark?

- 10 Calendar

#### 12 News

Sea-of-Gates Array Technology ECL Array New RISC Machines Two 64-bit FPUs Combination Control Store and Logic Analyzer

16 People

This Is the House That Ross Built

- 18 Industry Insights Floorplanning for the Future

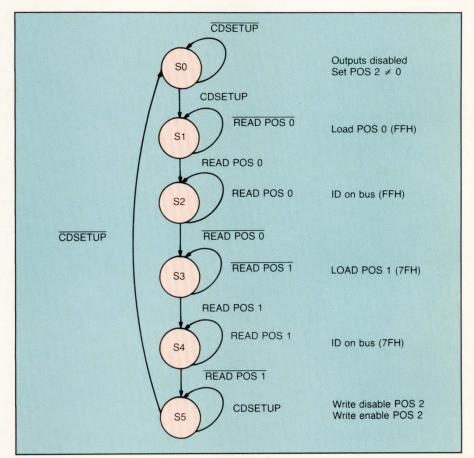

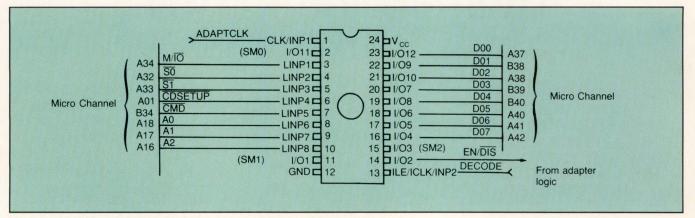

- 61 Designer's Corner Putting PS/2 POS in the 5AC312 EPLD

- 65 Product Showcase GaAs Standard Cells Use SCFL Logic for 2-GHz Toggle Frequencies

- 72 Advertisers' Index

Page 22

Page 65

## Articles

#### 19 Conference Preview The 1988 Custom Integrated Circuits Conference

This year's conference will cover a wide variety of custom and semicustom ICs, including the newest high-density sea-of-gates arrays, plus new design tools.

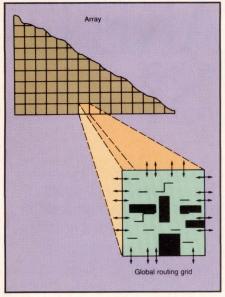

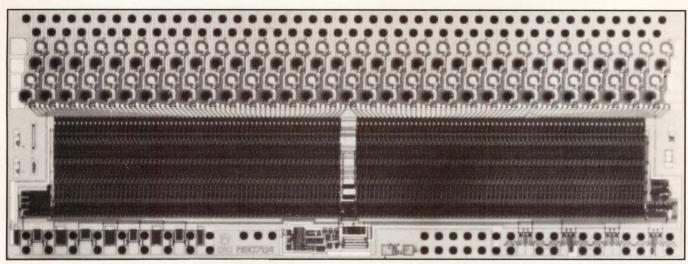

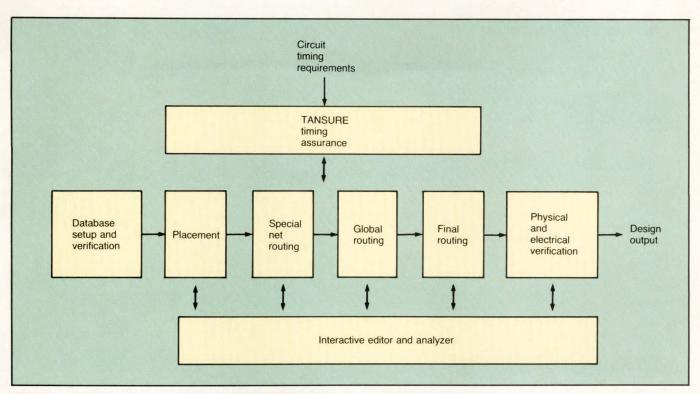

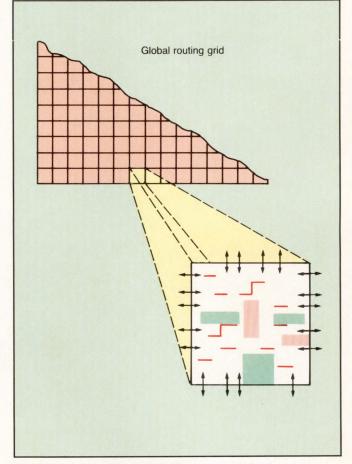

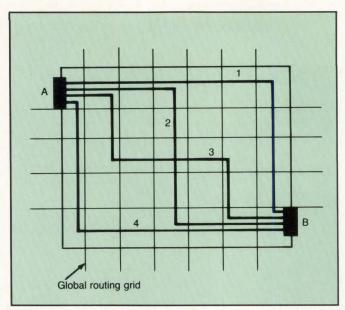

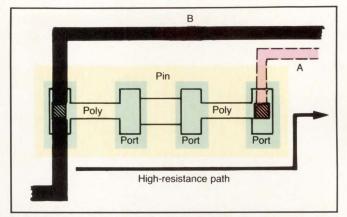

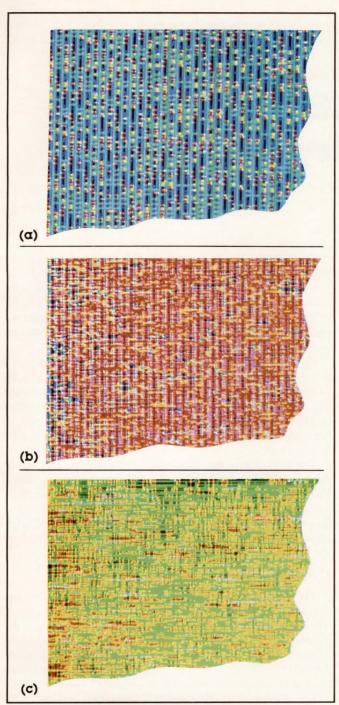

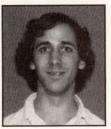

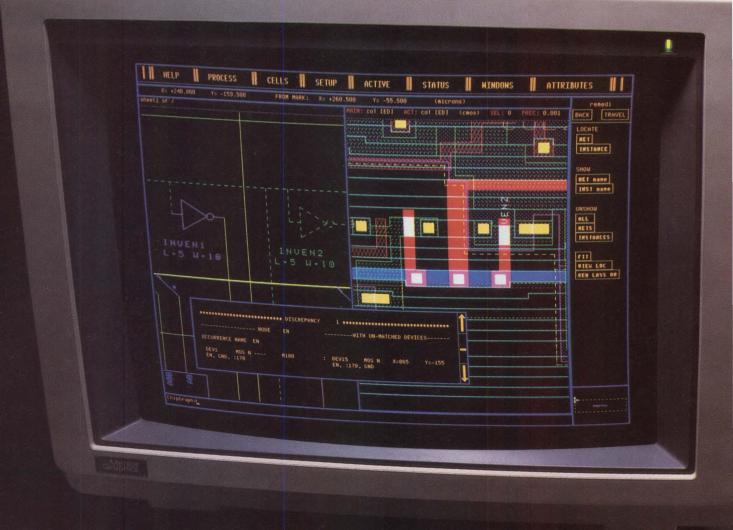

#### 22 Automating the Layout of Very Large Gate Arrays

#### Aki Fujimura, Tangent Systems Corp.

To automate the layout of large gate arrays, CAD systems must juggle large designs and achieve high gate utilization. This system uses unique placement algorithms, a two-stage routing step, and a compact database to design both channeled and sea-of-gates gate arrays.

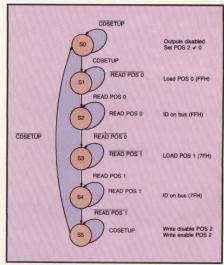

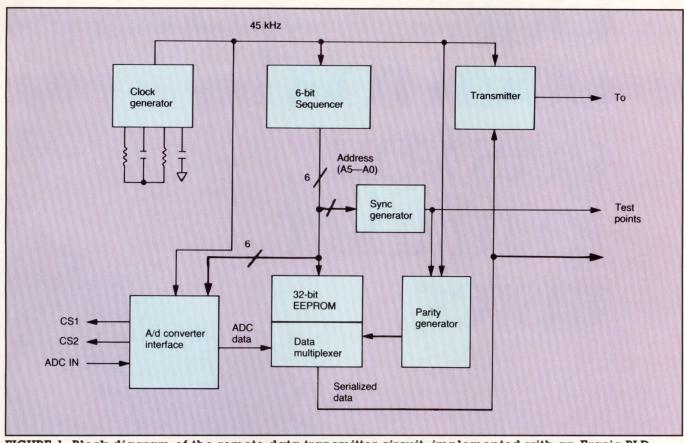

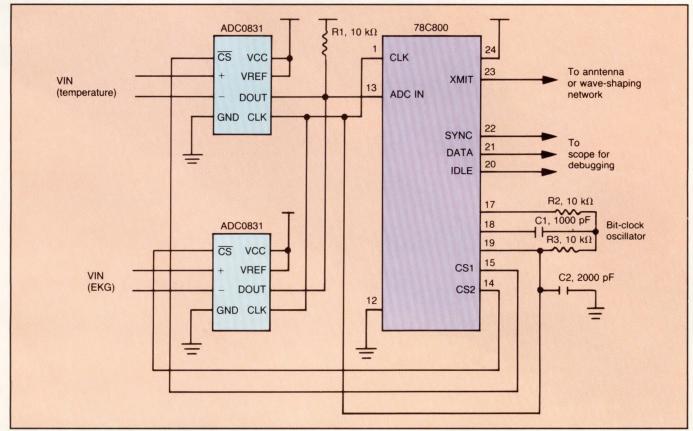

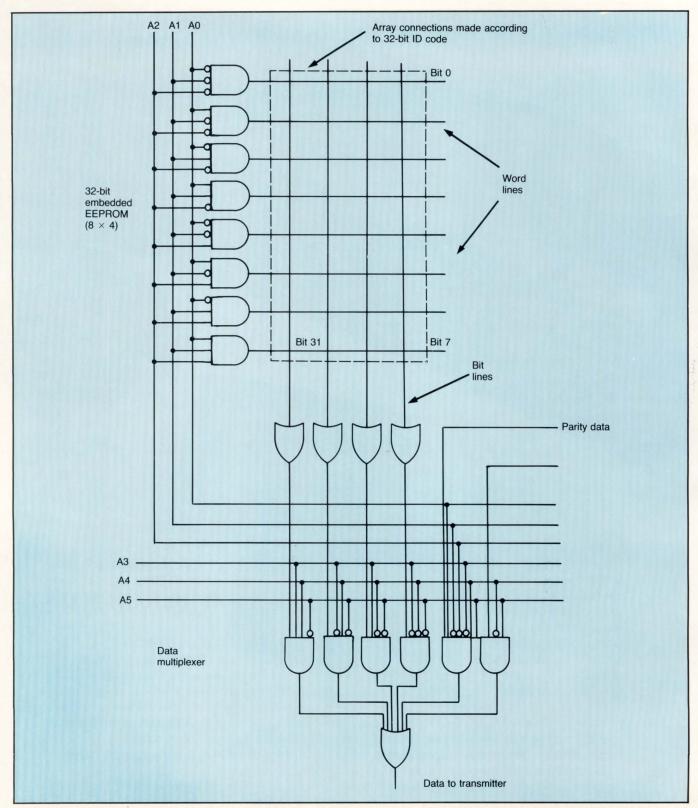

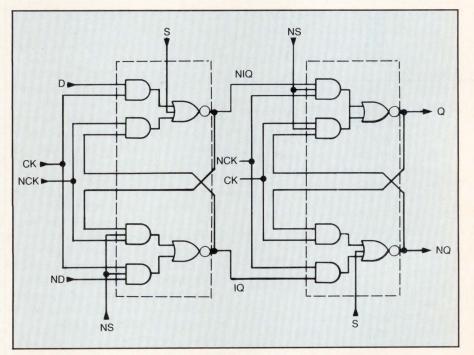

#### 28 Multilevel EEPLD Implements Biotelemetry System

#### Erich Goetting, Mikael Hakansson, and Steven Peterson Exel Microelectronics Inc.

A relatively complex subsystem for tracking and monitoring livestock owes its implementation simplicity to a new electrically erasable PLD. The device forms the heart of the system, a remote data transmitter.

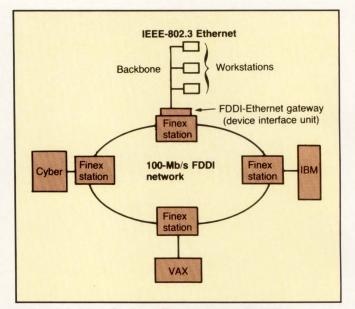

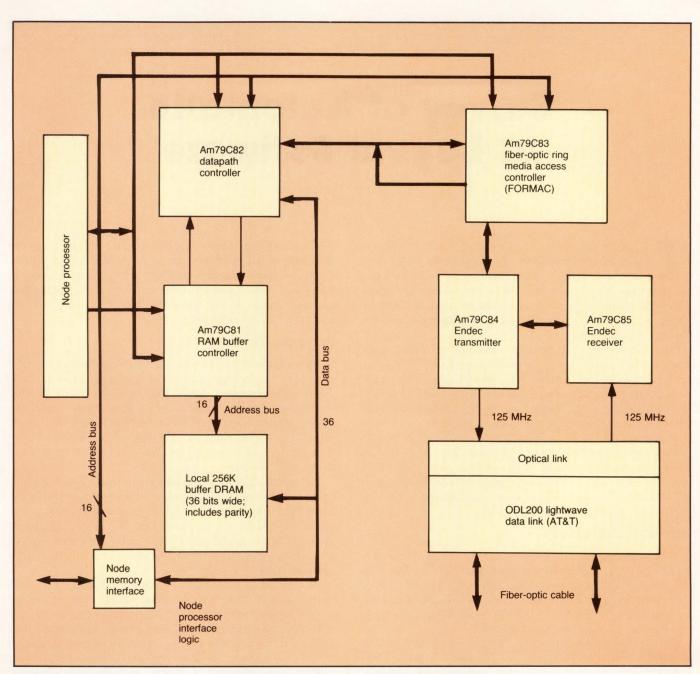

#### 34 The Integration of Fiber Optics into Network Systems

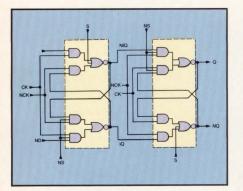

#### Mark Stansberry, Cypress Information Resources

System designers considering including network nodes in their systems must ultimately address the coming of the fiber-optic age. The advantages of the medium, the arrival of VLSI support ICs, and the demands of applications point to expanding adoption.

#### 40 Survey of Automatic IC Layout Software

#### VLSI Systems Design Staff

Our annual survey of automatic placement and routing tools spots these trends: corporate mergers, tools designed for sea-of-gates arrays, and growing numbers of interfaces.

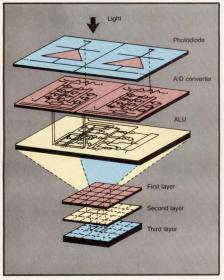

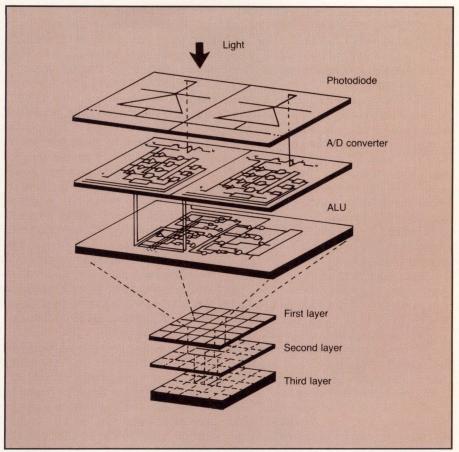

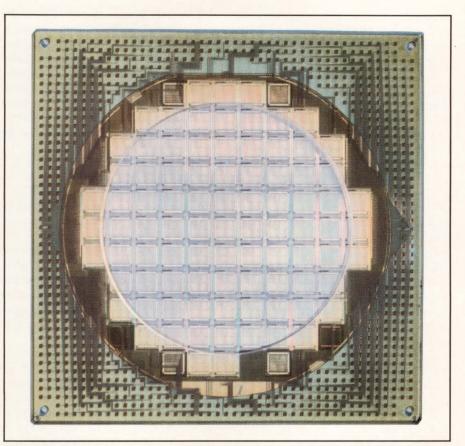

#### 52 Japanese Engineering Girds for the Future

#### Stan Baker, Editor-at-Large

Although the difference in East-West engineering and management cultures has slowed the acceptance of U.S. design automation tools by Japanese companies, the Japanese electronics industry is busily preparing for future breakthroughs in chip technology in the areas of wafer-scale integration, three-dimensional IC fabrication, and packaging technology—as well as in new mainframe- and workstation-based design tools.

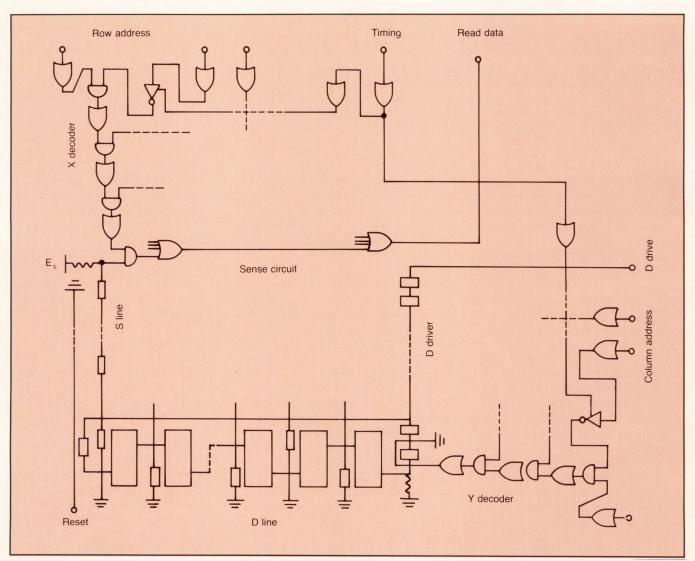

#### 57 A High-Speed, Low-Power Josephson-Junction RAM

#### Y. Wada, S. Nagasawa, I. Ishida, M. Hidaka, S. Tsuge, and S. Tahara NEC Corp., Microelectronics Research Laboratories

A 1-Kb Josephson-junction RAM uses a resistor-coupled Josephson logic decoder and sense circuits, plus a nondestructive-read-out memory cell, to help achieve a 570-ps minimum access time while dissipating 13 mW.

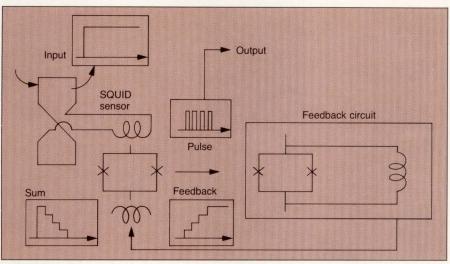

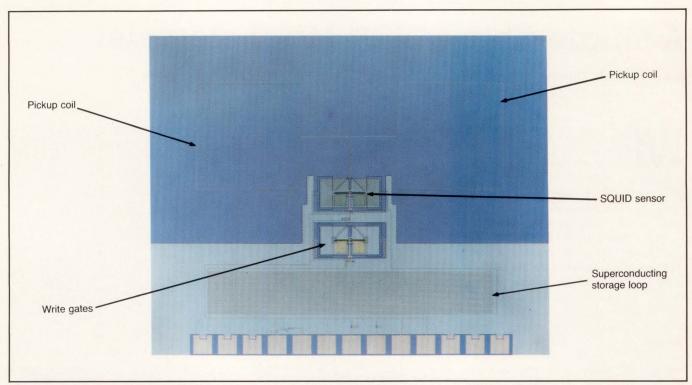

#### 59 A Single-Chip SQUID Magnetometer

#### N. Fujimaki, H. Tamura, T. Imamura, and S. Hasuo, Fujitsu Laboratories

A magnetometer based on superconducting quantum interference device (SQUID) technology integrates a complete SQUID sensor circuit and feedback circuit, together with the necessary pickup coils, on a single superconducting chip that operates at 4.2K.

Page 52

# DO YOU HAVE WHAT IT TAKES TO MAKE IT BIG IN ASICS?

Not long ago, designing accelerator is seamlessly intewith more than 170 design grated with the sche-ASICs wasn't even kits supplied by 70 different ACCELERATED ASIC DESIGN KITS vendors. So you can build propart of your job. matic, so you can locate Now it's the and correct design ductivity instead of libraries. Which may explain why problems interactively. part everyone's counting on. That means faster more MegaLOGICIANs are That's where debugging and more in use today than all other time to improve Daisy comes in. Cadnetix Others accelerators combined. Valid the quality of your Speaking of combining, you Daisy CAE tools Daisy are used by more design. Plus ASIC designers than no other accelerator any other CAE workstations. is as well supported, Because from schematic creation through post-layout Daisy 53% 5,000 GATES 2,000 GATES Zycad 11% Simulation accelerator market share. Source: Prime Data, 1985 and 1986 unit shipments. simulation, Daisy has what it takes to keep ASICs on time and on budget. For example, our MegaLOGICIAN<sup>™</sup> simulation

© 1988, Daisy Systems Corporation. MegaLOGICIAN is a trademark of Daisy Systems Corporation. \*Based on minimum 10x performance improvement compared to 32-bit workstations. Source for design kit estimates: VLSI Systems Design's Semicustom Design Guide, 1987. can share a MegaLOGICIAN with a network of our 386based desktop workstations, for a high-powered low cost ASIC design environment.

And that's just the beginning. With our library of more

than 4,500 systemlevel components, you can include your ASIC in complete "real world" system simulations to ensure that your designs will be ready for production, instead of revision.

All of which makes Daisy today's choice for no-sweat ASIC success.

But what about tomorrow? Gate counts are on the rise. If your tools run out of steam at 5,000 gates, so could your future.

No problem. Our ASIC design tools glide through 20,000-

without even breathing hard. In fact, new design kits already support arrays of over 100,000 gates.

gate designs

So you'll never have to worry about hitting a dead-end.

But don't take our word for it, listen to what Rockwell and other industry leaders have to say. For a free copy of "Making It Big In ASICs" call Daisy at 1 (800) 556-1234, Ext. 32. In California, 1 (800) 441-2345, Ext. 32.

European Headquarters: Paris, France (1) 45 37 00 12. Regional Offices: England (256) 464061; West Germany (89) 92-69060; Italy (39) 637251.

## Are We Still Playing Games?

t's almost 20 years since the UNIX operating system was developed by Ken Thompson at Bell Laboratories. It was originally created for an experimental computer game. However, during the past 19 years, AT&T has revised, enhanced, and expanded the system so that it now has a robust suite of features. The University of California at Berkeley also got involved with the system in the late '70s and added many of its own enhancements and extensions such as the BSD 4.x versions.

In recent years UNIX has become one of the most popular de facto standards in the design automation industry. As a result, more and more design systems and tools are being ported to UNIX operating systems. This trend could bode well for the computer-aided engineering community. A strong, universally accepted operating system would help designers in picking and choosing a set of tools, from a variety of vendors, that was best suited to their particular applications. Unfortunately, a number of dark clouds have been looming on the UNIX horizon. One such cloud is the proliferation of different UNIX or "UNIX-like" systems. There's System V, BSD 4.3, AIX, DNIX, HP-UX, and ULTRIX, and the list keeps growing. Also, there have been numerous efforts to standardize on one unified system. Just recently AT&T and Sun Microsystems announced a long-range joint effort to develop a unified UNIX that incorporates the best features of System V and BSD 4.3. Additionally, the IEEE POSIX (portable operating system) committee has received conditional approval for a UNIX user-interface standard (IEEE-1003.1). But both System V and BSD 4.3 will require some rework to meet this standard.

A second storm cloud appeared a few months ago when AT&T announced a buy-in at Sun. That event, together with the AT&T-Sun program for determining the future directions of UNIX, triggered a much publicized dispute between AT&T and a large group of prominent UNIX licensees. Despite AT&T's assurances to the contrary, the licensees fear that the new UNIX will end up with a built-in bias to-ward the Sun and AT&T workstation architectures. In addition, there are still some shortcomings to the present versions of UNIX—even though a number of independent groups from both academia and industry are hard at work on the solutions. For instance, a group at Carnegie-Mellon University has already developed a MACH kernel for UNIX that solves many of the problems of extending UNIX to networked uniprocessor and multiprocessor systems.

I doubt that UNIX will ever be the answer to every designer's prayers—and systems with large installed bases like MS-DOS and VMS won't be abandoned but a good operating-system standard could ease and accelerate the transition of many reluctant system engineers into the world of design automation. Such a speedup can't help but benefit the entire U.S. electronics industry. So let's stop playing games with industry standards and get the various industry groups together to try to work out a solution agreeable to all parties. Perhaps a cooperative industry-university program like the X Window program now operating at MIT with industry sponsorship is the answer. We've already got a head start, since many of the university enhancements and developments for UNIX were funded with U.S. tax dollars and are now in the public domain.

Coland With

Roland C. Wittenberg Executive Editor

## The One Week Analog ASIC.

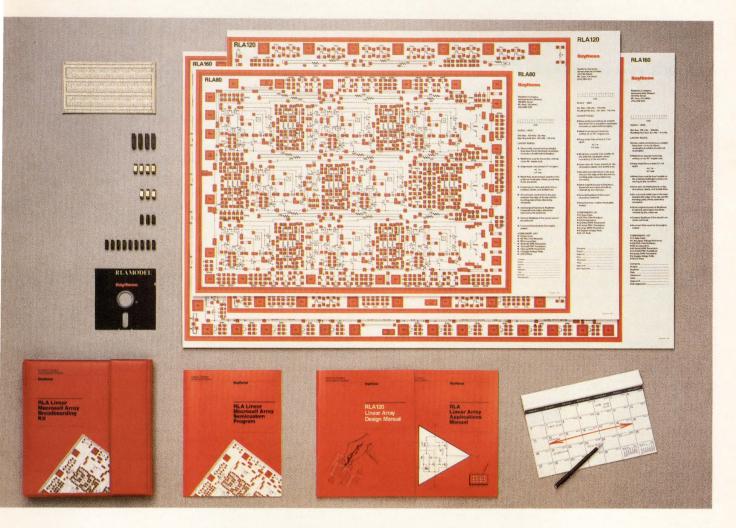

#### The leading technology . . . the best support . . . go!

The leading analog ASIC family: RLA80, RLA120, and RLA160 userconfigurable macrocell arrays. Onchip thin film SiCr resistors and duallayer metal for ease of interconnect routing and maximum array utilization and performance. Wide supply voltage range —  $\pm 1V$  to  $\pm 16V$ . And simplified design procedures that take days, not weeks.

□ Configurable macrocells: 8, 12, or 15 gain blocks in any combination as general purpose op amps, open collector output comparators, or as input amplifiers with ground sensing function for single-supply systems. RLA160 has a preconfigured onboard adjustable ±30 ppm voltage reference. **Thin-film resistors:** on-chip SiCr resistors exhibit 1% matching and temperature drift characteristics comparable to discrete film resistors. High performance and high values (1.25 kΩ to 150 kΩ) handle a wide variety of applications.

□ Design support: The RLA Breadboarding Kit contains complete design and applications documentation, 200x plots, a pre-drilled printed circuit board, and 23 ICs. Friendly RLAModel software includes menudriven user interface program for PSPICE<sup>1</sup>, SPICE<sup>2</sup> model library for RLA series, documentation files, and full screen editor. Not to mention the attention you get from applications engineers who have 15 years experience meeting custom and semi-custom requirements.

Call Raytheon for access to RLA program information and details on the RLA Macrocell Array Breadboarding Kit. We promise you a week that will go down in history.

Raytheon Company Semiconductor Division 350 Ellis Street Mountain View, CA 94039-7016 (415) 966-7716

PSPICE is a trademark of MicroSim Corporation. SPICE developed by University of California.

Access to the right technology

#### A Poorly Executed Benchmark?

Dear Editor:

I must question the article "Benchmarking Schematic Entry Systems" published in your 1988 User's Guide to Design Automation. The article is a poorly executed product evaluation that suffers from several very serious flaws, including inaccuracy. The caveatin the concluding paragraph does not begin to cover the extent of variables unaccounted for. Here are some examples of the flaws in the article:

• The author did not solicit the current version of the products under evaluation.

• The author failed to learn about and develop a consistent methodology for evaluating the four products.

An apt example of poor methodology is that the author did not enlist users of equal proficiency even though ease of use was considered to be an important factor in the evaluation. As a consequence, a given schematic editor was judged more favorably if Ms. Filseth had access to a proficient user of that editor. In fact, in counting keystrokes, she substituted short-cut procedures developed by proficient users, if available. That reduced the number of keystrokes for some editors and not for others.

The Daisy product did not benefit by reduced keystroke counts because, according to Ms. Filseth, the Daisy user was familiar only with DED, the precursor to ACE, and ACE was substituted at the last minute as the Daisy product in the evaluation. That helps to explain her poor rating of ACE.

It is clear that neither Ms. Filseth nor her users had much experience with the functionality of ACE. Otherwise, she would have known that ACE does indeed have an *undo* command. In fact, it is probably the only editor that has has an infinite undo/redo capability, which can be used on multiple files independently.

She also would have known that ACE can delete not only a rectangular area but any selection or group of selections the user defines. In fact, Ms. Filseth was completely unaware that ACE offers the user the ability to select and group objects so that operations may be performed on them later. This Macintoshlike feature actually reduces the required number of keystrokes.

• The author provided insufficient information about the design and published the schematic for only one editor. This lack of information is particularly disappointing because readers would have been better able to judge the contents of the article if they had access to all the critical information. For example, judging by the design shown for LSED, the times for all four schematic editors seem tremendously high. At the 1986 Design Automation Conference, Daisy conducted a "race for productivity" in which attendees were invited to use ACE to create a design similar to the one shown in the article. Nearly all of these participants, who had never used ACE before, were able to complete the schematic in under 6 minutes. Perhaps if the actual schematic created by Ms. Filseth's ACE users had been shown, readers would have been able to evaluate why such a seemingly simple design required a reported 260 minutes to complete. Showing all the schematics would also have allowed readers to evaluate the "aesthetic" problems Ms. Filseth reported.

In addition, better information about the design would have illustrated whether problems with the schematic were indeed a function of the schematic editor or the user or whether the design Ms. Filseth selected was more suited to one vendor's modeling system than that of another.

David A. Stamm Executive Vice President Daisy Systems Corp. Mountain View, CA

#### Dear Editor:

In the article entitled "Benchmarking Schematic Entry Systems," which appeared in the 1988 User's Guide to Design Automation, a benchmark is performed using the Apollo DN420, a platform that has been made obsolete for over two years by two subsequent generations of computers, and by Mentor Graphics' software release 5.1 for NET-ED/SYMED, which in fact has been upgraded by three new software versions over the past two years. I believe that the other competitive products in this article were also far from current offerings.

The caveat at the end of her article that "software is in constant flux" cannot excuse a review of products that were replaced over two years ago.

#### Frank Costa

Vice President and General Manager Design and Analysis Division Mentor Graphics Corp. Beaverton, OR

The author replies: Let me start with the criticism that both Mentor Graphics and Daisy make, that systems benchmarked were not the latest offerings from the four vendors.

Mr. Costa's complaints that the benchmark was performed on an obsolete Mentor platform using an outdated software release are valid, and I certainly share Mentor's frustration over the difficulty of keeping studies of this kind current with vendor releases.

First, I must point out that there was an excessively long lead time on this article. I initially gathered information for the study in September, 1986, and submitted it to VLSI Systems Design for consideration in early 1987. VLSI accepted the article for publication in late spring but asked that I substitute Daisy Systems' new product, ACE, for DED/-CED. I performed that benchmark in mid-1987. The published article finally emerged in early 1988. As a result, none of the products in this article were "current offerings."

Secondly, recognizing the futility of playing perpetual "catch-up" with constant new product releases, I simply reported which versions I used; furthermore, I did use the most current versions available to me.

This article began as a term project in a class at San Jose State University. When I embarked upon this project in the fall of 1986, I submitted letters of inquiry to all of the vendors involved. In those letters, I described the proposed study as a student "technical report" and noted that I hoped eventually to get the paper published in a trade journal. I asked for information about recent product releases, upcoming demonstrations, and equipment availability. Noting that my research would be incomplete were I unable to include data about these vendors' products, I asked for "any information [they] might be able to provide toward a more accurate comparison of [their] product to the other editors."

Of the four vendors in this study, Mentor Graphics alone did not respond to my letter. A follow-up call also was ignored, an my phone calls were not returned.

As for Daisy, it is certainly true that the study was originally completed with DED/CED as a prominent player and that ACE was only later substituted for its outdated precursor.

Let me now turn to Mr. Stamm's other criticisms.

• Poor methodology. The reference to "short-cut procedures" was included because NETED/SYMED is a more reconfigurable editor than the others in this study. Ignoring this characteristic would have made it impossible to give a clear picture of that editor's real-world usefulness. If ACE also has such capabilities, I am sorry that I wasn't aware of them.

Secondly, proficiency is a subjective quality and one difficult to measure. I enlisted engineers whose daily work required them to use the respective editors in similar capacities. All the engineers participating in this study believed themselves to be proficient users.

• Unfamiliarity with ACE. I did not say that the Daisy user was familiar only with DED/CED, ACE's predecessor. What I said was that the same engineer who entered the DED/CED design for the original comparison also entered the ACE design. Presumably, many ACE users were once DED/CED users; I did not regard proficiency in both systems to be an unlikely prospect. It is true the ACE user was less experienced with ACE than the other users with their editors, but that is hardly surprising, since ACE is a newer product than its competition in this study.

• Inexperience with ACE. It is true that ACE offers the attractive features mentioned in Mr. Stamm's letter, and I am sorry I missed them. In retrospect, it seems unwise to have moved so quickly through an evaluation of ACE in a futile attempt to keep the article timely. For whatever inconvenience these mistakes may have caused Daisy, its clients, and VLSI Systems Design, I apologize.

The select-and-group-for-later-recall capability he describes reduces the required number of keystrokes for group operations slightly. Since I don't know how this feature works on ACE, I will not attempt to revise my keystroke estimate. While I strongly regret overlooking

Continued on page 66

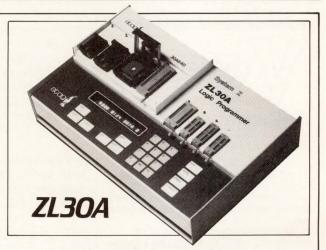

## Universal Logic Device Programmers

The Stag ZL30A provides:

- Extensive PLD, EPLD and GAL\* programming support for most DIP and Surface Mount logic devices.

- Low cost optional expansion adaptors for support of any future device packages.

- Long-term value protected by the ability to upgrade hardware and software both easily and inexpensively.

- Largest device support found in any logic programmer on the market.

- Certification and test by the major semiconductor manufacturers to ensure compliance with device specifications.

- RS232C and IEEE-488 ports for easy interface to a terminal or a computer.

- Computer Remote Control (Standard).

For further information, contact:

Stag Microsystems Inc. 1600 Wyatt Drive Santa Clara, CA 95054 (408) 988-1118 (CA) Stag Microsystems Inc. 3 Northern Blvd. Amherst, N.H. 03031 (603) 673-4380

- Built-in automatic IC handler Control Port and optional interface kits for high volume production/throughput capability.

- Compatibility with CUPL\* and other logic compilers.

- Optional StagCom\*2 interface and file management software package for easy remote communications with your P.C.

- Worldwide sales and service.

\*Cupl is a trademark of P-CAD. \*GAL is a trademark of Lattice.

#### CICC '88 May 16-19, 1988 Rochester Riverside Convention Center/Holiday Inn-Genesee Plaza Rochester, NY

CICC '88 is sponsored by the IEEE Electron Devices Society and the IEEE Solid State Circuits Council and co-sponsored by the IEEE Rochester Section. Its goal is to bring together designers and manufacturers of circuits and systems and users of custom ICs to discuss new developments and future trends in custom integrated circuits. Session topics will include application-specific memories, circuit and logic simulation, drivers and interfaces, layout analysis and generation, analog circuit techniques, targeted silicon compilers, user-programmable logic devices, testers and testability, high-performance fabrication technology, packaging and systems interconnection, cell-based designs, telecom cir-

generation and modification has long been a monotonous, error-prone process. Flexibility in emulating and modifying system timing has been almost nonexistent. The availability of VGEN, however, radically changes this situation. A designer can now algorithmically generate patterns with precise control over pattern cycle times as well as individual pin timing.

If you are involved with large logic simulations on any of today's popular simulators, let us show you how VGEN can improve your productivity and enhance your overall simulation effectiveness.

#### Write or call TODAY: (408) 997-2575

MENTOR GRAPPHCS is trademark of Mentor Graphics Corporation, VALID is a trademark of Valid Logic Systems, Inc., DAISY is a trademark of Daisy Systems Corporation, HILO is a registered trademark of CentRad Corporation, SILOS is a trademark of trademark of a trademark of G.E. Calma Company, LDS is a registered trademark of LSI Logic Corporation, VGEN is a trademark of G.E.

10 VLSI SYSTEMS DESIGN April 1988

cuits, and reliability. For additional information, contact Mrs. Roberta Kaspar, Executive Secretary, CICC '88, 20 Ledgewood Dr., Rochester, NY 14615. (716) 865-7164.

#### 15th Annual Symposium on Computer Architecture May 30-June 2, 1988 Ilikai Hotel Honolulu, HI

This annual symposium is sponsored by the Computer Society of the Institute of Electrical and Electronics Engineers and the Association for Computing Machinery. It will feature presentations that include language-oriented architectures, distributed and parallel architectures, performance evaluation and measurement, advanced devices, architectures for transaction-based systems, memory systems, architectures for artificial intelligence applications, interconnection networks, the impact of VLSI on architecture, novel computing techniques, operating-systems-oriented architectures, and tools and methods for architecture design and description. Additional information about the symposium may be obtained by contacting H.J. Siegel, General Chair, Supercomputing Research Center, 4380 Forbes Blvd., Lanham, MD 20706.

#### Design Automation Conference '88 June 12-15, 1988 Anaheim Convention Center Anaheim, CA

DAC '88, which is sponsored by the IEEE Computer Society and the Association for Computing Machinery, is devoted solely to the field of design automation. This year's conference will offer tutorials, panel discussions, and technical presentations. General session topics will include electrical and discrete simulation, timing verification, testing and diagnosis, formal verification techniques, IC layout and silicon compilation, layout verification, logic and register-level synthesis, design systems and databases, behavioral and hardware description languages, design automation for integrated-circuit fabrication and for analog circuits, high-speed systems and microwave design automation, and system-level design aids. Additional information may be obtained by contacting Pat Pistilli, MP Associates Inc., 7490 Clubhouse Road, Suite 102, Boulder, CO 80301. (303) 530-4333.

#### ICCAD-88 November 7-10, 1988 Santa Clara Convention Center Santa Clara, CA

This international conference, sponsored by the IEEE Computer Society and the IEEE Circuits and Systems Society, in cooperation with the IEEE Electron Devices Society and the ACM Special Interest Group on Design Automation, is oriented toward the electrical engineering CAD professional. Original papers are invited for 25-minute presentations on these topics: simulation, layout, layout verification/extraction, testing, database/CAD systems, and design synthesis. Twelve copies of both a one-paragraph abstract and a detailed 1500-word description, which are due April 29, should be sent to ICCAD-88 Secretary, Electrical and Computer Engineering Dept., Carnegie Mellon University, Pittsburgh, PA 15213, (412) 268-3546. For more details, contact MP Associates Inc., 7490 Clubhouse Road, Suite 102, Boulder, CO 80301. (303) 530-4562.

#### IEEE International Conference on Wafer-Scale Integration January 3-5, 1989 Fairmont Hotel San Francisco, CA

This conference will present a balanced program of all the aspects of monolithic wafer-scale integration, including theory, technology, applications, and products. The program will feature contributed papers, poster presentations, and panel discussions and will cover topics such as WSI reliability, yield modeling, wafer-scale CAD systems, packaging, power/ground distribution, signal and image processors, and wafer-scale memory. Interested authors should submit, by May 1, three copies of a summarized proposal to Joe Brewer, Westinghouse Electric Corp., Box 746, M/S 5240, Baltimore, MD 21203. For more information, contact Patty Patterson, TRW Defense Systems Group, 1 Space Park (R2/2076), Redondo Beach, CA 90278. (213) 812-0788.

## At 100 MHz, the IMS Logic Master XL creates a new world standard for ASIC verification.

## But speed isn't everything.

You might think it sufficient that we're introducing the highest performance ASIC verification system available anywhere.

And that our new Logic Master XL is the first system with data rates of 100 MHz.

But we didn't think that was enough.

Instead, we concentrated on the kind of features that turn superior performance into superb productivity.

Like advanced driver electronics which produce symmetrical waveform edges for measurement accuracy.

And complete per-pin control. So you can handle complex timing configurations with ease. And mixed technology devices.

Plus automatic wiring for rapid, error-free setup, and superb system skew for greater measurement confidence.

Best of all, the Logic Master XL comes from Integrated Measurement Systems, the international leader in ASIC verification.

Contact us for more information.

Integrated Measurement Systems, Inc. Corporate Headquarters 9525 S.W. Gemini Drive Beaverton, Oregon 97005 TEL, 503 626-7117

**CIRCLE NUMBER 4**

Photo courtesy of NASA

U.S. Regional Offices: Boston, MA 617-366-3676; Irvine, CA 714-768-5808; Portland, OR 503-626-7117. International Offices: Belgium 02-219-2453; Canada 416-890-2010; France 01-4534-7535; Hong Kong 5-701181; Japan 0423-33-8111; Sweden 753-38465; Switzerland 830-5040; Taiwan 02-501-0055; The Netherlands 01-40-582911; United Kingdom 06-284-76741; West Germany 5722-2030.

#### Sea-of-Gates Array Technology

Shedding its quiet image, Silvar Lisco (Menlo Park, CA), pushes into the forefront of semicustom IC design with a new gate array design system, AVANT GARDS. The new software places and routes sea-of-gates designs having as many as 150,000 gates. Arrays with two or three routing layers can be implemented. Automatic and interactive placement and routing algorithms allow the tools to use between 80% and 90% of the available gates on an three-layermetal array, according to Silvar Lisco.

AVANT GARDS is approximately comparable to the other new sea-of-gates layout system, TANGATE from Tangent Systems Corp. (see p. 22). Although TANGATE specifies a larger potential design size, we imagine that 100,000 gates is sufficient for most gate array users.

TANGATE is still available only to Tangent's technology partners. It will not be available commercially for two months. In contrast, Silvar Lisco has taken pains to make AVANT GARDS an immediately applicable product, with features we may see in the commercial version of TANGATE. AVANT GARDS can lay out designs for any foundry or process technology. It can automatically develop a model of an array and its cell libraries from physical designs in the GDS II format, and it can lay out designated nets to keep propagation delays below a user-specified maximum. Nets can also be prioritized.

AVANT GARDS contains an automatic program that produces a rough initial floorplan according to hierarchy in the logic design. Automatic placement tools improve the initial placement through hierarchical, min-cut, and seed-based placement algorithms. Routing is accomplished with line search and exhaustive maze routing algorithms. During any step, interactive placement and routing editors allow designers to preplace and alter macros and routes.

The product can, with customer input, route arrays with channels and "islands" as handily as it does sea-of-gates ICs. It is available for VAX computers for \$325,000; workstations from Apollo Computer and Sun Microsystems will be supported later this year. SGS-Thomson Microelectronics (Carrollton, TX) has already incorporated the tool into the design suite for its ISB12000 Continuous Array family.

VLSI Technology Inc. (San Jose, CA) has announced its second sea-of-gates arrays, called the VGT200 series, which join its VGT100 products. The new series has a unique "bent-contact" structure that allows the transistors to be packed more tightly, resulting in not only higher density but also lower parasitic capacitances. Like the VGT100 chips, the VGT200 arrays use gate isolation to isolate macrocells from one another, a feature that increases the flexibility of the placement tools during layout.

The total gates in the seven arrays in the series range from 30,752 to 187,300. With the denser transistor layout, utilization efficiency falls to 35% (from 75%) for the VGT100 series), allowing the VGT200 arrays to implement designs as large as 10,000 gates for the smallest array and 65,000 gates for the largest. Although the total number of usable gates has not increased much from that of the VGT100 series (which accommodates 50,000 maximum usable gates), the real benefit of the new architecture is in performance. The typical gate propagation delay for the VGT200 arrays is 0.560, 70% that of the VGT100 arrays.

Both the VGT100 and VGT200 series can implement designs created from VLSI Technology's "portable libraries," which include macrocells and compilers for RAMs, state machines, and datapaths. The designs can also be implemented in cell-based ICs. NRE for the VGT200 arrays ranges from \$40,000 to \$150,000.

Finally, Toshiba America Inc. (Sunnyvale, CA) has shrunk its TC110G seaof-gates arrays from 1.5- to 1.0-μm CMOS technology, resulting in the TC120G series. The new technology reduces propagation delays 33%, offering typical gate delays of 400 ps. Like its predecessor, the TC120G series uses two layers of interconnect and has array sizes ranging up to 129,042 available gates. Although Toshiba uses the TANGATE layout tools, two-layer-metal technology limits the gate utilization of the TC120G arrays to between 30% and 50%. Toshiba is accepting designs this month.

#### ECL Array

Raytheon Co.'s Semiconductor Division (Mountain View, CA) has rolled out its latest ECL gate array, the CGA1ME12. This low-power, high-speed array is based on the BIT1 ECL process developed by Bipolar Integrated Technology Inc., and features a typical access time of 3.5 ns. It contains 4584 equivalent gates, 1280 bits of RAM, and 120 I/O cells. The core gates are laid in 12 contiguous rows with 18 first-metal routing tracks between each row. There are 1,320 transistors and an equal number of resistors in each row. At the end of each row there are bias cells that provide reference voltages and constant current sources for the internal logic. Gate transition times are approximately 300 ps/gate, and power runs at 300 µW/gate. Commercial versions of the new gate array start at \$150, with typical NRE charges running from \$40,000 to \$60,000.

#### **New RISC Machines**

Apollo Computer Inc. (Chelmsford, MA) is attempting to leapfrog competitors like Sun Microsystems and Hewlett-Packard by building the Series 10000 family of RISC-based computers with multiprocessing capabilities. Called the parallel reduced-instruction-set multiprocessing, or PRISM, architecture, the new design is based on co-equal integer and floating-point processors sitting on a 64-bit CPU bus. Large register files, a 128-kilobyte instruction cache and a 64kilobyte data cache help maintain singlecycle execution of all instructions, except for floating-point division, floatingpoint square-root calculations, and integer division. The result is a RISC CPU board that, according to Apollo, executes between 15 and 30 VAX MIPS.

By combining one to four processors on a 150-megabyte/s, 64-bit "X-bus," Apollo will create four workstations and four servers with a peak estimated processing power of 100 VAX MIPS for the four-processor systems. Users can plug as many as 128 MB of system memory into the X-bus, as well as disk drives and an eight-plane graphics system. The Xbus also has an interface to resident VMEbus and PC AT-compatible bus slots, so that the Series 10000 systems

# ARRAY FOR BICKIOS!

#### 180 MHz with low power.

It's cause for celebration. AMCC extends its lead as the high performance/low power semicustom leader with three exciting, new BiCMOS logic

arrays that optimize performance where today's designs need it most. In throughput (up to three times faster than 1.5µ CMOS).

Today, system designers look at speed, power and density. For

| Q14000 SERIES                  |             |                 |             |  |  |  |

|--------------------------------|-------------|-----------------|-------------|--|--|--|

|                                | Q2100B      | Q9100B          | Q14000B     |  |  |  |

| Equivalent Gates               | 2160        | 9072            | 13440       |  |  |  |

| Gate Delay* (ns)               | .7          | .7              | .7          |  |  |  |

| Maximum I/O<br>Frequency (MHz) | 180         | 180             | 180         |  |  |  |

| Utilization                    | 95%         | 95%             | 95%         |  |  |  |

| Power<br>Dissipation (W)       | 1.8         | 4.0             | 4.4         |  |  |  |

| I/O                            | 80          | 160             | 226         |  |  |  |

| Temperature<br>Range           | COM,<br>MIL | COM,<br>MIL     | COM,<br>MIL |  |  |  |

| *(2 loads 2 mm of metal)       |             | †Available soon |             |  |  |  |

good reasons. As CMOS gate arrays become larger and faster, designers can't meet their critical paths due to fanout and interconnect delay. As Bipolar arrays become larger and faster, power consumption becomes unmanageable. So AMCC designed a BiCMOS logic array family that merges the advantages of CMOS's low power and higher densities with the high speed and drive capability of advanced Bipolar technology. Without the disadvantages of either.

Our new Q14000 BiCMOS arrays fill the speed/power/ density gap between Bipolar and CMOS arrays. With high speed. Low power dissipation. And, mixed ECL/TTL I/O compatibility, (something CMOS arrays can't offer).

For more information on our new BiCMOS logic arrays, in the U.S., call toll free (800) 262-8830. In Europe, call AMCC (U.K.) 44-256-468186. Or, contact us about obtaining one of our useful evaluation

kits. Applied MicroCircuits Corporation, 6195 Lusk Blvd., San Diego, CA 92121. (619) 450-9333.

can support the same peripherals as Apollo's other computers.

The Series 10000 depends heavily on semicustom VLSI chips for its high performance. The RISC CPU chip set was designed by Integrated CMOS Technology Inc. (ICS), and the chips are being fabricated in the California foundries of VLSI Technology and the Japanese foundries of Toshiba Corp. Implemented with gate arrays having up to 256 pins and 40,000 gates, the chips use CMOS

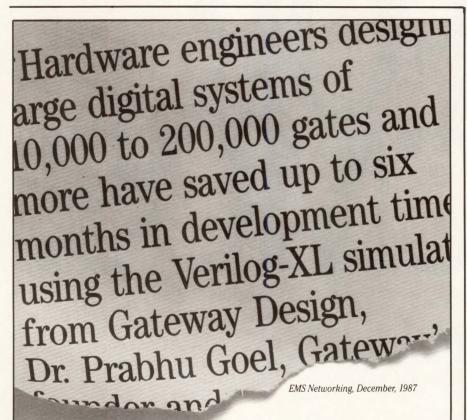

The single hardware-description language of the Verilog-XL<sup>®</sup> simulator spans the spectrum of logic design needs — from architectural/behavioral to gate/switch level. It's increasing the productivity of digital designers around the world. Verilog-XL can do the same for you.

Qualify for our thorough, interactive demonstration tape of Verilog-XL (only \$35) by calling 1-800-356-2631.

Gateway Design Automation Corporation, Six Lyberty Way, P.O. Box 573, Westford, Massachusetts 01886.

**CIRCLE NUMBER 6**

technology for the integer processor, floating-point register files, and memory management units. The floating-point multiplier and floating-point ALU are standard bipolar ECL chips from BIT.

The workstations will be "sourcecode-compatible" with Apollo's 68020based platforms, meaning Apollo-based application software must be recompiled to run on the DN10000. For that purpose, Apollo has developed compilers that use data-flow techniques to exploit the parallel operation of the components in the architecture.

Entry-level prices for the servers range from \$69,000 to \$129,900; prices for the workstations are \$10,000 more than the servers. Shipments of completed systems are expected in the third quarter of this year.

MIPS Computer Systems Inc. (Sunnyvale, CA) has unveiled its next generation of RISC chips, which could form the heart of PRISM-class computers. The new R3000 CPU, built with 1.5-µm CMOS technology, runs at 25 MHz and is specified at a sustained execution rate of 20 VAX MIPS. Its companion floatingpoint accelerator, the R3010, performs 7 MFLOPS for single-precision arithmetic and 4 MFLOPS for double-precision arithmetic, according to the Linpack benchmarks.

MIPS and its semiconductor partners, LSI Logic, Integrated Device Technology, and Performance Semiconductor, will be offering the chips by the end of the second quarter of this year. Applications of the new chips will benefit from an AT&T-blessed Applications Binary Interface (ABI), which will ensure that all R3000-based UNIX systems will be able to run the same software.

LSI Logic Inc. (Milpitas, CA) is positioning itself as the primary source for semicustom RISC machines by licensing the SPARC CPU from Sun Microsystems. As it is doing with MIPS's RISC products, LSI Logic will develop support chips and unique coprocessors for the SPARC architecture, as well as offering the CPU as a standard product and a "buildingblock" cell. The SPARC products will be available by midyear.

#### Two 64-bit FPUs

The WTL 3364 and WTL 3164 floating-Continued on page 66

# HOW TO SUCCEED IN ASIC PROTOTYPE VERIFICATION. FIRST TIME. EVERY TIME.

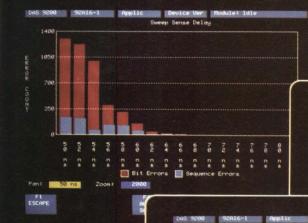

Applic Device Ver M

n Londi data.log

In

Timescale :

**Even first-time ASIC designers** can put Tek's new turnkey prototype test system to work, with total confidence in the results.

There are no languages to learn, no difficult setups, no complex interpretations, no incomplete answers.

You simply advance from one menu to the next. Use the same test vectors you developed during design. Debug with highly flexible, interactive pattern editing and timing characterization routines.

Test vector data from your logic simulator is translated and checked for tester compatibility automatically.

111101111011 00100 101110 111111101111 F3 UNDO FB

DAS 9200 92816-1

Test up to 50 MHz for atspeed analysis, with balanced resolution and accuracy for

F8 READ NAMES

unprecedented signal measurement quality. The test fixture adapts to your DUT quickly.

The system can be easily reconfigured to help with many other complex problems-including integrating your ASIC onto the circuit board.

To learn more about Tek's DAS9200 Personal ASIC Verification System, call: 1-800-245-2036 In Oregon, 231-1220

## This Is the House That Ross Built

oss Freeman started Xilinx Inc. to have a good place to work. A Silicon Valley veteran, he was looking for a place to hang his hat, to find some basic values: employee loyalty; a good, useful product; and pride in a job well done.

To keep Xilinx a nice place to work, Ross and the other managers interview prospective employees to find those who are "philosophically compatible." Certain types of people will flourish in the atmosphere, but not the "fast-buck types." He explains that "high-driving people who scream and bang the table wouldn't fit here."

Ross describes himself as a team player, serious about hard work, company pride, and the close knot of employees he calls "the tribe." He wants to keep the atmosphere within Xilinx pretty calm.

The strategy pays off, by the way. None of the technical staff, and only a handful of people in the whole company, have left in its four years of existence. This record gives Xilinx more continuity than most Silicon Valley companies and reduces the amount of recruiting effort needed. It also makes Ross Freeman proud.

He seems to be a man with broad ideals and high aspirations. As a physics student, he was interested in cosmology, including general relativity and the evolution of the universe. He received a bachelor's degree in physics from Michigan State University and a master of science degree in physics from the University of Illinois. As he approached his PhD thesis, though, he realized there was only a handful of jobs for those of his bent. Rather than start all over again in a new field, Ross decided to track his own path. The path led him, by way of the Peace Corps and West Africa, to a career in electronics.

Drawing on his experience with electronic equipment as a research assistant, Ross first worked at Teletype Corp. He moved to Zilog Inc., where he designed an enormously successful peripheral for the Z80 microprocessor—the serial I/O device, or SIO. He also helped design another popular peripheral, the serial communications controller (SCC). On the strength of such achievements, he worked his way up to director of IC engineering.

Ross found that he was not fulfilled by his rapid rise at Zilog. Although those times were heady ones at the company, technical management of 200 people didn't suit him. "When you have 200 people to manage, you're clearly not doing any useful work."

He began to consider alternatives. Consulting was one possibility, but he didn't like being drawn into sorting out other people's problems. "Whether you succeed or not, you don't get emotional benefit from it," he says. He decided that starting the right kind of company would give him the best work environment as well as long-term satisfaction.

At Xilinx, he has designed a product, the Logic Cell array (LCA), that he hopes will be as universally successful as his Z80 peripherals. The LCA, also referred to as a programmable gate array, reflects Ross's belief that one off-the-shelf product, if it does many things for many people, is better than a product that must be customized. "I'm an incorrigible standard-products person" he says.

Ross, Bernie Vonderschmitt, and Jim Barnett—all from Zilog—started Xilinx with only a concept and faith. They had a clear idea that something could be done and enough IC design experience to be sure they could make such a device. They didn't know exactly what type of part would emerge; "we just wanted to be the best company in the field of programmable gate arrays."

Ross also knew that he wanted to stay in the technical area. He didn't want to do the business-oriented tasks that other founders excel at. "I don't enjoy talking to the financial community," he says. "It takes a different mind set."

The part that resulted from his efforts used, for the first time, static RAM cells as the programmable elements in a userprogrammable logic device. SRAM technology was chosen because it generally leads EPROM or EEPROM technology by a full generation. However, Ross points out that Xilinx is a gate array company, not a CMOS gate array company. It will use more appropriate technology when one becomes available.

The LCA itself was not the only challenge. The design software required more engineering than the hardware. In fact, the first three engineers hired were software engineers. Xilinx is as much or more a software company as it is an IC company, because, as Ross puts it, "what good is the most wonderful IC in the world if you can't design with it?"

Despite his faith in his ideas, Ross claims he's not very good at predicting the future. For now, he's quite delighted to do technical work and management. With his tendencies toward hard work, loyalty, pride, and faith, he should enjoy his coming days in the house that he helped build. —David Smith

## SILVAR-LISCO Performance Redefined.

## For complex designs, HELIX is the "what if" simulator!

When designing large systems, printed circuit boards or VLSI/VHSIC chips, simulation becomes an invaluable aid. Logic, switch level and circuit simulators are excellent tools for validating design implementations. Silvar-Lisco's Helix Behavioral Simulator takes you one giant step further. In addition to design validation, system architects now can optimize the design itself through analysis of various implementation alternatives.

With Helix you can define and test your system concepts first. If the concept works, you move down to the register level. Then the gate level. Multi-level throughout. If it doesn't work, you can rethink the concept and probe Helix with additional design alternatives. In the end, you will get the best design. The first time.

Helix is a vital component of Silvar-Lisco's Architectural Design Series. Incorporating

design capture, simulation and design libraries, the Architectural Design Series gives you the competitive edge.

#### Be a design winner! Contact Silvar-Lisco today!

#### SILVAR-LISCO OFFICES

Corporate Headquarters 1080 Marsh Rd. Menlo Park, CA 94025 TEL: (415) 324-0700 WATS: 1 (800) 624-9978 TWX: 910-373-2056 FAX: (415) 327-0142.

*European Headquarters* Leuven, Belgium TEL: 32-16-200016 TWX: 221218 FAX: 32-16-236076

Far East Nihon Silvar-Lisco Tokyo, Japan TEL: 81-3-449-5831 FAX: 81-3-449-4040

**Architectural Design Series**

CAE Software products for electronic design.

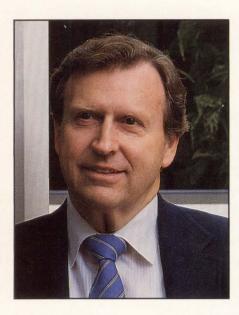

### Floorplanning for the Future

Dave Hightower, Calma Co., Santa Clara, CA

n the next-generation layout system, the floorplanner may well be the most important tool on the designer's workbench. The reasons for this are many: the geometric increase in integration; block-style layout in full-custom chips, standard cells, and gate arrays; and the typically poor performance of block placement tools.

We know that the level of integration (number of gates per die) increases exponentially, roughly doubling every two years. I know of 1.5-million transistor chips currently in the design stage; by 1990, therefore, our technology will permit 1 billion transistors on a single chip. With such high levels of integration, achieving acceptable performance and die size requires very careful attention to placement and routing at all levels of the hierarchy. For integrated circuits in the range of 160,000 to 250,000 square mils, an increase in size of 5% to 10% is at least serious and probably unacceptable.

A powerful floorplanner is vital in helping control die size. Even with smaller designs having large blocks, a good planning tool used at the beginning of the design and at each level of the hierarchy can have a significant impact on die size, performance, and cost.

More and more full-custom chips are

designed using hierarchy and block layout styles. The engineers designing these chips would like to have access to good automatic layout; however, since fully automatic block placement probably lags all the rest of CAD technology in effectiveness, at least some manual intervention is required in the beginning of the design process. Furthermore, this manual intervention also includes analysis of performance, I/O assignment, power consumption, and bus routing. For manually designed blocks, the designer has an additional degree of freedom-the aspect ratio. With a good floorplanner, the designer can analyze trade-offs intelligently, before committing himself to a particular layout.

Although hands-off standard-cell and gate array designs are routine, some designs require careful placement of certain structures to perform correctly or, in many cases, to attain successful routing. Many standard-cell designs today have microprocessor parts, large memory blocks, or other large structures. These blocks are difficult to handle well automatically. Furthermore, there is increasing demand for implementing a portion of the design as one or more custom blocks and the rest as standard cells; I believe this design style will become more prevalent within a few years. All these design styles may need careful placement and analysis to achieve the target cost and performance goals.

Even with large gate arrays, where typically we think of hands-off layout, a floorplanner can help predict exactly which gate array size is appropriate for a particular design. A few hours on a floorplanner can save a gate array designer from having to go to the next larger size of gate array, resulting in a significant reduction in recurring cost.

For all these reasons, a sophisticated, highly interactive floorplanner is required. Even the "automatic" placement tool in the floorplanner should be interactive; that is, it should have a "human subroutine'' through which it calls the operator from time to time to solve some local problem and then continues searching for the global solution.

A "super"-floorplanner will have other features as well. Recursive block size and die size estimation will permit progressive improvement of a layout. Naturally, the tool should permit both interactive and automatic I/O and block terminal assignment. There should also be interactive and automatic "routing" for adding the area needed for bus communication between the large blocks.

We can foresee more advanced capabilities than are commonly available in current floorplanning systems. One possibility is a "hierarchy rearranger," to optimize the input hierarchy before layout is begun. Traditionally, the arrangement of hierarchy in the floorplanner is fixed; attempts to automate hierarchical definition have so far been mostly unsuccessful. There should also be suitability measures for channel generation or slicability. The designer could then participate in creating the most optimal hierarchy and routing arrangement. At present, the designer has no assistance in these areas.

Conventional tools should be included at the back end of the design suite, including automatic or semi-automatic placement tools; block movement tools; standard-cell movement tools; a prerouting congestion analysis program; and placement evaluation tools, with wiring length estimates tied to delay analysis.

Consequently, the next-generation floorplanner will be an extremely important analytic tool. It will no doubt be integrated with many other analytic tools, to provide a vital front-end analysis tool set that will virtually guarantee a successful layout.

David Hightower has been the manager of advanced systems development at Calma since October, 1986. He has been involved in IC CAD since 1966.

## Conference Preview The 1988 Custom Integrated Circuits Conference

The Custom Integrated Circuits Conference (CICC) comes home to Rochester, NY, this month for its tenth anniversary. Fittingly for this occasion, the keynote address is "From Childhood to Adolescence—The ASIC Industry Comes of Age," to be given by Douglas Fairbairn, vice president of VLSI Technology Inc. and general manager of its ASIC division. ASICs, which were just finding their way into leading-edge applications at the beginning of this decade, are now considered a necessity for almost every new product. Would any self-respecting company announce a new workstation or graphics engine in today's market without also touting the number and complexity of the custom chips that make the product's breakthrough performance possible?

This year's CICC will offer a record-setting 168 papers covered in 25 technical sessions, plus four evening panel sessions and a repeat of last year's successful "New Product Announcements" session. The panels will cover some provocative topics such as the Davids versus the Goliaths in the ASIC business, the pros and cons of fast turnaround for ASICs, various trade associations and groups tied to the semiconductor industry, and the good and the bad of different semiconductor technologies. The new product session will be held Monday evening and feature eight companies, each with 15 minutes to unveil its latest offering.

First and foremost, though, the CICC will continue to emphasize its traditional role as the conference of record for application-specific ICs. A total of 19 of the sessions will be devoted to ASICs and the tools for designing them: 7 are pegged for design automation tools and 12 for the actual custom and semicustom ICs. Four of the remaining 6 sessions are devoted to manufacturing, testing, and packaging issues. In addition, reliability will have its own session, and a hot new topic, neural networks, will debut this year.

#### Chips and More Chips

The Thursday morning session devoted to high-density, high-performance gate arrays will cover devices with up to 12,000 gates for bipolar ECL technologies and up to 237,000 gates for CMOS designs. A. Hui et al. of LSI Logic Corp. will describe a compacted sea-of-gates array fabricated in a 1- $\mu$ m HCMOS technology. The 237,000-gate array occupies a 1.5cm<sup>2</sup> die and delivers 400-ps gate delays.

Also scheduled for the same session is a presentation by K. Sawada et al. of Toshiba Corp.'s Semiconductor Device Engineering Laboratory that should elicit much interest. Their paper will describe a sea-of-gates chip the same size as LSI Logic's but with only 72,000 gates. However, the gates occupy only two thirds of the chip's real estate, and the remaining third of the chip sports a complete 1-megabit dynamic RAM. The typical delay time for the gate array is 400 ps and the worst-case access time for the DRAM is 60 ns.

On the bipolar front, B. Coy et al. of Applied MicroCircuits Corp. will talk about their 12,000-gate ECL/TTL gate array with 100-ps gate delays. The chip uses three-layer metallization and a sea-of-gates architecture to achieve over 95% cell utilization. The power dissipation is less than 10 W.

"Application Specific Memories," a Tuesday morning session, will cover such topics as consumer EPROMs and RAMs, large EEPROMs for ASICs, and a unique 2-bit-per-cell dynamic RAM. Also at the session, T. Maruyama et al. of Toshiba will discuss a low-power EPROM with a wide operating-voltage range for consumer products, particularly batterypowered systems. A demonstration microcontroller running at 32 kHz and 3 V and incorporating the new EPROM structure consumes only 90  $\mu$ W.

A dynamic RAM targeted at TV and other video applications will be described in a paper by Y. Murakami et al. of Sharp Corp. The  $185K \times 6$ -bit RAM stores one NTSC TV field with 6-bit quantitization. The 1.2- $\mu$ m dual-metal CMOS device has a 60-ns cycle time.

National Semiconductor Corp. has developed an 8-bit parallel EEPROM megacell suitable for large EEPROM arrays, and B. Carney et al. will discuss some examples of the use of the cell in a variety of ASIC applications. A four-level dynamic RAM cell that stores 2 bits per cell will be described by T. Furuyama et al. of Toshiba. They will also describe an experimental 1-Mb array composed of 512K cells with a 170ns access time that demonstrates the new technology.

Also on the agenda for Tuesday morning is a session entitled "Drivers and Interfaces" that covers everything from a smart biCMOS driver for 400-dot-per-inch thermal printing heads to an NMOS driver capable of modulating laser diodes at up to a 1.7-gigabit/second rate. The laser driver paper, written by K.R. Shastri et al. of AT&T Bell Laboratories, will also describe the 0.75- $\mu$ m NMOS technology used to fabricate this driver. The chip can deliver adjustable constant amplitude-modulation current pulses of up to 50 mA with rise and fall times of 200 to 300 ps over a wide range of supply and input voltages as well as operating temperatures.

K. Tsubone et al. of Oki Electric Industry Co. will talk about the thermal printer driver chip that consists of a 128-bit shift register, a dot-history control circuit (DHCC), and a 128-

#### Custom Integrated Circuits Conference

Rochester Riverside Convention Center/ Holiday Inn-Genesee Plaza Rochester, NY, May 16-19, 1988

| ίe | V |  |  |

|----|---|--|--|

|    | ' |  |  |

|    |   |  |  |

ł

Design tools

Chips and circuits

Manufacturing and test

| Holiday Hall<br>(Holiday Inn)                                                                                      | Windsor Room<br>(Holiday Inn)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 101 Meeting Rooms<br>(Convention Center)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Lilac Ballroom North<br>(Convention Center)                                                                           | Lilac Ballroom South<br>(Convention Center)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Welcome/Opening<br>Remarks, Technical<br>Program, Keynote<br>Address                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                                                                                                     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| VLSI Design<br>Environments &<br>Synthesis<br>Chairman: Samuel N.<br>Stevens<br>Co-Chairman: Ronald<br>T. Jerdonek | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Advances in<br>Simulation Methods<br>& Tools<br>Chairman: Gregory W.<br>Ledenbach<br>Co-Chairman: John<br>Barnes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Application Specific<br>Memories<br>Chairman: K.<br>Venkateswaran<br>Co-Chairman: Ken Au                              | Drivers & Interfaces<br>Chairman: Jagdish C.<br>Tandon<br>Co-Chairman: Wesley<br>A. Vincent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |