600 Community Drive, Manhasset, New York 11030

NBWS

NEWS

NUN

## VLSI Systems Design

Bulk Rate U.S

Postage

Publications Inc.

\$50.00

NEWAR

NEWIG

NEWDO

GMAN

#### 1988 SENTERSOR DESIGNERS DESIGNERS

PUBLICATION

CMP

This is the stuff reputations are built on.

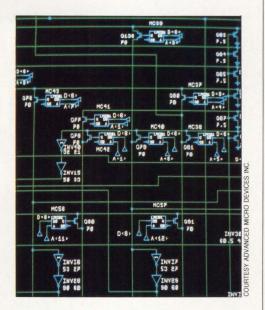

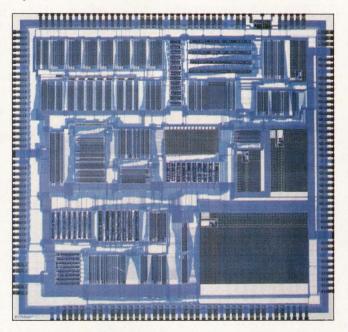

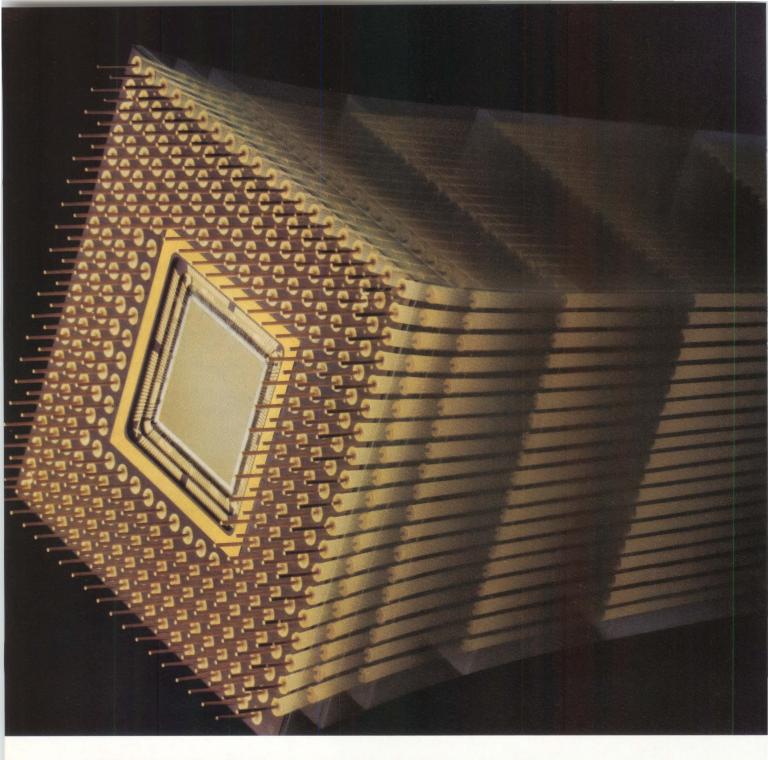

A cell design with 100,000 gates. More than 1000 library elements. 2MB of memory. And sub-micron

HCMOS technology.

You can search high and low, but there's only one place in the world you can find a chip of such staggering complexity.

LSI Logic.

Designs like this are precisely why we're the #1 domestic ASIC supplier with more than 4,000 working cell and array-based designs in the field.

And why our Modular Design Environment (MDE)<sup>™</sup> software is the best foundation for building killer cells.

MDE is the industry's most advanced design software for ASICs. It arms you with the capability to build today's most sophisticated cellbased designs. Easily. And with the smallest possible die size.

Besides MDE, LSI Logic delivers more than 400 LSI and VLSI building

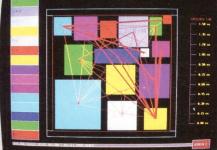

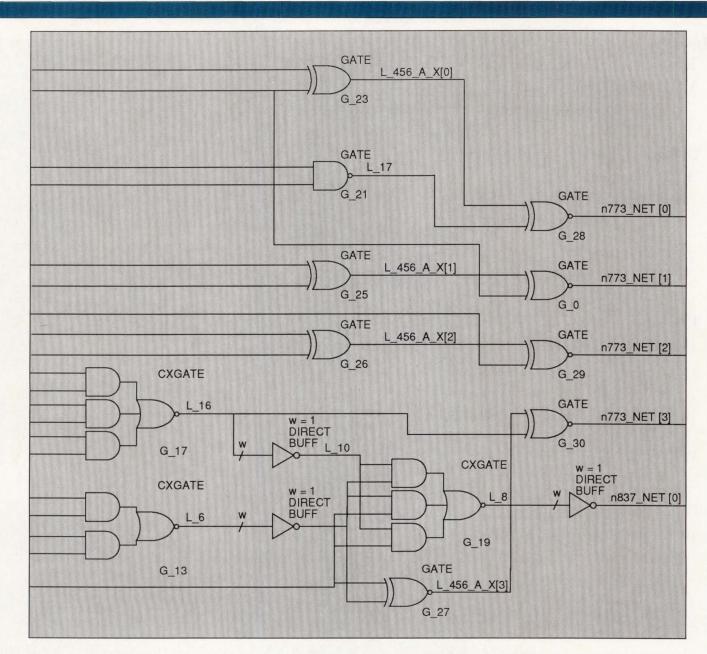

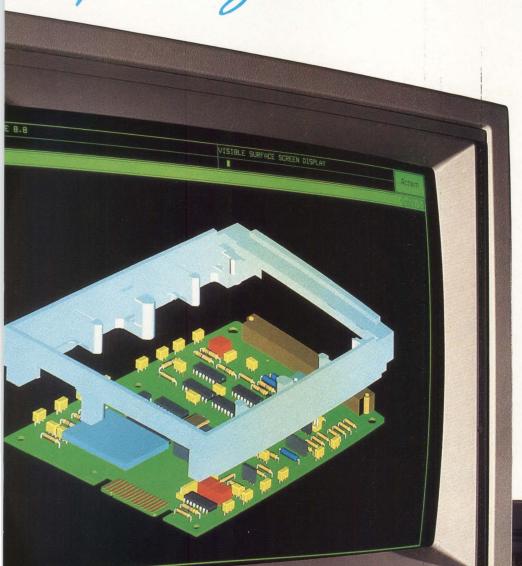

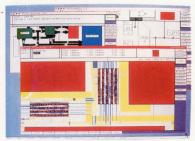

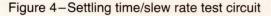

High complexity Cell-Based ASICs require advanced tools like the MDE chip floorplanner to optimize delays and verify performance prior to layout.

blocks, including 16 and 32-bit microprocessor cells and industry-standard processor and peripheral functions; the longest list of SSI and MSI functions; and memory compilers to

> develop exactly the RAM or ROM your chip requires.

> And if your application calls for lower densities, that's covered, too. Because LSI Logic has more cost-effective cell-based solutions than you can imagine.

> No matter what kind of Cell-Based ASIC you

build, LSI Logic will deliver a fullytested prototype in as little as 4 weeks.

All in the production quantities you want, thanks to our advanced worldwide wafer fabrication, assembly, and test facilities.

So find out more about LSI Logic's Cell-Based ASICs by calling the sales office nearest you.

After all, we can help you make a killing.

LSI Logic Sales Offices and Design Resource Centers: Scottsdale, AZ 602-951-4560, Milpitas, CA 408-433-8000, San Jose, CA 408-248-5100, Irvine, CA 714-553-5600, Sherman Oaks, CA 818-906-0333, Denver, CO 303-756-8800, Altamonte Springs, FL 305-339-2242, Boca Raton, FL 305-395-6200, Norcross, GA 404-448-4898, Chicago, IL 312-773-0111, Bethesda, MD 301-897-5800, Waltham, MA 617-890-0161, Ann Arbor, MI 313-769-0175, Minneapolis, MN 612-921-8300, Bridgewater, NJ 201-722-7522, Poughkeepsie, NY 914-454-6593, Raleigh, NC 919-783-8833, Worthington, OH 614-438-2644, Beaverton, OR 503-644-6697, Trevose, PA 215-638-3010, Austin, TX 512-338-2140, Dallas, TX 214-788-2966, Bellevue, WA 206-822-4384, Calgary, Alta 403-262-9292, Paris, France 33-1-46212525, Israel 972-3-403741/6, Milan, Italy 39-39-651575, Tokyo, Japan 81-3-589-2711, Seoul, Korea 82-2-785-1693, Nidau/Biel, Switzerland 032-515441, Bracknell, United Kingdom 44-344-426544, Munich, West Germany 49-89-926903-0. © 1988 LSI Logic Corporation. Modular Design Environment and MDE are trademarks of LSI Logic Corporation.

## VLSI Systems Design

#### A CMP Publication EDITORIAL DIRECTOR Robert W. Henkel EDITOR-IN-CHIEF Roland C. Wittenberg MANAGING EDITOR Mike Robinso SENIOR EDITOR Bob Cushman SOLID STATE EDITOR Roderic Beresford WESTERN REGIONAL EDITOR David Smith DIRECTORIES EDITOR Michelle A. Losquadro EDITORIAL ART Marie D'Ippolito, Design Director Catherine McHale, Composition Laurie Kaufman, Cover & Layout Dawn Cammarata, Layout Tom Holmes, Robyn Stabulas, Vilma Baston, Graphics Sharon Anderson, Art Director EDITORIAL PRODUCTION Patricia L. Gaynor, Sr. Production Editor Deborah Porretto, Ass't Production Editor

MANUFACTURING Stephen Grande, Director of Manufacturing Marie Myers, Production Manager James Pizzo, Production Supervisor Jane Mahoney, Asst. Production Supervisor

> PUBLISHER Norm Rosen

VLSI SYSTEMS DESIGN (ISSN 0279-2834) is published monthly with an extra issue in May by CMP Publications, Inc., 600 Community Drive, Manhasser, NY 11030, (516) 562-5000. VLSI SYSTEMS DESIGN is free to qualified subscribers. Subscriptions to others in the US: one year \$60.00, two years \$95.00; Canada and Mexico: one year \$90.00, two years \$95.00; Europe, Central and South America: one year \$120.00, two years \$225.00. Asia, Australia, Israel and Africa: one year \$100.00, two years \$285.00. Second-class portage paid at Manhasser, NY and additional mailing offices. POSTMASTER: Send address changes to VLSI SYSTEMS DESIGN, Box No. 2060, Manhasser, NY 11030. Copyright 1988, CMP Publications, Inc. All rights reserved.

CMP ELECTRONICS GROUP Kenneth D. Cron Vice President/Group Publisher Electronic Buyers' News Electronic Engineering Times VLSI Systems Design

CMP PUBLICATIONS, INC. 600 Community Drive Manhasset, New York 11030 (516) 562-5000

UND/102-3000 Electronic Bores, Decomputer Systems News, VISI Systems Design, Computer Systems News, UNIX Computer Reseller News, VARDISINESS, UNIX Communication, Businers Travel News, Communication, Businers Travel News, Tour & Travel News, Long Island Monthly, HealthWeek

Michael S. Leeds, President Pearl Turner, Vice President/Treasurer Daniel H. Leeds, Vice President

Lilo J. Leeds, Gerard G. Leeds Co-Chairpersons of the Board

#### **INTRODUCTION TO THE GUIDE**

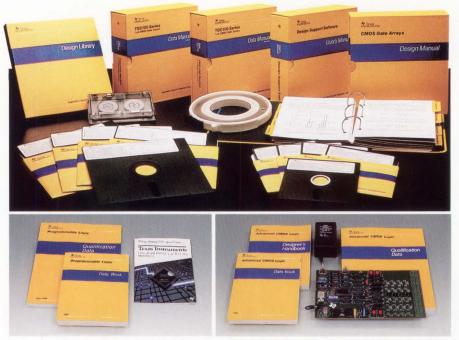

ith the third annual *Semicustom Design Guide*, we continue to provide in-depth technical articles on the range of semicustom IC technologies and the CAE tools and methodologies required to exploit fully those technologies. Backing up the articles are extensive and detailed listings of semicustom vendors, products, and design centers.

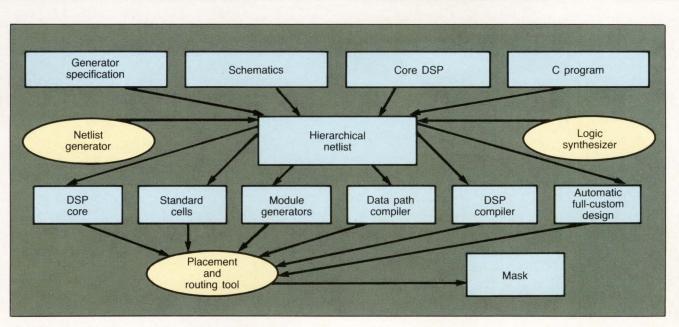

Leading off the *Guide* are two articles on state-of-theart aspects of gate arrays. Next comes an article that approaches the question of semicustom from the point of view of a particular application area—digital signal processing; it argues that, for now, designers are best served by a hybrid approach that includes DSP cores, standard cells, logic synthesis, and silicon compilation (module generation). Then an update covers the recent

#### SEMICUSTOM TECHNOLOGIES 7

GARNERING THE GATES IN HIGH DENSITY ARRAYS 8 Ernest L. Meyer

HIGH-SPEED GATE ARRAYS: CONSIDERING THE OPTIONS 24 Ron Cates

A HYBRID APPROACH TO APPLICATION-SPECIFIC DSP DESIGN 32 Howard Moscovitz

PROGRAMMABLE LOGIC UPDATE 42 Ernest L. Meyer

#### DESIGN TOOLS & METHODOLOGIES 53

THE ROLE OF LOGIC SYNTHESIS IN SILICON COMPILATION 56 Misha R. Burich

VHDL FOR ASIC DESIGN AND VERIFICATION

64

Rick Sullivan and Lisa R. Asher

64

ADVANCED MODELING TECHNOLOGIES FOR LOGIC SIMULATION 74 William B. Fazakerly and Robert P. Smith

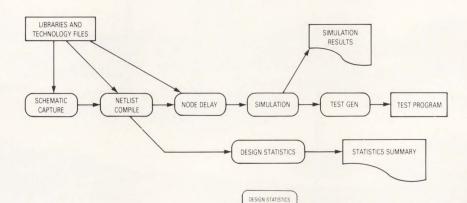

LINKING DESIGN AND TEST FOR ASIC PROTOTYPE TEST DEVELOPMENT 86 Eric Archambeau, Teresa Butzerin, and Dave Roth flurry of developments in programmable logic, including "user-programmable gate arrays."

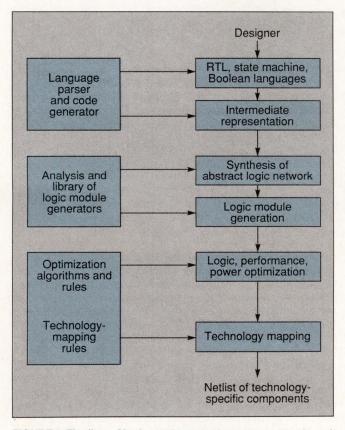

On the tools side, probably nothing has been hotter this year than logic synthesis and VHDL. Section II starts with a consideration of logic synthesis technology embedded in a silicon compilation design system (something that is also touched on in the DSP design article) and a description of the use of VHDL for behavioral description and verification. The following article addresses the need for more accurate timing models for logic simulation, and the last one tackles the problem of developing tests for verifying ASIC prototypes.

We conclude with our set of directories and the 1987 subject index to *VLSI Systems Design*.

Mike Robinson

#### **III DIRECTORIES 99**

Guide to the Directories 100 Gate Array and Cell Library Vendor Profiles 100 Directory of Gate Arrays 106 Directory of Cell Libraries 117 Directory of Programmable Logic Devices 125 Gate Array and Cell Library Vendor Contacts 128 Directory of ASIC Design Centers 130

#### IV REFERENCES 138

VLSI Systems Design Subject Index 1987 139 Advertiser's Index 143

Guide to Data Sheets 144 Data Sheets 145

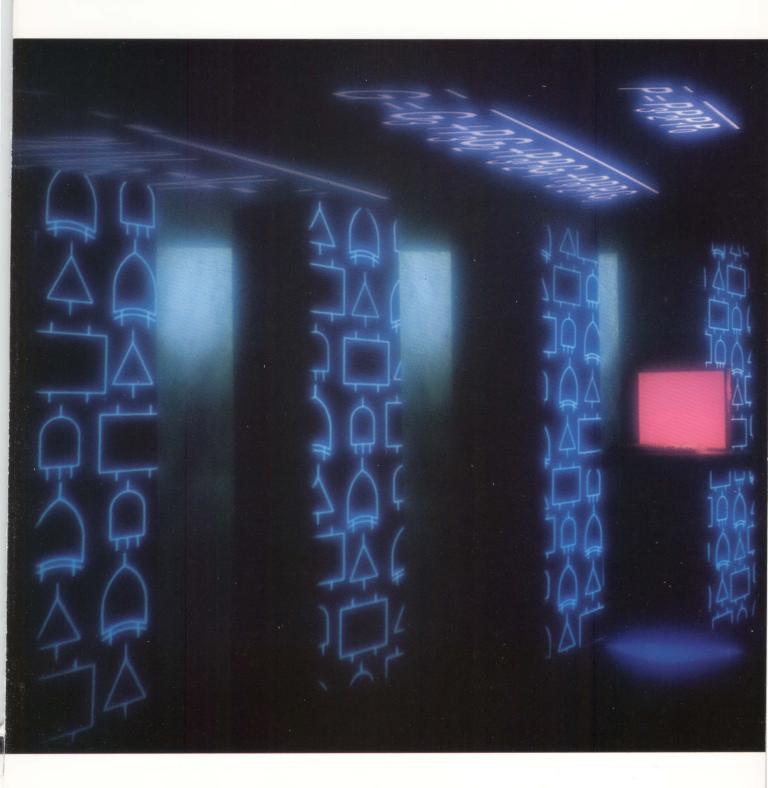

COVER ART COURTESY OF NATIONAL SEMICONDUCTOR CORP.

## DO YOU HAVE WHAT IT TAKES TO MAKE IT BIG IN ASICS?

Not long ago, designing with more than 170 design accelerator is seamlessly inte-ASICs wasn't even grated with the schekits supplied by 70 different ACCELERATED vendors. So you can build propart of your job. matic, so you can locate ASIC DESIGN ductivity instead of libraries. Now it's the and correct design Which may explain why problems interactively. part everyone's counting on. more MegaLOGICIANs are That means faster That's where debugging and more in use today than all other Daisy comes in. time to improve accelerators combined. other Cadnetix Daisy CAE tools the quality of your Speaking of combining, you are used by more design. Plus ASIC designers than no other accelerator any other CAE workstations. is as well supported, Because from schematic creation through post-layout Daisv 53% 5,000 Zvcad 11% Simulation accelerator market share. Source: Prime Data, 1985 and 1986 unit shipments. simulation. Daisy has what it takes to keep ASICs on time and on budget. For example, our MegaLOGICIAN<sup>™</sup> simulation

© 1988, Daisy Systems Corporation. MegaLOGICIAN is a trademark of Daisy Systems Corporation. \*Based on minimum 10x performance improvement compared to 32-bit workstations. Source for design kit estimates: VLSI Systems Design's Semicustom Design Guide, 1987. can share a MegaLOGICIAN with a network of our 386based desktop workstations, for a high-powered low cost ASIC design environment.

And that's just the beginning. With our library of more

than 4,500 systemlevel components, you can include your ASIC in complete "real world" system simulations to ensure that your designs will be ready for production, instead of revision.

All of which makes Daisy today's choice for no-sweat ASIC success.

But what about tomorrow? Gate counts are on the rise. If your tools run out of steam at 5,000 gates, so could your future.

No problem. Our ASIC design tools glide through 20,000DEAD

breathing hard. In fact, new design kits already support arrays of over 100,000 gates.

gate designs

without even

So you'll never have to worry about hitting a dead-end.

But don't take our word for it, listen to what Rockwell and other industry leaders have to say. For a free copy of "Making It Big In ASICs" call Daisy at 1 (800) 556-1234, Ext. 32. In California, 1 (800) 441-2345, Ext. 32.

European Headquarters: Paris, France (1) 45 37 00 12. Regional Offices: England (256) 464061; West Germany (89) 92-69060; Italy (39) 637251.

## Harris Guarantees ASICs To Specs After Irradiation!

## There... We Put It In Writing!

We're hard-liners about reliability in rad-hard ASICs. Including MIL-STD 883C and to Class S.

Hey...it happens to the best of 'em... your rad-hard ASIC design's first pass requires first aid!

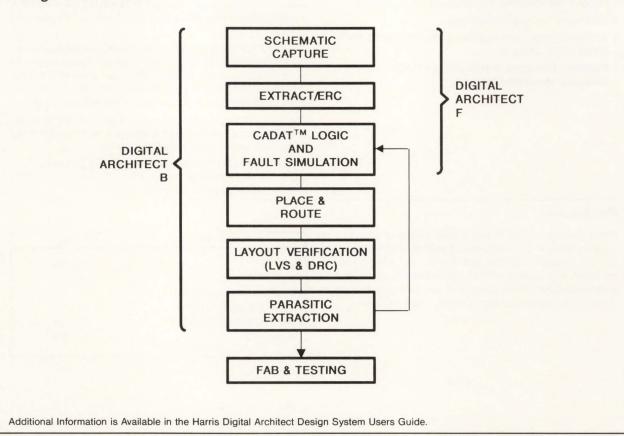

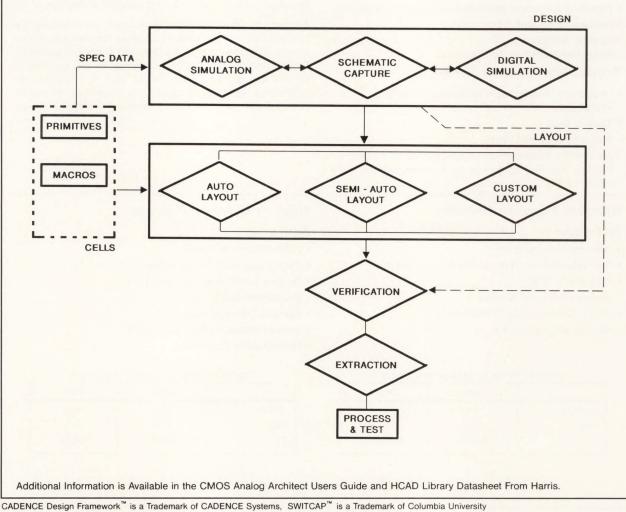

For better results, avoid rigid design systems that lock you into the wrong solution and keep you there. Come to Harris; nobody offers you more frontend flexibility.

- Advanced rad-hard library...Basic gates, 54XX equivalents, 80C86 peripherals (cells and macros you can intermix to enhance design), proprietary data communications functions.

- Broad workstation support...Simulations include both pre- and post-radiation performance models. Libraries are fully supported on the UNIX-based

Trademarks, Daisy: Daisy Systems Corp. Mentor: Mentor Graphics  $\textcircled{\sc 0}$  1988, Harris Corporation

Harris toolset. Daisy<sup>™</sup> and Mentor<sup>™</sup> platforms also supported; Silicon Compilers due soon.

• Guaranteed parametrics...Harris can guarantee your ASICs to specs after irradiation exceeding 1 megarad.

SICS

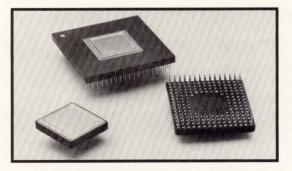

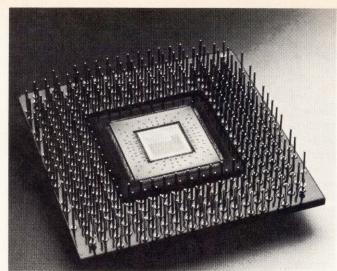

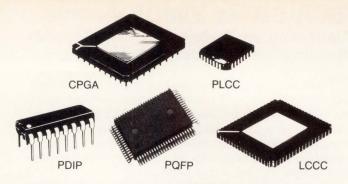

• Packaging options...Select from ceramic DIPs, chip carriers and pin grid arrays; screenings to Class S standards.

So what does it all mean? More ASIC design options. Less design risk. For a faster time to market, it's time to call Harris Semiconductor.

> In U.S. phone 1-800-4-HARRIS, Ext. 1910 or (407) 729-4151. In Canada: 1-800-344-2444, Ext. 1910.

**CIRCLE NUMBER 2**

## SEMICUSTOM TECHNOLOGIES

#### GARNERING THE GATES IN HIGH-DENSITY ARRAYS

#### Ernest L. Meyer

8

Changes in gate array technology have opened up new vistas for systems designers who seek high performance and high levels of integration without incurring exorbitant engineering expenses.

#### 24 HIGH-SPEED GATE ARRAYS: CONSIDERING THE OPTIONS

Ron Cates, Vitesse Semiconductor Corp.

To meet the needs of high-performance systems, semicustom designers now have a choice of silicon-based ECL and gallium arsenide, and GaAs has stepped up to enhancement/depletion-mode technology.

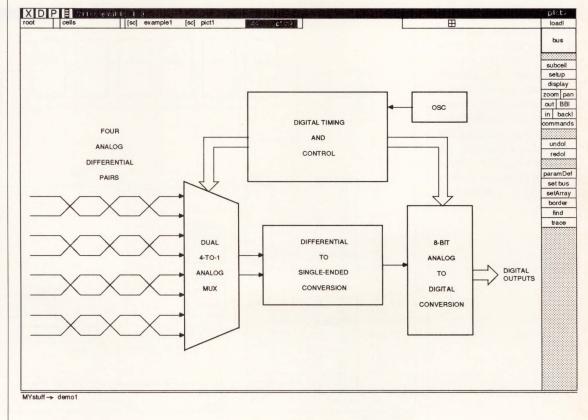

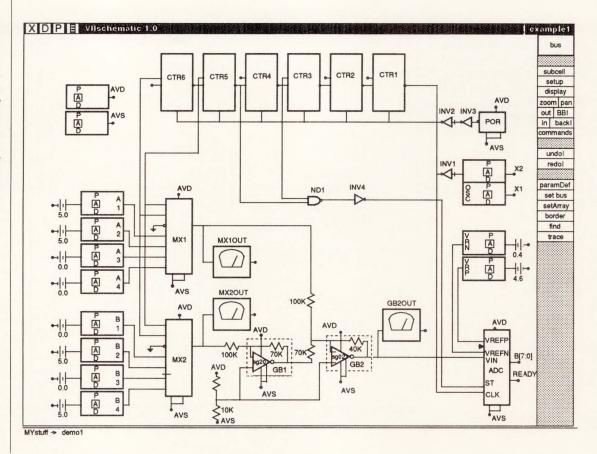

#### 32 A HYBRID APPROACH TO APPLICATION-SPECIFIC DSP DESIGN

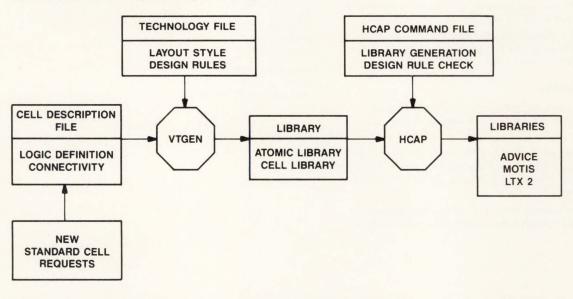

Howard Moscovitz, AT&T Bell Laboratories

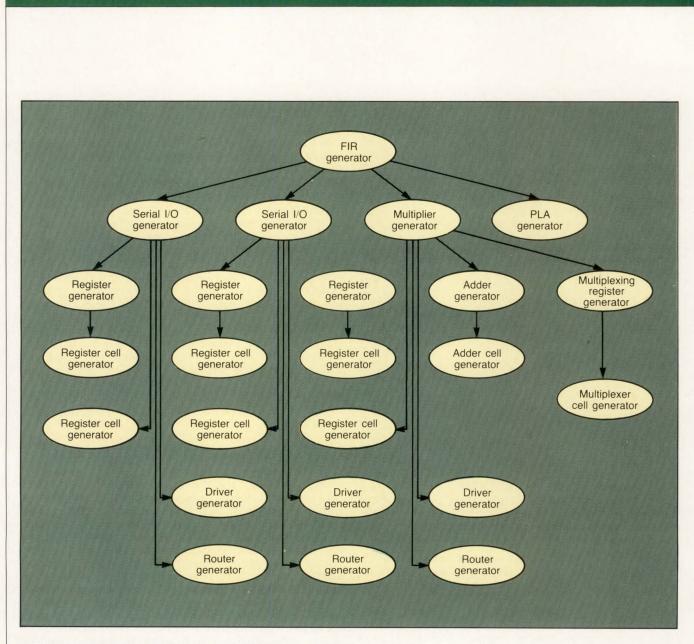

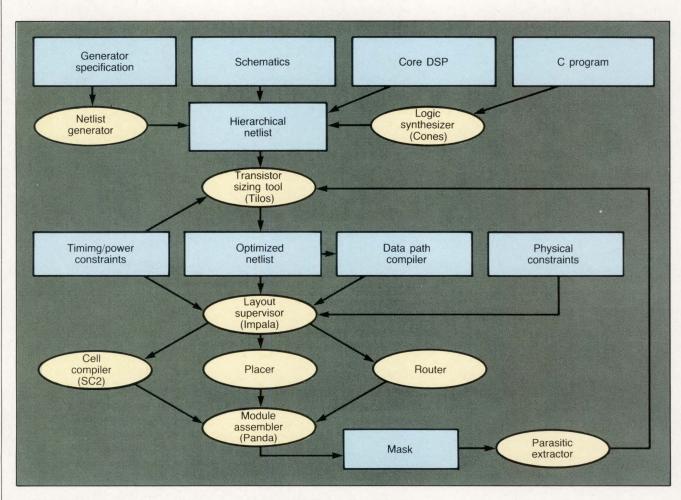

Designers of application-specific DSP integrated circuits have a variety of design alternatives available to them, from traditional schematic capture and standard-cell design to logic synthesis, module generators, data path compilers, and DSP CPU cores. No single tool satisfactorily handles all the applications.

#### 42 PROGRAMMABLE LOGIC UPDATE

#### Ernest L. Meyer

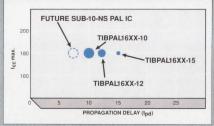

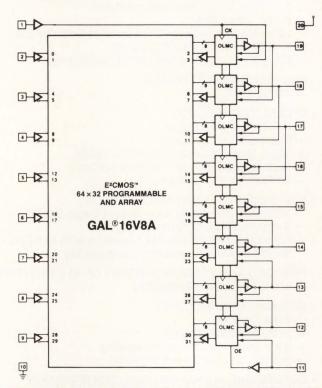

Recently, a wave of new, improved, and faster programmable logic chips, includer userprogrammable gate arrays, were introduced, promising to expand the usefulness of programmable logic technology.

1988 SEMICUSTOM DESIGN GUIDE 7

## GARNERING THE GATES IN HIGH-DENSITY ARRAYS

Ernest L. Meyer, Campbell, Calif.

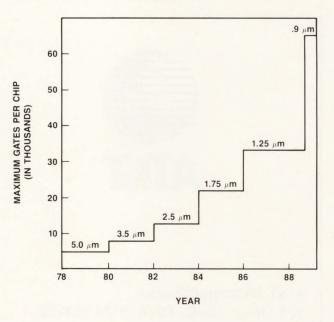

The past decade has seen a virtual implosion of IC functionality. Even a gate array can now hold 100,000 twoinput NAND gate equivalents—10 times as much integration as was possible even three years ago—and the manufacturing and design innovations for high-density arrays are increasingly counterbalancing the area, performance, and cost barriers traditionally associated with gate array implementation. In addition, those innovations are applicable to all array sizes and are expected to "trickle down."

Two particular techniques are especially significant: the use of triple-level metal (TLM) and the omission of empty wiring channels from the die (channelless, channel-free, or sea-of-gates arrays). With TLM, wires account for proportionally less area and transistor density increases. Parasitic delays are not only smaller on average, but also more predictable. When applied to sea-of-gates array architectures, TLM is yielding utilizations of 90% and higher. However, computer-aided design is not coping easily with these newer technologies. In particular, the increased density and large gate counts intensify the problems of power distribution and critical path constraints. New techniques for placement and routing are being tried out on these very large gate arrays.

#### **TRACKING DOWN THE PROBLEM**

Having chosen a semicustom approach, most of the arguments cited against gate arrays arise from their size. Wasted silicon area results from the use of one common base for a number of different functions. Not only might the die size influence final package cost, but also a larger chip will slow down the logic. The less dense the chip, the longer the average wire length. Longer wires add capacitive delays that introduce severe design problems; these problems center not so much on the longest delay, but rather on the range of delays. The impact of die size on performance is particularly strong in gate arrays, where a computer decides the transistor and wire arrangement with algorithms that solve the topological wiring problem, not necessarily the electrical performance problem.

Net lengths display a "right-biased" distribution, with the average net length exceeding the median. Also, the average net length deviates further from the median on the high side as fan-out increases. This distribution poses grim problems for the designer. Simulating with a worstcase delay is highly unrealistic, as only a small number of nets have that delay figure. Especially for high fan-outs, simulating with an average delay may not be much better, because the distribution is skewed to the right. Using a median delay will not allow for the worst-case paths—on one out of ten occasions, approximately, the actual delay will be more than three times the median delay.

High-density arrays are therefore attractive mostly for their advantageous wire delay distribution. The transistors may have much the same speed and the average wire delay may not be much smaller. Even halving the average wire delay does not typically increase speed by more than 10%. However, if the chips are smaller, there are fewer critical paths (whether anticipated or not). Because the longest possible path is now also shorter, there also are fewer restrictions on gate placement and routing. Layout software therefore struggles less to complete the design within the same constraints. In fact, according to manufacturers, the computer time required to complete a highdensity array layout is reduced and that reduction more than offsets the costs incurred by the lower yield of a larger die. At the same time, the wiring delays are more predictable, making the technology more attractive to users.

#### SHRINKING

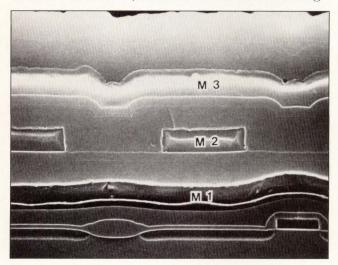

Shrinking the fabrication process design rules is the most obvious way to reduce a chip's size. However, as transistors shrink below  $1.25 \ \mu$ m, the impact of minimum feature size on gate array density becomes much less important. More significant are the minimum wire width and the isolation distance between adjacent wires. Adding these two numbers gives the metal pitch, the minimum possible distance between the centers of two adjacent wires. The pitch can never be as small as the minimum feature size: the transistors and polysilicon wires under the metal track make the surface too bumpy for an even deposition of metal on top (Gulett, 1985)

More recent IC processes use planarization to smooth the surface between each deposited layer. In planarized processes, the wafers are heated up between metal depositions so that the deposited intermetal dielectric flows and tends to "soften" abrupt steps in the underlying layers, providing a smoother surface for subsequent layers.

Planarized processes make it possible to forge much narrower wires, but if the wires are too small, electromigration can fuse out the metal. In metal migration, excessively high current density causes a gradually accelerating movement of the metal atoms in the direction of the current, until the wire wears out.

Metal migration places a lower limit on metal track width. The dangerous current density for aluminum is about 2 mA/ $\mu$ m<sup>2</sup> of the wire's cross-section. Wires cannot be more than 0.5  $\mu$ m thick without making the surface too irregular. A typical high-speed process, with a 200-MHz toggle frequency and a 2.5- $\mu$ A/MHz gate transient current, creates a 0.5-mA drive. A pure aluminum signal wire thus cannot be less than 1  $\mu$ m wide without self-destructing.

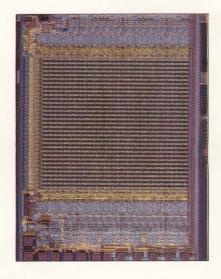

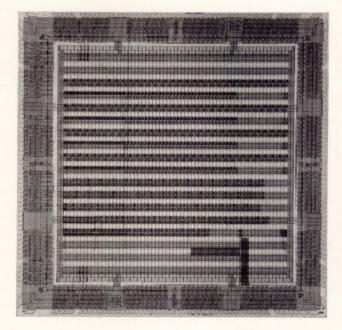

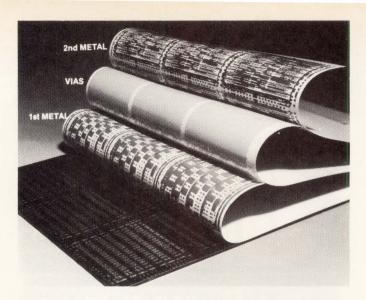

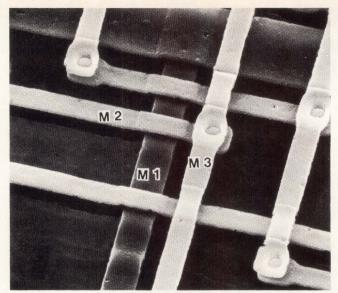

FIGURE 1. The quality of the planarization is shown in a cross section of a Motorola triple-level-metal (TLM) die.

Since it is not possible to compact wires any further in the horizontal direction, vendors are applying the skyscraper principle and going up. Three-level metal (TLM) has been used for power distribution in a number of bipolar processes, in which the pitch of the third metal level has to be much wider than those of the first two levels, because the third metal level is deposited on a surface with even more irregularities.

Fujitsu was the first company to apply the same principle to a CMOS gate array family, using a 4.5- $\mu$ m pitch on first metal and a 9- $\mu$ m pitch on the third metal layer with a 1.5- $\mu$ m process. Fujitsu has been shipping TLM CMOS since 1985.

Shortly after, Hughes Aircraft extended its planarized process to permit the use of 4- $\mu$ m-wide wires on all three metal layers. In such planarized processes, the reduced metal pitch that is possible on the second and third levels allows even the third level to be used for signal distribution. At about the same time, Toshiba started shipping TLMarrays. Recently, NEC started shipping TLMarrays, with maximums of about 40,000 and 75,000 available gates.

At the time of writing, Motorola has TLM arrays at least in

prototype, and Hitachi and LSI Logic are reported to have TLM prototypes. All three companies may have productionquantity TLM arrays by the fourth quarter of this year; Motorola's highly planarized TLM process is shown in Figure 1. Some other companies, including SGS-Thomson, Texas Instruments, and VLSI Technology, are likely to follow suit.

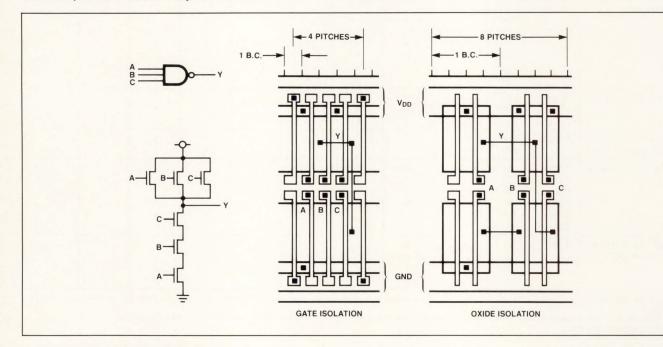

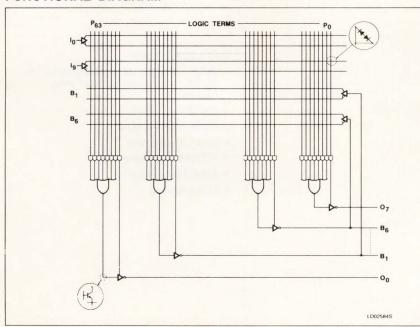

#### **CHANNELED ARCHITECTURES**

Traditionally, gate array bases have been built with separate transistor and wiring areas. In these "channeled" arrays, an empty channel of silicon separates one or two unwired p-n transistor row pairs. The gate array macrocell library then wires up the transistor rows into gates, flipflops, and larger functions: first-level metal joins up the uncommitted transistors in custom metal patterns over the p-n transistor row diffusion regions. These gates and multigate functions, called hard macros, are the smallest building blocks used by the system designer.

On the same metal level used to wire the uncommitted transistors in the base into hard macros, the hard macros are wired into functions. With a channeled architecture, horizontal wires between the gates are run in first-level metal in the wiring channels between the transistor rows. Vertical wire tracks then run over the horizontal wire channels and p-n transistor rows, on second-level metal. By adding a third metallayer, it is possible to move some of the horizontal wiring tracks from the first metallevel to the third, permitting the rows of macros to be moved closer together and thus achieving higher density.

With two layers of metal, it is not feasible to obtain high utilization on a channeled array having more than 20,000 gates. The channels must be increased in width so much that the wire loads become too big. NEC uses three layers of metal to obtain 90% utilization with a channeled array of 40,000 equivalent gates.

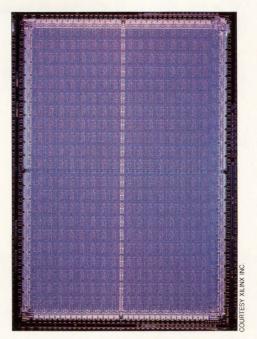

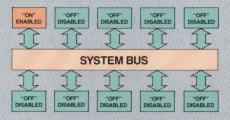

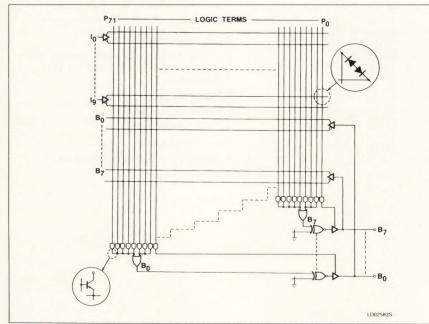

#### **SEA-OF-GATES ARRAYS**

WhereasTLM attacks the problem of increasing gate density, channelless or sea-of-gates arrays are employed to increase absolute gate counts past the 20,000-gate mark. In these array types, all the wiring channels are removed from the array base. By covering the array base totally with a "sea" of cells or transistors, it is possible to obtain utilizations in excess of 90% for designs with a lot of regular structures (RAM, ROM, and PLA). Array bases that strive for these high gate counts and high utilizations, sometimes called "brick wall" or "puzzle fit" arrays, may be the wave of the future. To obtain the highest utilizations with irregular logic, however, triple-level metal is mandatory.

For example, Tangent Systems laid out an experimental TLM array from Texas Instruments and is reported to have obtained a 99% utilization—without any manual intervention—of over 100,000 gates. Vendors now offering TLM sea-of-gates arrays do not generally quote utilizations as high as sported by TI'S CAD benchmark. Hughes does offer 100% utilization for up to 20,000 gates (Hsu et al., 1986), but utilization falls steeply for arrays beyond this level, and in fact Hughes does not sell larger arrays on the commer-

cial market. Motorola is claiming 75% utilization for a prototype 100,000-gate array. Other TLM vendors fall below the half-way mark on utilization; Toshiba, for example, quotes less than 50% (Sawada et al., 1988).

Of course, it is not necessary to have TLM in order to use a sea-of-gates architecture. Sea-of-gates arrays were first introduced in 1982 by California Devices (Lipp, 1983), using double-level metal (DLM). (California Devices has recently been liquidated.)

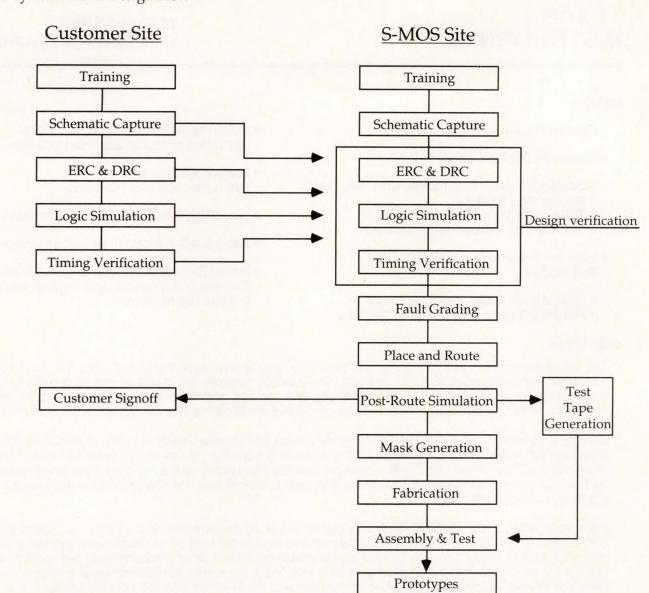

DLM sea-of-gates CMOS arrays are now available from many vendors, including LSI Logic, SGS-Thomson, S-MOS, and VLSI Technology, as well as from most of the vendors supplying TLM arrays. Note that DLM sea-of-gates arrays that were introduced this year are already obtaining utilizations as high as those of current TLM channelless arrays. For example, SGS-Thomson claims a 60% utilization; VLSI Technology, about a 45% utilization; and LSI Logic, a 40% utilization (T. Wong et al., 1986).

#### THE UTILIZATION ISSUE

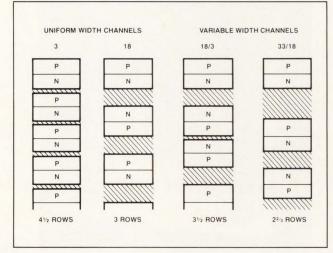

Utilization is one of the hottest issues in array design and is especially so with sea-of-gates architectures. Manufacturers typically indicate the size of an array by the number of two-input NAND gates the array will hold. The size of all other functions is then measured by the number of such gates that could fit in the same area.

This metric introduces the first level of confusion. Macrocells from different vendors can have different numbers of equivalent gates for the same function. The confusion is compounded by whether the equivalence is based on the number of used transistors or on the number of used *cells* (grouped transistors that are electrically isolated from their neighbors). Not all the transistors in a cell may be usable with some functions, and therefore if the quoted figure is for cell utilization, it will be higher than it would be for transistor utilization.

Whatever the case, it is rarely possible to use all the available transistors or cells, even in a channeled array. Leaving some cells unused will reduce wiring congestion. The effect of so-called "depopulated regions" on routability varies from one array (and the CAD system employed for it) to the next. With sea-of-gates arrays and double-level metal, some transistor sites *must* be "depopulated" for the horizontal wiring. Leaving every other row depopulated will reduce the maximum possible utilization to 50%. Vendors quoting a 40%–50% utilization are probably using this technique. Vendors with 30%–40% utilization are probably depopulating *two* rows of gate cells for each macro row used.

One may wonder, why use a sea-of-gates architecture at all if macro rows are regularly depopulated anyway? The answer lies in the use of solid multirow blocks (with no depopulated rows) for regular functions such as RAM, ROM, multipliers, and PLAS. Because these functions are very regular, it is possible to hand-craft building-block modules so that the signal, power, and control port locations directly abut neighboring building blocks. If the constituent building blocks use all the available active devices in the sea of transistors over which they lie, then utilization can be 100% in these areas. Typical designs usually contain a varying mixture of regular and random logic functions. With a 40% utilization of random logic and a 100% utilization in the regular structures, the final utilization depends heavily on the balance between regular and irregular functions in the specific design.

This discrepancy decreases as more and more rows are populated with logic functionality. The developers of more recent DLM sea-of-gates technologies have concentrated their efforts on designing base gate cells and developing CAD tools that can permit higher utilization, rather than on improving the process and manufacturing technology. SGS-Thomson, for example, is moving toward the depopulation of every third cell row only, allowing a peak 67% utilization for irregular functions. However, this higher utilization is obtained by slightly loosening the cell layout.

A low utilization now does not mean that the array is doomed for all time. The utilization may be low because the array and its library have been designed to be shifted to new processes as they become available. For example, the recent DLM arrays from SGS-Thomson, S-MOS, and VLSI Technology cited above all were designed to yield higher utilization when ported to TLM processes.

Moreover, utilization does not necessarily reflect an array's actual transistor density (number of usable transistors per square mil). Some arrays use base cells that are more spread out, so that the utilization will be higher but the number of transistors per square mil is lower.

#### **BASE CELL DESIGN**

The number of rows that must be depopulated to permit routing with the available metal resources depends partly on the base cell design. Transistors can be arranged in various ways inside the transistor rows and can vary in size, isolation technique, shape, and proportion.

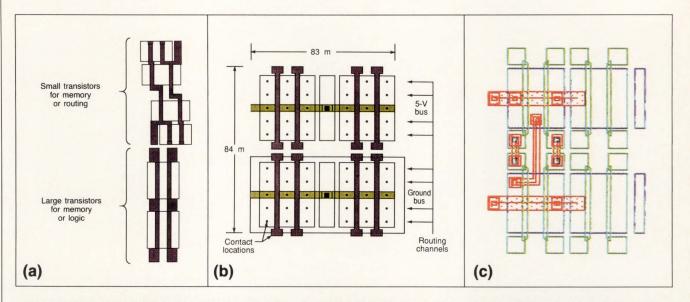

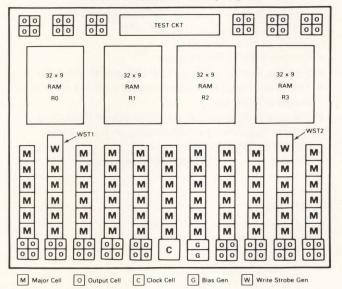

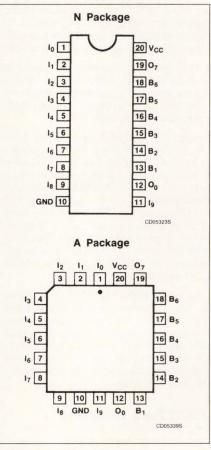

Fujitsu, for example, uses two big p-type, two big n-type, and four small n-type transistors in its base cell (Takahashi et al., 1985), as shown in Figure 2a. With logic functions, the four small n-type transistors are not used at all; instead, the space over them is used for wiring channels, yielding a "pseudochanneled" structure with about 13 first-level metal wiring channels between each gate. When the cell is used for RAM, all eight transistors are employed for a single memory bit. This approach yields a high density for RAM but a lower density for logic functions. Fujitsu does not quote utilization figures for its arrays, which is just as well, because any percentage would need to be qualified by the proportions of RAM and logic considered.

Figure 2b shows a more typical base cell design, with all transistors exactly the same size. This particular diagram shows the proportions used in the Hughes arrays. Figure 2c shows a very similar base array cell structure, this one from Motorola, with the transistors wired into a NAND gate. Both these arrays use a basic isolated cell of eight transistors: four p and four n types.

Higher transistor counts can be obtained by removing the dielectric isolation between neighboring cells. Transistors are then tied to the power rails at both ends ("dead" transistors) to provide electrical isolation between neighboring functions. This scheme uses up more area than

"CASE Technology: CAE Solutions Planned Right from the Start"

CASE Technology's new Vanguard CAE Design System supports a full range of industry standard hardware platforms — DEC VAX (VMS), Sun (UNIX) and PC (DOS) — and a comprehensive set of electronic design applications for PCB and ASIC design. Applications include schematic capture, digital logic simulation, circuit simulation and PCB design capabilities.

Since initial product introductions four years ago, CASE Technology has been setting trends in the computer-aided engineering industry. CASE was the first to introduce:

- a PC-based CAE solution in June 1983

- an integrated PC to VAX solution in November 1985

- a PC as an intelligent graphics terminal for CAE in February 1986

- a complete Sun Workstation-based CAE solution in October 1986

In 1986, CASE also announced major marketing agreements with Digital Equipment Corporation and Sun Microsystems for the joint promotion of the Vanguard CAE Design System on the VAX station and Sun-3 series of high performance engineering workstations.

Over the last three years, CASE Technology has experienced explosive growth to the rate of 80 percent per year and has remained profitable every quarter since the first product shipped. Today, CASE has over 3000 installations of the Vanguard CAE Design System worldwide, in companies such as Hughes Aircraft, Honeywell, and Rockwell International.

Why has CASE Technology been so successful? It's simple. We listen to our customers very carefully. Corporate and engineering managers want *solutions* that work. CASE provides electronic design solutions through a well-conceived, long term plan for product migration, an open database philosophy, and data and operating system independence.

Before you make a decision on CAE, take the time to see what CASE has to offer.

CASE Technology, Inc., 2141 Landings Drive, Mountain View, California 94043 Phone (415) 962-1440; Telex 506513; FAX (415) 962-1466.

**CIRCLE NUMBER 3**

FIGURE 2. Fujitsu's heterogeneous cell (a): the small transistors are either used for ROM or are not used in logic macros, freeing more first-level metal for horizontal wiring. Also shown are standard straight-transistor dielectrically isolated cells, one from Hughes (b) and one configured as a NAND gate, from Motorola's library (c).

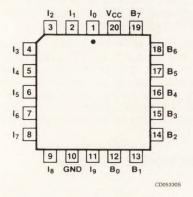

conventional dielectric isolation for a single gate, but since it provides flexibility as to where isolation may occur, it can save space when used with large functions. Technically speaking, arrays based on these cell types are true "sea-of-transistor" arrays—sometimes called "continuous" arrays, because each row has a continuous well diffusion; arrays with dielectric isolation are properly "sea-ofgates" arrays. However, these terms are used somewhat loosely. Figure 3 shows a D flip-flop implemented on a continuous array by VLSI Technology.

Note that some vendors include the transistors used for isolation as "utilized" transistors, and some do not. With continuous arrays, therefore, it is worth checking what any particular utilization number really means.

The continuous array example exhibits two further aspects of array cell design: p-n size ratio adjustment and bent (versus straight) gates. The balance between low-tohigh and high-to-low transitions is controlled by the ratio of p- to n-transistor sizes. "Transition balancing" is preferable because it makes logic design much simpler.

Bending the gate means that the source, gate, and drain contacts for any one transistor all lie in one column. This innovation by Lipp (1983) facilitates wiring. If the gates are not bent, as in the arrays in Figures 2b and 2c, the gate contact is in a different column from the one containing the source and drain. Therefore, half as many gates can fit in the same number of columns. On the other hand, straight-gate columns are narrower than bent-gate ones, because there is no area wasted in making the wire bend. Straight gates end up slightly wider and slightly shorter.

Since horizontal wiring is the crucial resource, it makes sense to use bent gates for sea-of-gates arrays. Bent gates could be why the DLM arrays from VLSI Technology and SGS-Thomson obtain high utilizations compared with the TLM arrays, which currently all use straight gates.

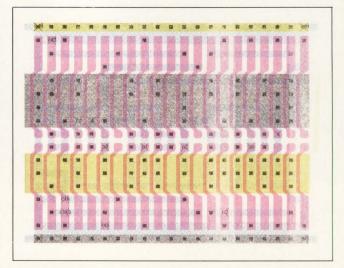

FIGURE 3. A D-type latch in stacked logic from VLSI Technology. Stacked logic and wider base cells permit more horizontal wiring on first-level metal over populated cell sites.

#### POWER DISTRIBUTION

Power distribution becomes critical as density increases. More transistors are packed into the same area, which means that the power lines may pick up more noise. Most arrays use a fixed power distribution grid (SGS-Thomson's grid is described by Blumberg and Waggoner, 1988). The grid must provide adequate clearance for routing to the underlying macrocells.

Adequate clearance to a fixed grid can be achieved with

## **Stop Wasting Power**

#### New CMOS array features the lowest power dissipation: 8µW/Gate/MHz

Raytheon's newest CMOS array family, the RL1000, helps you achieve optimum power performance. It offers the lowest power dissipation available at high densities—without sacrificing speed.

□ Lowest Power: Raytheon's  $8\mu$ W/gate/MHz CMOS arrays, with 1.0 micron effective channel lengths, have available densities ranging from 5670 to 20,440 gates. With 20 tracks per channel instead of the standard 16, gate utilization is typically 90 percent or better.

□ **High Speed:** At 0.3 ns unloaded inverter delay, this low-power, highspeed array family is perfect for portable equipment or where power sources are limited.

□ **Other features:** The RL1000 series, with symmetrical switching delays, operates at 250 MHz flipflop frequency and is TTL/CMOS compatible.

□ **Packaging:** All packaging options are available. And Raytheon's design support includes an extensive macrocell library on major workstations.  Also available in CMOS:

Approved VHSIC PHASE I gate array: RVG 1.25 family

Second source for LSI Logic Inc.'s LL7000 Series: RL7000

Call Raytheon for access to the right CMOS technology. Your success is our first priority.

Raytheon Company Semiconductor Division 350 Ellis Street Mountain View, CA 94039-7016 (415) 966-7716

## Build your gate array on a solid foundation.

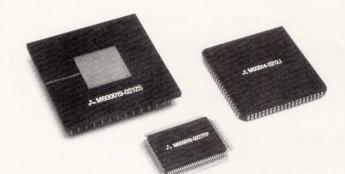

You want to implement your ASIC design quickly. With technology that meets your requirements. You need quality products and dependable delivery to maintain a competitive edge. In short, you expect a partnership built on a solid foundation. One you can count on for future designs as well.

And, that's precisely what you get with Mitsubishi. A solid partnership with a technology base that includes in-house wafer processing, advanced packaging, demonstrated production capabilities and long-term commitment to R&D.

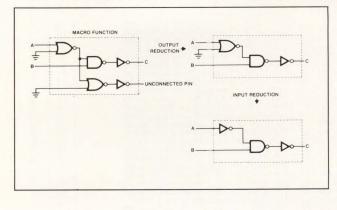

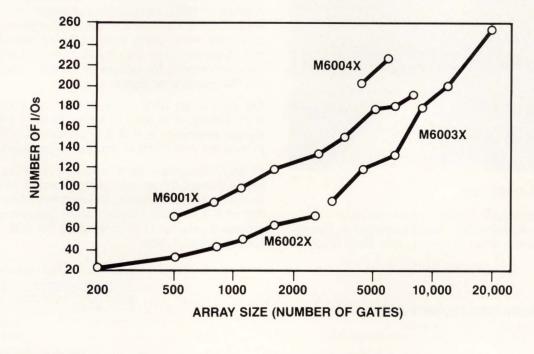

Mitsubishi offers a broad range of gate array product capabilities, from 200 to 20,000 useable gates. And, continuing development work at Mitsubishi's research laboratories is leading to sub-micron CMOS and even more advanced ASIC materials and processes. Unique variable track masterslice (VTM),  $1.3\mu$ m gate arrays provide an ideal architecture for mixed random logic and memory designs.

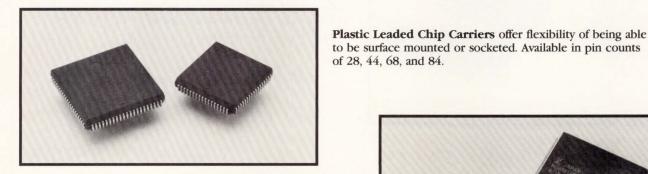

There's a broad range of packaging options: DIP and shrink DIP, SOP, PGA, as well as high pin count quad flat packages (QFP) and plastic leaded chip carriers (PLCC).

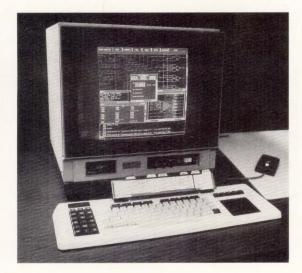

Mitsubishi is committed to supporting your ASIC needs with CAD/CAE design tools to help you develop designs fast. For maximum flexibility, you can design on Mitsubishi's workstations or your own. Remote access to Mitsubishi's proprietary mainframe CAD system allows design verification on any terminal with telephone access.

Mitsubishi's design centers, located in Sunnyvale, CA and Durham, NC, are networked with Regional Technical Centers and a gate array engineering support staff ready to assist in all phases of design.

Mitsubishi Electronics America, Inc. The solid foundation for all your ASIC needs.

THE REPORT

#### PACKAGING:

Mitsubishi offers a broad range of industry-standard and proprietary packaging options. A leadership foundation in high pin count surface-mount packages includes quad flat packages (QFP), now available with up to 160 leads. For throughhole technology, Mitsubishi provides a cost-effective alternative to ceramic PGAs by mounting QFPs on a PC board adaptor (MPGA).

#### **PROCESS:**

Low power,  $1.3\mu m$ , double metal CMOS technology is available today, with submicron levels on the way. Mitsubishi's patented\* gate isolation structure provides 10% to 20% faster performance, with a 15% to 25% higher gate density than conventional oxide isolation. \*U.S. Patent No. 4,562,453

#### MANUFACTURING **COMMITMENT:**

Mitsubishi is committed to continued advancements in ASIC technology, quality and production capacity. Typical time from design to prototype is three to five weeks. Prototype approval to production is eight to ten weeks.

#### **DESIGN SUPPORT:**

At your workstation or Mitsubishi Design Centers, use industry-standard, advanced CAE tools with Mitsubishi's mainframe CAD system. Or, let Mitsubishi integrate your design.

#### SERVICE:

MITSUBISHI

Mitsubishi offers design and applications support at centers in Sunnyvale, CA; Durham, NC and Regional Technical Centers.

### Quality through commitment.

For further information, call or write Mitsubishi Electronics America, Inc., Semiconductor Division, 1050 E. Arques Avenue, Sunnyvale, CA 94086, (408) 730-5900.

Semiconductor Division, 1050 E. Arques Avenue, Sunnyvale, CA 94086, 4(98) 730-5900.

US,/CANADIAN REGIONAL SALES OFFICES AND TECHNICAL CENTERS: NW: Sumnyvale, CA (498) 730-5900, SW: Torrance, CA (213) 55-3993, N: Minnetonka, MN (612) 938-7779, NC: Mt. Prospect, IL (312) 298-9223, SC: Carrollton, TX (214) 484-1919, NE: Woburn, MA (617) 938-1220, MA: Hackensack, NJ (201) 488-1001, SA: Norcross, CA (404) 662-0813, SE: Boca Raton, FL (305) 487.7747, Canada: St. Laurent, Quebec (514) 337-6046.

US,/CANADIAN AUTHORIZED SALES REPS: AL: Beacon Elect. (205) 881-631, AR: OM Assoc. (214) 60-6746, AZ: SMS & Assoc. (202) 908-831, CA: Pathfinder Elect. (619) 578-2555, QCI (408) 432-1070, SC Cubed (805) 496-7307, SC Cubed (714) 731-9206, CO: Simpson Assoc. (305) 997-5740, (813) 796-2378, (305) 332-1940, GA: Beacon Elect. (404) 256-9640, Beacon Adv. Comp. (404) 662-8190, IA: Mid-Tec Assoc. (314) 275-8666, Di Es: (A29, 2840, IL: Phase II Mktg, (312) 303-5092, IN: Carter, McCormick & Pierce (317) 244-1685, KS: Mid-Tec Assoc. (913) 544-0505, KY: Makin Assoc. (514) 691-6746, MA: Comp Rep Assoc. (617) 329-3454, MD: Trinkle Sales

(609) 795.4200, ME: Comp Rep Assoc. (617) 329.3454, MI: Carter, McCormick & Pierce (313) 477.700, MN: Gibb Elect. (612) 935.4600, MO: Mid-Tec Assoc. (314) 275.8666, MT: Simpson Assoc. (801) 566-3691, NC/SC: Baccon Elect. (919) 787.4330, ND/SD: Gibb Elect. (612) 935.4600, NE: Mid-Tec Assoc. (913) 541.0505, NH: Comp Rep Assoc. (617) 329.3454, NJ: Trinkle Sales (600) 795.4200, Nin-Cor Elect. (516) 627.9474, NM: SMS & Assoc. (602) 998-0831, NV (Northern & Central): QCI (408) 432-1070, NV (Southern): SMS & Assoc. (602) 998-0831, NV (Northern & Central): QCI (408) 432-1070, NV (Southern): SMS & Assoc. (602) 998-0831, NV (Northern & Central): QCI (408) 432-1070, NV (Southern): SMS & Assoc. (602) 998-0831, NV (Northern & Central): QCI (408) 432-1070, NV (Southern): SMS & Assoc. (613) 871-2424, (614) 848-5424, (216) 248-57370, OK: OM Assoc. (214) 690-6746, OR: ES/Chase (503) 292-8840, PA: Trinkle Sales (609) 795-4200, PUERTO RICO: Beacon Elect. (800) 726-5040, R1: Comp Rep Assoc. (617) 329-3454, TN: Beacon Elect. (404) 256-9640, (205) 881-5031, TX: OM Assoc. (512) 388-1151, (713) 789-4426, (214) 690-6746, SMS & Assoc. (617) 329-3454, VA: Trinkle Sales (609) 795-4200, WA: ES/Chase (206) 823-9335, WI: Gibb Elect. (612) 935-4600, Phase II Mkrg (312) 303-5902, WV: Trinkle Sales (607) 795-4200, WY: Simpson Assoc. (801) 566-3691, VT: Comp Rep Assoc. (617) 329-3454, VA: Trinkle Sales (609) 795-4200, WA: ES/Chase (206) 823-9335, WI: Gibb Elect. (612) 935-4600, Phase II Mkrg (312) 303-5902, WV: Trinkle Sales (607) 755-4200, WY: Simpson Assoc. (801) 566-3691, CANADA: Tech Rep Elect. (416) 890-2903, (613) 225-9186, (514) 337-6046, (604) 254-2004, (604) 432-1788

two methods. Some arrays restrict macro placement so that the macro wiring ports do not fall under the power lines, but this approach lowers utilization. Alternatively, cells can be designed with more than one contact location, called "antennas," for each signal port in the macro, but they introduce additional wiring congestion.

The alternative to both methods is to use a flexible power distribution scheme, as advocated by VLSI Technology. This approach is desirable, but it presents a far greater burden on the CAD software, and most current routing systems are not up to the task.

#### **GLOBAL SIGNALS**

Heavily loaded paths (clocks and global signals such as resets) are handled in various manners. Hughes, for example, recommends the use of the output driver in an 1/0 buffer to drive such critical signals into the chip core. This approach yields a high fan-out capability, but the signal source is on the edge of the array, resulting in more clock skew between one side of the array and the other. Balanced clock trees are therefore preferable if more than 20,000 gates are used. On the other hand, tree balancing can use up an appreciable number of gates and is not simple.

#### LAYOUT

As array size grows beyond about 20,000 gates, further problems are thus imposed on the layout software by the increasingly complex power distribution and critical path constraints. Indeed, as Dan Skilken, product marketing manager, ASIC strategic marketing, at VLSI Technology, says, "The array architecture is built around the router, and not the other way around."

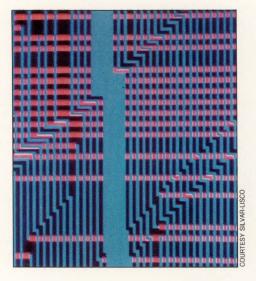

The routing software used for high-density arrays is under continual development by all parties involved and cannot be fairly evaluated by benchmarks. Only three third-party CAD suppliers (Descartes Automation, Silvar-Lisco, and Tangent Systems) are supplying solutions for TLM and channelless arrays.

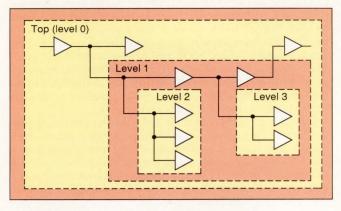

Descartes Automation is not selling a product but rather advocating a design philosophy and customizing tools in terms of it. "Treating layout software as a standard product does not make sense, because each array has its own characteristics," says Antek Szepieniec, the company's executive vice president. Descartes's experience is that flattened designs lay out better than hierarchical designs. "It is not always the case that hierarchy coming either from the netlist or from min cuts actually groups critical paths together. On the other hand, logical clustering or min cut is difficult to outsmart!" Szepieniec says.

To overcome this problem, placement and routing should take place concurrently. "While performing a placement using an arbitrary partitioning scheme with seeded critical elements, we manipulate the global routing data for wires that cross the partition. This information helps the evaluation of final performance, and if critical lengths are likely to be exceeded, we can reroute these nets at the global level," he explains.

Each block, as it and the routing within it are defined at the global level, is then fully placed and routed. The resulting postlayout wiring delay data for each completed block are then used to create more accurate delay estimates for the remaining design. According to Descartes' experience, this incremental process is very efficient.

Silvar-Lisco is selling a product that uses hierarchy for initial placement. Routing, however, is a back-end process, rather than integrated into the early stages of detailed placement; a conventional min-cut algorithm is used to define the blocks. Critical paths are not confined within block boundaries and so additional placement processing must be performed.

In Silvar-Lisco's scheme, overlapping partitions are used to optimize the placement of critical gates after initial min-cut partitioning. With overlapping partitions, gates placed within the overlap can move anywhere into a neighboring block. Critical gates can therefore move to their optimal position and are not constrained to the block in which they are first placed. Silvar-Lisco's approach can handle up to about 75,000 utilized gates. SGS-Thomson and Digital Equipment use the Silvar-Lisco tools.

Tangent Systems aims to provide a totally automatic solution and 100% routing completion. Placement can be flat, or hierarchy can be used, with "fuzzy" blocks resulting(block size and shape can be changed after initial placement, and functional density within the block can be specified by the system to permit more or less throughblock routing as needed). Unlike the case with all other systems, the routing algorithm is not a channel router; instead, it sees "obstructions" in the Manhattan path (a connection with only one corner) and finds the best route around them. Obstructions may comprise existing or predicted routing congestion, as well as elements that are already placed.

The router is also loaded with additional features, such as smart power routing and automatic clock-tree balancing. If power grids are used, they can be automatically altered in type, depending on whether the grid runs over irregular logic or over a modular function such as RAM or ROM. Individual power wires can also be widened automatically when there is no signal wire obstruction.

The automatic clock-tree balancing ensures that the loads are even on each side of the the clock tree by dynamically adding gates during routing.

Tangent's software is being used by, among others, Motorola, S-MOS, and Toshiba. Its present maximum capacity is a quarter of a million gates.

#### STRUCTURED GATE ARRAYS

Before sea-of-gates arrays acquired their viselike grip on the semicustom market, a number of manufacturers introduced arrays that put a fixed block of memory, a certain-sized multiplier, or a small microcontoller core on the edge of a channelled gate array. This approach, pioneered by IBM and marketed first by LSI Logic as structured gate arrays, can yield greater density improvements for the highly regular functions than sea-of-gates arrays, and the embedded hard macros can be customized for speed.

However, the user is committed to the actual function sizes that are supplied. If anything other than the supplied function size is required, such arrays actually waste space for a small performance improvement. As a result, they

# We're eliminating the competition with something everyone else seems to have forgotten you need...

## ...the maximum performa

#### Plessey - Unsurpassed Process Technology

As system design becomes more and more challenging, and product life cycles become increasingly shorter, design flexibility and getting it right the first time have become critical factors in gaining and maintaining that maximum performance edge you've been looking for.

Plessey's investment in advanced process technology is unequaled in the industry. Successive reductions in feature size and continued improvement in process techniques are at the heart of leading-edge Plessey products.

PLESSEY and the Plessey symbol are trademarks of the Plessey Company, PLC.

### Plessey - The Ultimate in ASIC Technology

Our broad range of ASIC products has grown to the point where we are now able to meet all the needs of ASIC users. We offer a full ASIC product range with a variety of options for digital, analog and mixed analog/digital applications, in gate arrays, standard cells, and full-custom. Advanced, stateof-the-art processes in fine geometry, high-density CMOS, bipolar and ECL technologies give you the highest levels of performance and system integration available today.

#### Plessey - Unparalleled CAD Support

The Plessey Design System (PDS) is a comprehensive suite of software em-

bracing the design, simulation and implementation of gate arrays, standard cell and compiled ASICs in CMOS and bipolar technologies.

Customers who want to use their own CAD workstations or simulators are accommodated by flexible design interfaces at various stages into PDS.

#### Plessey - Standard Products And Discrete Components

Plessey's standard product family offers the highest performance product range available in the world today. Capabilities range from CMOS DSP devices operating in excess of 20MHz to the world's most advanced 1.3GHz monolithic log amplifier.

High performance solutions are also offered in radio communications, digital

# ce that gives you the edge.

#### PLESSEY KEY PROCESS TECHNOLOGY

|                                                                | BI                                | POLAR         |                    |               |                 |  |  |

|----------------------------------------------------------------|-----------------------------------|---------------|--------------------|---------------|-----------------|--|--|

| DESCRIPTION                                                    |                                   | Ft            | EMIT               |               | METAL<br>LAYERS |  |  |

| Industry standar                                               | d                                 | 400MHz        | 14µ                | m             | 1               |  |  |

| High voltage                                                   |                                   | 400MHz        | 20µm               |               | 1               |  |  |

| High speed linea                                               | igh speed linear                  |               | 4µm                |               | 2               |  |  |

| High speed digit                                               | ligh speed digital                |               | 3µm                |               | 2               |  |  |

| Ultra-high speed                                               |                                   | 14GHz         | 0.6µm              |               | 3               |  |  |

|                                                                |                                   |               |                    |               |                 |  |  |

|                                                                |                                   | MOS           |                    |               |                 |  |  |

| PROCESS FAMILY                                                 |                                   | fCLOCK        | MINIMUM<br>FEATURE |               | VSUPPLY         |  |  |

| KC Industry standard CMOS                                      |                                   | 20MHz         | 4µm                |               | 3-10V           |  |  |

| JG Double SiGate NMOS                                          |                                   | 10MHz         | 6µm                |               | 9-18V           |  |  |

| VB High speed CMOS                                             |                                   | 40MHz         | 2µm                |               | 3-5V            |  |  |

| VJ Very fast CMOS                                              |                                   | 50MHz         | 1.5µm              |               | 3-5V            |  |  |

| VQ Ultra fast CMOS                                             |                                   | 75MHz         | 1.2µm              |               | 3-5V            |  |  |

| MH/MA SiGate CMOS                                              |                                   | 30MHz         | 4µm                |               | 3-15V           |  |  |

| BIPOLAR (CDI)                                                  |                                   |               |                    |               |                 |  |  |

| PROCESS                                                        | EMITTER<br>WIDTH/<br>FEATURE SIZE | GRID<br>PITCH | MAX.<br>SPEED      | MAX.<br>POWER | MIN.<br>POWER   |  |  |

| ORIGINAL CDI                                                   | 5µm                               |               |                    |               |                 |  |  |

| CDI FAB I                                                      | 3.75µm                            | 11.5µm        | 10ns               | 2.4pJ         | 1.5pJ           |  |  |

| CDI FAB IIa                                                    | 2.5µm                             | 8µm           | 4ns                | 1.2pJ         | 0.8pJ           |  |  |

| Geometry change (utilizing multi-level differential logic-DML) |                                   |               |                    |               |                 |  |  |

| CDI FAB IIb                                                    | 2.5µm                             | 8µm           | 800ps              | 0.8pJ         | 0.54pJ          |  |  |

| CDI FAB III                                                    | 1.5µm                             | 6µm           | 400ps              | 0.4pJ         | 0.27pJ          |  |  |

| CDI FAB IV                                                     | 1.2µm                             | 4.5µm         | 200ps              | 0.2pJ         | 0.14pJ          |  |  |

|                                                                |                                   |               | STATISTICS SALE    |               |                 |  |  |

frequency synthesis, data conversion, telecommunications, data communications and consumer products.

Complementing the standard IC family, Plessey manufactures a complete line of discrete components including FETs, transistors and diodes available in SOT-23 and TO-92 packages.

#### Plessey - Over Two Decades Of Quality Commitment

For more than 20 years, Plessey Semiconductors has been commited to supplying the latest technology, highest quality, and highest performance semiconductor products in the industry. With our unique combination of CAD support, major advances in process technology, and the most advanced research facility in the world, Plessey Semiconductors is, today, a totally commited leader in the industry.

To learn more on how Plessey can help you achieve the maximum performance that gives you the edge, send for our new comprehensive, full color, 72-page short form brochure, or call Plessey Semiconductors today.

In North America call 1-800-441-5665. Outside North America call 44-793-726666. For further information you can write to us at one of the following addresses:

Plessey Semiconductors 1500 Green Hills Road Scotts Valley, CA 95066 U.S.A.

Plessey Semiconductors Ltd. Cheney Manor, Swindon Wiltshire SN2 2QW United Kingdom

have largely fallen out of favor.

However, with the continuing progression in memory density, structured arrays could be on the way back. An unusual chip from Toshiba integrates a sea-of-gates array with high-density DRAM (Sawada et al., 1988). The chip clocks in with about 30,000 gates available for logic and a whole megabit of 60-ns DRAM. This capacity is two orders of magnitude more memory than offered by any previous structured array and a lot of gates!

To use this phenomenal fusion of function, not more than about 5,000 gates and 32 output drivers can switch at once. As long as these limits are not exceeded, the chip is reported to be fully hardened against noise disturbance.

The combination of sea-of-gates arrays with various high-density memory functions may in fact lead to specialized chips appearing for graphics control, BITBLT processing, cache and memory management, and digital signal processing.

#### THE FUTURE?

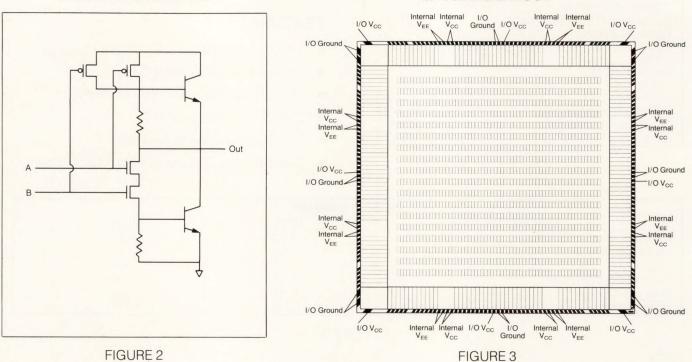

We can expect further improvements in density and the adoption of sea-of-gates techniques in other technologies besides CMOS. LSI Logic has now presented technical data on the first bicMOS sea-of-gates array, which may be available for prototyping over the next six months (A. Wong et al., 1988). The array will support up to 123,000 gates and departs from the fully integrated bicMOS array used by Applied Micro Circuits Corp. (Lin and Spehn, 1987). Instead, bipolar drivers are lined up on one edge of the array and used to drive high-fan-out signals into the pure CMOS core. This setup permits adoption of the buffer clock driver technique advocated by Hughes, with less clock skew. At the same time, cells developed for the company's established sea-of-gates arrays can be directly used in the identical CMOS core.

Bicmos is an important step in part because it permits the integration of analog circuitry with sea-of-gates architectures. Analog circuitry could be used for on-chip power regulation to reduce the switching noise problem. As a result, the arrays could use a lower power supply (perhaps 2.5 or 3 v), which would lower the current density in the metal interconnections, reduce migration effects, and permit the use of submicron-wide wires in planarized DLM processes.

AMCC, which introduced bicmos channeled arrays last year, is now developing the first sea-of-gates bipolar array (Coy, Mai, and Yuen, 1988). The chip is being produced using Plessey's HE1 process. Bipolar transistors are more difficult to embed in a sea-of-gates architecture, particularly because of the larger amount of wiring space that must be used to distribute power. Furthermore, the reduction in chip size made possible with sea-of-gates architectures has less impact on performance and predictability for bipolar than for CMOS technology, because wire lengths are less critical. Thus AMCC's movement to a sea of gates for bipolar arrays may be an indication that layout techniques for these chips are generally superior to those offered for traditional channeled approaches, even if only for the savings in chip real estate.

#### CONCLUSIONS

The advent of high-density arrays heralds the increased feasibility of gate arrays in many applications where before only hand-crafted or standard-cell designs were viable. Of course, triple-level metal and sea-of-gates layout will before long be applied to cell-based design; the implications of those developments are left to future articles.

#### Acknowledgments

I would like to thank all the individuals who helped me in writing this article, and in particular Richard Blumberg, director of semicustom CAD at SGS-Thomson; John Carey, merchandising manager for Motorola's ASIC Division; Kerry Pierce, portable library design manager at VLSI Technology; and Terry Smith, president of Tangent Systems.

#### References

- Blumberg, R., and C. Waggoner. February 1988. "Aluminum Screen Gives Superior Power Distribution in a Sea-of-Gates Array," VLSI Systems Design.

- Coy, B.; A. Mai; and R. Yuen. 1988. "A 13,000 Gate 3 Layer Metal Bipolar Gate Array," *Proceedings of the 1988 IEEE Custom Integrated Circuits Conference.*

- Gulett, Michael R. January 1985. "Dual-Metal CMOS for Semicustom or Custom Designs," VLSI Design.

- Hsu, C. P., et al. 1986. "Automatic Layout of Channelless Gate Array," *Proceedings of the 1986 Custom Integrated Circuits Conference.*

- Lin, L.T., and Richard Spehn. 1987. "A BicMos Gate Array Family," VLSI Systems Design's Semicustom Design Guide.

- Lipp, R. 1983. "Advanced Architecture (Channelless) Dual Layer Metal CMOS Gate Array," *Proceedings of the 1983 IEEE Custom Integrated Circuits Conference.*

- Sawada, K., et al. 1988. "A 72k cmos Channelless Gate Array with Embedded 1-mbit Dynamic RAM," *Proceedings of the 1988 IEEE Custom Integrated Circuits Conference.*

- Takahashi, H., et al. 1985. "A 240k Transistor CMOS Array with Flexible Allocation of Memory and Channels," *Proceedings of the 1985 IEEE Solid-State Circuits Conference.*

- Wong, A., et al. 1988. "A High-Density Bicmos Direct Drive Array," Proceedings of the 1988 Custom Integrated Circuits Conference.

- Wong, T., et al. 1986. "A High Performance 129k Gate CMOS Array," Proceedings of the 1986 IEEE Custom Integrated Circuits Conference.

#### **About the Author**

**Ernest Meyer** is a free-lance writer and editorial consultant, as well as a contributing writer and columnist for *SupercomputingReview* and *Embedded SystemsProgramming*. Previously, he was an editor at *VLSI Systems Design*. He has worked on the design of various electronic systems, including an Apple-compatible microcomputer and a music synthesizer.

# Cadnetix. The Difference **Ketween** Vorking ASICs and Reworking

Nothing costs more than a missed opportunity.

That's why you can't afford to spend time reworking ASICs that work only until you put them into your system.

Cadnetix's comprehensive set of tools for design, simulation and test minimizes ASIC rework by letting you thoroughly analyze how your ASIC will perform in your system. Before it becomes part of your system.

You can include your ASIC design in a system level simulation or actually use a physical prototype. And with ASIC complexity on the increase,

Cadnetix offers guaranteed testability. Our advanced automatic test generation tool, INTELLIGEN, delivers extremely high fault coverage on all of your designs. While only using a fraction of the overhead circuitry required by full scan methods.

So if you need to design working ASICs, look to Cadnetix's open EDA environment. Before you know it, you'll be working on your next ASIC. Instead of reworking the

last one.

Boulder, CO (303)444-8075 INTELLIGEN is a trademark of HHB Systems, Inc., a subsidiary of Cadnetix Corporation.

NEC

#### NEC's FREE Design Kit is Your Gate Array Gateway to

- 1. CMOS, BiCMOS, and ECL technologies.

- 2. Valid, Sun, Mentor, Daisy, HP 9000, FutureNet, Calma TEGAS V, and HILO compatibility.

- **3.** A powerful block library with more than 170 macros, including analog, peripheral, and megamacro functions.

- 4. Cell utilization rates of 95% over a range of 800 to 45,000 gates.

- 5. Better than 95% first-time success with engineering prototypes.

- 6. The most experienced manufacturing capability.

- 7. The widest choice of through-hole and surface-mount packages.

- 8. The most effective way to lower your system costs.

- **9.** Local design support with local FAEs and design centers backed by a satellite network of computers for worldwide communications services.

- **10.** The easiest translation of your ideas into silicon.

NEC Electronics Inc. 401 Ellis Street, P.O. Box 7241 Mountain View, CA 94039

Our gate arrays are your gateway to higher system performance. Call **1-800-632-3531** to browse through our block library. FREE!

©Copyright 1988 by NEC Electronics Inc.

Valid is a trademark of Valid Logic Systems Inc. Daisy is a trademark of Daisy Systems Corp. HILO is a trademark of GenRad Inc. FutureNet is a registered trademark of FutureNet, a Data I/O Company Tegas V is a registered trademark of GE Calma.

.....

NEC

## HIGH-SPEED GATE ARRAYS: CONSIDERING THE OPTIONS

Ron Cates, Vitesse Semiconductor Corp., Camarillo, Calif.

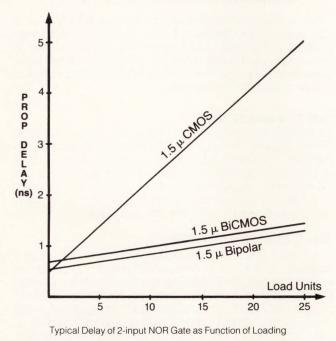

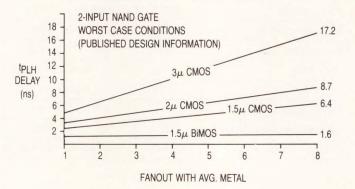

igh power dissipation has traditionally been part and parcel of every fast-clocking system, and in many cases it sets the upper bound on the practical density of an integrated circuit. For ICS clocked at less than 50MHz, CMOS is the obvious choice. It offers an unparalleled combination of circuit complexity and low power dissipation. Digital circuits that operate beyond 50 MHz, however, are needed for many applications—high-performance workstations and computers, telecommunications, and automated test equipment, to name a few. CMOS just does not have the performance for such settings.

Typically, designers turn to bipolar ECL circuits when higher performance is essential. Recently, though, system designers have been given aviable alternative technology for high-speed digital circuits—enhancement/depletion-mode gallium aresenide, or E/D GaAs.

Gate arrays have become a dominant approach to implementing high-performance systems. They offer an opportunity to create a custom component that can meet performance criteria and that involves a minimum of design time and risk. Advanced software tools, usually running on engineering workstations, make it possible to enter the schematic and accurately simulate logic and timing before committing to silicon.

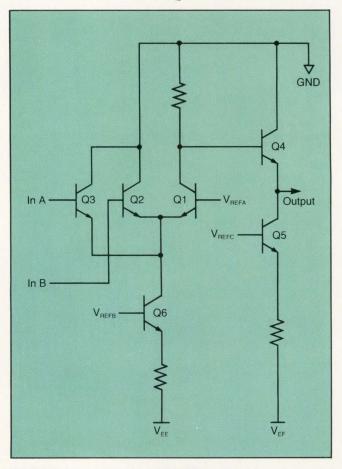

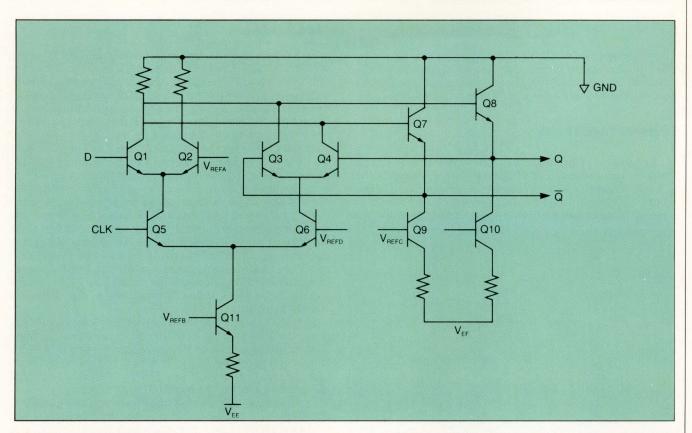

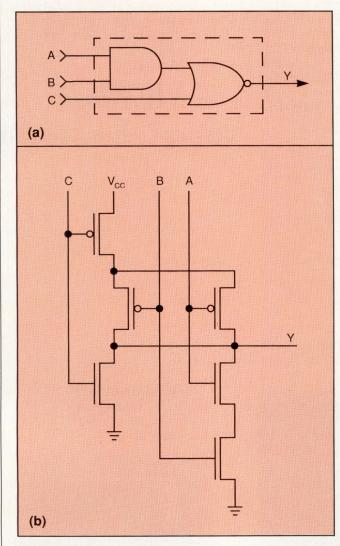

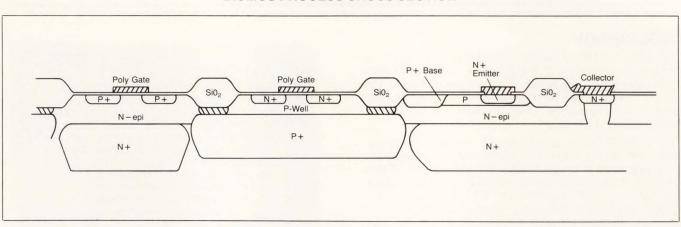

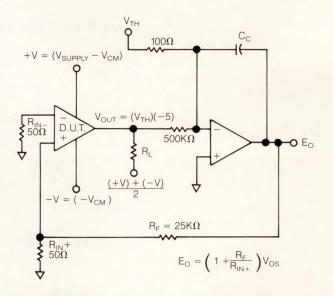

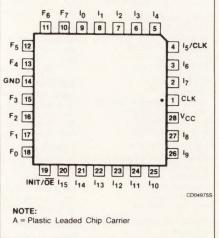

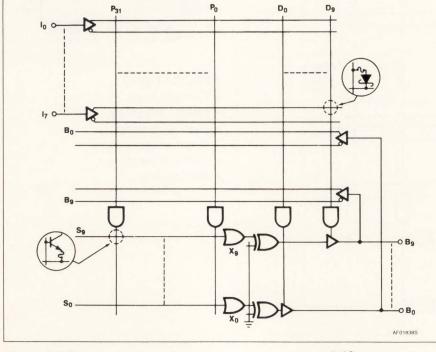

#### **DIFFERENT TOPOLOGIES**

To understand the differences between ECL silicon and E/DGaAs, it is useful to review the basic circuit topologies of each. Central to the operation of a typical ECL NOR gate (Figure 1) is the main differential pair ( $Q_1$  and  $Q_2$ ).  $V_{\text{REFA}}$  is set at a voltage halfway between a valid logic high and logic low. When digital signals arrive at the base of  $Q_2$  or  $Q_3$ , the active device in the differential pair switches state, resulting in a change of voltage across the load resistor (R). Emitter-follower  $Q_4$  shifts the level of that voltage change and buffers it.  $Q_5$  and  $Q_6$ , along with their corresponding resistors, act as active current sinks.

The majority of the current consumed by an ECL gate passes through the emitter-follower to drive the interconnect capacitance. To reduce power consumption, advanced ECL gate arrays use a special power supply to supply power to the emitter-followers. Since  $V_{\rm EF}$  is typically set at -3.3 v, this approach saves power when compared with

gate arrays that tie the emitter-followers to  $V_{\rm EE},$  which is set at  $-5.2\,v.$

The simple ECL NOR gate requires six transistors and three resistors, as well as several voltage references that set currents or provide the reference voltage to the differential pair. Typically, these reference generators are shared among several gates. Unfortunately, the metal buses that distribute the reference voltages can increase the size of

FIGURE 1. A typical two-input ECL NOR gate requires six transistors, three resistors, and several voltage references.

FIGURE 2. Adding "clocking pair" ( $Q_5$  and  $Q_6$ ) and a "latching pair" ( $Q_3$  and  $Q_4$ ) to the circuit shown in Figure 1 creates a data latch. Cascading two of these structures results in a D-type edge-triggered flip-flop.

the gate and consume routing resources.

Although the ECL gate looks complex, slight modifications to the basic structure make it configurable to a variety of logic primitives. A data latch is created (Figure 2) by adding a clocking differential pair ( $Q_5$  and  $Q_6$ ) and a regenerative pair ( $Q_3$  and  $Q_4$ ). When the clock is high, the input transistor pair amplifies the data input; when the clock is low, the regenerative pair is active, latching the data through feedback from the outputs. Other structures that are similar to this latch use the regenerative transistor pair for logic inputs and capitalize on the vertical gating structure to implement such functions as a 2:1 multiplexer or an exclusive-OR gate. Cascading two latches and cross-wiring the clock inputs creates an edge-triggered D flip-flop.

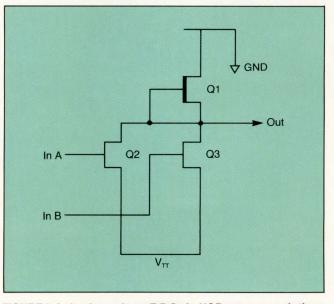

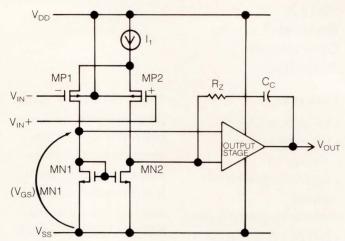

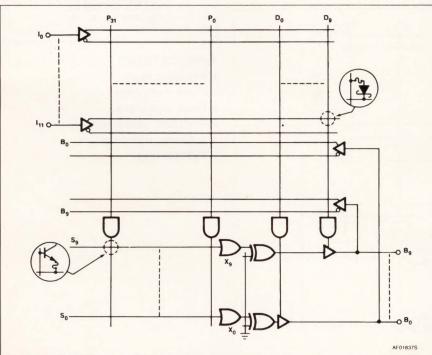

When compared with the ECL structure, the E/D GaAs gate is very simple. A two-input NOR gate (Figure 3) uses only three transistors and needs no resistors. It uses a depletion-type MESFET ( $Q_1$ ) as an active-load pull-up device and two enhancement-type MESFETs ( $Q_2$  and  $Q_3$ ) as pull-down switches. The GaAs gate operates identically to equivalent silicon NMOS structures.  $Q_2$  and  $Q_3$  are large enough so that if one or the other is on, or if both are on, it or they can sink all of the current from  $Q_1$  and provide a small  $V_{vDS}$  for a logic-low output. When both enhancement transistors are off, the pull-up current is forced into the forward-biased gate-source junction of the driven gate, providing a logic high.

In the E/D GaAs configuration presented here, the power

dissipation of the gate is independent of the logic state that it is in. Because the current on the power supply buses is constant, self-generated noise on the signal and internal

power buses is virtually eliminated, reducing the need for artificially large noise margins. Reduced voltage swings—such as the 500 mV for E/D GaAs—also simplify high-speed switching and reduce current-drive requirements.

#### DRIVING CAPACITANCE

Regardless of the material from which they are made, bipolar transistors have a higher transconductance than FETS. As a result, ECL circuits drive long capacitive lines fairly well, exhibiting 50 to 60 ps of delay for every millimeter of interconnect. Driving long capacitive lines with

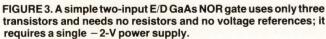

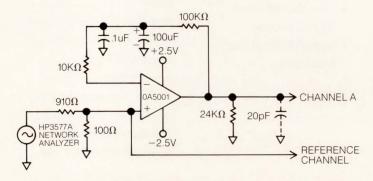

FIGURE 4. An E/D buffer with a push-pull stage (a) can drive a millimeter of wire in 50 ps. Adding a set of pull-down devices converts the buffer into a NOR gate (b).

some E/D GaAs circuits, however, is inefficient because the pull-down transistors grow in proportion to the size of the pull-up driver and, therefore, may not provide an adequate capacitive buffering ratio (the ratio of the capacitance of the driven load to the input capacitance of the buffer). If the ratio is too low, the buffer itself introduces excessive capacitance on the input signal.

A buffer skirts this limitation (Figure 4a). The push-pull operation of its output stage enhances its ability to drive capacitive loads by placing a positive bias on the gate of the output pull-up transistor. The pull-down transistor doesn't have to be made larger in order to sink the extra current of the pull-up transistor, because the pull-up transistor's current is enhanced only when the input voltage is low. When the input is high, the gate and source of  $Q_3$  are at the same potential, so that the transistor has a lower current drive. The buffer is capable of driving a millimeter of metal in 50 ps. Logic operations can be incorporated into the buffer by providing additional sets of pull-down devices (Figure 4b).

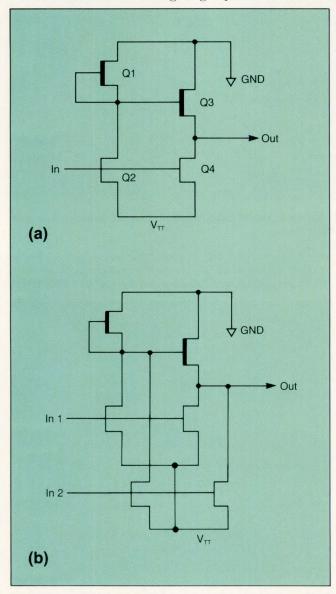

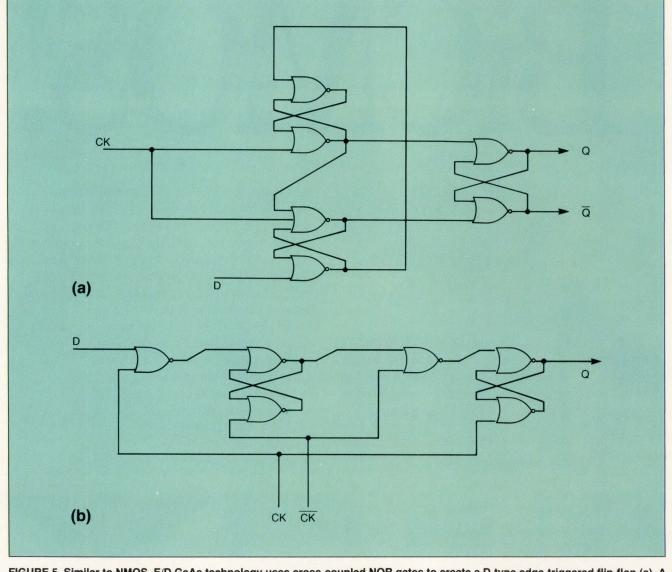

E/D GaAs is similar to NMOS in that flip-flop circuits are created with NOR gates. Consider two posssible D flip-flops (Figure 5): one would be a typical edge-triggered version; the second uses differential clocks to reduce both set-up and propagation-delay times. Both rely on cross-coupled NOR gates to achieve the basic latching function.

In general, simple digital functions such as logic gates, registers, and multiplexers can be implemented in E/D GaAs with fewer transistors than they would need in ECL. As shown, a flip-flop requires 19 transistors in E/D GaAs but 22 transistors and 10 resistors in an ECL implementation. As a result, much less real estate is required to implement a given function in E/D GaAs. Since they don't require area-consuming resistors, E/D GaAs circuits can achieve densities equivalent to NMOS circuits. A two-input NOR gate, for example, occupies only 100  $\mu$ m<sup>2</sup>.

This density has strong implications for gate arrays. E/D GaAs arrays occupy about one half the area of ECL arrays of equivalent compexity. Metal routes, therefore, are shorter for E/D gate arrays: statistical analysis on automatically routed arrays shows an average route length of 0.3 mm per fan-out load in an E/D GaAs array (from Vitesse's design manual), much shorter than the 0.8 mm per fan-out load in an ECL device (according to Raytheon's ECL Family Design Manual).

#### **POWER CONCERNS**

No discussion of high-performance circuits would be complete without a careful consideration of power dissipation. High power dissipation has traditionally been associated with every fast-clocking system and, in many cases, it limits the density of an integrated circuit.

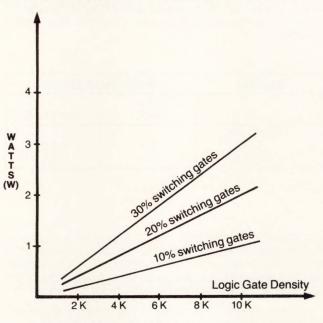

ECL circuits have dramatically improved their power dissipation for a given function over the levels of early SSI devices. Today, typicalECL gate power falls between 1 and 4 mW, depending on the speed option that the designer selects. Even at such low values, new 10,000- and 12,000gate ECL arrays can dissipate as much as 30 w when their

# ARRAY FOR BicNOS

180 MHz with low power.

It's cause for celebration. AMCC extends its lead as the high performance/low power semicustom leader with three exciting, new BiCMOS logic

arrays that optimize performance where today's designs need it most. In throughput (up to three times faster than 1.5µ CMOS).

Today, system designers look at speed, power and density. For

| Q14000 SERIES                  |                 |             |             |  |  |  |

|--------------------------------|-----------------|-------------|-------------|--|--|--|

|                                | Q2100B          | Q9100B      | Q14000B     |  |  |  |

| Equivalent Gates               | 2160            | 9072        | 13440       |  |  |  |

| Gate Delay* (ns)               | .7              | .7          | .7          |  |  |  |

| Maximum I/O<br>Frequency (MHz) | 180             | 180         | 180         |  |  |  |

| Utilization                    | 95%             | 95%         | 95%         |  |  |  |

| Power<br>Dissipation (W)       | 1.8             | 4.0         | 4.4         |  |  |  |

| I/O                            | 80              | 160         | 226         |  |  |  |

| Temperature<br>Range           | COM,<br>MIL     | COM,<br>MIL | COM,<br>MIL |  |  |  |

| *(2 loads, 2 mm of             | †Available soon |             |             |  |  |  |

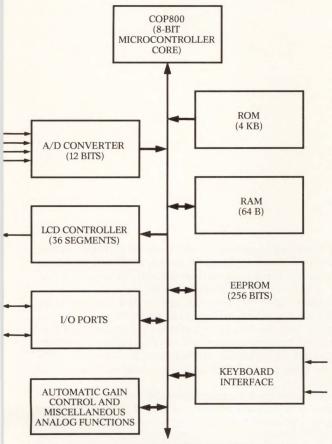

good reasons. As CMOS gate arrays become larger and faster, designers can't meet their critical paths due to fanout and interconnect delay. As Bipolar arrays become larger and faster, power consumption becomes unmanageable. So AMCC designed a BiCMOS logic array family that merges the advantages of CMOS's low power and higher densities with the high speed and drive capability of advanced Bipolar technology. Without the disadvantages of either.

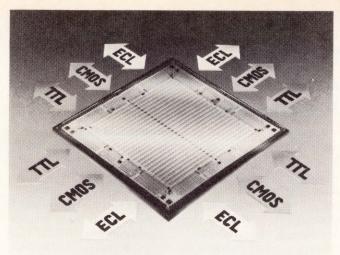

Our new Q14000 BiCMOS arrays fill the speed/power/ density gap between Bipolar and CMOS arrays. With high speed. Low power dissipation. And, mixed ECL/TTL I/O compatibility, (something CMOS arrays can't offer).

For more information on our new BiCMOS logic arrays, in the U.S., call toll free (800) 262-8830. In Europe, call AMCC (U.K.) 44-256-468186. Or,

contact us about obtaining one of our useful evaluation kits. Applied MicroCircuits Corporation, 6195 Lusk Blvd., San Diego, CA 92121. (619) 450-9333.

resources are fully used. Some ECL arrays have low-power options that drop the total power of a 10,000-gate device to less than 10 w by reducing performance. The designer must be careful to ensure that these devices still meet speed requirements.

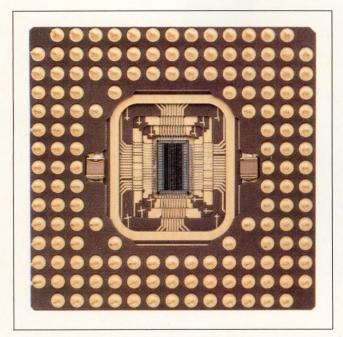

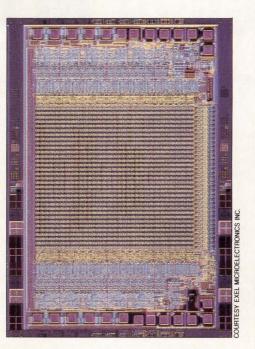

The primary improvement that E/D GaAs technology brings to the high-performance market is reduced power dissipation. By operating from a single -2-v power supply, E/D GaAs can offer performance comparable to that of ECL circuits while consuming one fourth the power. For example, the VSC4500 gate array from Vitesse Semiconductor (Figure 6) can integrate as many as 4,000 NOR gates and has a typical power dissipation of only 1.5 w.

E/D GaAs and ECL silicon circuits have very similar speed parameters. Typical gate delays for both technologies are

on the order of 200 ps, and flip-flop delays, from clock input to data output, are approximately 700 ps for lightly loaded outputs. Exercising high-power options on an ECL array can result in higher performance than that possible with an E/D GaAs array, but these options can increase power consumption to the point where the device becomes unsuitable for air- or conduction-cooled systems. GaAs has an analogous technology—D-mode MESFET—that trades low power consumption for operating frequencies in excess of 3 GHz.

$\rm E/D~GaAs~has~a~slight~edge~over~ECL~silicon~in~terms~of~the~bandwidth~of~l/O~buffers. Typical ECL devices have 1/O bandwidths of approximately 600 MHz, whereas E/D GaAs devices can reach 1 GHz. This bandwidth is achievable despite the fact that the E/D GaAs devices use non-ECL logic$

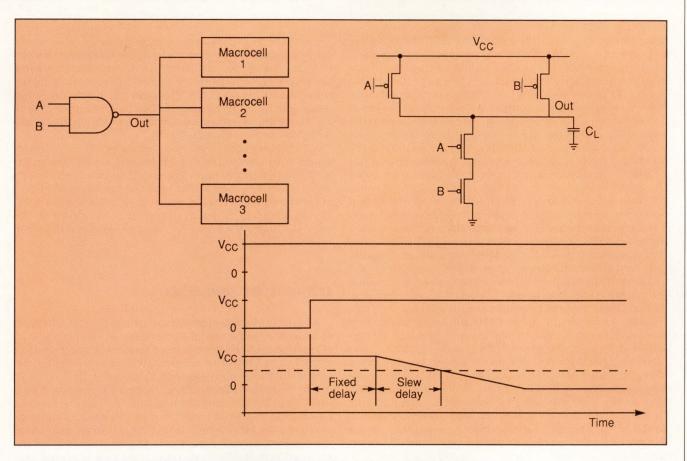

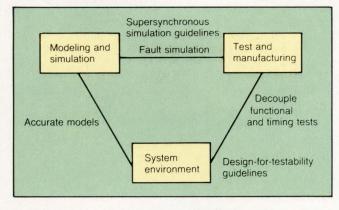

FIGURE 5. Similar to NMOS, E/D GaAs technology uses cross-coupled NOR gates to create a D-type edge-triggered flip-flop (a). A version that uses a differential clock signal (b) has better setup and delay propagation characteristics.