# Digital Design COMPONENTS - PERIPHERALS - COMPONENTS - RULE Tolerant Architectures • Minicomputers • DEC-Compatibility • Graphics Boards • Display Processors

VOL. 13

## THE UNIVERSAL FAST CMOS GATE ARRAY SOLUTION. THREE OR FIVE MICRON TECHNOLOGY! 360 to 2400 GATES!

There are many sound reasons to select Universal as your CMOS gate array partner. Here are a few:

**Advanced Technology**—We don't buy technology from others—we make it! For toggle rates to 25MHz, our  $5\mu$  process serves nicely. For frequencies beyond, our  $3\mu$  process is

employed. In either case, you're dealing with a company in full command of the technology behind its arrays.

**Broad Array Selection**—No other company has a more useful selection of arrays. There are 14 different arrays logically sized between 360 and 2400 gates available. Large or small, fast or faster performance, we have an array to serve your needs.

| Туре       | Gates | Size      | Speed        | Pads |

|------------|-------|-----------|--------------|------|

| 1S03 or 5A | 360   | 118 × 140 | 50 or 25MHz  | 44   |

| 1S03 or 5B | 540   | 132 × 167 | 50 or 25 MHz | 58   |

| 1S03 or 5C | 720   | 159 × 167 | 50 or 25 MHz | 64   |

| 1S03 or 5D | 960   | 161 × 208 | 50 or 25 MHz | 70   |

| 1S03 or 5E | 1200  | 188 × 208 | 50 or 25 MHz | 74   |

| 1S03 or 5F | 1500  | 188 × 244 | 50 or 25 MHz | 80   |

| 1S03 or 5G | 1800  | 202 × 230 | 50 or 25 MHz | 92   |

| 1S03 or 5H | 2400  | 232 × 252 | 50 or 25 MHz | 110  |

**Complete CAD Support**—No other company has more sophisticated CAD tools. Every Universal array is completely simulated and verified prior to converting it to silicon. And that's not all:

- Macrocells are placed automatically

- Macrocells are routed automatically

- Logic and circuit functions are fully simulated

- The design is completely verified.

- Test program automatically generated

**Fast Turnaround**—For arrays of 800 gates or less, we guarantee an 8-week turnaround. For larger arrays, add one week per 150 gates. And because of our powerful CAD tools, when you get your prototypes, they'll work and perform to spec!

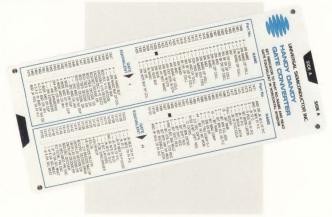

**Start Today**—What size array do you need? With our Handy Dandy Gate Counter, you can convert your TTL or LSTTL design to CMOS gate equivalents quickly. In less than an hour, you'll know exactly what size array will do your job. *Write* or *call* today for your *FREE* Handy Dandy. We'll also send you a full color brochure describing our products and services.

Write 43 on Reader Inquiry Card

UNIVERSAL SEMICONDUCTOR INC.

1925 Zanker Road San Jose, CA 95112 (408) 279-2830

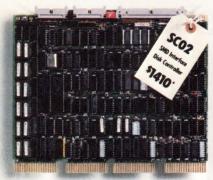

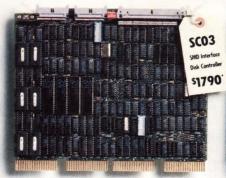

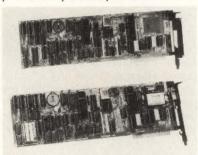

# Q-BUS\* DISK CONTROLLERS

You can't beat the configuration flexibility DILOG's family of Q-BUS disk controllers provide you for systems integration. They interface the full line of DEC LSI-11 through 11/23 PLUS computers and wide range of today's high technology Winchester drives.

DILOG further insures this flexibility with exclusive Universal Formatting™...so you can change drives as newer models become available...all without changing on-board components or adding cost...thus making DILOG a real price/performance value.

## SMD COMPATIBLE WINCHESTER DISK CONTROLLERS

Model DQ228

> Model DQ215

Model DQ214

> Model DQ202A

- RM02/RM05/RM80 emulation

- · 22-bit addressing

- Universal Formatting™

- 56-bit ECC

- RSX-11, RSTS and UNIX

- Drive capacities to 600MB

- RK06/RK07 emulation

- 22-bit addressing

- Universal Formatting™

- 56-bit ECC

- RT-11, RSX-11, RSTS and TSX-Plus\*\*

- Drive capacities to 160 MB

- RL01/RL02 emulation

- 22-bit addressing

- Universal Formatting™

- 56-bit ECC

- RT-11, RSX-11 and RSTS

- Drive capacities to 40 MB

- RP02/RP03 emulation

- Universal Formatting™

- RT-11, RSX-11, RSTS and TSX-Plus

- Drive capacities to 160 MB

PROPRIETARY WINCHESTER DISK CONTROLLERS

· SA4000 I/O compatible

• RT-11, RSX-11 and RSTS

Drive capacities to 40 MB

• RL01/RL02 emulation

Model DQ404

> Model DQ413

- · Priam I/O compatible

- RP02/RP03 emulation

- RT-11, RSX-11 and RSTS

- Drive capacities to 154 MB

Model DQ414

- Priam I/O compatible

- RL01/RL02 emulation

- RT-11, RSX-11 and RSTS

- Drive capacities to 40 MB

ST506/412 WINCHESTER DISK CONTROLLERS

ST506 I/O compatible

RK06/RK07 emulation

Enhanced 32-bit ECC

· 22-bit addressing

Model DQ615

Model DQ634

- DMA Systems Micro Magnum compatible

- 22-bit addressing

- RL01 emulation

- Enhanced 32-bit ECC

- RT-11, RSX-11 and RSTS

Model DQ614

- ST506 I/O compatible

- RL01/RL02 emulation

- Enhanced 32-bit ECC

- · 22-bit addressing

- RT-11, RSX-11, RSTS and TSX-Plus

In addition, DILOG also offers you a full range of removable disk and tape controllers for Q-BUS and UNIBUS\* (PDP/VAX) computer systems.

• RT-11, RSX-11, RSTS and TSX-Plus

Write or call for complete details and prices of DILOG's full line of Q-BUS and UNIBUS mass storage Disk and Tape Controllers.

\*Trademark Digital Equipment Corporation

\*Trademark Digital Equipment Corporation

\*\*Trademark s&h computer systems, inc.

DILOG

DISTRIBUTED LOGIC CORPORATION

64-A White Street Red Bank, NJ 07701 (201) 530-0044 12 Temple Square Aylesbury, Buckinghamshire England HP 20 # 2QL (0296) 34319 TLX 837038

12800 Garden Grove Blvd. Garden Grove, CA 92643 (714) 534-8950 TLX 681399

Write 1 on Reader Inquiry Card

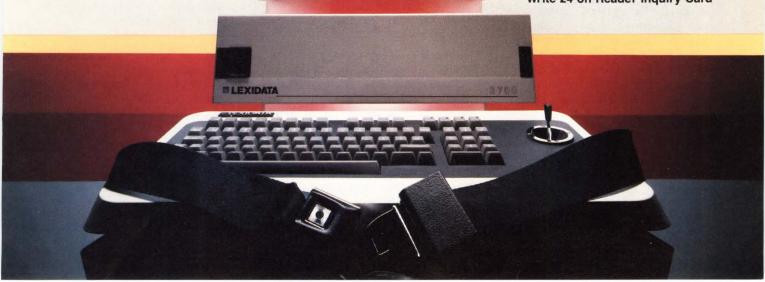

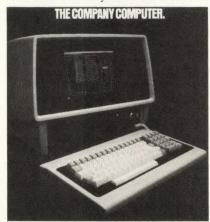

Power, versatility, and superior ergonomics.

THE OVT-108 TERMINAL

Quine.

A Subsidiary of ITT

## The Great Emulator.

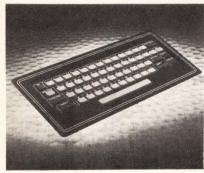

Qume's new QVT 108m CRT terminal emulates Televideo models 925, 920 and 912, making it a perfect fit for operators familiar with any of these terminals. It more than matches the Televideo 925 with sophisticated features like 11 function keys, 12 editing functions, 25th status line, a menu set-up mode, two full pages of screen memory, and many other standard features.

The QVT 108 takes up minimal workspace, and operators will love its ergonomic design: a non-glare green or amber screen with full tilt and swivel, a big 9 x 12 character matrix to minimize eyestrain, and a lowprofile, detached keyboard.

Engineered and built to Qume's exceptional reliability standards, the QVT 108 is backed by our six-month warranty and a nationwide service network. Features

• Local or duplex editing • 11 Function keys (22 functions total) . Bidirectional auxiliary port . Two pages of screen memory . Line drawing graphics character set

• Tilt/swivel, non-glare, green screen (amber optional) • 9 x 12 character cell resolution, 7 x 9 character size

• Detached, low-profile typewriter style keyboard with numeric pad • 24 lines x 80 characters with a 25th status/menu/user-programmable line • Screen-saver time out (an inactive terminal shuts off its screen after fifteen minutes with no screen data loss) • 5 video attributes; blink, blank, reverse video, underline, and half-intensity \* Televideo model 925 code compatible

• Emulations: Televideo 925 and 912/920 • Self test • Time of day • Monitor mode • Switching power supply (efficient operation and low power consumption)

Display Format

24 lines x 80 characters 25th status/set-up/user programmable line

Character Formation

7 x 9 matrix in a 9 x 12 cell

Displayed Character Set

96 ASCII characters, 32 control character symbols, and 15 line-drawing symbols

Editing (Local and Duplex)

Cursor: up, down, left, right, home. Character/line insert and delete, erase to end of line/page, tab, back tab, alternate page

Communications Interface EIA RS232-C, optional current loop (active or passive)

Communications Protocols DTR and/or XON/XOFF

Communications Modes

Full or half duplex, block line or block page; 7 or 8

**Baud Rates**

16 selections from 50 to 19.2k

**Auxiliary Port**

Bidirectional. Modes: parallel, transparent, screen copy.

EIA RS232-C

Tilt/swivel, 12-inch diagonal, non-glare green (optional

non-glare amber) Character Attributes

Blink, blank, underline, reverse video, half intensity

Keyboard

Detached, low-profile (home row 30mm from work surface), alphanumeric keys, 14-key numeric pad, 11 function keys (22 functions with shift), defeatable autorepeat and key click, 12 editing keys. Print, set-up, and scroll lock keys

Fields

Protected and unprotected

Parity

Odd, even, mark, space, none

Screen-Saver

Screen shuts off after 15 minutes of inactivity without data loss

Screen Memory

Two page

Set-Up Mode

Menu-style preserved in non-volatile memory (lithium battery with 7-year life)

Power Supply

Switching-type (low power consumption)

Amber screen 14" screen 20mA current loop

Special character sets Command Set

Televideo 925 compatible

Emulations

Televideo 925

Televideo 912/920

Power Requirements

95-125 VAC 200-264 VAC

50/60Hz, 30W

Keyboard 1.5"(H) x 18"(W) x 8"(D) Display 14"(H) x 13"(W) x 12"(D)

Weight

Keyboard 3 lbs., display 19 lbs

Command Codes

ESC =rc Address cursor, row, column Address cursor, page, row, column ESC - prc ESC v Auto page on ESC w Auto page off Back tab ESC I CTRL/G Bell ESC B Block mode on ESC ' Transparent print or ESC a Transparent print off CTRL/M Carriage return Character delete ESC W ESC Q ESC 3 Character insert Clear all column tabs Clear all to half intensity ESC, blank characters

Clear unprotected to blank characters

ESC; or CTRL Z or ESC +

ESC

ESC C

ESC @ ESC A CTRL/V

CTRL/~

CTRL/H

CTRL/L

CTRL/T

CTRL/N

ESC g

ESC CTRL/R

ESC T ESC Y

ESC .

ESC

ESC R

FSC F

ESC #

ESC U

ESC K

ESC J

ESC P ESC '

ESC &

ESC /

ESC b

ESC j

ESC o ESC n

ESC 6 ESC 4

ESC s

ESC S ESC 7

ESC 1

ESC .(n)

ESC p(n) ESC G(n)

CTRL/I

ESC (

ESC

FSC

ESCx4(nn)

CTRL/\_ ESC d

CTRL/J

ESC f (text) CR

ESC u or ESC X

CTRL/O

Clear unprotected to nulls Conversation mode Copy print mode on Copy print mode off Cursor down Cursor home Cursor left Cursor right

Cursor up Disable bidirectional port

Disable XON/XOFF control

Disable status line Display user line Duplex edit on Enable bidirectional port Enable XON/XOFF control

Erase to EOL with blanks Erase to EOP with blanks Field tab

Keyclick off Keyclick on Line delete

Linefeed Line insert Load user line

Local edit on Lock keyboard Monitor mode off

Monitor mode on Next page Newline

Normal video Previous page Print page

Protect mode off Protect mode on Read cursor, page, row, column

Read cursor, row, column Reverse video Reverse linefeed Screen, blank Screen, normal

Select termination character Send line all Send line unprotected only

Send message all Send message unprotected

Send page all Send page unprotected only Set column tab

Set cursor attributes Set printer termination character Set video attribute

Unlock keyboard

Write protect off Write protect on

Load time Read time

Special graphics off Special graphics on

ESC sp n<sub>1</sub>n<sub>2</sub>n<sub>3</sub>n<sub>4</sub>n<sub>5</sub> ESC sp 2 ESC % ESC % ESC \$ Authorized Qume Distributor/Dealer

Qume Corporation 2350 Qume Drive San Jose, CA 95131

**Qume Corporation** 1754 Technology Drive Suite 110 San Jose, CA 95110 (408) 942-4111

**Qume Corporation** 6011 Bristol Parkway Suite 150 Culver City, CA 90230 (213) 410-1458

Qume Corporation 1820 East Gary Avenue Suite 104 Suite 104 Santa Ana, CA 92705 (714) 957-4040

Qume Corporation Shamrock Park Office Suite 110G 2323 South Troy Street Aurora, CO 80014 (303) 752-3000

**Qume Corporation** Unit B-2 Palatine, IL 60067 (312) 991-7250

**Qume Corporation** 5335 Far Hills Avenue Suite 107 Dayton, OH 45429 (513) 439-0469

Clear all to nulls

Clear column tab

**Qume Corporation** 1925 Westridge Drive Irving, TX 75062 (214) 659-0745

**Qume Corporation** 20 Mayfield Rd. Edison, NJ 08837 (201) 225-5005

Qume Corporation 19 Crosby Drive Bedford, MA 01730 (617) 275-3200

Qume Corporation 4319 Covington Highway Suite 212 Decatur, GA 30035 (404) 284-8500 GERMANY

FSC.

ESC 2

QUME GmbH Eicheisstr 31 4000 Düsseldorf 13 West Germany PH: 0211743016

**ENGLAND**

QUME (UK) Ltd. 1 Bridgewater Close Reading, Berkshire UK PH: 734-584-646

FRANCE

QUME GmbH Bureau de Liaison France 20, rue Thiers 92100 Boulogne, France PH: (1) 6082334

CANADA

QUME Canadian Office 207 Place Frontenac PTE Claire Quebec, Canada H9R4Z7 (514) 695-3837

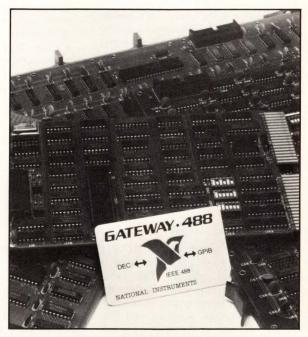

## 20 major capabilities together for the first time on a single SMD controller!

## TRUE DEC implementation and media compatibility

Switch selectable auto-configuration

Data capacity up to 1,024 gigabytes (formatted) • TRUE SMD interface (standard drivers and receivers) • Emulates RM02, RM03, RM05, RK06, RK07 • Mixes emulation modes on a single Unibus controller • Compatible with all major Operating Systems--DEC and others (uses standard drivers--no patches required) • DEC diagnostic compatible • Disk sector buffering (no "data lates") • Automatic self-test upon power up Built-in bootstrap loader

DMA throttle - no interleaving required • 16, 18, 22 - bit addressing • TRUE media compatibility • TRUE DEC ECC/CRC implementation • Multiple word size block transfer Up to four physical drives per controller

Up to eight logical drives per controller • Standard DEC media defect flagging • Standard DEC device addressing, interrupt priority and interrupt vectoring-others can be user selectable • Maximizes disk data transfer rate for any bus band width (grows with technology)

THE WORLD'S LARGEST INDEPENDENT MANUFACTURER OF COMPUTER INTERFACES.

1995 N. Batavia St., Orange CA 92665 (714) 998-6900 TWX 910-593-1339

## Digital Design

p. 28

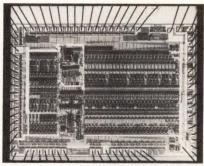

(Photo courtesy DEC)

p. 48

(Photo courtesy Honeywell)

p. 70

(Photo courtesy Intel Corp.)

## Cover

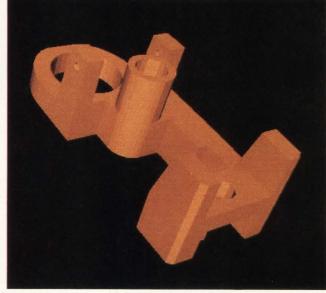

Shown on the cover are the 2-chip General Data Processor and single chip Interface Processor, part of Intel Corp.'s 5-chip iAPX 432 Fault Tolerant Multiprocessor system. Center photo by Rudi Legname. Cover graphics by Henry Jackson, Benjamin Morse, Inc.

Published monthly thirteen times a year with two issues in November. Copyright © 1983 by Morgan-Grampian Publishing Company, 1050 Commonwealth Ave., Boston, MA 02215. Second class postage paid at Boston, MA and at additional mailing offices. POSTMASTER: Send address changes to Morgan-Grampian Publishing Company, 1050 Commonwealth Ave., Boston, MA 02215. ISSN 0147-9245

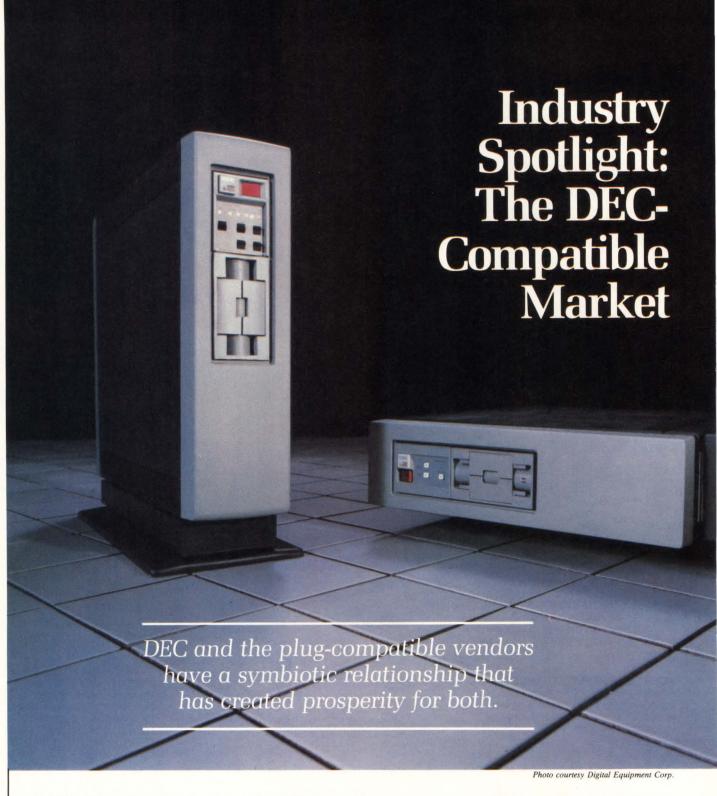

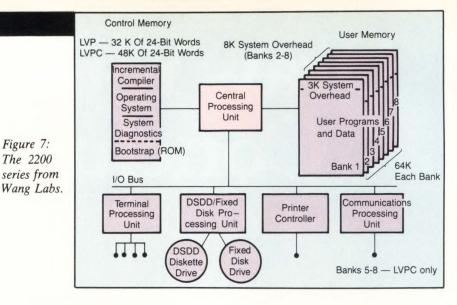

| COMPUTERS/SYSTEMS                                          |

|------------------------------------------------------------|

| Industry Spotlight: DEC-Compatible Market                  |

| Display Processors—The Design of Computer Graphics Systems |

| Minicomputers Face Stiff Competition                       |

| Fault Tolerant Architectures                               |

| Unix Leads To Greater Flexibility                          |

| Graphics System Design                                     |

| Innovative Design                                          |

| PERIPHERALS                                                |

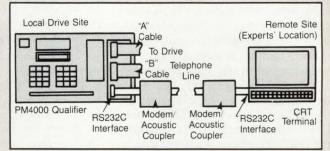

| Self-Testing Components Pinpoint Network Faults            |

| Innovative Design                                          |

| COMPONENTS                                                 |

Washington Report . . . . . . . 12

Technology Trends . . . . . . . . 15

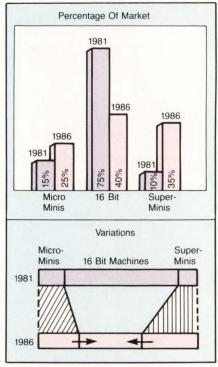

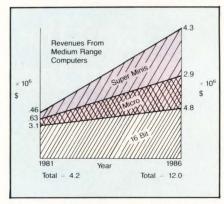

Market Trends......23

Product Index.....98

| News Update10 Reader Service99          |

|-----------------------------------------|

| Application Notebook                    |

| Graphics System Design                  |

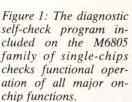

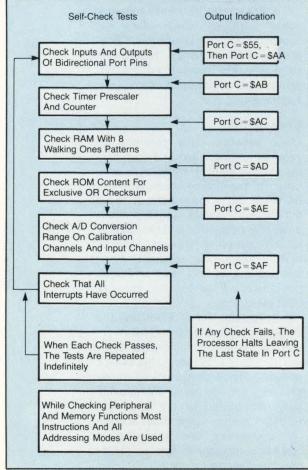

| Self Diagnosis Of Single-Chip Computers |

|                                         |

Calendar..... 118 Advertiser Index . . . . . . . . . 118

New Literature ..... 116

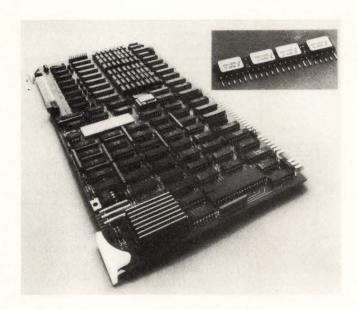

Custom LSI devices and new packaging techniques solve PCB space constraints.

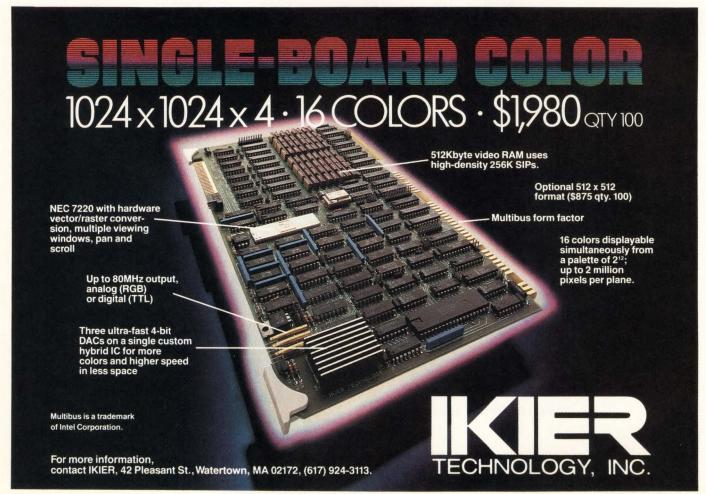

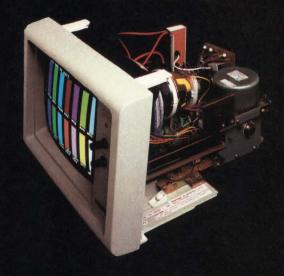

Innovative Packaging Improves Color Graphics Boards'

| Distal  | D :    | - A                      | 1000 |

|---------|--------|--------------------------|------|

| Didital | Design | <ul><li>August</li></ul> | 1900 |

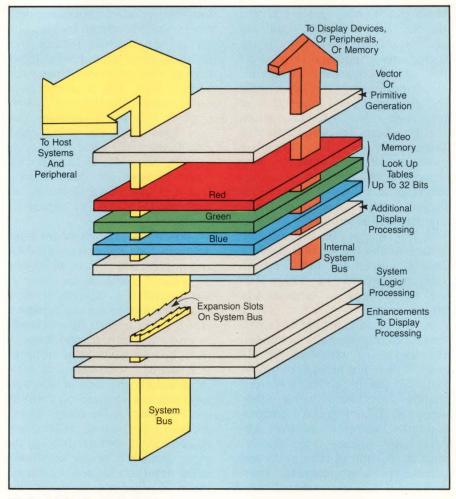

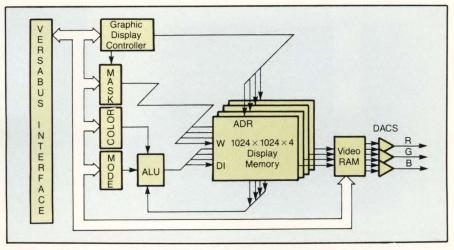

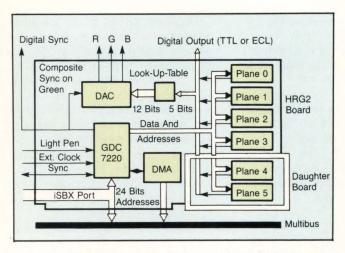

## GRAPHIC CONTROLLER MLZ-VDC

Heurikon unveils a graphic solution for your microcomputer application.

On-Card Feature Summary CPU Section:

Z80A CPU Z80A DMA

Up to 32K bytes of EPROM/ROM

Up to 16K bytes of RAM

One iSBX module module

132 byte bi-directional FIFO Buffer

Multibus<sup>TM</sup> Multimaster or Slave

mode

24 bit address bus

Memory mapping RAM

Hardware and software selectable bus maps

## Video Section:

NEC 7220 graphics controller chip 512K bytes of video memory, arranged as 4 overlapping planes, 1024 by 1024 pixels

640x480 display format standard 16 Color programmable look-up

able

4096 color palette

Light Pen I/F

Interlaced video

Non-interlaced video

Composite SYNC

Separate SYNC

BNC or MOLEX connectors on card,

for the video

Call Heurikon Direct 1 800 356-9602 In Wisconsin 1 608 271-8700

Write 53 on Reader Inquiry Card

## Has Your Address Changed? Are You Planning To Move In The Near Future?

Please use the enclosed qualification form to notify us of your address change. A change of address requires that you fill out the entire form. Please allow 6-8 weeks for your change to take effect.

## **Digital Design**

Publisher Jeffrey C. Hoopes

Editor-in-Chief Jerry Borrell

Production Editor Debra A. Lambert

Technical Editor Dave Wilson

West Coast (408) 371-9620 Technical Editor

Technical Editor Doug Eidsmore

West Coast (213) 981-3300

Technical Editor Mike Cashman

Associate Editor/

Directory Editor Julie Pingry

Departments Editor Mary Rose Hanrahan

Editorial Assistant Andrea Coville

International

Electronics Editor Ron Neale

International

Computers Editor Eric Wignall

Contributing Editor

Data Communications

Data Communications Walter Bolter, Ph.D

Contributing Editor Graphics Systems

Thomas DeFanti, Ph.D.

Contributing Editor

Software Andrew Rubel

Washington Correspondent Anne Armstrong

Publication Services Manager Charlotte King

Production Manager Jon Buchbinder

Art Director Richard D. Sarno

Associate Art Director Tilly Berenson

Assistant Art Director Maureen Bernardini

Production/Graphics

Martha Watjen

Judy Osburn,

Joan Scheffler,

Vete Saulenas, Don Schaff, Paul Christo

Promotion Manager Elaine Bull

Research Helen Obermayer, Peter Micheli

Circulation Manager Hugh Dowling

**Circulation** Sarah Binder, Gary Byrne, Deborah Goldstein, Lynda Neue

General Administration Karen Melanson

Nancy Deveau Dianna Lynn Reed Leslie Saunders Debra Sturm

Group Publishing Director Albert J. Forman

## Advertising Sales

Northeast: John C. Moon (617) 232-5470, 1050 Commonwealth Avenue, Boston, MA 02215

Middle Atlantic: Barbara L. Smith (212) 340-9700, Morgan-Grampian Publishing, 2 Park Avenue, New York, NY 10016

Southeast: Rich Santos (404) 393-2505, 1224 Mt. Vernon Road, Dunwoody, GA 30338

Midwest, South Central: Hank Bean (312) 346-4611, Morgan-Grampian Publishing, 2 North Riverside Plaza, Chicago, IL 60606

Northwest: Cassandra Ewing, Ralph Petersen (408) 371-9620, 1901 S. Bascom, Suite 1005, Campbell, CA 95008

**Southwest:** Pam Rock **(213) 981-3300**, 15910 Ventura Boulevard, Suite 1215, Encino, CA 91436

Telemarketing/Northwest: (408) 371-9620, 1901 S. Bascom, Suite 1005, Campbell, CA 95008

**Telemarketing/Southwest: (213) 981-3300,** 15910 Ventura Boulevard, Suite 1215, Encino, CA 91436

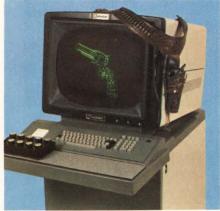

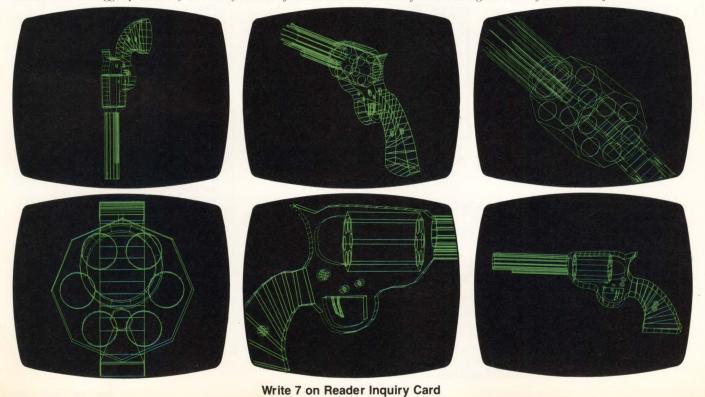

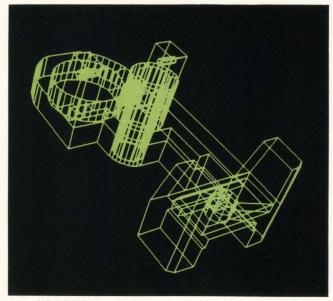

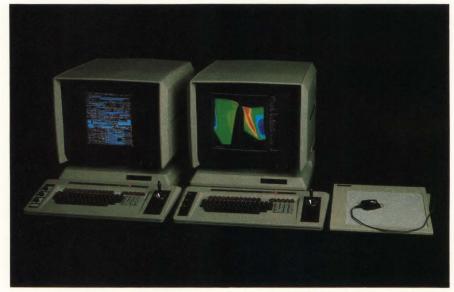

## The Lundy UltraGraf is absolutely the fastest draw in the West or anywhere else.

This is the fastest, most intelligent 3-D computer graphics workstation available.

The superlatives would seem to indicate a high price, too. But the Lundy UltraGraf workstation is surprisingly low cost considering its unmatched performance features.

At Lundy we don't develop technology for its own sake; we develop it to meet your needs. In the case of 3-D computer graphics workstations, you needed more speed, higher IQ, larger display and easier operation. UltraGraf delivers all four.

## The Lundy UltraGraf is first when it comes to speed and IQ.

Keys to UltraGraf's instant response are a high speed microcomputer and a high resolution vector display, both developed by Lundy.

Besides these features, we've designed more intelligence into the workstation, so UltraGraf places fewer demands on your host computer.

The result is unmatched interaction while freeing up your host computer to concentrate on other operations.

## 19 × 15 inches sets a new screen standard.

UltraGraf's 21-inch CRT has the largest viewing area— $19 \times 15$  inches—in the industry. Fast vector drawing and mini-

Lundy UltraGraf sets 3-dimensional standards.

mum operator time produce easy-toread, flicker-free images. Spot size is only one ten thousandths of an inch, which produces remarkable crispness and clarity.

Furthermore, UltraGraf is easier to use. You send a picture only once, instead of resending over and over as

with many other systems. And you have local storage of all control functions for the interactive input devices. This provides maximum input flexibility, with minimum keyboarding.

## Lundy helps you see more in graphics.

When you take a close look at our graphics terminals, service, support, software, systems capability, enhancements—and our company—you'll understand why Lundy can help you see more in graphics now and in the long term.

For more information about our 3-D UltraGraf, or other CAD/CAM products, write Lundy Electronics & Systems, Inc., Glen Head, New York 11545, or call: (516) 671-9000.

Get the draw on sluggish productivity with Lundy's UltraGraf. Shown here are six views of a six shooter generated in just a matter of seconds.

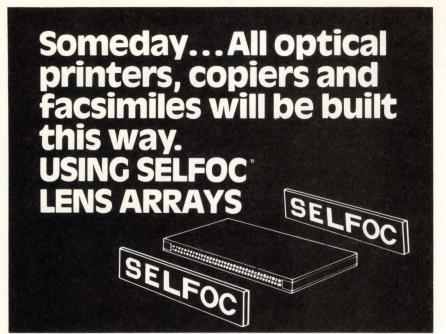

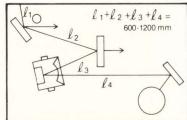

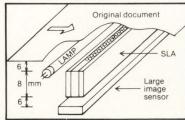

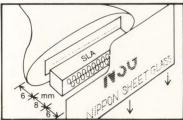

For now, only state-of-the-art optical printers, copiers and facsimiles are using SELFOC Lens Arrays (SLA). Spherical lenses, until now the only feasible way to transfer optical information, have given way to the size reduction, fidelity and reliability of SELFOC Lens Arrays.

## **COPIERS**

Using conventional lenses, the optical path is typically 600-1200 mm.

## 64-74 mm SELFOC Lens Array

The SELFOC Lens Array reduces the path length to 64-74 mm.

## FACSIMILES Reading Head

Typical inputs:

- Documents

- Display panels

- LED source arrays

## **PRINTERS** Writing Head

Typical receivers:

- Photo drums

- Image sensors

- Photo detector arrays

For complete specifications and application information on how SELFOC Lens Arrays are replacing conventional optics in printers, copiers and facsimiles, write or call:

## NSG America, Inc.

A Subsidiary of Nippon Sheet Glass Co., Ltd.

New Jersey Office: (Technical Representative) 136 Central Avenue, Clark, N.J. 07066 (201) 499-0939

## Write 9 on Reader Inquiry Card

## Digital Design

## EDITORIAL, SALES, AND CIRCULATION OFFICES

Digital Design 1050 Commonwealth Avenue Boston, MA 02215 Telephone: (617) 232-5470

MORGAN-GRAMPIAN

## CORPORATE HEADQUARTERS

Morgan-Grampian Publishing Company, 2 Park Avenue, New York, NY 10016, (212) 340-9700. Domenic A. Mucchetti, President.

## **EXPOSITIONS GROUP**

Morgan-Grampian Expositions Group, 2 Park Avenue, New York, NY 10016 (212) 340-9700. Robert Poggi, Director.

The following is a list of conferences sponsored by the Expositions Group:

ATE West CADCON East

CADCON West ATE Central

ATE Northwest CADCON Central

ATE Fast

In addition to Digital Design, Morgan-Grampian publishes the following in the United States: Circuits Manufacturing • Electronic Imaging • Electronics Test • Computer & Electronics Marketing

## **New Publication Development**

H.G. Buchbinder, Director

Morgan-Grampian also publishes the following in the United Kingdom: Electronic Engineering • Control & Instrumentation • Electronic Times • What's New in Electronics • What's New in Computers.

DIGITAL DESIGN serves the manufacturers of computer-related OEM products. This includes primary computer and systems manufacturers, systems integrators, components and peripheral manufacturers, integrating OEM's and commercial end users. These companies manufacture products used to control machinery, equipment and information in manufacturing, material processing, machine tools, packaging, health care, defense, data processing, communications, instrumentation, and scientific and business operations.

## **☆ABP** ♥BF

## SUBSCRIPTION POLICY

DIGITAL DESIGN is circulated only to qualified research, development and design engineers and engineering managers primarily responsible for computer products and systems in OEM plants. To obtain a complimentary subscription, request (on company letterhead) a qualification card from Circulation Director. For change of address, attach old address label from recent issue to new company letterhead or note. Send this plus request for new qualification card to:

## Circulation Department DIGITAL DESIGN 1050 Commonwealth Avenue

1050 Commonwealth Avenue Boston, MA 02215

Subscription rates: non-qualified subscribers (US and Canada) — \$35/yr; foreign — surface mail — \$45; air mail — \$70. Single copies — \$4.

DIGITAL DESIGN solicits editorial material and articles from engineers and scientists. Contributors should submit duplicate manuscripts typed with two spaces between lines. All illustrations should be clear; components on all schematics and line drawings should be labeled. The editors assume no responsibility for the safety or return of any unsolicted manuscripts.

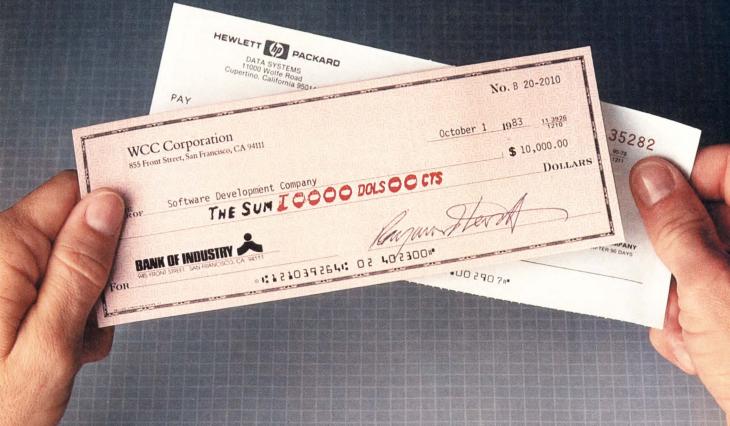

## Writing HP software can be doubly rewarding.

Doubly rewarding, because every time Hewlett-Packard sells a new system with your software, you'll not only get a check from the customer, but one from HPas well!

As thanks for writing software for our systems, we'll give you a bonus of 30% of your software's sales price—up to 6% of the net HP system's price. That could mean \$3,000 on a \$50,000 system...or as much as \$30,000 on a \$500,000 system. And you'll get it every time a new system is sold with your software.

We won't tell you what kind of program to write. What industry to write it for. Or even specify the system. Our only restriction is that, to qualify for the bonus, your software must sell for at least \$10,000.

Of course, extra cash isn't the only incentive. To help you get started, we'll sell you a development computer at a 40% discount.

We'll also promote your software in HP catalogs, direct mail and advertisements. And you'll have the benefits of being associated with HP—one of the worldwide leaders in computing systems. A company whose products range from widely-used business computers, like the HP 3000, to one of the world's most advanced 32-bit computers, the HP 9000.

If you'd like to learn more, write to Hewlett-Packard, Attn Gwen Miller, Dept. 91173, 19447 Pruneridge Avenue, Cupertino, CA 95014. In Europe, write to Henk van Lammeren, Hewlett-Packard, Dept. 91173, P.O. Box 529, 1180 AM Amstelveen, The Netherlands.

We'll give you all the details on our HP Plus Software Supplier program. And all the reasons why it will be rewarding for you to develop software for HP.

## NEWS UPDATE =

## **Pilot Application**

Concord Data Systems (Waltham, MA) announced that General Motors Manufacturing, Engineering and Development (ME&D) has selected its Token/Net local area network for use in GM's Multi-Vendor Node Development pilot project. The pilot application is the combined effort of the GM Assembly Division, ME&D and other General Motors divisions, and is designed to allow non-compatible computers and programmable devices within manufacturing to communicate with one another. Token/Net, a broadband token passing local area network, conforms to GM's Manufacturing Automation Protocol of IEEE-802 Token Bus. It will provide a physical and link layer (ISO layers 1 and 2) interconnection between IBM, DEC, Hewlett Packard, and other non-compatible computers used in GM's manufacturing.

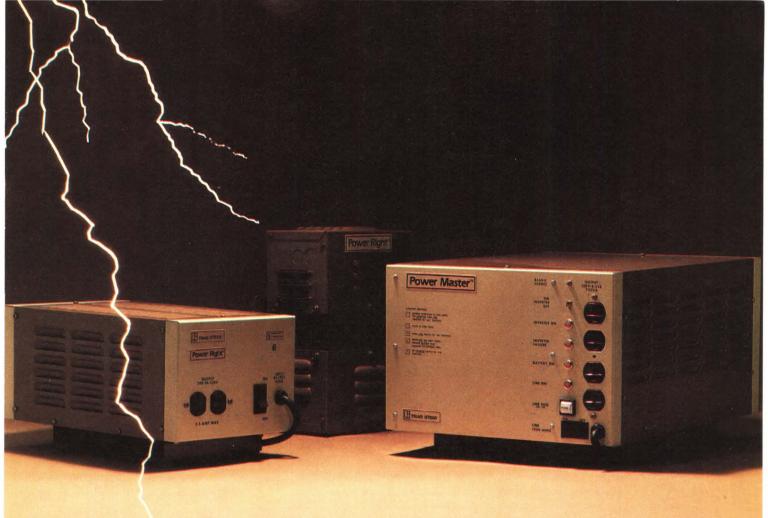

## Gould To Supply UPS To Intel

Intel Corp. stated it has arrived at an agreement with Gould Inc. for Gould to make and supply the Uninterruptible Power Systems (UPS) for Intel's FAST-3825 Semi-Conductor Disk System.

Gould's UPS is designed to supply automatically as much as 15 minutes of uninterrupted power if electrical service fails. Thus, Intel's FAST-3825 Random Access Memory (RAM) is protected while power is being restored to the CPU.

## **VMEbus Users Group Formed**

The VMEbus, an international computer architecture that was introduced eighteen months ago by Motorola, Signetics, Mostek, Philips, and Thompson/EFCIS, has completed the acceptance cycle with the formation of the VMEbus Users Group. A small group, representative of the hundreds of companies that are currently using the VMEbus architecture in the U.S., met on May 18th, 1983 to approve the organizational charter, appoint an Advisory Board and initiate several ad hoc committees. The Users Group approved the preliminary

charter, initiated a data base for VMEbus Users and committed to publishing two newsletters between now and the first official VMEbus Users Group meeting. The first meeting of the Users Group will be held during the WESCON Show in San Francisco the second week in November. Contact: Astraea Computer Corp., 846 Del Ray Ave., Sunnyvale, CA 94086.

## AMI, Daisy Agreement

American Microsystems, Inc. (AMI), a subsidiary of Gould Inc., and Daisy Systems Corp. have reached an agreement in principle by which AMI will make a volume purchase of Daisy's family of engineering workstations. With the volume that is anticipated, AMI will be able to offer its customers a favorably priced turnkey system for design of MOS circuits and systems.

This agreement will allow system designers to use AMI's extensive libraries of standard cells and gate arrays, integrated in computer-aided-engineering (CAE) design system software and hardware. The AMI and Daisy joint agreement will be based on a volume purchase of Daisy's LOGICIAN and GATE-MASTER systems by AMI. AMI and Daisy plan a joint marketing effort of these systems.

## Mostek Receives JAN Qualification

United Technologies' Mostek Corp. has become the first 64K dynamic RAM supplier to receive Joint Army Navy (JAN) qualification. Designated the MIL-M-38510/244-02 under the JAN 38510 program, the Mostek 64K dynamic RAM provides an access time of 150ns, and uses the Mostek Scaled POLY 5<sup>®</sup> process technology with advanced circuit techniques.

## Foreign Trade Zone Attracts High Tech

Construction has begun at Boston's Logan Airport for the \$200 million Bird Island Flats Development that will house the first Foreign Trade Zone at a U.S. international gate-

way. Groundbreaking ceremonies took place on April 4, and the zone is expected to receive final approval from the U.S. Customs Department soon. The zones were created by Congress as legal islands with the purpose of stimulating international trade by exempting products from import duties, excise taxes and bonding costs.

## Micro-Style Software For Mainframe Users

The Mega Group, Inc. (Irvine, CA) has been formed to develop microcomputer-style software that will operate in mainframe system environments. The Mega Group's products will take concepts such as electronic spreadsheets, personal data bases, graphics and word processing, from the micro computer software library and integrate them into the installed mainframe market.

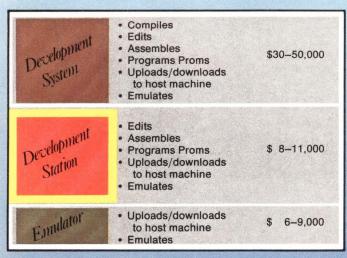

## **Emulogic Receives \$3 Million**

Emulogic, Inc. (Norwood, MA), a producer of universal microprocessor development systems, has received \$3 million in venture capital financing. The funds will be used for working capital to finance rapidly accelerating demand for its products. Emulogic's ECL-3211 systems are sold to companies producing consumer and industrial products incorporating microprocessor chips.

## High-Speed Logic Cross-License

Motorola, Inc. and Monolithic Memories, Inc. jointly announced the execution of a cross-license agreement covering a broad range of high-speed logic products.

Under terms of the agreement, Monolithic Memories is licensed to produce Motorola's ECL logic devices, specifically the MECL 10KH series logic circuits and MCA600ECL and MCA1200ECL macrocell arrays. Motorola is licensed to produce Monolithic Memories' ECL programmable array logic (PAL) circuits and 74LS series of buffers and dynamic RAM drivers.

## CHANGE THE WORLD.

GR-2412 with standard

GR-2212 (monochrome) also available.

0-in. x 20-in. digitizing tablet

Or anything else you can display. Easier and faster than you imagine. Because D-SCAN's new GR-2412 terminal is changing the cost/performance standards for raster scan graphics.

Its world address space, for example, is a full 32K by 32K. Large enough to handle the most ambitious project. Yet easily manageable with dynamic zoom, pan, window, and viewport commands.

Its zoom operation faithfully preserves resolution and detail, instead of simulating it with pixel replication.

And those aren't all the improvements we've made.

Our dual microprocessor architecture draws 12,500 short vectors per second while transferring data at 19.2 kilobaud. And our exclusive anti-aliasing hardware removes jaggies without affecting drawing speed.

About the only thing we didn't change is our long list of standard features. Like our high resolution 1024x780 display. Local transforma-

tions. Up to 768K bytes of local segment memory. 4014 emulation mode. And the 10 years of Daini Seikosha (Seiko) craftsmanship in every D-SCAN product.

If you're ready to make some changes, contact us at Seiko Instruments U.S.A., Inc., 2620 Augustine Drive, Santa Clara, California 95051. Telephone (408) 727-0768.

We'll give you a terminal that can take on the world.

Seiko Instruments U.S.A., Inc.

## WASHINGTON REPORT

by Anne Armstrong

A secondary skirmish in the war over semiconductor chips has been the question of chip piracy. Everyone seems to agree that it's a growing problem and some type of legislation is needed to protect the investment which goes into designing and manufacturing chips. The disagreement has been whether patent, trademark, copyright or some new special protection is most suitable.

Recent discussions have focused on two similar bills introduced in the House and the Senate which would place chips and the masks used to produce them under the protection of a new section of the copyright law. Sponsored by Senators Charles M. Mathias, Jr. (R-Md.) and Gary Hart (D-Colo.), S. 1201, "The Semiconductor Chip Protection Act of 1983," is a refinement of several bills introduced in earlier years. (The House version is H.R. 1028.)

Basically, the legislation would create a new category of copyrightable work known as "mask works." These mask works would have a limited term of protection—10 years from first authorized use instead of copyright's normal 75—and would offer special protections for innocent or unknowing infringers.

"Current law gives only very limited protection to semiconductor chips," said Sen. Mathias. "Patent law can protect the basic electronic circuitry used in the chip, but not its carefully developed design. By giving chip engineers and manufacturers copyright protection for a 10-year period, S. 1201 will protect their R&D investment. It will also protect innocent purchasers of pirated chips, by including a compulsory licensing provision allowing them to use that chip after paying a royalty to the innovating firm, and by eliminating any liability for innocent infringement."

Although the obviously industrial nature of the semiconductor chip might lead observers to wonder why patent law would not be a better way to protect chips, none of the major players have suggested it. Patent law's rigid standards for novelty and invention eliminate most chips.

Trade secret protection wouldn't work either because it is based on the idea of keeping the components or parts secret, and chips are widely available and easily disassembled to reveal the design.

Although legislation protecting chips with copyright has been introduced and died quietly before, there is more attention focused on the problem today. Trade questions are getting more press interest and the dollars at stake keep going up. The Semiconductor Industry Association does not have figures on the losses each year due to chip piracy but Intel Corp, a major chip manufacturer, estimates that an investment of \$80 million is required to bring a new family of chips to market. A simple photographic copy of the main chip would cost a pirate only \$100,000. In fact, Intel's corporate counsel says that every new chip is evaluated for the risk of piracy, and as a result, many chip designs are cast aside because the threat of piracy makes the investment too risky.

Proponents of the legislation maintain that although American copyright law traditionally protected "writings" as described in the Constitution, the copyright concept has now been extended beyond works that convey ideas or have artistic merit. In fact, copyright has been granted on belt buckles, E.T. lunchboxes, ashtrays, pill boxes and a host of similar items.

Currently supporting the legislation is the Semiconductor Industry Association and with minor modifications, the Computer and Communications Industry Association. On the opposite side are the Association of American Publishers, the Association of Data Processing Service Organizations, the Information Industry Association, a committee of the American Bar Association, and the U.S. Copyright Office, all of whom for

a variety of reasons believe that the copyright act is being twisted beyond its limits and is the wrong way to try and protect chips.

The opponents base their objection primarily on four arguments: copyright does not protect useful articles per se; it protects the design of a useful article only to the extent that it can be identified as separate from the article itself and can exist independently; copyright of a drawing does not protect against duplication of the article itself; and copyright protects only expression, not ideas, plans or processes. They also believe the question of legitimate reverse engineering has not been adequately addressed. The distinctions between photographically copying the masks and reproducing the chip, and photographically copying the masks for the purpose of studying and drawing new schematics is a fine and somewhat obscured line.

A compromise which has been mentioned by several organizations is new legislation which would not extend copyright, but provide copyright-like protection for works such as chip masks which do not fit into the copyright term "original works of author-ship." One model suggested for this legislation is H.R. 2985, "Design Protection Act," a retooling of a bill introduced in the last Congress, H.R. 20. This bill provides protection for ornamental designs of useful articles. Counsel from many organizations want to "fix" the design bill so that it can be a model for chip protection. If the fixers do not destroy the fabric of the original legislation, it might prove the better avenue for manufacturers to pursue.

Even Mathias is not certain copyright is the best way. "Our aim is to deter and to punish chip piracy, without discouraging legitimate reverse engineering. The copyright law seems to be the best tool at hand to get the job done, but we must make sure that it isn't stretched out of shape in order to accommodate this new need."

## PKASO Printer Interface Family

Welcomes the New Apple //e... We work together.

PKASO Interfaces come complete with Cable, Instructional Diskette and Comprehensive Manual.

## The PKASO family makes you and your Apple Computer a master of text and graphics.

PKASO makes it easy to use the features of your printer—select character sizes, vary line spacing, even print in colors. Simple PKASO commands make these features usable from the keyboard or a program.

PKASO also adds features to your system. Press a few keys and get a snapshot "dump" of the image you see on the screen—text or graphics. Add new characters and symbols that you couldn't print before, using our SuperFont ™system. Add our new PipeLine™ printing buffer and your printer can take its time while you and your Apple move on to the next task. The PipeLine is a modular add-on to the standard PKASO board.

The PKASO interface is designed for Apple II and Apple III in all the popular configurations. It prints in full color on the IDS Prism Printer, and in striking black on C. Itoh, Centronics, Epson, IDS, NEC, and Okidata matrix printers.

Write 5 on Reader Inquiry Card

## NEW!

The IS Pipeline™ Printing Buffer with Random Access Printing stores paragraphs or pictures for printing in any order—any number of times!

- Universal—works with any parallel (Centronics style) computer/printer combinations.

- 8K to 128K Bytes of memory with data compression for efficient use of memory space.

Interactive Structures Inc. 146 Montgomery Avenue Bala Cynwyd, PA 19004 Telephone: (215) 667-1713

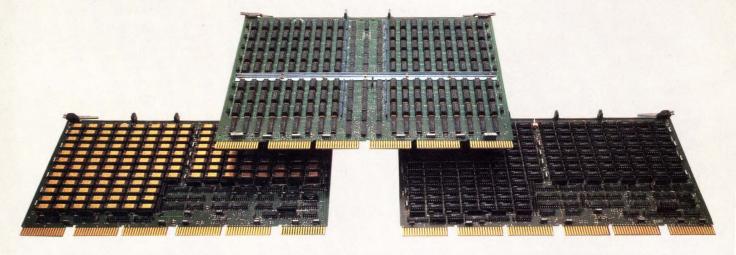

## DEC\* COMPATIBILITY PLUS PERFORMANCE DEPENDABILITY ECONOMY

Monolithic Systems Corporation has provided reliable DEC compatible memory products for over 12 years. In fact, MSC patented the first semiconductor memory product in 1974! The success of Monolithic Systems has been attributed to products that perform better than any other in the business, products that have the modularity to grow with the systems that they're installed in and products that offer the best price in the market. These claims are supported by a one-year warranty which underscores MSC's superior quality in design and manufacturing.

In 1983 MSC will continue to lead the market with products for Q-BUS\* and VAX\* machines. These products will be very formidable contenders for years to come. As always, Monolithic Systems will be on the leading edge of memory technology and innovation with products to last the life of your machine.

For further information on Monolithic Systems Corporation and how we may support your computer needs, call Toll Free 1-800-525-7661.

## Scorp. ... means technically advanced solutions.

## USA

84 INVERNESS CIRCLE EAST ENGLEWOOD COLORADO 80112 303-770-7400 TELEX: 45-4498

## **EUROPE**

JUSTINIANSTRASSE 22 6000 FRANKFURT aM MAIN 1 WEST GERMANY 611590061 TELEX: 41-4561

## CANADA

6503 NORTHAM DRIVE MISSISSAUGA ONTARIO, CANADA L4V IJ2 416-678-1500 TELEX: 96-8769

DEC VAX - 11/730, VAX - 11/750 AND VAX - 11/780 MEMORY

TOTAL DEC HARDWARE AND SOFTWARE COMPATIBILITY

DEC EQUIVALENT PERFORMANCE AND CAPACITY

MSC RELIABILITY, QUALITY AND SERVICE

\*DEC, Q-BUS, VAX and LSI are registered trademarks of Digital Equipment Corporation.

## Z800 Family Features Memory-Management And Cache

A new μP family that runs any software written for the Z80 CPU but offers up to five times greater performance through the use of on-chip peripherals, on-chip cache and instruction enhancements, has been announced by Zilog, originator of the Z80 device.

The family consists of the 8-bit bus Z8108 and Z8208 that are packaged in 40-pin and 64-pin dual in-line packages, and the 16-bit bus Z8116 and Z8216 in 40-and 64-pin packages.

Central to the Z800 µPs is an enhanced version of the Z80 Central Processing Unit (CPU). To better assure system integrity, the Z800 can operate in either User or System mode, allowing protection of system resources from user tasks and programs. System mode operation is supported by the addition of the System Stack Pointer to the working register set. The IX and IY registers have been modified so that in addition to their regular function as index registers, each register can be accessed as a 16-bit general-purpose register or as two single-byte registers.

The Z80 instruction set has been refined, meaning that the Z800  $\mu$ Ps are completely binary-code compatible with present Z80 code. The basic addressing modes of the Z80  $\mu$ P have been aug-

| Prima             | ary File                  | Auxili             | ary File       |

|-------------------|---------------------------|--------------------|----------------|

| A Accumulator     | F Flag Register           | A' Accumulator     | F' Fla         |

| B General Purpose | C General Purpose         | B' General Purpose | C' Gen         |

| D General Purpose | E General Purpose         | D' General Purpose | E' Ger         |

| H General Purpose | L General Purpose         | H' General Purpose | L' Ger         |

|                   | dex Register dex Register |                    | ditio          |

| IX Inc            | lex Register              |                    | nega           |

|                   |                           |                    | mult           |

| PC Pro            | gram Counter              |                    | A dov's        |

| SP S              | tack Pointer              | User               | day's<br>to in |

|                   |                           | System             | 10 11          |

| 4                 | 16 Bits                   |                    | space          |

mented with the addition of Indexed mode with full 16-bit displacement, Program Counter Relative with 16-bit displacement, Stack Pointer Relative with 16-bit displacement, and Base Index mode. The new addressing modes are incorporated into many of the old Z80 instructions, resulting in greater flexibility and power. Some additions to the instruction set include 8- and 16-bit signed and unsigned multiply and divide, 8- and 16-bit sign extension, and a test and set instruction to support multiprocessing. The 16-bit instructions have been expanded to include 16-bit compare, memory Figure 1: Configuration of CPU registers in Z800.

increment, memory decrement, negate, add, and subtract, in addition to the previously mentioned multiply and divide.

F' Flag Register

E' General Purpose

General Purpose

A requirement of many of today's μP-based system designs is to increase the memory address space beyond the 64K byte range of typical 8-bit μPs.

The Z800 µPs have an on-chip Memory Management Unit (MMU) that enables the µPs to address either 512K bytes or 16M bytes, depending on the package of the device. In addition to enabling the address space to be expanded, the MMU performs other memory management functions previously handled by dedicated off-chip memory management devices.

I/O address space has been expanded by the addition of an I/O page register used to select pages of I/O addresses. The 8-bit I/O page register can select one of 256 possible pages of I/O addresses to be active at one time, allowing a total of 64K I/O addresses to be accessed.

| Peripheral<br>Number | Peripheral Name                              | Periphera<br>Number | Peripheral Name                               |

|----------------------|----------------------------------------------|---------------------|-----------------------------------------------|

| z                    | 8108/Z8208 8-bit bus (Z80 control signals)   | ZE                  | 8116/Z8216 16-bit bus (Z-BUS control signals) |

| Z8410                | DMA Direct Memory Access Controller          | Z8016               | DTC Direct Memory Access Transfer Controlled  |

| Z8420                | PIO Parallel Input/Output                    | Z8030               | Z-SCC Serial Communications Controller        |

| Z8430                | CTC Counter/Timer Circuit                    | Z8031               | Z-ASCC Asynchronous Serial Communications     |

| Z8440/1/2            | SIO Serial Input/Output Controller           |                     | Controller                                    |

| Z8470                | DART Dual Asynchronous Receiver/Transmitter  | Z8036               | Z-CIO Counter/Timer and Parallel I/O Unit     |

| Z8516                | DTC Direct Memory Access Transfer Controller | Z8038               | Z-FIO FIFO Input/Output Interface Unit        |

| Z8530                | SCC Serial Communications Controller         | Z8060               | FIFO Buffer Unit and Z-FIO Expander           |

| Z8531                | ASCC Asynchronous Serial Communications      | Z8065               | -Z-BEP Burst Error Processor                  |

|                      | Controller                                   | Z8068               | Z-DCP Data Ciphering Processor                |

| Z8536                | CIO Counter/Timer and Parallel I/O Unit      | Z8070               | Floating Point Processor                      |

| Z8038                | Z-FIO FIFO Input/Output Interface Unit       | Z8090               | Z-UPC Universal Peripheral Controller         |

| Z8070                | Floating Point Processor                     |                     |                                               |

Table 1. Peripheral support for the Z800 Microprocessors

## **Technology Trends**

There are 256 bytes of on-chip memory present on all members of the Z800 family. This memory can be configured as a high-speed cache or as a fixed address local memory. When configured as a cache, the memory can be programmed to be instruction only, data only, or both data and instruction. The cache memory allows programs to run significantly faster by reducing the number of external bus accesses. Operation and update of the cache is performed automatically and is completely transparent to the user. When used as a local memory, the addresses are programmable, allowing "RAMless" systems to be

Many features that have traditionally been handled by external peripheral devices have been incorporated in the design of the Z800 μP. The "on-chip peripherals" reduce system chip count by reducing system interconnection on the external bus. All members of the Z800 family contain an onchip clock oscillator. Also present is a refresh controller that provides 10-bit refresh addresses for dynamic memories.

The Z8208 and Z8216 contain additional on-chip peripherals to provide system design flexibility. To support high-bandwidth data transmission, four Direct Memory

Access (DMA) channels are incorporated on-chip. Each DMA channel operates using full 24-bit source and destination addresses with a 16-bit count. The channels can be programmed to operate in single transaction, burst, or continuous mode. System event counting and timing requirements are met with the help of the four 16-bit counter/timers (available as internal timers on the Z8108 and Z8116). The counter/timer functions can be externally controlled with gate and trigger inputs, and can be programmed as retriggerable or non-retriggerable. Also, a full duplex UART, capable of handling a variety of data and character formats is present to facilitate asynchronous serial communication.

Regardless of whether the 8-bit or the 16-bit bus is used, all members of the Z800 family feature programmable bus timing in which the user can specify timing that is tailored to individual systems. Upon reset the Z800 µPs can be programmed to have system timing that is one-fourth, one-half, or equal to the speed of the CPU, with one-half being the default. In addition to clock scaling, programmable Wait states can be inserted during various bus transactions. Without the use of external hardware, zero to three Wait

states can be inserted into Memory, I/O and Interrupt Acknowledge transactions. Furthermore, separate memory Wait states can be specified for upper and lower memory, enabling different speeds of ROMs and RAMs to be used in the same system.

A feature of the 16-bit Z8116/Z8216 bus interface is the ability to support "nibble-mode" Dynamic RAMs. Using this feature (known as burst mode), the bus bandwidth of memory read transactions is essentially doubled. Burst mode transactions have the further benefit of allowing the cache to operate more efficiently by guaranteeing a higher probability of the accessed memory to be present in the cache.

The Z800 family supports Zilog's Extended Processor Architecture in a number of ways. All members are capable of trapping External Processor Unit (EPU) instructions in order to perform software emulation of the EPU. The Z8216 directly interfaces with an EPU such as the Z8070 Floating Point Unit and operates in a manner that is completely transparent to the user and the program. The other members of the Z800 family can easily interface with EPUs with the aid of support software.

Write 235

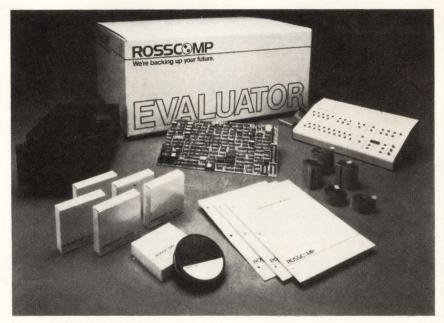

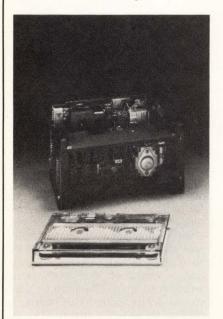

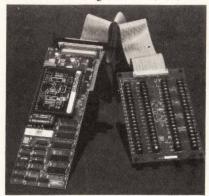

## **Evaluators Speed Tape Drive Integration**

Designed to ease integration of the company's 24 track, 160 Mbyte ½" tape streamer into computer based systems, Rosscomp's (Cerritos, CA) E Series Evaluators allow file and restore operations at 90 or 130 in/sec. The evaluators are used with low speed Q2000/SA1000 interfaces or the higher speed SMD interface. Each evaluation package includes a Rosscomp D160 tape drive, and exerciser plus cables and connectors. The exerciser is used to write data in forward and reverse directions.

step the head, and analyze signals and windows using an oscilloscope. An intelligent controller is included that supports both on- and off-line data transfers between disk drives and the streamer. Five versions of the Evaluator are offered.

Model E160 is based on a D160 90 in/sec drive and a Rosscomp C160 single-board tape/disk controller. The C160 controller interfaces a Rosscomp drive to up to four Q2000/SA1000-compatible Winchesters, and to a host pro-

cessor with a SASI bus. The E160 will support data transfer rates up to 8 MHz across the host interface.

The evaluator permits direct communication between the peripheral subsystem and the host processor and operates off-line for file backup and restore evaluations between the tape and disk drives. This evaluator can be used in the drive's split-drive mode with the 24-track format logically divided into drives of two, four, eight or twelve tracks, thus reduc-

## "We've got what makes the difference in Local Area Networking..."

The ACC Exchange System (ACCES) is a product umbrella that incorporates a comprehensive approach for truly distributed networks.

ACC Knows Networking. For over a decade, ACC personnel have set the pace in network product development. Beginning with the ARPANET, ACC has designed and developed a broad range of high performance network access equipment for packet switched and local area networks.

It is this experience that makes the difference in our approach.

Everyone agrees that Local Area Networking is good. But no one seems to agree on much else. Coax versus twisted pair. Baseband versus broadband. Token ring versus random access. The list goes on and on. Our experience, however, has taught us that low level features are only a small part of a functioning network.

The ACCES Approach. Most Local Area Network products today are hardware solutions at the lowest networking levels. Before LANs can become truly useful, network users need to have higher level functions at their fingertips. The ACCES approach provides network services through the upper layers of the OSI model. By following the layered model, the ACCES product line does not rely on specific low level implementation (baseband, broadband, etc).

The ACCES Product Line. Some of the products under the ACCES umbrella:

- Intelligent Ethernet front ends (UNIBUS and VERSAbus)

- X.25/Ethernet Bridge

- IBM Channel/Ethernet interface

- · Baseband/Broadband Converter

- Xerox Network Systems (NS) communications protocol package

- LAN industry news, over your terminal and modem, dial up On-Line Information at (408) 475-7940. And it's free.

If you'd like more information on the ACCES approach and product line, call us. Today. (408) 425-0937.

ACCES is a trademark of Associated Computer Consultants.

UNIBUS is a registered trademark of Digital Equipment Corporation.

Ethernet is a registered trademark of Xerox Corporation.

Associated Computer Consultants Local Area Network Center 2901 Park Avenue Soquel, CA 95073 TWX 910 334-4907 (408) 425-0937

## **Technology Trends**

ing access time to a record to 30 seconds on the average. \$4455.

E163-90 and E163-130 versions have the same functional specifications as the E160 evaluators but also support a D160 ½" tape drive operating at either 90 or 130 in/sec respectively and two SMD Winchester disk drives. Both are \$4675.

Model E161 is designed for online analysis of file backup and restore using the D160 drive and a host processor. The system uses an intelligent controller that makes the D160 compatible with drives that use the ½" cartridge (QIC) interface.

The E161 provides an 8-bit parallel connection to the host processor, handles data separation, tape formatting, and errordetection and control. It is available in either a 90 in/sec version (the E161-90) or in a 130 in/sec version (the E161-130). Both are \$3295.

The company claims these tape drive evaluators are, like the drives themselves, unique. For example, the D160 stores its 160 Mbytes on a self loading 4" tape reel rather than the cartridges

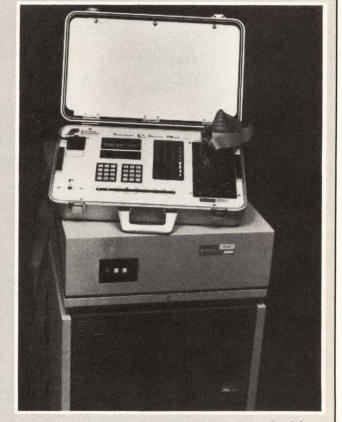

Figure 1: Rosscomp's E-Series evaluators.

used in competing drives. The reel design is said, by the company, to be more stable at high speeds and high transfer rates than cartridge based products. The current drive is packaged in an 8" Winchester form factor. A new drive using the same 4" reel is in development with the same 90

or 130 in/sec speeds and capacity as the D160, yet packaged in a 5 1/4" form factor. Interfaces being explored include: SASI/SCSI, QIC, STS06, ESDI, Q2000/SA1000, SMD and the 9-track Pertec type. Quantity pricing is expected to be approximately \$300. Write 231

## 3.5" Winchester Uses Plated Media, Thin Film Heads

The Control Data Corp. (Minneapolis, MN) Cricket hard disk drive boasts an unformatted capacity of 6.38 Mbytes on a single 3.5" disk. This high storage capacity is due primarily to the use of plated media and IBM 3380 type thin film. Both heads and media are nickel-cobalt plated. Recording densities are 15,390 bits/in and 450 tracks/in.

The thin film technology is shared by four other drives that were announced by the company at the same time. They include: two half-height 5.25" floppy disk drives; an 80-Mbyte model in the "Wren" 5.25" Winchester family; two 9" Fixed Storage Drives that hold up to 516 Mbytes of data; and an 825-Mbyte, 14"

Winchester.

Because of LSI technology, including two custom chips for servo and read chain control, drive electronics are contained on a PCB that is roughly a third the size of boards used in 5.25'' Winchester drives. The result is a drive with the Sony form factor measuring  $1.63'' \times 4'' \times 6.37''$ . It is the same height as a half height 5.25'' Winnie.

The Cricket is timing and format compatible with the ST506 interface with a 5 Mbits/sec transfer rate. Average seek time is 117 msecs using a band stepper positioning method. The microprocessor controlled, closed loop digital servo system uses information that is written on a servo surface

The CDC 9290-6 Cricket.

embedded at the beginning of each track. \$465. Initial evaluation units will be available in the third quarter of 1983. Write 232

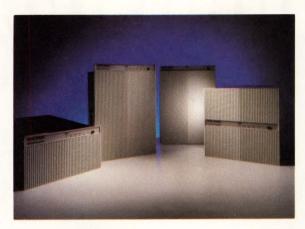

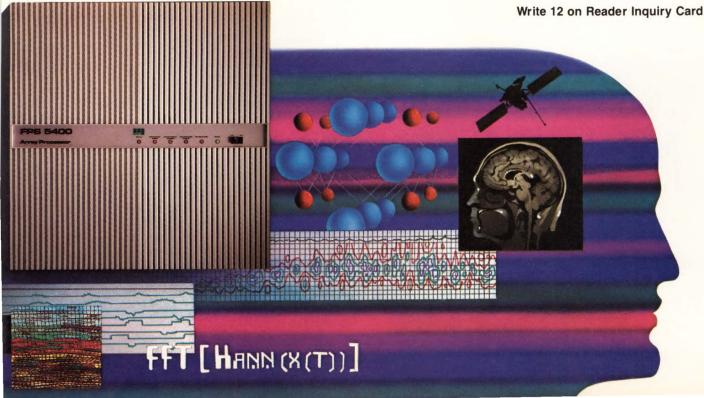

Introducing the first array processor to break the \$2,000/MFLOP barrier.

## The FPS-5000 Series from

Now, a new family of products from Floating Point Systems brings increased computing power and unmatched price/performance to the signal/image processing world.

With 3 to 6 times the speed and 4 times the memory capacity of previous FPS products, the FPS-5000 Series provides computing for applications that exceed their present system's capability.

The FPS-5000 Series offers fast, accurate, flexible computing for the most demanding real-time, user-interactive, and production-oriented applications.

Four basic product groups make up the new FPS-5000 Series: the 5100, 5200, 5300 and 5400. Peak performances range from 26 million floating-point operations per second (MFLOP), to 62 MFLOP. Data memory of 0.5M to 1M words are available along with program memory to 32K words.

By combining a distributed architecture concept with the latest VLSI technology, the FPS-5000 Series sets a new standard for cost-effective computing, breaking the \$2,000 per MFLOP\*

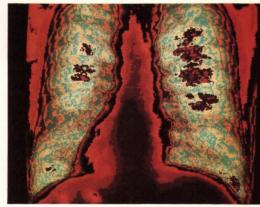

Typical performance examples of geophysical, medical imaging and signal/image processing applications.

| Application Example |                                                                          | AP-120B    | FPS-5410  | 5420      | 5430      |

|---------------------|--------------------------------------------------------------------------|------------|-----------|-----------|-----------|

| 1.                  | Demodulation/Signal<br>Analysis                                          | 13.8 msec. | 6.5 msec. | N/A       | N/A       |

| 2.                  | Tomography Preprocessing                                                 | 60 sec.    | 25.0 sec. | 16 sec.   | 12 sec.   |

| 3.                  | Multispectral Image Classification (512 x 512 pixels 8 Bands, 4 classes) | 49 sec.    | 25 sec.   | 13.3 sec. | 10.5 sec. |

| 4.                  | 2D FFT<br>(512 x 512 complex)                                            | 3.4 sec.   | 1.4 sec.  | .7 sec.   | .5 sec.   |

|                     | Matrix Multiply<br>(100 x 100)                                           | 439 msec.  | 177 msec. | 96 msec.  | 71 msec   |

| Вс                  | ased upon specifications subject to change.                              |            |           |           |           |

barrier—the first time this has been achieved in any floatingpoint computing system.

\*Based on U.S. Domestic Prices

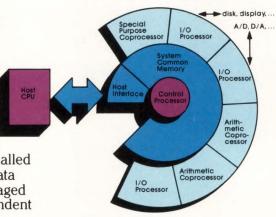

## Distributed processing architecture

The FPS-5000 Series is a distributed processing system that maximizes throughput by allocating the computational load to a set of high-performance, independent, floating-point processing elements called Arithmetic Coprocessors. Data flow is simultaneously managed by a combination of independent

I/O Processors and the central Control Processor.

## FPS-5000 Series Architecture

## Floating Point Systems.

**Each Arithmetic** Coprocessor, with synchronous architecture to allow simple application debugging, functions as a selfcontained unit.

The new Multiple Array Processor Execution Language (MAXL), based upon FORTRAN 77, allows the user to construct an integrated system environment which can be tuned to application requirements.

Increased performance can be achieved by adding Arithmetic Coprocessors as a field-installable upgrade as the user's requirements evolve.

## Compatibility

The FPS-5000 Series maintains software compatibility with previous FPS 38-bit processors and is supported on a range of host computers. Thus, the extensive software support developed for FPS-100 and AP-120B products is maintained and users are able to move existing applications onto

the FPS-5000 Series with minimal effort.

## **Quality and Reliability**

The FPS-5000 Series was designed and built with the same quality standards inherent in all of the previous Floating Point Systems products—standards that have earned those products a reputation for unprecedented reliability and one of the best meantime between failure (MTBF) rates in the industry.

The Series is backed by the same outstanding worldwide support services that distinguish

Floating Point Systems from other manufacturers.

For more information about how the FPS-5000 can be used in your specific application, call (800) 547-1445 or your local sales office.

The world leader in array processors.

P.O. Box 23489 Portland, OR 97223 (503) 641-3151 TLX: 360470 FLOATPOIN BEAV

FPS Sales and Service Worldwide.

U.S.: CA - Laguna Hills, Los Angeles, Mountain View.

CO - Lakewood. CT - Simsbury, FL - Winter Park.

GA - Atlanta. IL - Schaumburg. LA - New Orleans.

MD - Rockville. MA - Dedham. NJ - Red Bank.

NM - Cornales. PA - Philadelphia. TX - Grand Prairie,

Houston. WA - Bellevue.

INTERNATIONAL: Canada, Calgary, Montreal, Ottawa;

England, Bracknell, Berkshire; France, Runglis, Japan,

Tokyo; Netherlands, Gouda; West Germany, Haar.

DISTRIBUTORS: Australia and New Zealand, Milsons Point-N.S.W., Melbourne-Victoria (Techway Pty., Ltd.); Austria, Vienna (Elektronische Bauelemente Und Geräte); Finland, Helsinki (OY Emmeth AB); India, Bombay (Hinditron Computers PVT, Ltd.); Israel, Tel Aviv (Eastronics, Ltd.); Korea, Seoul (World Business Machine, Inc.); Singapore, Hong Kong, Brunei, Indonesia, and Malaysia (Scientek Engineering Co.); Southern Africa, Johannesburg (Anker Data Systems); Sweden and Norway, Vaxholm (Tre Konsulter AB); Taiwan, Talpei (Scientek Corporation).

© Floating Point Systems, Inc. 1983

## A unique combination.

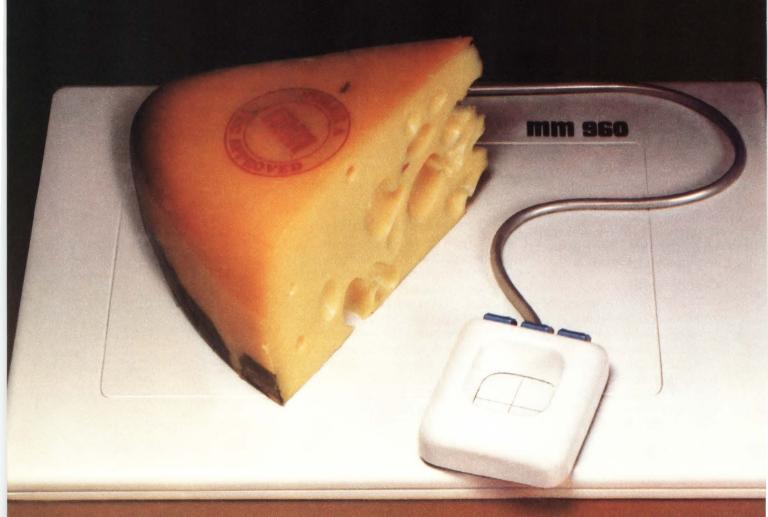

## Introducing a digitizer with a built-in mouse.

A unique combination unmatched by any digitizer on the market today, the MM™ Series can perform all your cursor steering, menu picking and graphics digitizing tasks. The MM outputs both absolute coordinate data like a digitizer and delta coordinate data like a mouse.

The MM Series was designed to offer builders of today's lower-cost terminals, graphic workstations

and personal computers Maximum performance at Minimum cost. Maximum performance because you'll get all the features you need from a high resolution, remotely-controlled digitizer plus the

versatility of a cursor steering mouse in one compact package. And Minimum cost because MM was designed, right from the start, to be inexpensive to purchase, integrate and maintain.

Advanced packaging combining light weight, small overall size, and slim profile with built-in tilt mechanism make the MM Series an ideal addition to your user-friendly system.

Every MM Series digitizer is backed by Summagraphics, the leader in digitizers, and the emerging leader in graphics input devices.

Call or write Summagraphics Corporation, 35 Brentwood Avenue, P.O. Box 781, Fairfield, CT 06430. Telephone (203) 384-1344. Telex 96-4348.

MM digitizers are available with either cursor or pen-like stylus.

Write 13 on Reader Inquiry Card

## Disk Drive Market Holds Course

With the rising popularity of "Winchester" fixed media drives, many disk manufacturers were uncertain as to the effect, if any, it would have on cartridge disk drive sales. In a recently released analysis, Venture Development Corp. (Wellesley, MA) found that 5.25", 8", and 14" cartridge disk drive sales will grow approximately five percent annually over the next five years, starting from 1982 sales of \$1.2 billion. The fixed media, cartridge disk, and disk pack market will grow from \$7.0 billion in 1981 to a predicted \$17.8 billion in 1986.

The disk drive industry is rapidly growing because of three important factors: 1) escalating requirements for additional storage space; 2) the increasing reliability of hard disk technology; and 3) the appearance of new types of computer systems utilizing hard disk technology.

The growth of cartridge disk drive sales is contigent upon a host of variables including the development of the sub-8" drive market, product standardization, plated media, and greater than 10 Mbyte 1/4" tape drives.

Plated media's success may largely determine the future of cartridge disk drives. Previously, this media has principally been used in fixed media drives. International Memories Inc., who purchases the plated media from Ampex and PolyDisk and incorporates it into a drive, has been a pioneer in selling plated media. This year they secured a \$10 million contract with Data General for their H series 5.25" drive with shipments beginning in 1983. 1983 will also be the first year that both Syquest and Disctron will be selling their plated media cartridge disk drives.

Quarter-inch cartridge tape drives are viable competitors within the removable media marketplace as well.

## Graphics Terminal Vendors Making Shift to CAD

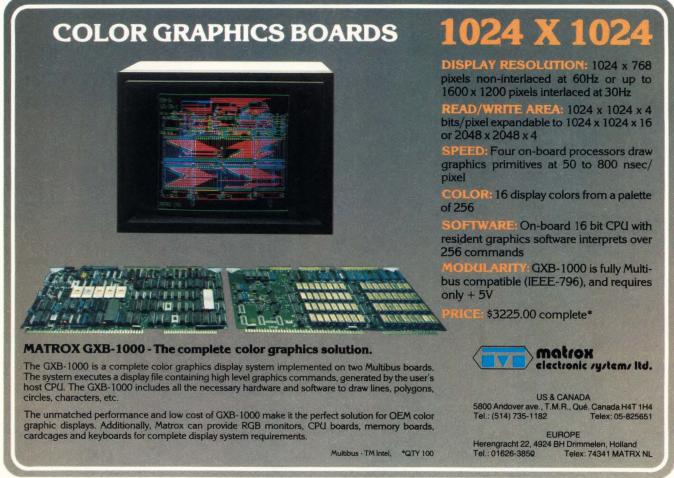

Several prominent graphics terminal manufacturers made announcements at the recent NCGA show in Chicago that indicates the continuing maturation of the vendors participating in graphics marketplace. Notable among them were Intecolor Company (Norcross, GA) and DataType (Mountain View, CA). Intecolor, part of the Intelligent Systems Corporation's growing number of firms discussed a 1024 × 1024 color monitor, which may have applications in future CAD products. Intecolor may soon launch a very substantial entry into low cost, high resolution CAD systems.

DataType which announced further advances in its graphics terminals showed a product incorporating a Motorola 68000, allowing standalone or independent graphics operations. Of interest is that both of these were for years known primarily as suppliers of ASCII based graphics systems or in the case of DataType for retrofitting other manufacturers' products. As the cost of powerful processors decreases both of the companies are moving enhanced graphics into markets that they have exploited well for lower resolution products.

-Borrell

## New Resource For Software Buyers

A new concept in cataloguing software was recently introduced by PC Telemart Inc. (Fairfax, VA). Over 1,000 pieces of software have been donated or loaned to the PC National Software Reference Library by distributors, publishers, hardware retailers and manufacturers.

The library, which is non-lending and requires a membership, was conceived as a resource for potential buyers who want to test a variety of software before purchase. The facility allows for individual testing and selection and is staffed by a thirty-person technical staff.

For members who cannot come to the facility in person, a network called "Telemart" has been devised. Information is obtained in "kiosks" which are leased by stores nationwide. The kiosks are outfitted with a terminal and printer accessing users to information on 30,000 software packages, their applications, manufacturers,

as well as technical analysis and critical reviews. To access information the user goes to a kiosk which can be found anywhere from a 7–11 to a bookstore, or calls the leased property for a nominal connect charge. There are thirty pilot stores in Washington and ninety more in New York, Boston, Los Angeles, San Francisco, Denver, Chicago and Dallas.

The library will rely on consultants to teach seminars and write reviews on software and is designed with a main reference room and a theater for classes and films. It sponsors seminars and training courses for the novice to the advanced micro-technician. Membership is on a quarterly or annual basis. An initial charter subscription is \$300, quarterly rate \$100, and daily fee \$25. For more information contact: PC Telemart, 11781 Lee-Jackson Highway, Fairfax, VA 22033 (703) 352-0721. -Coville

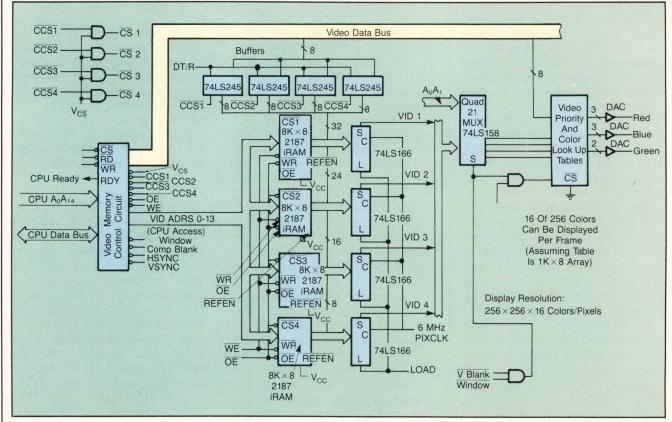

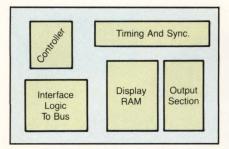

## Color Graphics Display Uses 8K×8 iRAMs

Unlike the pseudostatic or quasistatic RAM devices which only incorporate a portion of the refresh circuitry onto the memory chip and still require much control from the CPU, an iRAM integrates all the components of a dynamic RAM system into a single device. The integration used in the iRAM includes the refresh timer, refresh address control and counter, address multiplexing, and memory cycle arbitration as well as an 8-bit wide memory array.

The design that follows shows the 2186/2187 iRAM in a specific application: a color graphics display memory.

In this example (**Figure 1**), the color display resolution is 65,536 ( $256 \times 256$  pixels)  $\times 4$  bits. The four bits select the color of the pixel by addressing a color lookup and video priority table. This programmable table permits up to 16 colors (out of 256 possible) per

display frame. It also assigns priority. For example, a red disk crosses a green on the display. Does the red cross in front of the green disk, the green in front of the red, or does the area of the overlap become yellow? The priority encoding assigns answers to these questions.

By industry standards, this 256×256 pixel display has lowend to medium display resolution. For those unfamiliar with the capabilities at this level, visit a local video game parlor and examine some of the dazzling displays on the state-of-the-art video games such as Williams Electronics Defender. Advanced machines such as this are only beginning to approach this display density.

The iRAM used in this example is the synchronous 2187. Due to the sequential addressing scheme of video displays, video memory typically requires no additional

circuitry for refresh. The 2187 is no exception, and in this design the REFEN pin is tied high. The sequential scanning by the video address generator automatically refreshes the internal array of the iRAM.

CPU addresses A<sub>14</sub> and A<sub>15</sub> are decoded to generate one of four iRAM chip selects so that the (assumed 8-bit) CPU can read or writer information to the individual memory planes (iRAMs). These chip selects are gated so that all four iRAMs can be simultaneously enabled by the V<sub>CS</sub> signal from the video timing circuitry. A similar circuit (not shown) would allow OE for the iRAMs to be generated by either the CPU or the video timing generator. The iRAM addresses are generated by multiplexing the CPU addresses with video timing addresses. The 32-bit output from the iRAMs is loaded into four 8-bit shift regis-

Figure 1: Using the 2187 iRAMs in a color graphics display memory.

## **Graphics System Design**

ters and are serially shifted out as four bits of video information used to address the color lookup table. The four lines (Vid<sub>1</sub>–Vid<sub>4</sub>) are multiplexed with CPU addresses A<sub>0</sub>–A<sub>3</sub> to create the actual addresses of the lookup table. Comprised of two 2148H RAMs, the eight data lines of the lookup table are directed to three digital-to-analog converters for generating 16 of 256 different display colors.

Due to the byte-wide organization of the iRAMs, there is plenty of time between video read cycles to allow CPU access to the memory. With a pixel rate of 6 MHz, the byte-wide iRAM has a video read rate of 6/8 MHz or once every 1.33 microseconds. Only 350 ns of this time is needed for a video read cycle. The balance of the time (approximately 1 µsec) can be used by the CPU to access the memory. This interleaving of CPU cycles with video timing cycles, combined with allowing the CPU unrestricted access to the memory during both horizontal and vertical blanking (retrace) periods permits the real time screen update required in an animated display. Write 233

## Attention 8K × 8 Dynamic RAM Designers. Free Samples . . .

Intel Corp. is offering free samples of either the 2186 or 2187 to design engineers who write in on company letterhead. The 2186 iRAM contains automatic internal refresh circuitry making it an ideal choice for asynchronous applications. The 2187 does not have the internal arbitration capability as it has been designed for use in synchronous applications.

You must include a brief description of your application, stating number of parts required. Send your requests to:

Free iRAM Offer/Digital Design, Bruce Christensen, Memory Components Division,

Intel Corporation, 5200 N.E. Elam Young Parkway Hillsboro, OR 97123

## Low Cost Automated Drafting— The Next Paperwork Revolution

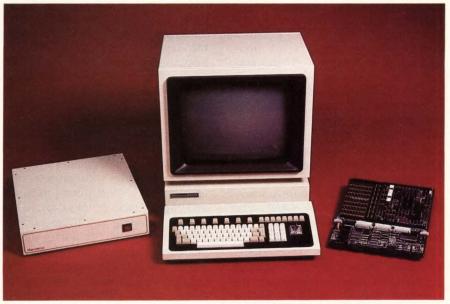

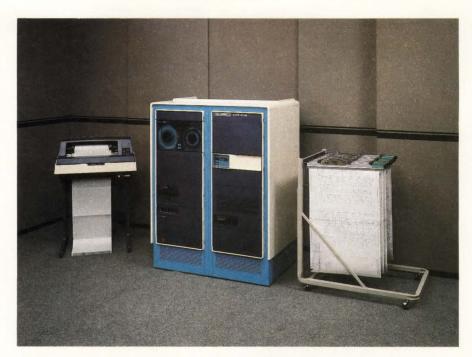

Figure 1: Andromeda's A-CADS/1 Automated Drafting System.

A new class of Computer-Aided-Drafting System (CADS) from the LSI-11 systems house, Andromeda Systems, Inc. (Canoga Park, CA) brings three dimensional CAD technology in at a \$24K price tag for a complete turnkey system. The system includes software, CPU, CRT terminal, disks, a "B" size plotter and digitizer, and approximates the salary and overhead of a "B" draftsman.

Andromeda has utilized its standard products to assemble the A-CADS/1 system. The system card cage contains a DEC LSI-11/23 CPU, 64Kbyte RAM, five serial RS232C ports, a video display controller, a floppy/Winchester controller, joystick interface, and several expansion slots. Mass storage is a 5Mbyte Winchester, and removable storage is with a

512Kbyte floppy. The I/O devices include Andromeda's VDT11-C graphic display terminal with a 512H by 256V resolution raster display. The display can emulate the Tektronix 4010 in the graphics mode and DEC's VT52 in the alphanumeric mode for text processing. A joystick is the primary input device for creating drawings. The ability of the CRT terminal to handle both graphics and text eliminates the need for a second terminal, common with many earlier CAD systems. Completing the hardware complement is a "B" size plotter that can select, under system controls, up to eight pens for varying color or line width and an 11" by 11" digitizing pad with a four button cursor.

Andromeda Systems, Inc., 9000 Eton Ave., Canoga Park, CA 91304. Write 315

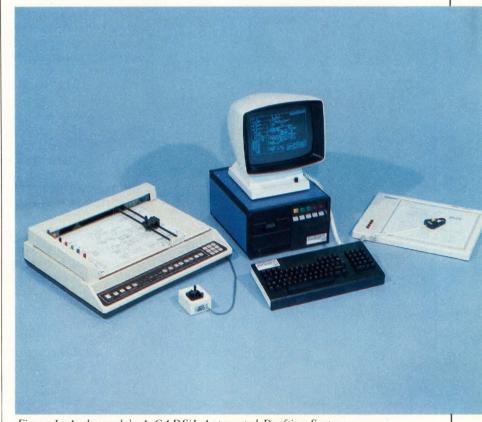

## INTRODUCING LARGE-DISK PERFORMANCE IN DRIVES HALF THE SIZE

MODEL 9715 FSD. With 160 Mbytes in a sealed module, you get the same capacity, speed and performance as the CDC" Mini Module Drive (MMD) in a unit one-half the size.