Release Date: 4-29-94

### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1994, Texas Instruments Incorporated

# TMS320 Family Development Support

# Reference Guide

Reference Guide

# TMS320 Family Development Support

1994

# TMS320 Family Development Support Reference Guide

### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

# **Preface**

# **Read This First**

### About This Manual

The TMS320 Family Development Support Reference Guide details the extensive development support available from TI for the TMS320 family of digital signal processors. As a reference manual, it provides helpful and essential information to assist you in selecting the proper TI tools for design and development of TMS320 applications.

More than 100 third-party suppliers provide development support tools and application hardware/software that supplement the TI DSP products and tools. Information on those offerings is provided in the *TMS320 Third-Party Support Reference Guide* (literature number SPRU052).

## How to Use This Manual

The chapters and appendices which make up this book provide detailed reference information on the TMS320 family of DSPs. The information is arranged in the following manner.

Chapter 1, the *Introduction*, presents an overview of the TI DSP offerings and a listing of the TMS320 digital signal processors now available.

Chapter 2, *The TMS320 Digital Signal Processor Family,* describes the TMS320 family of digital signal processors (DSPs), lists the key features of the devices, and provides a TMS320 road map of products. Also discussed in this chapter are the common DSP applications and the performance benchmarks for the TMS320 DSPs.

Chapter 3, *Code-Generation Tools*, provides an overview of software development. A discussion of software development products includes information on the TMS320C2x/C5x and TMS320C3x/C4x C compilers, the TMS320 macro assembler/linker, the Tartan Ada compiling system for the

TMS320C30 and TMS320C40, and SPOX, a DSP operating system for the TMS320C3x, TMS320C4x, and TMS320C5x.

Chapter 4, *System Integration and Debugging Tools*, gives the reader an overview of the integration and debugging process. This chapter also discusses system integration and debugging products such as the TMS320 programmer's interface (C/assembly source debugger) and the TMS320 software simulators and emulators. Chapter 4 also covers system integration and evaluation tools, TMS320C2x/5x DSP starter kits (DSKs), TMS320 XDS upgrade packages, and the parallel processing development system (PPDS) for the TMS320C40.

Chapter 5, *TMS320 Technical Support*, provides an overview of the technical literature and technical assistance. The chapter's technical literature overview covers application reports, data sheets, the TMS320 newsletter *(Details on Signal Processing)*, product bulletins, technical articles, user's guides, and textbooks. The overview of the technical assistance covers the TMS320 Hotline, FAX capabilities, and the TMS320 Bulletin Board Service (BBS). It also covers the TMS320 software cooperative, with information on how to license TI software and on the software technology available for license.

Chapter 6, *TMS320 Seminars and Workshops*, covers seminars and three-day workshops offered by the TI Technical Training Organization (TTO). The chapter discusses design assistance services offered by the TI worldwide Regional Technology Centers (RTCs) and provides a listing of RTC offices and addresses.

Chapter 7, *TMS320 University Program*, presents an overview of TMS320 code-generation, system-integration, and debugging tools available to universities. Additionally, it lists textbooks on DSP theories and applications using the TMS320 devices and discusses how to establish a DSP lab/research environment.

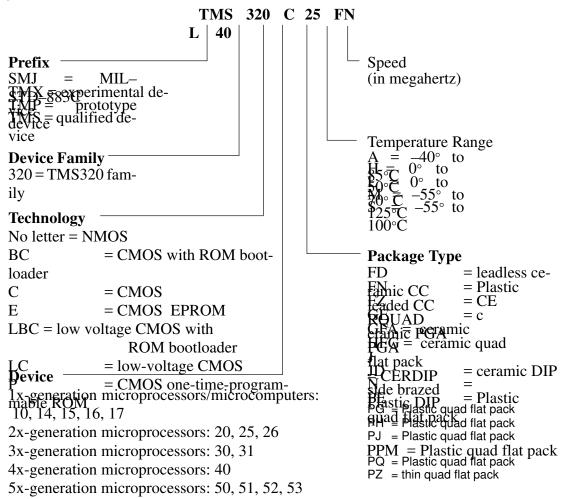

Appendix A, *TMS320 Product Information*, covers tabulated information about TMS320 devices and tools such as power dissipation, operating frequency, package type, part number, temperature range, and upgrade kits for the XDS/22 systems. This appendix also provides a detailed explanation of device nomenclature.

Appendix B covers Factory Repair and Exchange Instructions, while Appendix C presents the Program License Agreements. Appendix D discusses the ROM Codes, Appendix E covers Quality and Reliability, and Appendix F covers TMS320 EPROM Programming.

### Related Documentation

Texas Instruments provides extensive documentation to support the TMS320 family devices and development tools. The *TMS320 Third-Party Support Reference Guide* (literature number SPRU052) is a prime source of information. (See Chapter 6 of this book, *TMS320 Documentation and Technical Support* for complete lists of related materials.

# Style and Symbol Conventions

This document uses the following conventions.

Program listings, program examples, and interactive displays are shown in a special typeface similar to a typewriter's. Examples use a bold version of the special typeface for emphasis; interactive displays use a bold version of the special typeface to distinguish commands that you enter from items that the system displays (such as prompts, command output, error messages, etc.).

Here is a sample program listing:

```

0011 0005 0001 .field 1, 2

0012 0005 0003 .field 3, 4

0013 0005 0006 .field 6, 3

```

Here is an example of a system prompt and a command that you might enter:

```

c: csr -a /user/ti/simuboard/utilities

```

# **Trademarks**

IBM, OS/2, PC, PC-AT, PC-DOS, and PC-XT are trademarks of International Business Machines.

DEC, VAX, and VMS are trademarks of Digital Equipment Corp.

MAC II, MacIntosh, and MPW are trademarks of Apple Computer Corp.

MS-DOS is a trademark of Microsoft Corp.

SPOX, SPOX-DSP, and SPOX-LINK are trademarks of Spectron Microsystems, Inc.

Sun-3 and Sun-4 are trademarks of Sun Microsystems, Inc.

TI is a trademark of Texas Instruments Incorporated.

UNIX is a registered trademark of Unix Systems Laboratories, Inc.

# If You Need Assistance. . .

| If you want to                                                                                  | Do this                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Request more information about<br>Texas Instruments Digital Signal<br>Processing (DSP) products | Write to: Texas Instruments Incorporated Market Communications Manager, MS 736 P.O. Box 1443 Houston, Texas 77251–1443                                                                |

| Order Texas Instruments documentation                                                           | Call the TI Literature Response Center: (800) 477–8924                                                                                                                                |

| Ask questions about product operation or report suspected problems                              | Call the DSP Hotline:<br>(713) 274–2320<br>(Monday–Friday, 8:00 AM – 5:00 PM CST)                                                                                                     |

| Contact DSP hotline via facsimile                                                               | Call the DSP hotline FAX: <b>(713) 274–2324</b> (24 hours)                                                                                                                            |

| Contact DSP hotline via electronic mail:                                                        | 4389750@mcimail.com                                                                                                                                                                   |

| Request code or application support                                                             | Call the DSP BBS: (713) 274–2323 (24 hours) or by anonymous ftp on the following Internet sites: evans.ee.adfa.oz.au (directory /mirrors/tibbs) ti.com (directory /mirrors/tms320bbs) |

| Request pricing and availability information on products                                        | Call the local sales office:<br>See list of offices in Section 7.3                                                                                                                    |

| Report mistakes in this document or any other TI documentation                                  | Send your comments to: Texas Instruments Incorporated Technical Publications Manager, MS 702 P.O. Box 1443 Houston, Texas 77251–1443                                                  |

# **Contents**

| 1 |       | duction                                         |      |

|---|-------|-------------------------------------------------|------|

|   | 1.1   | TI DSP Overview                                 |      |

|   | 1.2   | TMS320 Digital Signal Processors                |      |

|   | 1.3   | TMS320 Development Support Products             | 1-8  |

| 2 | The 1 | TMS320 Digital Signal Processor Family          | 2-1  |

|   | 2.1   | TMS320 Family Overview                          |      |

|   | 2.2   | TMS320C1x Devices                               | 2-8  |

|   | 2.3   | TMS320C2x Devices                               | 2-16 |

|   | 2.4   | TMS320C3x Devices                               | 2-22 |

|   | 2.5   | TMS320C4x Devices                               | 2-27 |

|   | 2.6   | TMS320C5x Devices                               | 2-30 |

|   | 2.7   | Application-Specific DSPs                       | 2-36 |

|   |       | 2.7.1 TMS320SS16                                | 2-36 |

|   |       | 2.7.2 TMS320SA32                                | 2-37 |

|   | 2.8   | Customizable DSPs (cDSPs)                       | 2-38 |

|   | 2.9   | Typical Applications and Performance Benchmarks | 2-39 |

| 3 | Code  | e-Generation Tools                              | 3-1  |

|   | 3.1   | TMS320 Optimizing ANSI C Compilers              |      |

|   |       | 3.1.1 Floating-Point Compiler                   |      |

|   |       | 3.1.2 Fixed-Point Compiler                      |      |

|   |       | 3.1.3 Features of TMS320 ANSI C Compilers       |      |

|   |       | 3.1.4 TMS320 ANSI C Compiler Optimizations      |      |

|   | 3.2   | TMS320 ANSI C Compiler-Supported Hosts          |      |

|   | 3.3   | TMS320 Macro Assembler, Linker, and Archiver    | 3-25 |

|   | 3.4   | Tartan Ada Compilers                            | 3-27 |

|   | 3.5   | Tartan C++ Compiler                             | 3-29 |

|   | 3.6   | SPOX—TMS320 DSP Operating System                | 3-31 |

|   |       | 3.6.1 SPOX Software Components                  |      |

|   |       | 3.6.2 SPOX Enhancements for the TMS320C4x       |      |

|   |       | 3.6.3 Host Development Software Packages        | 3-32 |

|   |       | 3.6.4 SPOX DBUG                                 |      |

| 4 | Syste | em Integration and Debugging Tools                         | 4-1  |

|---|-------|------------------------------------------------------------|------|

|   | 4.1   | TMS320 Programmer's Interface (C/Assembly Source Debugger) | 4-2  |

|   |       | 4.1.1 Debugger Features                                    | 4-3  |

|   |       | 4.1.2 Code Profiler                                        | 4-4  |

|   | 4.2   | TMS320 Software Simulators                                 | 4-6  |

|   |       | 4.2.1 Simulator Features                                   | 4-6  |

|   |       | 4.2.2 TMS320C1x Simulator                                  | 4-7  |

|   |       | 4.2.3 TMS320C2x Simulator                                  | 4-7  |

|   |       | 4.2.4 TMS320C3x Simulator                                  | 4-9  |

|   |       | 4.2.5 TMS320C4x Simulator                                  | 4-10 |

|   |       | 4.2.6 TMS320C5x Simulator                                  | 4-12 |

|   | 4.3   | System Debugging and Evaluation Tools                      | 4-13 |

|   |       | 4.3.1 DSP Starter Kit (DSK)                                | 4-13 |

|   |       | 4.3.2 Evaluation Modules                                   | 4-14 |

|   |       | 4.3.3 TMS320C4x Parallel Processing Development System     | 4-18 |

|   |       | 4.3.4 Behavioral Models                                    | 4-21 |

|   | 4.4   | TMS320 Emulators                                           | 4-22 |

| 5 |       | 4.4.1 Scan-Based Emulators                                 | 4-22 |

|   |       | 4.4.2 XDS/22 Emulators                                     | 4-25 |

|   | 4.5   | TMS320 XDS/22 Upgrade Packages                             | 4-34 |

| 5 | TMS3  | 320 Technical Support                                      | 5-1  |

|   | 5.1   | Technical Documentation                                    |      |

|   | 5.2   | DSP Applications Books                                     | 5-3  |

|   | 5.3   | TMS320 DSP Designer's Notebooks                            |      |

|   | 5.4   | University Textbooks                                       |      |

|   | 5.5   | Technical Articles Bibliography                            |      |

|   | 5.6   | TMS320 Newsletter, Details on Signal Processing            |      |

|   | 5.7   | TMS320 DSP Bulletin Board Service                          | 5-19 |

|   | 5.8   | TMS320 DSP Technical Hotline                               | 5-21 |

|   | 5.9   | TMS320 Software Cooperative                                | 5-22 |

|   | 5.10  | Algorithm Software Sources                                 | 5-34 |

| 6 | TMS3  | 320 Seminars and Workshops                                 | 6-1  |

|   | 6.1   | Technical Training Organization (TTO) Services             |      |

|   |       | 6.1.1 TMS320C2x Design Workshop                            |      |

|   |       | 6.1.2 TMS320C3x Design Workshop                            |      |

|   |       | 6.1.3 TMS320C4x Design Workshop                            |      |

|   |       | 6.1.4 TMS320C5x Design Workshop                            |      |

|   |       | 6.1.5 Digital Control Design Workshop                      |      |

|   |       | 6.1.6 Applications in C Design Workshop                    |      |

|   |       | 6.1.7 Registration                                         |      |

|   | 6.2   | Design Services                                            |      |

|   | 6.3   | RTC Locations                                              |      |

| 7 | TMS:  | 320 University Program                                 | 7-1              |

|---|-------|--------------------------------------------------------|------------------|

|   | 7.1   | Development Tools Available to Universities            | 7-2              |

|   | 7.2   | DSP Lab Workstation Recommendations                    | 7-3              |

|   | 7.3   | DSP Research Workstation                               | 7-5              |

| Α | TMS   | 320 Product Information                                |                  |

|   | A.1   | DSP Device and Tool Part Numbers                       | A-2              |

|   | A.2   | Device and Development Support Tool Prefix Designators | ۹-13             |

|   | A.3   | Device Nomenclature                                    | <del>\</del> -14 |

| В | Facto | ory Repair and Exchange Instructions                   | B-1              |

|   | B.1   | Normal Warranty Exchange or Repair                     | B-2              |

|   | B.2   | Nonwarranty Exchange or Repair                         | B-2              |

|   | B.3   | System Updates                                         | B-2              |

|   | B.4   | Shipping Instructions                                  |                  |

|   | B.5   | Charges and Method of Payment                          | B-4              |

| С | Prog  | ram License Agreement                                  | C-1              |

|   | Prog  | ram License Agreement                                  | C-2              |

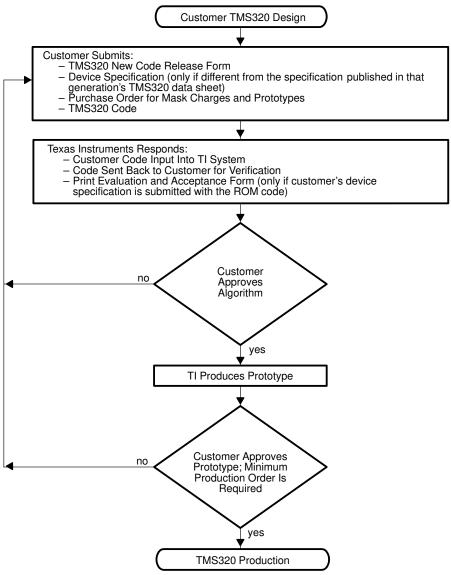

| D | ROM   | Codes                                                  | D-1              |

| Ε | Qual  | ity and Reliability                                    | E-1              |

|   | E.1   | TI's Quality Commitment                                |                  |

|   | E.2   | Reliability Stress Tests                               |                  |

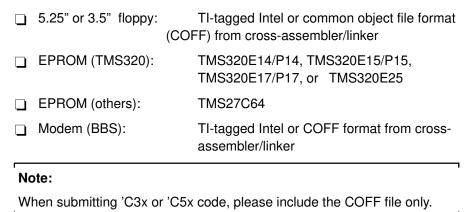

| F | TMS   | 320 EPROM Programming                                  | F-1              |

|   | F.1   | Programming                                            |                  |

|   | F.2   | Erasure                                                |                  |

|   | F.3   | Fast and SNAP! Pulse Programming                       | F-3              |

|   | F.4   | Version Verification                                   | F-3              |

|   | F.5   | EPROM Security                                         | F-4              |

# **Figures**

| 1–1        | TMS320 Family Development Support           |

|------------|---------------------------------------------|

| 1–1        | TMS320 Devices                              |

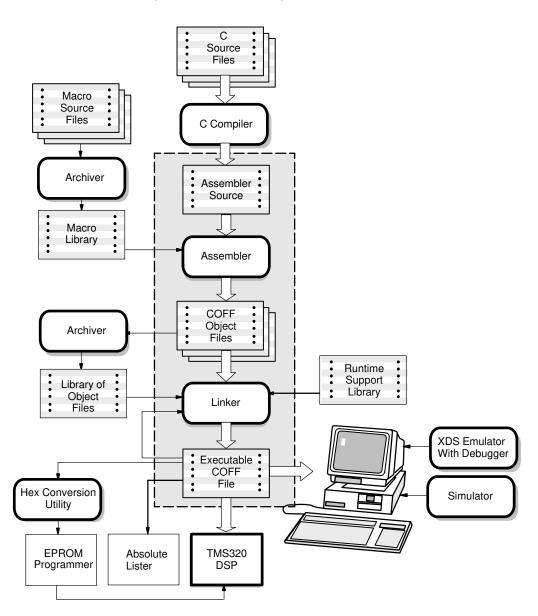

| 1–3        | Typical TMS320 Application Development Flow |

| 1–3        | TMS320 Development Product Integration      |

| 2–1        | · · · · · · · · · · · · · · · · · · ·       |

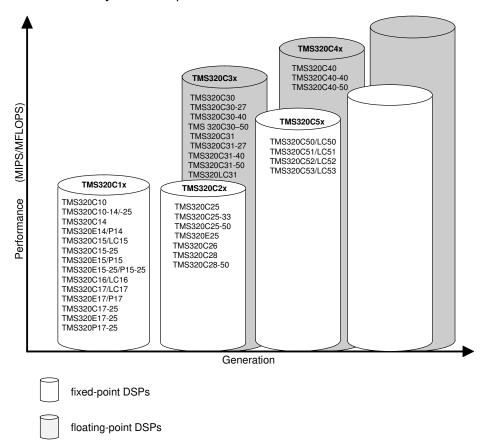

| 2–1<br>2–2 | The TMS320 Family Road Map                  |

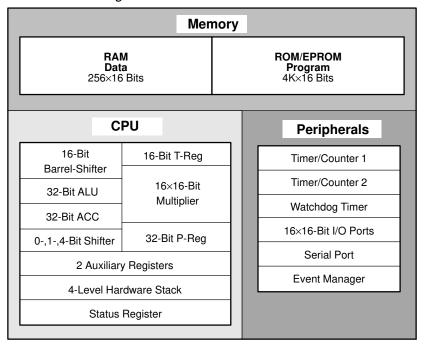

| 2–2<br>2–3 | TMS320C10 Block Diagram                     |

|            | TMS320C14 Block Diagram                     |

| 2–4        | TMS320C15 Block Diagram                     |

| 2–5        | TMS320C16 Block Diagram                     |

| 2–6        | TMS320C17 Block Diagram                     |

| 2–7        | TMS320C25/E25 Block Diagram                 |

| 2–8        | TMS320C26 Block Diagram                     |

| 2–9        | TMS320C28 Block Diagram 2-26                |

| 2–10       | TMS320C30 Block Diagram                     |

| 2–11       | TMS320C31/LC31 Block Diagram                |

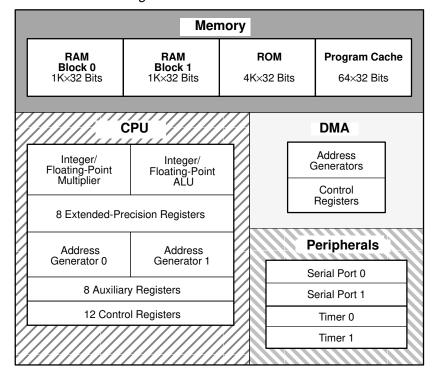

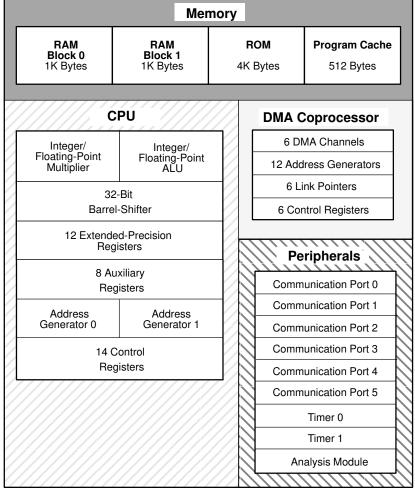

| 2–12       | TMS320C40 Block Diagram                     |

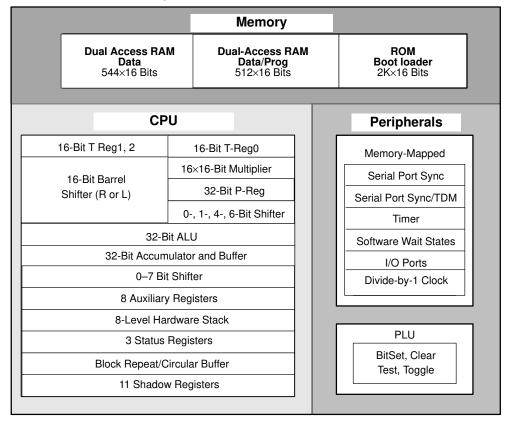

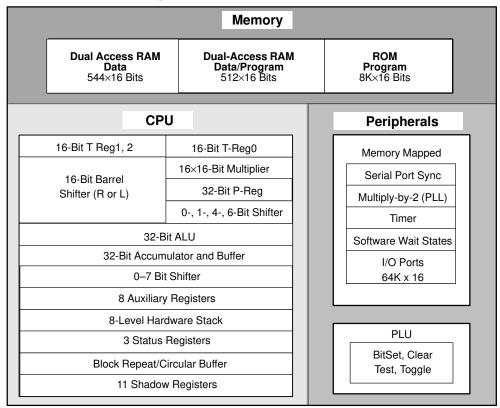

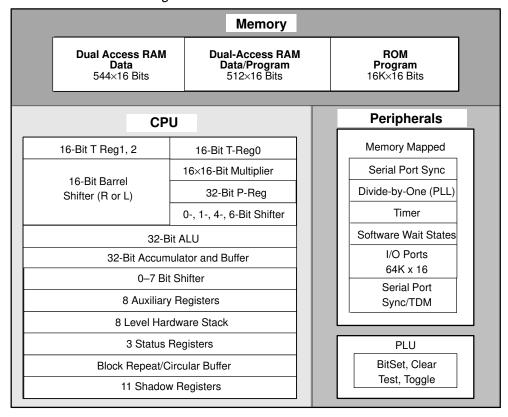

| 2–13       | TMS320C50 Block Diagram                     |

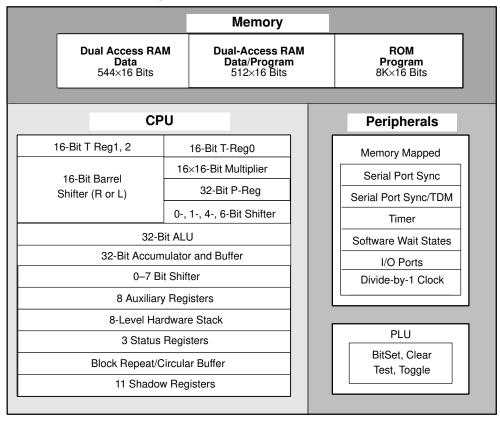

| 2–14       | TMS320C51 Block Diagram                     |

| 2–15       | TMS320C52 Block Diagram 2-39                |

| 2–16       | TMS320C53 Block Diagram 2-40                |

| 4–1        | Debugger's Customized Display 4-2           |

| 4–2        | Debugger's Data Display 4-4                 |

| 4–3        | TMS320 EVMs 4-16                            |

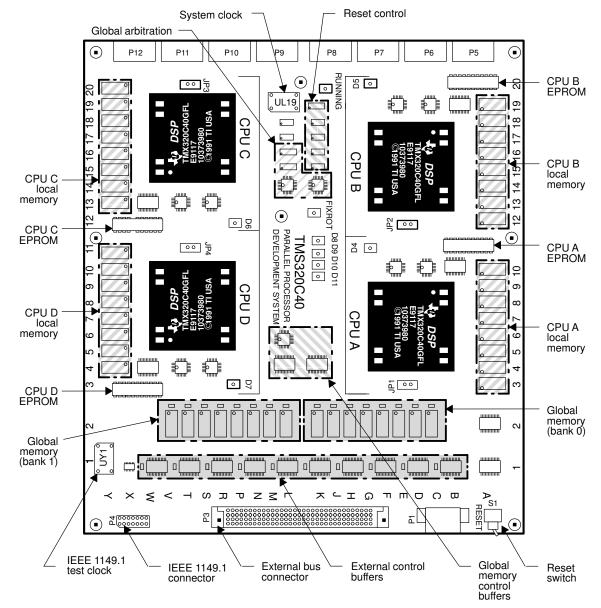

| 4–4        | The TMS320C40 PPDS Board Layout 4-19        |

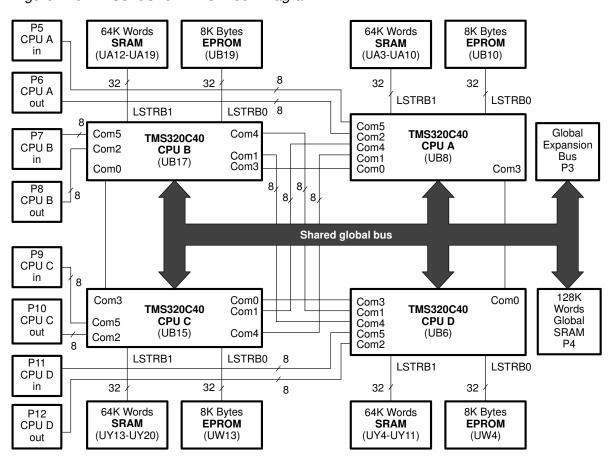

| 4–5        | TMS320C40 PPDS Block Diagram 4-20           |

| 4–6        | Behavioral Models in DSP Development 4-21   |

| 4–7        | XDS510 Scan-Based Emulators 4-25            |

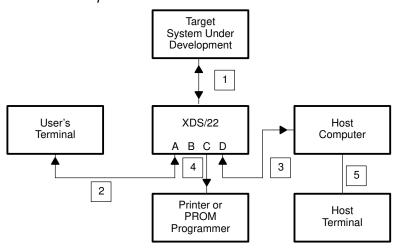

| 4–8        | TMS320 XDS/22 Host Computer Mode            |

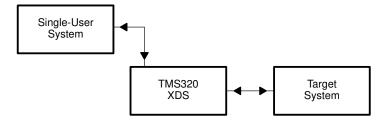

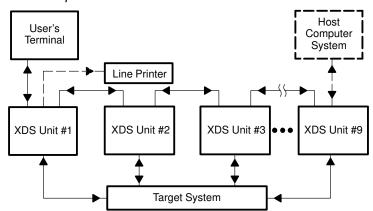

| 4–9        | TMS320 XDS/22 Single-User System            |

| 4–10       | TMS320 XDS/22 Multiprocessor Mode           |

| 4–11       | TMS320C10/C15 Emulator (XDS/22)             |

| 4–12       | TMS320C2x Emulator (XDS/22)                 |

| 4–13       | XDS Upgrade Configurations                  |

| A–1        | TMS320 Device Nomenclature                  |

| D-1        | TMS320 ROM Code Flowchart D-2               |

# **Tables**

| 1–1 | Features of TMS320 Simulation/Emulation Development Tools       | 1-11 |

|-----|-----------------------------------------------------------------|------|

| 2–1 | TMS320 Family Overview                                          |      |

| 2–2 | Typical Applications of the TMS320 Family                       | 2-39 |

| 2–3 | TMS320 DSP System Benchmarks                                    | 2-40 |

| 2–4 | TMS320 DSP Family Benchmarks                                    | 2-41 |

| 5–1 | Application Reports                                             |      |

| 5–2 | Currently Available Designer's Notebooks from Texas Instruments | 5-9  |

| 5–3 | Algorithms Available Through TI or Third Parties                | 5-23 |

| 6–1 | RTC North American Locations                                    | 6-8  |

| 6–2 | RTC International Locations                                     | 6-9  |

| A-1 | TMS320 Digital Signal Processor Commercial Part Numbers         | A-2  |

| A-2 | TMS320 Digital Signal Processor Military Part Numbers           | A-8  |

| A-3 | TMS320 Code-Generation Tools                                    |      |

| A-4 | TMS320 System Integration and Debugging Tools                   | A-10 |

| E-1 | Microprocessor and Microcontroller Tests                        | E-6  |

# **Examples**

| 3–1  | Data Flow Optimizations for Floating-Point Compilers                                                                                                                                                 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3–2  | Data Flow Optimizations for Fixed-Point Compilers                                                                                                                                                    |

| 3–3  | Copy Propagation and Control-Flow Simplification for Floating-Point Compilers 3-12                                                                                                                   |

| 3–4  | In-Line Function Expansion for Floating-Point Compilers                                                                                                                                              |

| 3–5  | In-Line Function Expansion for Fixed-Point Compilers                                                                                                                                                 |

| 3–6  | Register Variables and Register Tracking/Targeting                                                                                                                                                   |

| 3–7  | Repeat Blocks, Autoincrement Addressing Modes, Parallel Instructions, Strength Reduction, Induction Variable Elimination, Register Variables, and Loop Test Replacement for Floating-Point Compilers |

| 3–8  | Floating-Point Compiler Delayed Branch Optimizations                                                                                                                                                 |

| 3–9  | Loop Unrolling                                                                                                                                                                                       |

| 3–10 | Repeat Blocks, Autoincrement Addressing, Strength Reduction, Induction Variable Elimination, Register Variables, and Loop Test Replacement 3-20                                                      |

| 3–11 | Fixed-Point Compiler Delayed Branch, Call, and Return Instructions 3-21                                                                                                                              |

| 3–12 | Arranging Variables on the Local Frame                                                                                                                                                               |

| 3–13 | Elimination of Unnecessary LDPK Instructions                                                                                                                                                         |

# Chapter 1

# Introduction

This chapter presents an overview of the TI DSP offerings and a listing of the TMS320 digital signal processors. The listing provides a brief description of each of the five generations of TMS320 family products.

| 1.1 | TI DSP Overview                     | 1-2 |

|-----|-------------------------------------|-----|

| 1.2 | TMS320 Digital Signal Processors    | 1-4 |

| 1.3 | TMS320 Development Support Products | 1-8 |

### 1.1 TI DSP Overview

Since the first TMS320 digital signal processor (DSP) was introduced in 1982, Texas Instruments Incorporated (TI) has been dedicated to the advancement of digital signal processing technology and its applications. TI recognizes that fast time to market, increased productivity, and design ease are of primary importance in the development of DSP-based applications. Therefore, TI offers a comprehensive program of world-class development support for TMS320 DSPs that facilitates the design process from system concept to production and allows users to take advantage of rapidly evolving DSP technology.

The TMS320 support program includes leading-edge hardware and software development systems: optimizing C+ and C++ compilers, a user-friendly programming Interface consisting of C/assembly language source debuggers with code-profiling capabilities, low-cost evaluation tools, simulators, realtime emulators, realtime operating systems, and application software. More than ever, TMS320 DSP users enjoy a development environment that is comparable to the environment available for general-purpose microprocessor systems. Figure 1–1 shows the wide range of development tools available.

Various other support services are also available through the technical hotline, bulletin board service, field technical staff, and Technical Training Organization. A library of textbooks and over 2000 pages of application notes provide extensive information about the TMS320 DSP products.

Support from third-party companies complement the TI product/service offerings. Please consult the *TMS320 Third-Party Support Reference Guide* (literature number SPRU052) for details.

# 1.2 TMS320 Digital Signal Processors

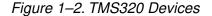

The powerful instruction sets, inherent flexibility, high-speed number-crunching capabilities, and innovative architectural designs have made the high-performance cost-effective TMS320 digital signal processor family the ideal solution for many automotive, computer, consumer, industrial, military, and telecommunication applications. The TMS320 family (see Figure 1–2) consists of five generations. Further expansion of this family is planned, creating even higher-performing more versatile spin-offs and new generations. Presently, the members (by generation) of the TMS320 family are:

### ☐ TMS320C1x Devices

- TMS320C10 a 20-MHz, fixed-point, CMOS digital signal processor

- TMS320C10-14 a 14-MHz version of the TMS320C10

- TMS320C10-25 a 25-MHz version of the TMS320C10

- TMS320C14 a version of the TMS320C15 with on-chip peripherals of a microcontroller

- TMS320E14 an EPROM version of the TMS320C14

- TMS320P14 a one-time-programmable (OTP) version of the TMS320E14

- TMS320C15 a version of the TMS320C10 with expanded ROM and RAM

- TMS320C15-25 a 25-MHz version of the TMS320C15

- TMS320E15 an EPROM version of the TMS320C15

- TMS320E15-25 an EPROM version of the TMS320C15-25

- TMS320LC15 a low-power version of the TMS320C15

- TMS320P15 a one-time-programmable (OTP) version of the TMS320E15

- TMS320P15-25 an OTP version of the TMS320E15-25

- TMS320C16 a version of the TMS320C15 with larger on-chip ROM, wider address space, and higher performance

- TMS320LC16 a low-power version of the TMS320C16

- TMS320C17 a version of the TMS320C15 with on-chip telecommunication peripherals

- TMS320C17-25 a 25-MHz version of the TMS320C17

- TMS320E17 an EPROM version of the TMS320C17

- TMS320E17-25 an EPROM version of the TMS320C17-25

- TMS320LC17 a low-power version of the TMS320C17

- TMS320P17 a OTP version of the TMS320E17

- TMS320P17-25 an OTP version of the TMS320E17-25

### ☐ TMS320C2x Devices

- TMS320C25 a 40-MHz, fixed-point CMOS DSP with twice the performance of first-generation devices

- TMS320C25-33 a 33-MHz version of the TMS320C25

- TMS320C25-50 a 50-MHz version of the TMS320C25

- TMS320E25 an EPROM version of the TMS320C25

- TMS320C26 a version of the TMS320C25 with three times the onchip RAM. An RS-232C, I/O port, and a byte-wide EPROM bootloader are also included.

- TMS320C28 a version of the TMS320C25 with expanded ROM and a power-down mode

- TMS320C28-50 a 50-MHz version of the TMS320C28

### ☐ TMS320C3x Devices

- TMS320C30 a 33-MFLOPS, (33-MHz) DSP with two memory-expansion buses, two serial ports, on-chip ROM floating-point, and CMOS

- TMS320C30-27 a low-cost, 27-MHz version of the TMS320C30

- TMS320C30-40 a 40-MHz version of the TMS320C30

- TMS320C30-50 a 50-MHz version of the TMS320C30

- TMS320C31 a low-cost, 33-MHz version of the TMS320C30 with one memory expansion bus, no on-chip ROM, one serial port, and preprogrammed ROM boot loader

- TMS320LC31 a low-power version of the TMS320C31

- TMS320C31-27 a low-cost, 27-MHz version of the TMS320C31

- TMS320C31-40 a 40-MHz verson of the TMS320C31

- TMS320C31-50 a 50-MHz verson of the TMS320C31

### ☐ TMS320C4x Devices

- TMS320C40 a high-performance, 275-MOPS, 320 Mbytes/second, 32-bit floating-point, multiport, parallel-processing, digital signal processor

- TMS320C40-40 a 40-MHz version of the TMS320C40

### ☐ TMS320C5x Devices

- TMS320C50 a fixed-point DSP capable of over twice the performance of previous TMS320 fixed-point generations. Available in instruction cycle times of 25, 35, or 50 ns with 10K-word RAM and 2K-word ROM.

- TMS320LC50 a low-power version of the TMS320C50. Available in instruction cycle times of 40 or 50 ns with 10K-word RAM and 2K-word ROM.

- TMS320C51 a low-cost, ROM-based version of the TMS320C50 with 2K-word RAM and 8K-word ROM.

- TMS320BC51 a version of the TMS320C51 with a preprogrammed ROM bootloader. Available in instruction cycle times of 25, 35, or 50 ns with 2K-word RAM and 8K-word ROM.

- TMS320LC51 a low-power version of the TMS320C51. Available in instruction cycle times of 40 or 50 ns with 2K-word RAM and 8K-word ROM.

- TMS320LBC51 a low-power version of the TMS320C51 with a preprogrammed ROM bootloader. Available in instruction cycle times of 40 or 50 ns with 2K-word RAM and 8K-word ROM.

- TMS320C52 a low-cost, high-performance ROM-based device. Available in instruction cycle times of 25, 35, or 50 ns with 1K-word RAM and 4K-word ROM.

- TMS320BC52 a version of the TMS320C52 with a preprogrammed ROM bootloader. Available in instruction cycle times of 25, 35, or 50 ns with 1K-word RAM and 4K-word ROM.

- TMS320LC52 a low-power version of the TMS320C52. Available in instruction cycle times of 40 or 50 ns with 1K-word RAM and 4K-word ROM.

- TMS320LBC52 a low-power version of the TMS320C52 with a preprogrammed ROM bootloader. Available in instruction cycle times of 40 or 50 ns with with 1K-word RAM and 4K-word ROM.

- TMS320C53 a highly integrated device with large on-chip RAM memory and ROM blocks. Available in instruction cycle times of 25, 35, or 50 ns with 4K-word RAM and 16K-word ROM.

- TMS320BC53 a version of the TMS320C53 with a preprogrammed ROM bootloader. Available in instruction cycle times of 25, 35, or 50 ns with 4K-word RAM and 16K-word ROM.

- TMS320LC53 a low-power version of the TMS320C53. Available in instruction cycle times of 40 or 50 ns with 4K-word RAM and 16K-word ROM.

- TMS320LBC53 a low-power version of the TMS320C53 with a preprogrammed ROM bootloader. Available in instruction cycle times of 40 or 50 ns with 4K-word RAM and 16K-word ROM.

- □ Application-Specific DSPs

- TMS320SS16—a single-chip, half-duplex transcoder that is pin selectable as a 64-kbps PCM passthrough device, a 32-kbps ADPCM transcoder, and a 16-kbps subband coding transcoder

- TMS320SA32—a CMOS, half-duplex, 32-kbps, ADPCM transcoder that is fully compatible with the 32-kbps ADPCM standards

Insert Photo B

# 1.3 TMS320 Development Support Products

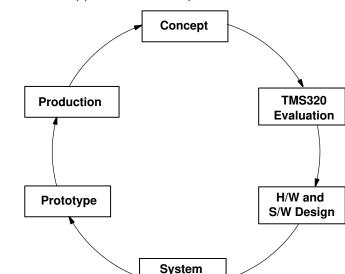

Texas Instruments supports designers in complete application development from concept through production. TI offers an extensive line of development support products to assist you in all aspects of TMS320 design and development. These products range from development and application software to complete hardware integration and debugging systems. Figure 3–1 shows a typical application flow.

Debugging

Figure 1-3. Typical TMS320 Application Development Flow

- □ Concept. The typical application development flow often begins with the concept for a new or upgraded system design. You can look at system benchmarks (available on the TI DSP bulletin board service) and review application notes and algorithms for information on a proven solution to your specific application. In addition, you can reference TI user's guides and DSP textbooks or seek assistance from the TI field technical staff and hotline. Hands-on training on TMS320 devices and development tools is also available.

- TMS320 system evaluation. Usually a TMS320 DSP device is chosen according to performance-per-dollar criteria. To help you make the best selection, TI provides extensive documentation on device specifications and capabilities. You can use a variety of support tools during this stage—including DSP starter kits (DSKs), evaluation modules (EVMs), the SPOX operating system, the assembler/linker, and C, C++ language

compilers—to evaluate the processor's performance, benchmark time-

Figure 1–4 shows development product integration. The appropriate TMS320 support product is indicated for each stage of development. Table 1–1 provides a matrix of the features of the TMS320 simulation/emulation development tools, comparing capabilities such as development purpose, software and hardware features, and amount of memory.

Figure 1-4. TMS320 Development Product Integration

Table 1-1. Features of TMS320 Simulation/Emulation Development Tools

| Features                               | EVM      | Simulator | XDS/22 | XDS510 |

|----------------------------------------|----------|-----------|--------|--------|

| TMS320 device supported:               | 'C10     | 'C1x      | 'C1x   | 'C4x   |

| ••                                     | 'C16/C1x | 'C2x      | 'C2x   | 'C5x   |

|                                        | 'C2x/C5x | 'C3x      |        | 'C3x   |

|                                        | 'C3x     | 'C4x      |        |        |

|                                        | 'C4x     | 'C5x      |        |        |

| Development purpose:                   |          |           |        |        |

| Evaluation/benchmarking                | Yes      | Yes       | Yes    | Yes    |

| Software design                        | Yes      | Yes       | Yes    | Yes    |

| Hardware design                        | No       | No        | Yes    | Yes    |

| Line-by-line or reverse assembler      | Yes      | Yes       | Yes    | Yes    |

| Modify/display memory and registers    | Yes      | Yes       | Yes    | Yes    |

| Single-stepping                        | Yes      | Yes       | Yes    | Yes    |

| Breakpoint on instruction acquisition  | Yes      | Yes       | Yes    | Yes    |

| Breakpoint on memory access/read/write | No       | Yes       | Yes    | Yes    |

| Time-stamping/clock counter            | No       | Yes       | Yes    | No     |

| Real-time trace samples                | No       | No        | Yes    | No     |

| Multiuser system                       | No       | Yes       | No     | Yes    |

| HLL user interface                     | Yes      | Yes       | Yes    | Yes    |

| Files associated with I/O ports        | No       | Yes†      | No     | No     |

| Full-speed in-circuit emulation:       |          |           |        |        |

| From on-board memory                   | Yes      | N/A       | Yes    | No     |

| From target memory                     | No       | N/A       | Yes    | Yes    |

| Amount of memory: (words)              |          |           |        |        |

| On-board program/data (TMS320C1x)      | 4K/      | N/A       | 4K     | N/A    |

| On-board program/data (TMS320C2x)      | N/A      | N/A       | 4K/4K  | N/A    |

| On-board program/data (TMS320C3x)      | 16K      | N/A       | N/A    | N/A    |

| On-board program/data (TMS320C4x)      | 384K     | N/A       | N/A    |        |

| On-board program/data (TMS320C5x)      | N/A      | N/A       | N/A    |        |

| Program/data expansion                 | N/A      | N/A       | 64K‡   | N/A§   |

<sup>†</sup>This purpose is not supported by the 'C1x simulator.

$<sup>{\ \ }^{\</sup>ddagger} \ The \ Memory \ expansion \ board \ (included \ in \ the \ TMS320C2x \ XDS/22) \ allows \ for \ memory \ expansion \ to \ 64K \ and \ the \ th$ total words of program and data memory, configurable in 1K-word blocks. § Program/data expansion is dependent upon the user's target system.

# **Chapter 2**

# The TMS320 Digital Signal Processor Family

The TMS320 family of 16-/32-bit single-chip digital signal processors combines the flexibility of a high-speed controller with the numerical capability of an array processor, offering an inexpensive alternative to custom VLSI and bit-slice processors.

This chapter discusses these TMS320 DSP devices, applications, and benchmarks.

| Topi | c Page                                               |

|------|------------------------------------------------------|

| 2.1  | TMS320 Family Overview                               |

| 2.2  | TMS320C1x Devices                                    |

| 2.3  | TMS320C2x Devices                                    |

| 2.4  | TMS320C3x Devices                                    |

| 2.5  | TMS320C4x Devices                                    |

| 2.6  | TMS320C5x Devices                                    |

| 2.7  | Application-Specific DSPs                            |

| 2.8  | Customizable DSPs (cDSPs)                            |

| 2.9  | Typical Applications and Performance Benchmarks 2-39 |

|      |                                                      |

# 2.1 TMS320 Family Overview

The combination of the TMS320's high degree of parallelism and its specialized digital signal processing (DSP) instruction set provide speed and flexibility to produce a CMOS microprocessor family that is capable of executing up to 50 MFLOPS (million floating-point operations per second) or 275 MOPS (million operations per second). The TMS320 family optimizes speed by implementing functions in hardware that other processors implement through software or microcode. This hardware-intensive approach provides the design engineer with power previously unavailable on a single chip. The newest TI generation of floating-point DSPs — TMS320C4x — is designed for high-performance, parallel-processing applications.

The TMS320 family consists of five generations (three fixed-point and two floating-point) of digital signal processors. The fixed-point devices are members of the TMS320C1x, TMS320C2x, or TMS320C5x generation, and the floating-point devices belong to the TMS320C3x or TMS320C4x generation. Figure 2–1 shows the TMS320 family. Table 2–1 provides a tabulated overview of each member's memory capacity, number of I/O ports (by type), cycle time, package type, technology, and availability.

Many features are common among these TMS320 processors. When the term TMS320 is used, it refers to all five generations of DSP devices. When referring to a specific member of the TMS320 family (e.g.,TMS320C15), the name also implies enhanced-speed in MHz (-14, -25, etc.), erasable/programmable (TMS320E15), low-power (TMS320LC15), and one-time-programmable (TMS320P15) versions. Specific features are added to each processor to provide different cost/performance alternatives. Software compatibility is maintained throughout the family to protect your investment. Each processor has code-generation, system integration, and debug tools to facilitate the design process.

Figure 2-1. The TMS320 Family Road Map

Table 2-1. TMS320 Family Overview

|                          |               |     | Memo    | Memory (Words) | s)        |        | ‡O/I   | #   |      |                  | Cycle   |                   |

|--------------------------|---------------|-----|---------|----------------|-----------|--------|--------|-----|------|------------------|---------|-------------------|

| Data<br>Tvpe             | Devicet       |     | On-Chip | d              | Off-Chip  | Cor    | 700    | VMO | m o' | On-Chip<br>Timer | Time    | Package           |

|                          |               | RAM | ROM     | EPROM          | Dat / Pro | ה<br>מ | ₹<br>L |     | 3    |                  | (ns)    |                   |

|                          | TMS320C10§    | 144 | 1.5K    | I              | 74 / –    | ı      | 8×16   | I   | ı    | I                | 200     | DIP/PLCC          |

|                          | TMS320C10-14  | 144 | 1.5K    | I              | – / 4K    | I      | 8×16   | ı   | ı    | ı                | 280     | DIP/PLCC          |

|                          | TMS320C10-258 | 144 | 1.5K    | I              | -/ 4K     | I      | 8×16   | I   | ı    | ı                | 160     | DIP/PLCC          |

|                          | TMS320C14     | 256 | 4K      | I              | – / 4K    | -      | 7×16   | ı   | I    | 4                | 160     | PLCC              |

|                          | TMS320E14§    | 256 | ı       | 4K             | -/ 4K     | -      | 7×16   | ı   | ı    | 4                | 160     | CERQUAD           |

|                          | TMS320E14-258 | 256 | ı       | 4K             | -/ 4K     | -      | 7×16   | ı   | I    | 4                | 167     | CERQUAD           |

|                          | TMS320P14     | 256 | ı       | 4K             | -/ 4K     | -      | 7×16   | I   | ı    | 4                | 160     | PLCC              |

| \ \frac{1}{2}            | TMS320C158    | 256 | 4K      | I              | – / 4K    | 1      | 8×16   | 1   | 1    | I                | 200     | DIP/PLCC/<br>PQFP |

| Point                    | TMS320C15-258 | 256 | 4K      | I              | – / 4K    | ı      | 8×16   | ı   | ı    | ı                | 160     | DIP/PLCC          |

| (16-Bit<br>Word<br>Size) | TMS320E158    | 256 | 1       | 4K             | – / 4K    | 1      | 8×16   | I   | 1    | ı                | 200     | DIP/CER-<br>QUAD  |

| (2)                      | TMS320E15-25  | 256 | -       | 4K             | ₩/-       | I      | 8×16   | 1   | 1    | I                | 160     | DIP/CER-<br>QUAD  |

|                          | TMS320LC15    | 256 | 4K      | Ι              | ¥4 / −    | I      | 8×16   | 1   | 1    | ı                | 200     | DIP/PLCC          |

|                          | TMS320P15     | 256 | I       | 4K             | – / 4K    | I      | 8×16   | ı   | ı    | ı                | 200     | DIP/PLCC          |

|                          | TMS320P15-25  | 256 | ı       | 4K             | – / 4K    | I      | 8×16   | ı   | ı    | ı                | 160     | DIP/PLCC          |

|                          | TMS320C16     | 256 | 8K      | I              | – / 64K   | I      | 8×16   | I   | ı    | ı                | 114     | PQFP              |

|                          | TMS320LC16    | 256 | У8      | _              | H9/-      | I      | 8×16   | I   | I    | 1                | 250     | PQFP              |

|                          | TMS320C17     | 256 | 4K      | I              | -/-       | 2      | 6×16   | I   | ı    | -                | 200/160 | DIP/PLCC          |

|                          | TMS320E17     | 256 | 1       | 4K             | -/-       | 2      | 6×16   | ı   | -    | 1                | 200/160 | DIP               |

† Refer to Table A-2 for TMS320 DSP military part numbers and information.

<sup>‡</sup> Ser = serial; Par = parallel; DMA = direct memory access (Int = internal; Ext = external); Com = parallel communication ports § A military version is available/planned; contact the nearest TI field sales office for availability.

Table 2-1. TMS320 Family Overview (Continued)

| Cycle                      |                     | (su)      | 200 DIP/PLCC | 160 DIP   | 100 PGA/PLCC/<br>PQFP | 120 PLCC        | 80 PGA/PLCC     | 100 PQFP/PLCC | 100 PLCC     | 100 PQFP/PLCC | 80 PQFP/PLCC |

|----------------------------|---------------------|-----------|--------------|-----------|-----------------------|-----------------|-----------------|---------------|--------------|---------------|--------------|

| Memory (Words) I/O≠¶ Cycle | On-Chip<br>Timer    |           | -            | -         | -                     | -               | -               | -             | -            | -             | 1            |

|                            | 200                 |           | 1            | 1         | ı                     | ı               | ı               | ı             | I            | I             | I            |

| <b>⊪</b> ‡0/I              | Š                   | Z<br>Z    | ı            | I         | Ext                   | Ext             | Ext             | Ext           | Ext          | Ext           | Ext          |

| )/I                        | a o o               | E<br>L    | 6×16         | 6×16      | 16×16                 | 16×16           | 16×16           | 16×16         | 16×16        | 16×16         | 16×16        |

|                            | 200                 | Sei       | 2            | 2         | -                     | -               | 1               | 1             | 1            | 1             | 1            |

| qs)                        | Off-Chip            | Dat / Pro | -/-          | -/-       | 64K /<br>64K          | 64K /<br>64K    | 64K /<br>64K    | 64K /<br>64K  | 64K /<br>64K | 64K /<br>64K  | / YF9        |

| ory (Word                  | di                  | EPROM     | _            | 4K        | 1                     | 1               | _               | У4            | _            | _             | _            |

| Memo                       | On-Chip             | ROM       | 4K           | ı         | 4K                    | 4K              | 4K              | ı             | I            | 8K            | 8K           |

|                            |                     | RAM       | 256          | 256       | 544                   | 544             | 544             | 544           | 1.5K         | 544           | 544          |

|                            | Device <sup>†</sup> |           | TMS320LC17   | TMS320P17 | TMS320C25§            | TMS320C25-33    | TMS320C25-50§   | TMS320E25     | TMS320C26§   | TMS320C28     | TMS320C28-50 |

|                            | Data                | od f.     |              |           |                       | Fixed-<br>Point | (16-Bit<br>Word | Olce)         |              |               |              |

Refer to Table A-2 for TMS320 DSP military part numbers and information.

‡ Ser = serial; Par = parallel; DMA = direct memory access (Int = internal; Ext = external); Com = parallel communication ports § A military version is available/planned; contact the nearest TI field sales office for availability.

¶ Programmed transcoders (TMS320SS16 and TMS320SA32) are also available. See Section 2.6, Application-Specific DSPs, for details.

Table 2-1. TMS320 Family Overview (Continued)

|                | Package             |              | РОFР            | PQFP/TQFP       | PQFP/TQFP       | PQFP/TQFP                | PQFP/TQFP       | PQFP/TQFP       | PQFP/TQFP       |

|----------------|---------------------|--------------|-----------------|-----------------|-----------------|--------------------------|-----------------|-----------------|-----------------|

| Cycle          | Time                | (su)         | 50/35/<br>25/20 | 50/35/<br>25/20 | 50/35/<br>25/20 | 50/35/<br>25/20∥         | 50/35/<br>25/20 | 50/35/<br>25/20 | 50/35/<br>25/20 |

|                | On-Chip<br>Timer    |              | 1               | 1               | 1               | 1                        | 1               | 1               | 1               |

|                | wo J                |              | I               | 1               | 1               | I                        | 1               | I               | 1               |

| #              | VMQ.                | ביים         | Ext             | Ext             | Ext             | Ext                      | Ext             | Ext             | Ext             |

| <b></b> \$±0/I | Dor                 | ı aı         | 64K×16#         | 64K×16#         | 64K×16#         | 64K×16#                  | 64K×16#         | 64K×16#         | 64K×16#         |

|                | 100                 | ם<br>ס       | 2               | 2               | 2               | 1                        | -               | 2               | 2               |

| ls)            | Off-Chip            | Dat / Pro    | 64K /<br>64K    | 64K /<br>64K    | 64K /<br>64K    | 64K /<br>64K             | 64K /<br>64K    | 64K /<br>64K    | 64K /<br>64K    |

| Memory (Words) | di                  | <b>EPROM</b> | 1               | I               | I               | ı                        | I               | -               | I               |

| Mem            | On-Chip             | MOH          | ВГ              | <del>%</del>    | BL              | 4K                       | BL              | 16K             | BL              |

|                |                     | RAM          | 10K             | ZK              | 2K              | <del>1</del>             | <del>두</del>    | 4K              | 4 <sub>X</sub>  |

|                | Device <sup>†</sup> |              | TMS320C50§      | TMS320C51       | TMS320BC51      | TMS320C52                | TMS320BC52      | TMS320C53       | TMS320BC53      |

|                | Data<br>Tvpe        |              |                 |                 | Fixed-          | Point<br>(16-Bit<br>Word | Size)           |                 |                 |

Refer to Table A-2 for TMS320 DSP military part numbers and information.

‡Ser = serial; Par = parallel; DMA = direct memory access concurrent with CPU operation (Int = internal; Ext = external); Com = parallel communication ports, BL = bootloader

§ A military version is available/planned; contact the nearest TI field sales office for availability.

¶ Programmed transcoders (TMS320SS16 and TMS320SA32) are also available. See Section 2.6, Application-Specific DSPs, for details. # Sixteen of these parallel I/O ports are memory-mapped.

∥ Planned

Table 2-1. TMS320 Family Overview (Concluded)

|              |              |     | Mem             | Memory (Words) | ls)             |     | <b>],±O/I</b>       | ±.      |          |                  | Cycle |                 |

|--------------|--------------|-----|-----------------|----------------|-----------------|-----|---------------------|---------|----------|------------------|-------|-----------------|

| Data<br>Type | Devicet      |     | On-Chip         | d              | Off-Chip        | 203 | Dor                 | VNG     | <u> </u> | On-Chip<br>Timer | Time  | Package<br>Type |

| -d.          |              | RAM | ROM             | EPROM          | Dat / Pro       | 201 | rai                 | Ž.      |          |                  | (su)  | 296.            |

|              | TMS320C301   | 2K  | 4K              | ı              | □W91            | 2   | 16M×32 <sup>◊</sup> | Int/Ext | Ι        | 2(6)             | 09    | PGA and PQFP    |

|              | TMS320C30-50 | 2K  | 4K              | I              | □W91            | 2   | 16M×32 <sup>◊</sup> | Int/Ext | ı        | 2(6)             | 40    | PGA and PQFP    |

|              | TMS320C30-27 | 2K  | 4K              | I              | □W91            | 7   | 16M×32 <sup>◊</sup> | Int/Ext | ı        | 2(6)             | 74    | PGA and PQFP    |

| Floating-    | TMS320C30-40 | 2K  | 4K              | 1              | □W91            | 2   | 16M×32 <sup>◊</sup> | Int/Ext | -        | 2(6)             | 9     | PGA and PQFP    |

| Point        | TMS320C30-50 | 2K  | 4K              | I              | □W91            | 7   | 16M×32 <sup>◊</sup> | Int/Ext | ı        | 2(6)             | 40    | PGA and PQFP    |

| (32-Bit      | TMS320C318   | 2K  | ₹.              | _              | □M91            | 1   | 16M×32              | Int/Ext | _        | 2(4)             | 09    | PQFP            |

| Size)        | TMS320LC31   | 2K  | ☆               | 1              | □W91            | 1   | 16M×32              | Int/Ext | _        | 2(4)             | 09    | PQFP            |

|              | TMS320C31-27 | 2K  | ₩.              | 1              | □M91            | 1   | 16M×32              | Int/Ext | _        | 2(4)             | 74    | PQFP            |

|              | TMS320C31-40 | 2K  | 女               | -              | □M91            | 1   | 16M×32              | Int/Ext | _        | 2(4)             | 20    | PQFP            |

|              | TMS320C31-50 | 2K  | 女               | -              | □M91            | 1   | 16M×32              | Int/Ext | _        | 2(4)             | 40    | PQFP            |

|              | TMS320C40    | 2K  | 4K <sup>∞</sup> | 1              | _9 <del>4</del> | _   | 4G×32 <sup>◊</sup>  | Int/Ext | 9        | 2                | 40    | PGA             |

|              | TMS320C40-40 | 2K  | 4K×             | ı              | □ <b>9</b> 4    | 1   | 4G×32 <sup>◊</sup>  | Int/Ext | 9        | 2                | 20    | PGA             |

Refer to Table A-2 for TMS320 DSP military part numbers and information.

Ser = serial; Par = parallel; DMA = direct memory access concurrent with CPU operation (Int = internal; Ext = external); Com = parallel

communication ports § A military version available/planned; contact the nearest TI field sales office for availability. ¶ Programmed transcoders (TMS320SS16 and TMS320SA32) are also available. See Section 2.6, Application-Specific DSPs, for details.

Il Includes the use of serial port timers

★ Preprogrammed ROM bootloader

□ Single logical memory space for program, data, and I/O; not including on-chip RAM, peripherals, and reserved spaces

◊ Dual buses

## 2.2 TMS320C1x Devices

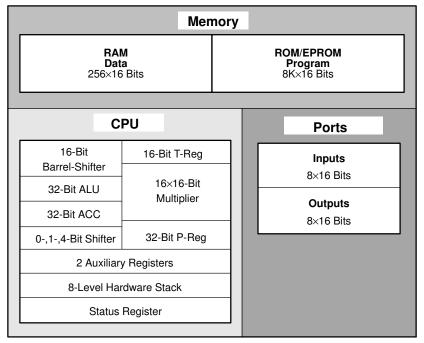

The TMS320C1x generation of the TMS320 family includes the TMS320C10, TMS320C10-14/C10-25, TMS320C14/E14/E14-25/P14, TMS320C15/E15/LC15/P15/P15-25, TMS320C15-25/E15-25, TMS320C16/LC16, and the TMS320C17/E17/LC17/P17, processed in CMOS technology. Note when referring to any member of the TMS320 family (e.g., TMS320C15) that the name also implies enhanced-speed versions as well as its associated erasable/programmable (EPROM) and one-time-programmable (OTP) products. TMS320C1x refers to all members within the TMS320C1x generation. Figure 2–2 is a block diagram of the architecture for the TMS320C10 family.

The **TMS320C10** has a 200-ns instruction cycle time, or 5 MIPS (million instructions per second) performance, and is capable of achieving a 16×16-bit multiplication within a single 200-ns cycle. The TMS320C10 is also available in a microcomputer version with 1.5K words of program ROM on-chip and up to 2.5K words of off-chip program memory for a total of 4K words. This ROM-code version can also operate entirely from off-chip ROM for ease of prototyping, code update, and field upgradeability.

The **TMS320C10-14**, a 14-MHz version of the TMS320C10, provides a low-cost alternative for DSP applications not requiring the maximum operating frequency of the TMS320C10. The device can execute 3.5 MIPS and has a 280-ns instruction cycle time.

The **TMS320C10-25**, a 25-MHz version of the TMS320C10, has a 160-ns instruction cycle time. Its low power consumption and higher speed (6.25 MIPS) make it well-suited for high-performance DSP applications.

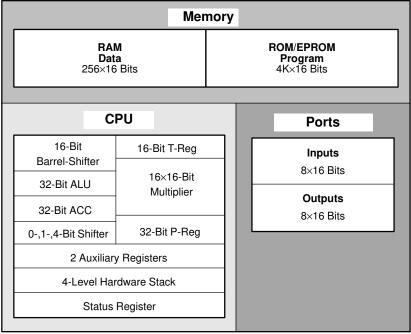

Memory ROM Program 1.5K×16 Bits RAM Data 144×16 Bits **CPU Ports** 16-Bit 16-Bit T-Reg Inputs Barrel-Shifter 8×16 Bits 16×16-Bit 32-Bit ALU Multiplier Outputs 32-Bit ACC 8×16 Bits 32-Bit P-Reg 0-,1-,4-Bit Shifter 2 Auxiliary Registers 4-Level Hardware Stack Status Register

Figure 2-2. TMS320C10 Block Diagram

The TMS320C14, TMS320E14, TMS320E14-25 and TMS320P14 are fully object-code compatible with the TMS320C10 and offer the high performance of a DSP with the on-chip peripherals of a microcontroller. The TMS320C14 incorporates 256 words of RAM, 4K words of ROM (TMS320C14) or EPROM (TMS320E14 and TMS320P14), and five major peripheral blocks optimized for control applications. These peripheral blocks include four timers/counters (two 16-bit general-purpose timer/counters, one serial port timer, and one watchdog timer), an event manager, 16-bit selectable I/O pins, and an asynchronous serial port. Figure 2–3 is a block diagram of the architecture for the TMS320C14 family.

Figure 2-3. TMS320C14 Block Diagram

The **TMS320C15**, **TMS320E15**, **TMS320LC15**, and **TMS320P15** are fully object-code and pin compatible with the TMS320C10 and offer an expanded on-chip RAM of 256 words and an on-chip program ROM (TMS320C15 and TMS320LC15) or EPROM (TMS320E15 and TMS320P15) of 4K words. The devices are processed in CMOS technology. The TMS320C15 is also available in a 160-ns version, the **TMS320C15-25** and **TMS320E15-25**. Figure 2–4 is a block diagram of the architecture for the TMS320C15 family.

Figure 2–4. TMS320C15 Block Diagram

The **TMS320C16** and **TMS320LC16** are fully object-code compatible with the TMS320C10 and each device offers an on-chip RAM of 256 words, an expanded on-chip program ROM of 8K words, and 64K words of external memory. The TMS320C16 is the highest performance member of the TMS320C1x generation, operating at a 114-ns instruction cycle time. It also features an eight-level hardware stack, as well as separate I/O write and memory write signals. The TMS320C16 is a low-cost version of the TMS320C16. Figure 2–5 is a block diagram of the architecture for the TMS320C16 family.

Figure 2-5. TMS320C16 Block Diagram

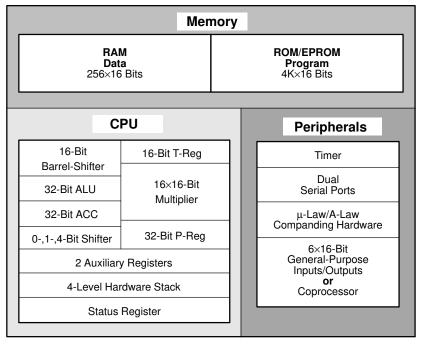

The TMS320C17, TMS320E17, TMS320LC17, and TMS320P17 are dedicated microcomputers with 256 words of on-chip RAM and 4K words of on-chip ROM (TMS320C17 and TMS320LC17) or EPROM (TMS320E17 and TMS320P17). The TMS320C17 features a dual-channel serial interface, on-chip companding hardware ( $\mu$ -law/A-law), a serial port timer, and a 16-bit latched coprocessor port for direct microprocessor/I/O interface. Figure 2–6 is a block diagram of the architecture for the TMS320C17 family.

Figure 2–6. TMS320C17 Block Diagram

Key features of the TMS320C1x generation are listed below. Specific devices that have a particular feature are enclosed in parentheses.

## □ CPU

- 114-ns single-cycle instruction execution time (TMS320C16); 8.75 MIPS

- 160-ns single-cycle instruction execution time (TMS320C14/C15-25/E14/E15-25/P15-25); 6.25 MIPS

- 200-ns single-cycle instruction execution time (TMS320C10/C15/C17/E15/E17/LC15/LC17/P15/P17); 5 MIPS

- 250-ns single-cycle instruction execution time (TMS320LC15/LC16); 4 MIPS

- 280-ns single-cycle instruction execution time (TMS320C10-14); 3.5 MIPS

- 32-bit ALU/accumulator

- 16×16-bit parallel multiplier with a 32-bit product

- 0- to 16-bit barrel shifter

## Peripherals

- Four-level hardware stack (except TMS320C16)

- Eight-level hardware stack (TMS320C16)

- 16 individual bit-selectable I/O pins (TMS320C14/E14/P14)

- Eight input and eight output channels

- Event manager with 6-channel PWM D/A converter, plus up to 6 compare outputs and up to 4 capture inputs (TMS320C14/E14/P14)

- Serial port with asynchronous mode (TMS320C14/E14/P14)

- Dual-channel serial port with timer (TMS320C17/E17/P17/LC17)

- Direct interface to combo-codecs (TMS320C17/E17/LC17/P17)

- On-chip µ-law/A-law companding hardware (TMS320C17/E17/P17/ LC17)

- 16-bit coprocessor interface (TMS320C17/E17/P17/LC17)

- Two general-purpose timers/counters (TMS320C14/E14/P14)

- Watchdog timer (TMS320C14/E14/P14)

- On-chip clock generator

## Memory

- 144-word on-chip data RAM (TMS320C10)

- 256-word on-chip data RAM (TMS320C14/C15/C16/C17)

- 1.5K-word on-chip program ROM (TMS320C10)

- 4K-word on-chip program ROM (TMS320C14/C15/C17/LC15/LC17)

- 8K-word on-chip program ROM (TMS320C16)

- 4K-word on-chip program EPROM (TMS320E14/E15/E17/P14/P15/P17)

| Memory interfaces                                                                                       |

|---------------------------------------------------------------------------------------------------------|

| ■ EPROM code protection for copyright security                                                          |

| ■ 4K-word total external memory at full speed (except TMS320C16)                                        |

| ■ 64K-word total external memory at full speed (TMS320C16)                                              |

| ■ 16-bit bidirectional data bus at 50-Mbps transfer rate                                                |

| Single 5-V <sub>DC</sub> supply                                                                         |

| Single 3-V <sub>DC</sub> supply (TMS320LC15/LC17)                                                       |

| 12.5-V <sub>DC</sub> supply additionally required for programming EPROM (TMS320E14/E15/E17/P14/P15/P17) |

| Packages                                                                                                |

| ■ 40-pin DIP (TMS320C10/C15/C17/E15/E17/LC15/LC17/P15/P17)                                              |

| ■ 44-pin PLCC (TMS320C10/C15/C17/LC15/LC17/P15/P17)                                                     |

| ■ 44-pin CERQUAD (TMS320E15/E17)                                                                        |

| ■ 68-pin PLCC (TMS320C14/P14)                                                                           |

| ■ 68-pin CERQUAD (TMS320E14)                                                                            |

| ■ 64-pin PQFP (TMS320C16)                                                                               |

| CMOS technology (TMS320C1x/E1x/LC1x/P1x)                                                                |

| Commercial and military versions available                                                              |

## 2.3 TMS320C2x Devices

The TMS320C2x generation of the TMS320 family of digital signal processors includes the TMS320C25/E25, TMS320C25-33/C25-50, TMS320C26, TMS320C28, and TMS320C28-50. The architecture of these devices is extended from that of the TMS320C10. This section briefly describes each device, lists key features, and provides a block diagram.

The TMS320C25 and TMS320E25 are capable of an instruction cycle time of 100 ns. They are pin and object-code upward-compatible with the TMS320C2. The TMS320C25's enhanced feature set includes 24 additional instructions (133 total), eight auxiliary registers, an eight-level hardware stack, 4K words of on-chip program ROM (TMS320C25) or EPROM (TMS320E25), a bit-reversed/indexed-addressing mode, and the low-power dissipation that is inherent to the CMOS process.

The **TMS320C25-33** is a 33-MHz version of the TMS320C25, capable of executing 8.25 MIPS. The TMS320C25-33 is object-code and pin compatible with the TMS320C25. It is designed for applications that require higher performance than that of the TMS320C1x devices but costs less than higher-speed TMS320C2x devices.

The **TMS320C25-50** is a 50-MHz version of the TMS320C25, capable of executing 12.5 MIPS. The TMS320C25-50 is object-code and pin compatible with the TMS320C25. Its higher speed makes it well-suited for high-performance DSP applications. Figure 2–7 is a block diagram of the architecture of the TMS320C25/E25 family.

Figure 2-7. TMS320C25/E25 Block Diagram

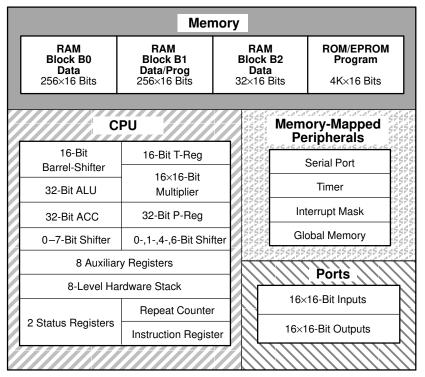

The **TMS320C26** is a TMS320C25 with three times the on-chip RAM. It has a  $1.5 \text{K} \times 16$ -bit program/data RAM and  $256 \times 16$ -bit program ROM. It is pin and object-code compatible with the TMS320C25. The on-chip RAM is composed of three  $512 \times 16$ -bit segments, which can be independently configured as program memory or data memory. An RS232C, I/O port, or byte-wide EPROM bootloader is also included when the 'C26 is operated in the microcomputer mode. Figure 2–8 is a block diagram of the architecture of the TMS320C26 family.

Figure 2-8. TMS320C26 Block Diagram

|                                             |                                             | Memory                                |                                             |                                  |

|---------------------------------------------|---------------------------------------------|---------------------------------------|---------------------------------------------|----------------------------------|

| RAM<br>Block B0<br>Prog/Data<br>512×16 Bits | RAM<br>Block B1<br>Prog/Data<br>512×16 Bits | RAM<br>Block B2<br>Data<br>32×16 Bits | RAM<br>Block B3<br>Prog/Data<br>512×16 Bits | ROM<br>Bootloader<br>256×16 Bits |

|                                             | CPU                                         |                                       | Pe                                          | ory-Mapped stripherals           |

| 16-Bit<br>Barrel-Shifte                     |                                             | 6-Bit T-Reg                           | 45454                                       | Serial Port                      |

| 32-Bit ALU                                  | 16×                                         | 16-Bit Multiplier                     | \$ 5 5 5 5<br>\$ 5 5 5 5                    | Timer                            |

| 32-Bit ACC                                  | 3                                           | 2-Bit P-Reg                           | ssss<br>ssss<br>Inte                        | errupt Mask                      |

| 0-7-Bit Shifte                              | er 0-,1-                                    | ,4-,6-Bit Shifter                     | \$5,57.5<br>\$5,45.4<br>Glo                 | bal Memory                       |

| 8                                           | Auxiliary Register                          | s                                     |                                             |                                  |

| 8-Le                                        | evel Hardware Sta                           | ack                                   |                                             | Ports                            |

| O Otataa Dawlata                            |                                             | peat Counter                          | 16×                                         | 16-Bit Inputs                    |

| 2 Status Registe                            |                                             | uction Register                       | 16×1                                        | 6-Bit Outputs                    |

|                                             |                                             |                                       |                                             |                                  |

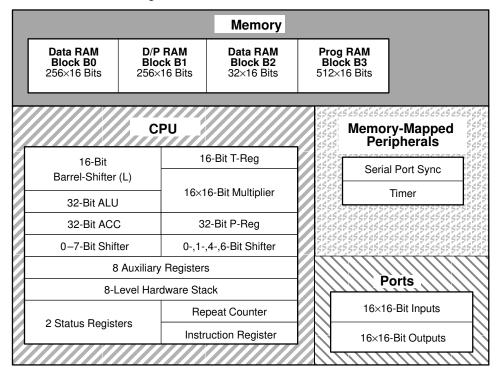

The **TMS320C28** is a TMS320C25 with 8K words of on-chip ROM and 544 words of RAM that can be configured between data and program. The off-chip memory is 64K-bit x 16-bit program and 64K-bit x 16-bit data. The 'C28 has power-down circuitry that reduces power consumption to 500  $\mu$ W. It is also both object-code compatible with all 'C2x devices and pin compatible with the TMS320C25.

The **TMS320C28-50** is a 50-MHz version of the TMS320C28 capable of executing 12.5 MIPS. Its higher speed makes it well suited for high-performance DSP applications. Figure 2–9 is a block diagram of the architecture of the TMS320C28 family.

Figure 2-9. TMS320C28 Block Diagram

| - | r features of the TMS320C2x generation are listed below. Specific devices thave a particular feature are enclosed in parentheses.                                                    |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| П | CPU                                                                                                                                                                                  |

| _ | <ul> <li>80-ns single-cycle instruction execution time (TMS320C25-50);</li> <li>12.5 MIPS</li> </ul>                                                                                 |

|   | ■ 100-ns single-cycle instruction execution time (TMS320C25/C26/E25); 10 MIPS                                                                                                        |

|   | <ul><li>■ 120-ns single-cycle instruction execution time (TMS320C25-33);</li><li>8.3 MIPS</li></ul>                                                                                  |

|   | ■ Single-cycle multiply/accumulates                                                                                                                                                  |

|   | <ul> <li>Repeats for efficient use of program space and enhanced execution</li> <li>Block moves for data/program management</li> </ul>                                               |

|   | <ul> <li>■ Indexed-addressing mode</li> <li>■ Bit-reversed indexed-addressing mode for radix-2 FFTs</li> <li>■ On this ALLI/one reproductors</li> </ul>                              |

|   | ■ 32-bit ALU/accumulator ■ Eight auxiliary registers with dedicated arithmetic unit                                                                                                  |

|   | ■ 16×16-bit parallel multiplier with a 32-bit product                                                                                                                                |

|   | <ul><li>0- to 16-bit parallel shifter</li><li>Power-down mode (TMS320C28)</li></ul>                                                                                                  |

|   | Peripherals                                                                                                                                                                          |

|   | ■ Eight-level hardware stack                                                                                                                                                         |

|   | Sixteen input and sixteen output channels                                                                                                                                            |

|   | Serial port for direct codec interface  Serial port for direct codec interface                                                                                                       |

|   | ■ Concurrent DMA using extended-hold operations                                                                                                                                      |

|   | <ul> <li>On-chip timer for control operations</li> </ul>                                                                                                                             |

|   | ■ On-chip clock generator                                                                                                                                                            |

|   | RS232, I/O and byte-wide EPROM bootloader                                                                                                                                            |

|   | Memory                                                                                                                                                                               |

|   | <ul> <li>544-word programmable on-chip data RAM (except TMS320C26)</li> <li>1568-word programmable on-chip data RAM (TMS320C26)</li> <li>256-word on-chip ROM (TMS320C26)</li> </ul> |

|   | ■ 4K-word on-chip program ROM (TMS320C25)                                                                                                                                            |

|   | ■ 4K-word on-chip program EPROM (TMS320E25)                                                                                                                                          |

|   | ■ 128K-word total data/program memory space                                                                                                                                          |

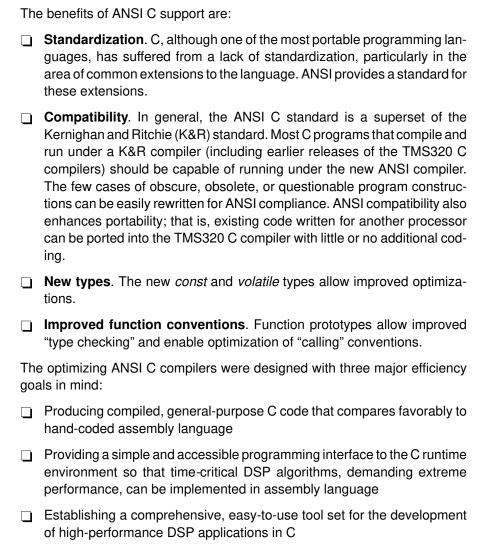

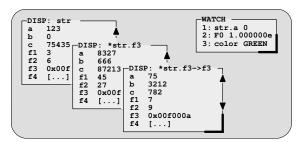

|   | Memory interfaces                                                                                                                                                                    |