#### PRODUCT NAME : CURIO (CURE FOR I/O SUBSYSTEM INTEGRATION)

(Combined 16-bit Ethernet Media Access Controller with Physical Layer Signalling (MACE), 16-bit SCSI Controller (53C94-Mode 1), Enhanced Serial Communications Controller (85C30) with LocalTalk capabilities and extended FIFOs, 79C30A Serial Bus Port Interface, and IEEE P1149.1 Test Access Port).

PRODUCT NUMBER: 79C950

**DOCUMENT NUMBER: 90-018-7661-OBS-003**

PRODUCT LINE: NPD - 802 Networking

**DATE:** 6-6-91

### **TABLE OF CONTENTS**

| 1 GENERAL DESCRIPTION                                     | 7  |

|-----------------------------------------------------------|----|

| 1.1 INTRODUCTION                                          | 7  |

| 2 DISTINCTIVE CHARACTERISTICS                             |    |

| 2.1 MACE SECTION                                          | 8  |

| 2.2 SCSI SECTION                                          |    |

| 2.3 ESCC SECTION                                          | 8  |

| 2.4 SBP INTERFACE SECTION                                 | 9  |

| 3 FUNCTIONAL DESCRIPTION                                  | 10 |

| 3.1 CURIO BLOCK DIAGRAM                                   | 10 |

| 3.1.1 Basic Block Diagram                                 |    |

| 3.1.2 Detailed Overview                                   | 11 |

| 3.2 PINOUT SUMMARY                                        |    |

| 3.2.1 Numerical Pin Assignment Table, 181 pin PGA         |    |

| 3.2.2 Pin Assignment, 168 pin PQFP                        | 10 |

| 3.3 PIN DESCRIPTION                                       | 10 |

| 3.3.1 Ethernet Subsection                                 | 18 |

|                                                           |    |

| 3.3.1.1 Attachment Unit Interface                         |    |

| 3.3.1.2 Digital Attachment Interface™                     | 20 |

| 3.3.1.3 MACE System Interface                             | 25 |

| 3.3.2 SCSI Subsection                                     | 27 |

| 3.3.2.1 SCSI BUS                                          | 27 |

| 3.3.2.2 SCSI System Interface                             | 27 |

| 3.3.3 16-Bit System Interface                             | 28 |

| 3.3.4 Internal ESCC Subsection                            |    |

| 3.3.4.1 Internal ESCC Interface                           | 29 |

| 3.3.4.2 Internal ESCC System Interface                    | 30 |

| 3.3.5 SBP Subsection                                      | 31 |

| 3.3.5.1 SBP Interface                                     | 31 |

| 3.3.5.2 External SCC Interface                            |    |

| 3.3.5.3 SBP System Interface                              |    |

| 3.3.6 8-Bit Host System Interface                         | 32 |

| 3.3.7 IEEE P1149.1 TAP Interface                          | 33 |

| 3.3.8 General Interface                                   | 34 |

| 3.4 MACE Functional description                           | 3. |

| 3.4.1 Basic MACE Functions                                | 35 |

| 3.4.1.1 Network Interfaces                                | 36 |

| 3.4.1.2 System Interface                                  | 20 |

| 3.4.2 System interface                                    | 3  |

| 3.4.2 Detailed MACE Functions                             | رد |

| 3.4.2.1 Bus Interface Unit (BIU)                          | 3  |

|                                                           |    |

| 3.4.2.1.2 BIU to Control and Status Register Data Path    | ع: |

| 3.4.2.2 FIFO Sub-system                                   | ند |

| 3.4.2.3 Media Access Control (MAC)                        | 40 |

| 3.4.2.4 Manchester Encoder/Decoder (MENDEC)               | 44 |

| 3.4.2.4.1 Attachment Unit Interface                       | 44 |

| 3.4.2.4.2 Digital Attachment Interface™                   | 4  |

| 3.4.2.5 General Purpose Serial Interface (GPSI) Extension | 4  |

| 3.4.2.6 Slave Access Operation                            | 40 |

| 3.4.2.6.1 Read Access                                     |    |

| 3.4.2.6.2 Write Access                                    |    |

| 3.4.2.7 Transmit Operation                                |    |

| 3.4.2.7.1 Transmit FIFO Write                             | 4  |

| 3.4.2.7.2 Transmit Function Programming                   | 4  |

| 3.4.2.7.3 Automatic Pad Generation                        | 5  |

| 2.4.2.7.4 Transmit ECS Congration                         | 5  |

| 3.4.2.7.5 Transmit Status Information                       | 52           |

|-------------------------------------------------------------|--------------|

| 3.4.2.7.6 Transmit Exception Conditions                     | 52           |

| 3.4.2.8 Receive Operation                                   | 54           |

| 3.4.2.8.1 Receive FIFO Read                                 | 55           |

| 3.4.2.8.2 Receive Function Programming                      | 55           |

| 3.4.2.8.3 Automatic Pad Stripping                           | 56           |

| - 3.4.2.8.4 Receive FCS Checking                            |              |

| 3.4.2.8.5 Receive Status Information                        | 56           |

| 3.4.2.8.6 Receive Exception Conditions                      | 56           |

| 3.4.2.9 Loopback Operation                                  | 50           |

| 3.4.3 MACE User Accessible Registers                        | 50           |

| 3.4.3.1 Receive FIFO(RCVFIFO)                               | 58           |

| 3.4.3.1 Receive FIFO (NOVFIFO)                              | 59           |

| 3.4.3.2 Transmit FIFO (XMTFIFO)                             | 59           |

| 3.4.3.3 Transmit Frame Control (XMTFC).                     | 60           |

| 3.4.3.4 Transmit Frame Status (XMTFS)                       | 61           |

| 3.4.3.5 Transmit Retry Count (XMTRC)                        | 62           |

| 3.4.3.6 Receive Frame Control (RCVFC)                       | 62           |

| 3.4.3.7 Receive Frame Status (RCVFS)                        | 62           |

| 3.4.3.7.1 RFS0 - Receive Message Byte Count (RCVCNT)        | 63           |

| 3.4.3.7.2 RFS1 - Receive Status (RCVSTS)                    | 63           |

| 3.4.3.7.3 RFS2 - Runt Packet Count (RNTPC)                  | 64           |

| 3.4.3.7.4 RFS3 - Receive Collision Count (RCVCC)            |              |

| 3.4.3.8 FIFO Frame Count (FIFOFC)                           | 65           |

| 3.4.3.9 Interrupt Register (IR)                             |              |

| 3.4.3.10 Interrupt Mask Register (IMR)                      | 63           |

|                                                             |              |

| 3.4.3.11 Poll Register (PR)                                 | 07           |

|                                                             |              |

| 3.4.3.13 FIFO Configuration Control (FIFOCC)                | 69           |

| 3.4.3.14 MAC Configuration Control (MACCC)                  | 71           |

| 3.4.3.15 PLS Configuration Control (PLSCC)                  | 72           |

| 3.4.3.16 PHY Configuration Control (PHYCC)                  | 73           |

| 3.4.3.17 MACE Chip Identification Register (CHIPID [15-00]) | 73           |

| 3.4.3.18 Internal Address Configuration (IAC)               | 74           |

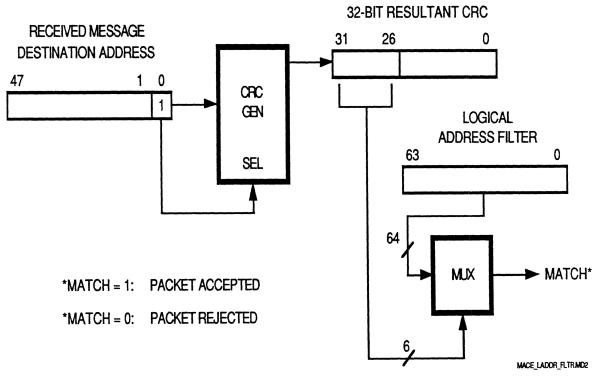

| 3.4.3.19 Logical Address Filter (LADRF [63-00])             | 74           |

| 3.4.3.20 Physical Address (PADR [47-00])                    | 76           |

| 3.4.3.21 Missed Packet Count (MPC)                          | 76           |

| 3.4.3.22 User Test Register (UTR)                           | 76           |

| 3.4.3.23 Reserved Test Register 1 (RTR1)                    | 78           |

| 3.4.3.24 Reserved Test Register 2 (RTR2)                    | 7Q           |

| 3.4.3.25 Register Table Summary                             | ۰            |

| 5.4.5.25 negister rable Sulmary                             | 00           |

| 3.4.3.26 Register Bit Summary                               | 01           |

| 3.4.3.26.1 16-Bit Registers                                 | 81           |

| 3.4.3.26.2 8-Bit Registers                                  | 81           |

| 3.4.3.26.3 Receive Frame Status                             |              |

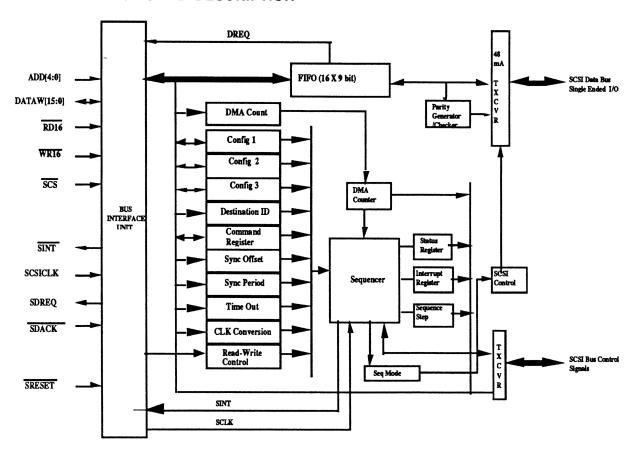

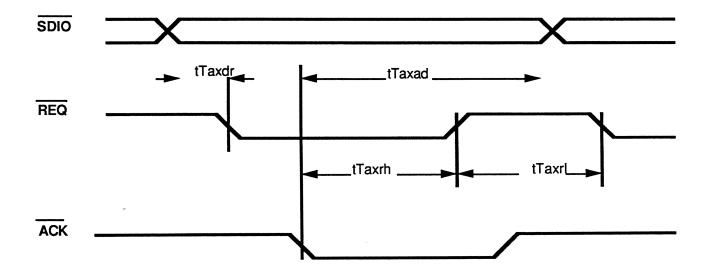

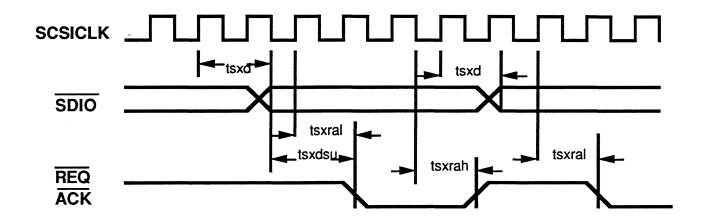

| 3.5 SCSI FUNCTIONAL DESCRIPTION                             |              |

| 3.5.1 SCSI Bus Sequences                                    | 83           |

| 3.5.2 Host Command Sequences                                |              |

| 3.5.3 Parity Detection and Generation                       | 86           |

| 3.5.4 FIFO Threshold                                        |              |

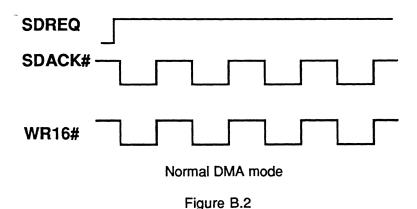

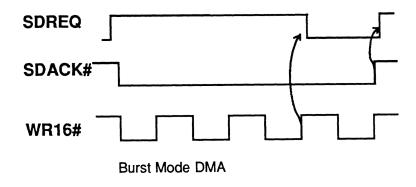

| 3.5.5 Burst Mode DMA                                        |              |

| 3.5.6 SCSI Bus Throughput                                   |              |

| 3.5.7 Data Alignment                                        | 22           |

| 3.5.8 Register Descriptions                                 | oo           |

| 3.5.8 Register Descriptions                                 | oz           |

| 3.5.8.1 DMA Counter                                         | <del>.</del> |

|                                                             |              |

| 3.5.8.3 FIFO Register                                       |              |

| 3.5.8.4 Command Register                                    |              |

| 3.5.8.5 Status Register                                     |              |

| 3.5.8.6 Destination ID                                      |              |

| 3.5.8.7 Interrupt Register                                  | 94           |

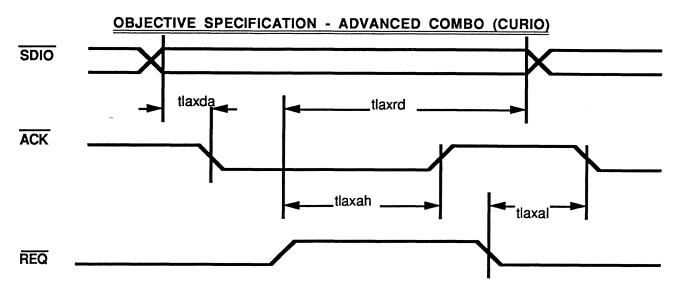

| <u>OI</u>  | JECTIVE SPECIFICATION - ADVANCED COMBO (CURIO)    |     |

|------------|---------------------------------------------------|-----|

|            | 3.5.8.8 SELECT/ReSELECT Time-Out                  | 95  |

|            | 3.5.8.9 Sequence Step                             | 95  |

|            | 3.5.8.10 Synchronous Period                       | 96  |

|            | 3.5.8.11 FÍFO Flags / Sequence Step               | 96  |

|            | 3.5.8.12 Synchronous Offset                       | 97  |

|            | 3.5.8.13 Configuration-1 Register                 | 97  |

| -          | 3.5.8.14 Clock Conversion                         | 99  |

|            | 3.5.8.15 Test Mode Register                       | 99  |

|            | 3.5.8.16 Configuration-2 Register                 | 100 |

|            | 3.5.8.17 Vendor ID/Rev / Configuration-3 Register | 101 |

|            | 3.5.8.18 FIFO Bottom Register                     | 103 |

| 3.5        | .9 Command Execution                              | 103 |

|            | 3.5.9.1 Initiator mode interrupts                 |     |

|            | 3.5.9.2 Target mode interrupts                    |     |

| 3.5        | .10 Command Set                                   | 106 |

|            | 3.5.10.1 Initiator Commands                       | 108 |

|            | 3.5.10.2 Target Commands                          | 110 |

|            | 3.5.10.3 Disconnected State Commands              | 112 |

|            | 3.5.10.4 Miscellaneous Commands                   |     |

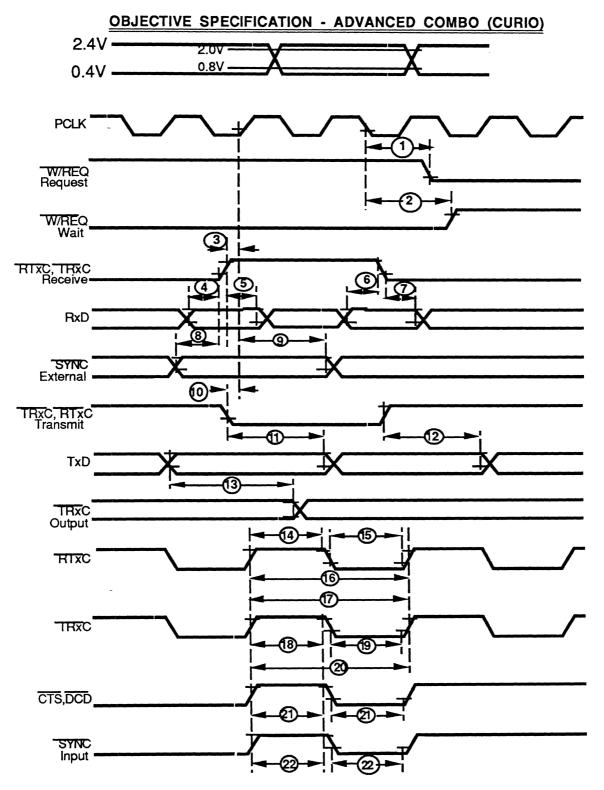

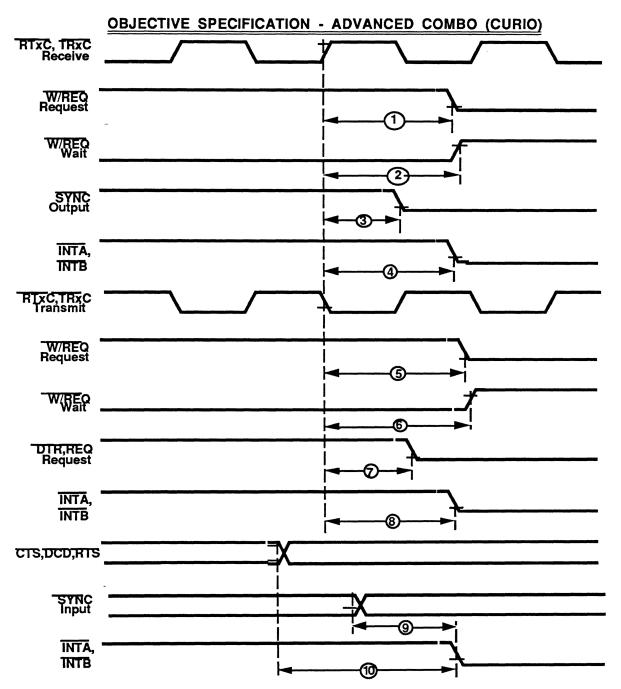

| 3.6 ESCC F | JNCTIONAL DESCRIPTION                             | 115 |

|            | .1 ESCC Block Diagram                             |     |

| 3.6        | .2 ESCC Data Path                                 | 116 |

| 3.6        | .3 Detailed ESCC Description                      | 116 |

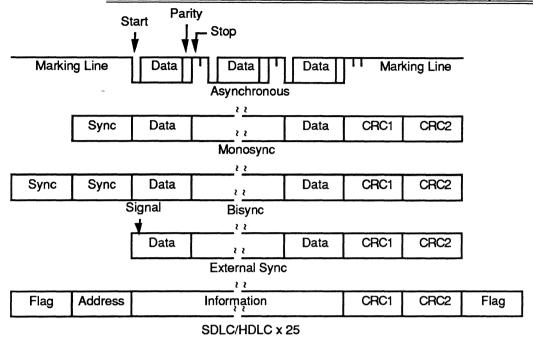

|            | 3.6.3.1 Data Communications Capabilities          | 116 |

|            | 3.6.3.2 Asynchronous Modes                        | 117 |

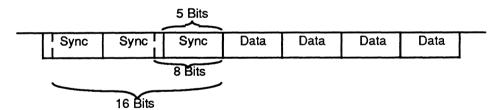

|            | 3.6.3.3 Synchronous Modes                         | 11/ |

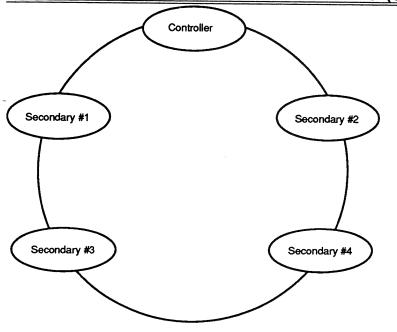

|            | 3.6.3.4 SDLC Loop Mode                            | 119 |

|            | 3.6.3.5 Baud Rate Generator                       |     |

|            | 3.6.3.6 Digital Phase-Locked Loop                 | 122 |

|            | 3.6.3.7 Crystal Oscillator                        | 122 |

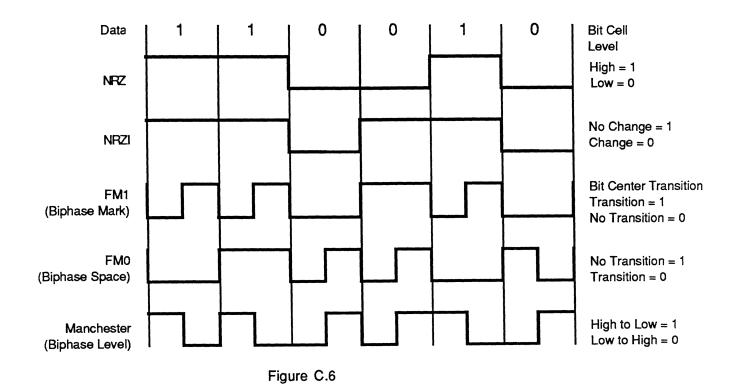

|            | 3.6.3.8 Data Encoding                             | 120 |

|            | 3.6.3.10 I/O Interface Capabilities               | 120 |

|            | 3.6.3.11 Polling                                  | 124 |

|            | 3.6.3.12 Interrupts                               | 12/ |

|            | 3.6.3.13 CPU/DMA Block Transfer                   | 125 |

| 2.0        | .4 Programming Information                        | 126 |

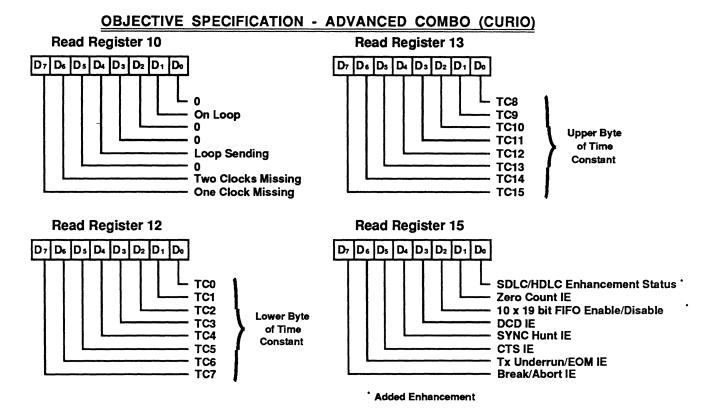

| 3.0        | 3.6.4.1 Read Registers                            | 12  |

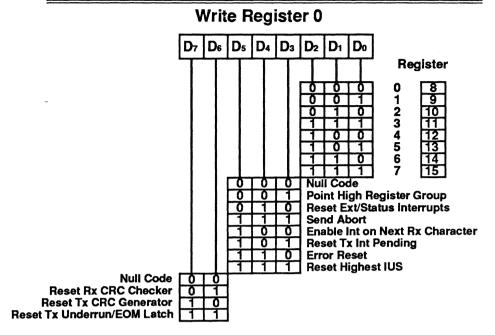

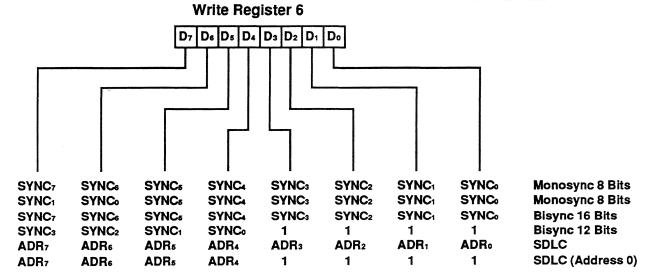

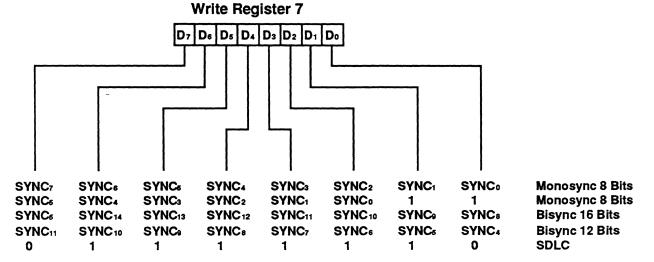

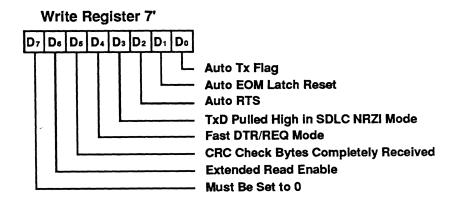

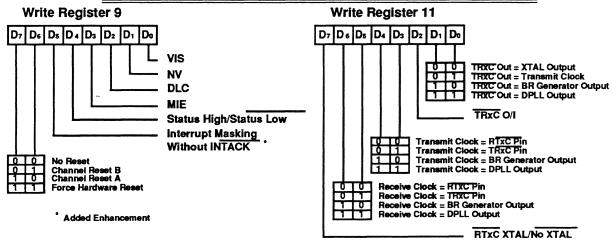

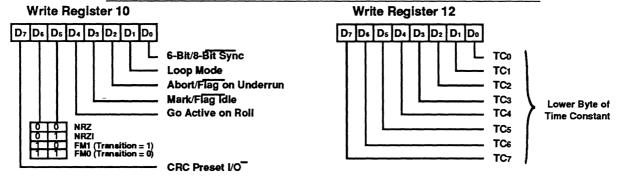

|            | 3.6.4.2 Write Registers                           | 120 |

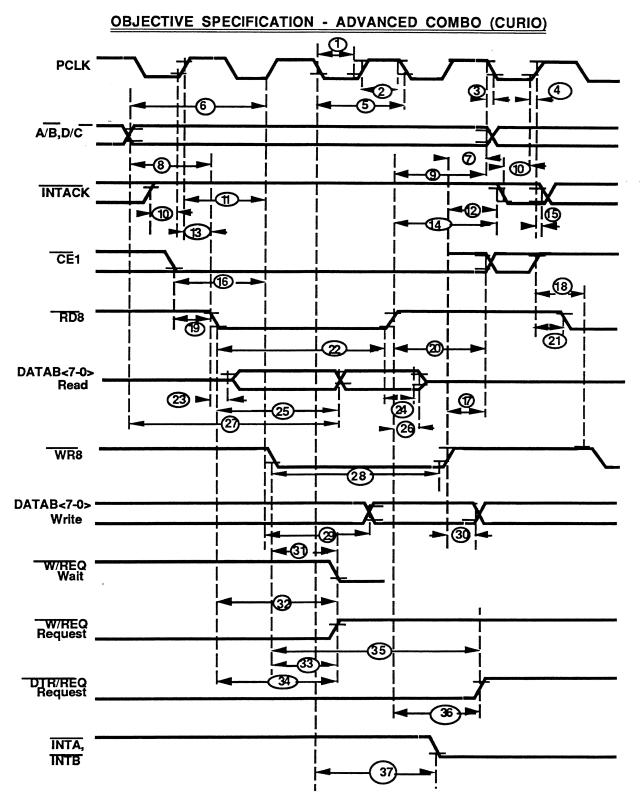

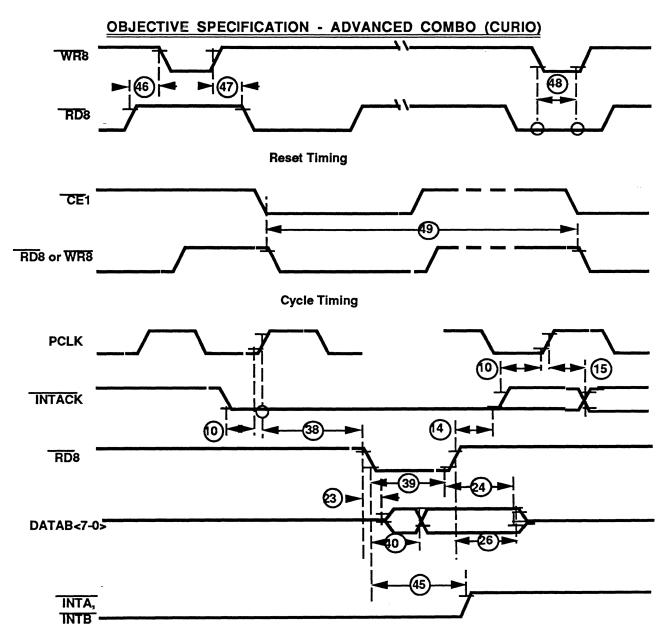

| 2 (        | 5.5 ESCC Timing                                   | 135 |

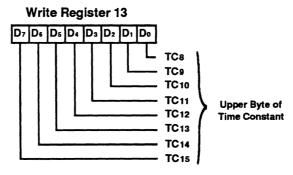

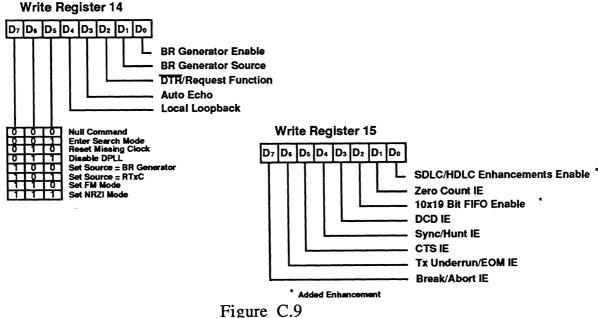

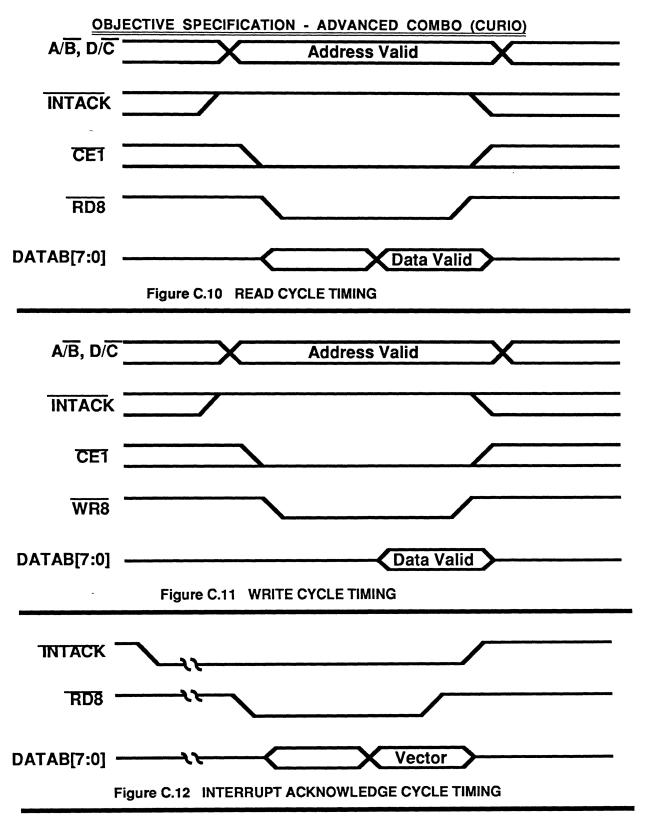

| 5.0        | 3.6.5.1 Read Cycle Timing                         | 136 |

|            | 3.6.5.2 Write Cycle Timing                        | 136 |

| -          | 3.6.5.3 Interrupt Acknowledge Cycle Timing        | 136 |

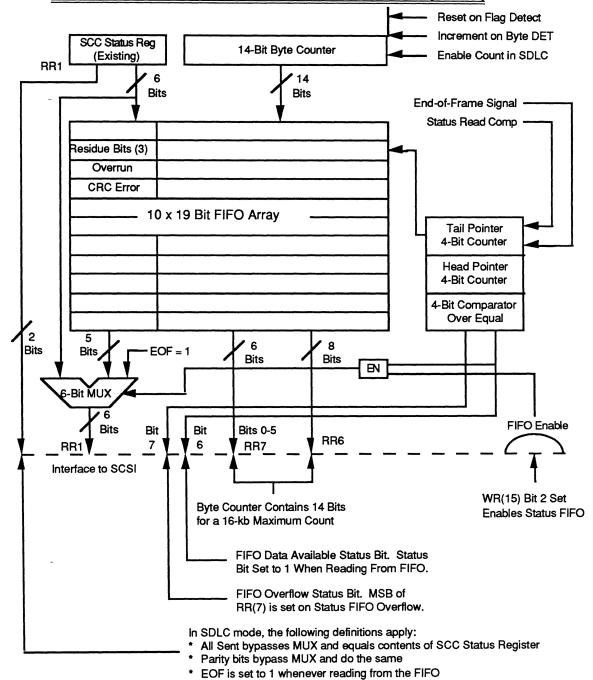

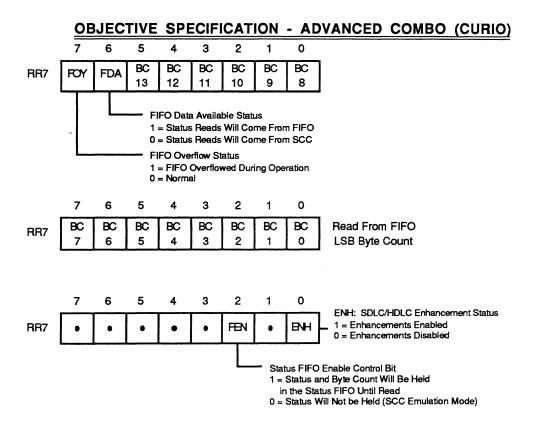

| 3 (        | 5.6 Status FIFO Enhancements                      | 138 |

| 5.         | 3.6.6.1 FIFO Detail.                              | 139 |

|            | 3.6.6.2 Enable/Disable                            |     |

|            | 3.6.6.3 Read Operation                            | 140 |

|            | 3.6.6.4 Write Operation                           | 140 |

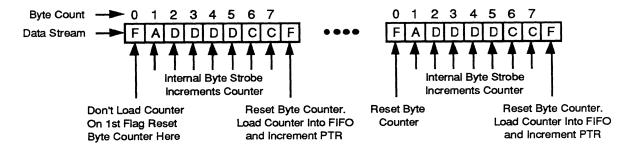

|            | 3.6.6.5 Byte Counter Detail                       | 140 |

| 3 (        | i.7 LocalTalk Enhancements                        | 14  |

| 0          | 3.6.7.1 ENRA, ENRB Register Format                | 14  |

|            | 3.6.7.2 LocalTalk protocol format                 | 144 |

|            | 3.6.7.3 ESCC enhanced features                    | 14  |

| 3.0        | 6.8 Extended Transmit and Receive Data FIFOs      | 14  |

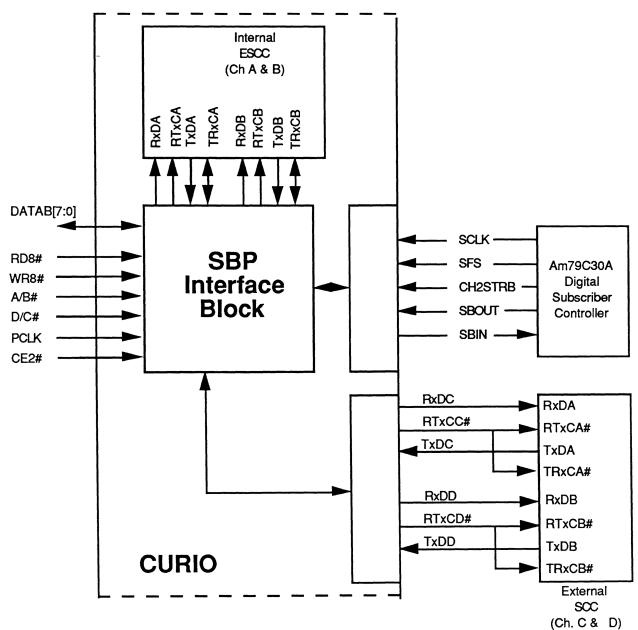

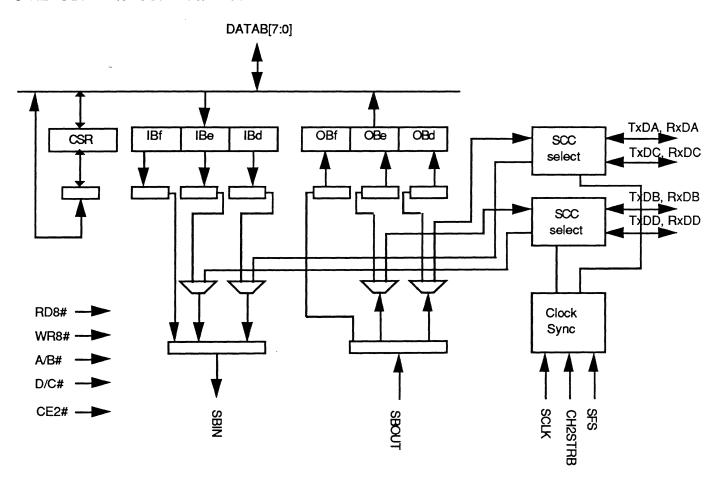

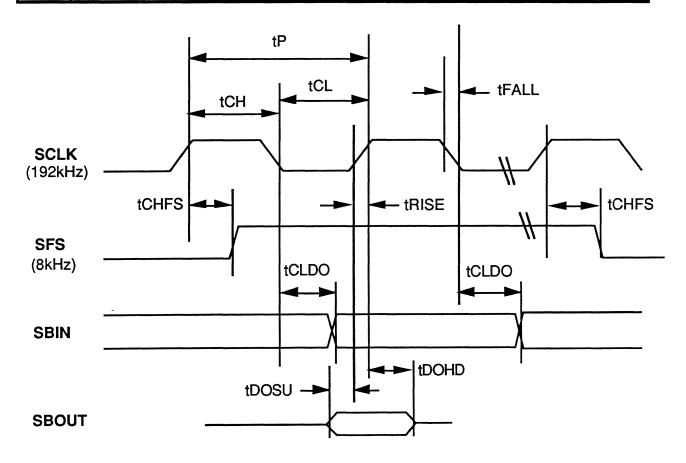

| 3.7 SBP IN | ERFACE FUNCTIONAL DESCRIPTION                     | 14  |

| 3.         | 7.1 SBP Interface Block Diagram                   | 14  |

| 3.         | 7.2 SBP Interface Data Path                       | 14  |

| 3.         | 7.3 SBP Interface Detail Functional Description   | 14  |

| -          | 3.7.3.1 Address Table                             | 14  |

|            | 2.7.2.2 Command/Status Bogistor (CSR) Format      | 15  |

| 3.7.3.3 SBP Interface Routing Commands              |     |

|-----------------------------------------------------|-----|

| 3.7.4 External SCC interface                        | 151 |

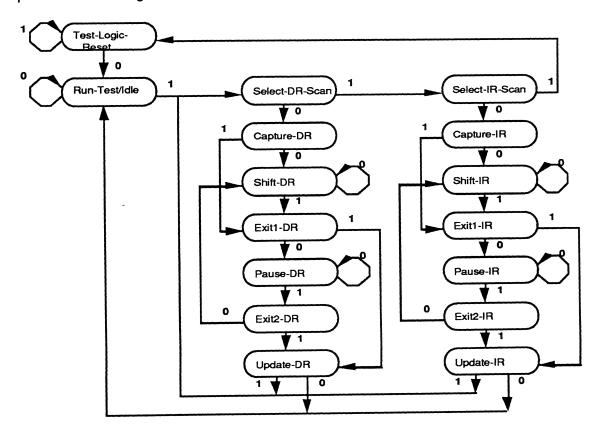

| 3.8 IEEE P1149.1 (JTAG) PORT FUNCTIONAL DESCRIPTION | 152 |

| 3.8.1 Boundary Scan Circuit                         | 152 |

| 3.8.2 TAP FSM                                       |     |

| 3.8.3 Supported Instructions                        | 153 |

| 3.8.4 Instruction Register and Decoding Logic       | 153 |

| 3.8.5 Data Register Array                           | 153 |

| 3.8.6 The TAP Reset Pin, TRST#                      | 154 |

| 4 ELECTRICAL SPECIFICATIONS                         |     |

| 4.1 DC CHARACTERISTICS                              | 155 |

| 4.2 AC CHARACTERISTICS                              | 159 |

| 4.2.1 MACE AC Timing                                |     |

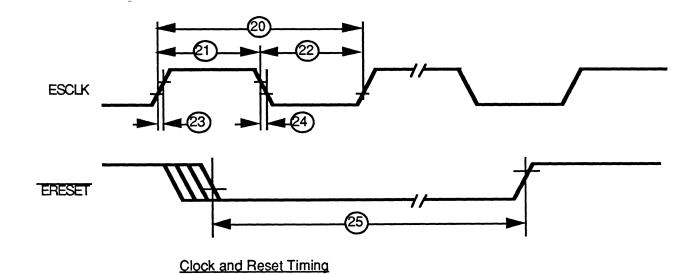

| 4.2.1.1 Clock and Reset Timing                      | 179 |

| 4.2.1.2 BIU Timing                                  | 180 |

| 4.2.1.3 AUI Timing                                  | 180 |

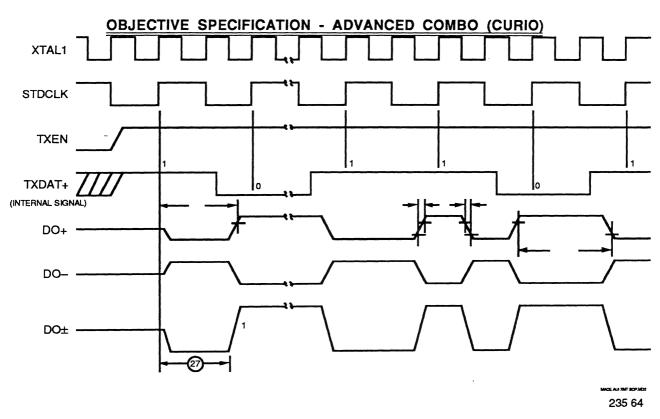

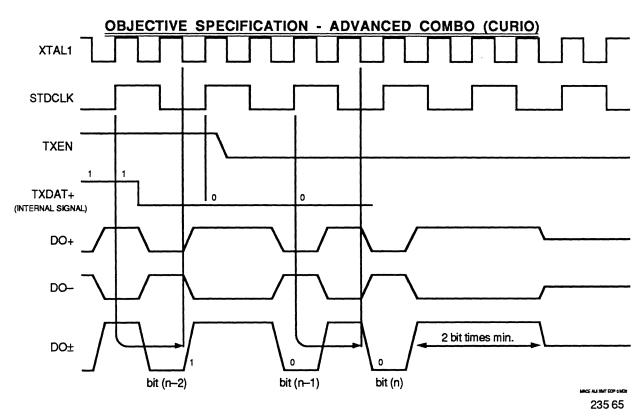

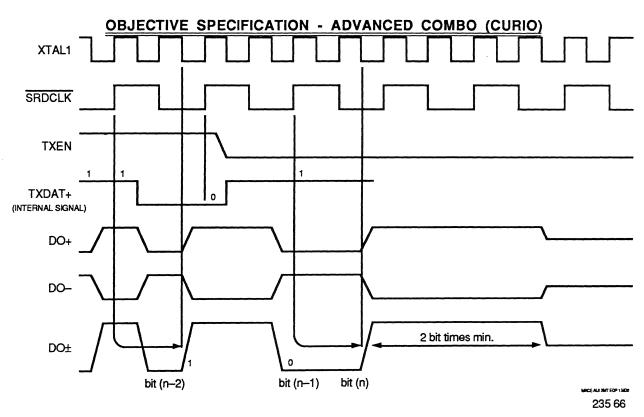

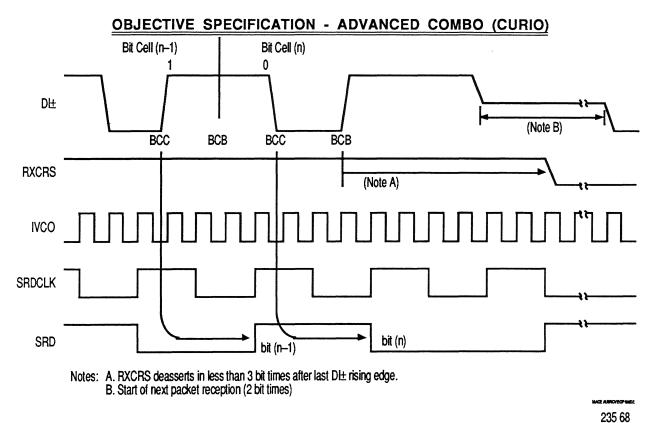

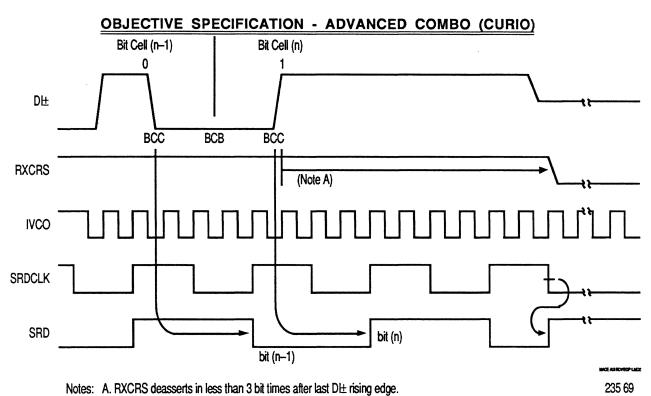

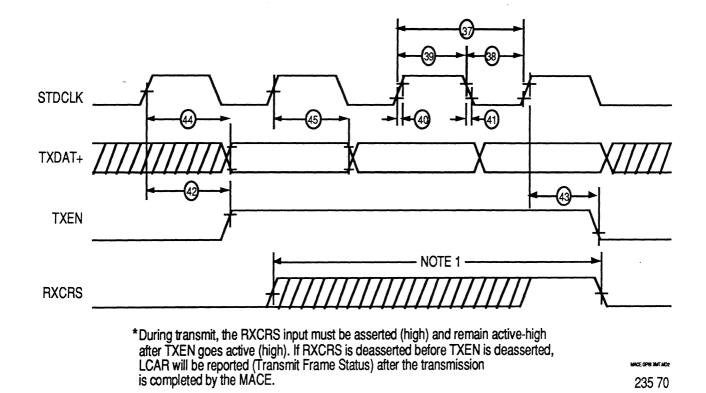

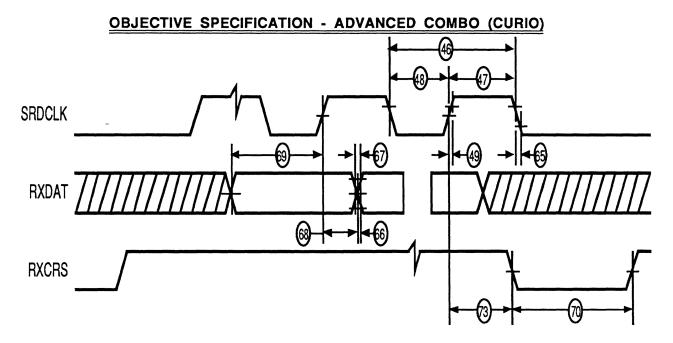

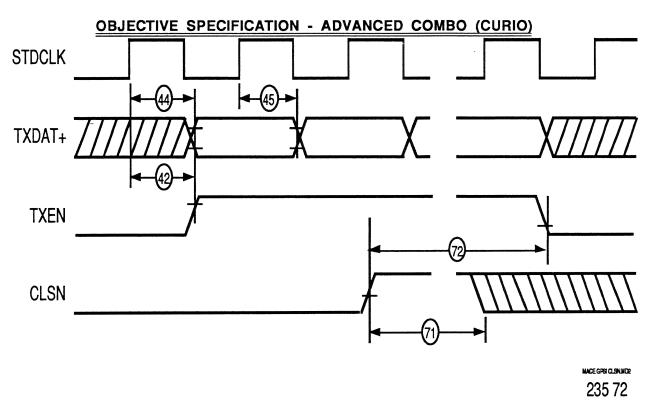

| 4.2.1.4 DAI™ Timing                                 | 182 |

| 4.2.1.5 GPSI Timing                                 | 183 |

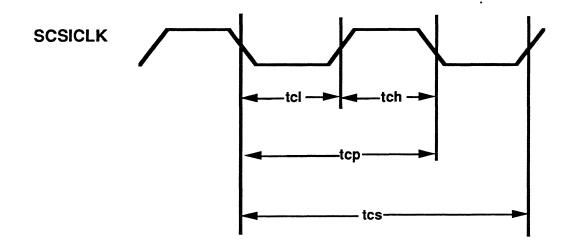

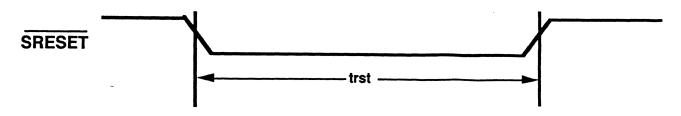

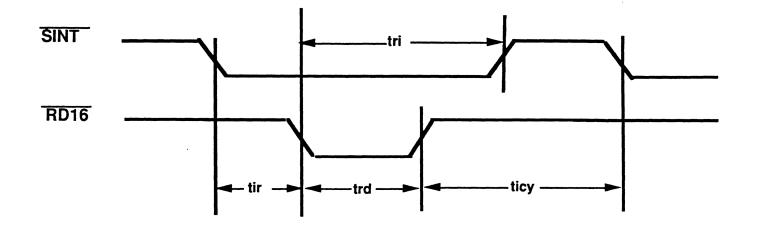

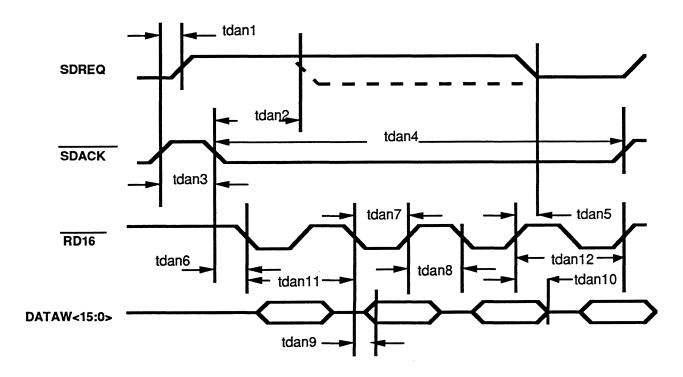

| 4.2.2 SCSI AC Timing                                | 184 |

| 4.2.3 ESCC AC Timing                                | 195 |

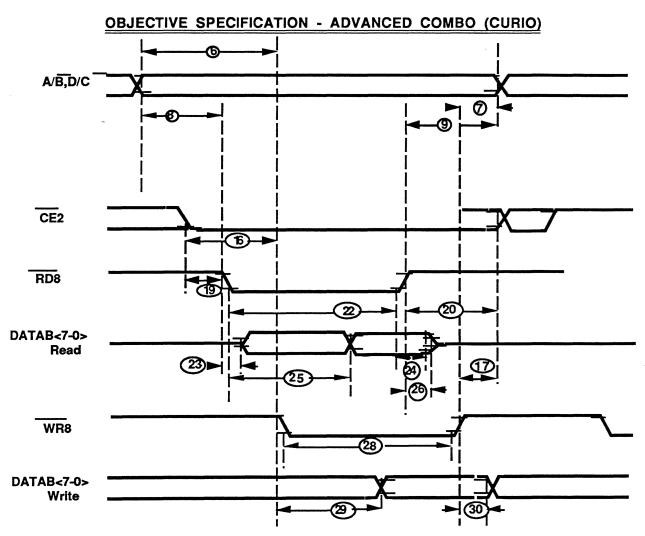

| 4.2.4 SBP AC Timing                                 | 204 |

| 4.2.5 IEEE/JTAG P1149.1 Port AC Timing              | 207 |

#### 1 GENERAL DESCRIPTION

#### 1.1 INTRODUCTION

The CURIO is a combined Ethernet controller (MACE), Small Computer Systems Interface controller (SCSI), Enhanced Serial Communications Controller (ESCC) with LocalTalk capabilities and extended FIFOs, together with a Serial Bus Port interface to the Am79C30A ISDN Controller (SBP Interface). The chip includes most of the functionality in the Am79C9416, the Am53C94 (Mode 1), the Am85C30 and the SBP interface requirement for the Am79C30A. An IEEE 1149.1 compliant test access port is also provided.

The Ethernet Media Access Controller (MACE) section embodies the Media Access Control (MAC) and Physical Signaling (PLS) sub-layers of the 802.3 protocol. The device provides the IEEE defined Attachment Unit Interface (AUI) for coupling to remote Media Attachment Units (MAUs) or on-board transceivers. The device also provides a Digital Attachment Interface TM (DAITM), bypassing the differential AUI interface.

The SCSI controller section is a high performance device conforming to the ANSI standard, X3.131-1986, for Small Computer Systems Interface. It is a software compatible superset of the 53C90 with additional commands, registers, etc., (53C94, mode 1). It also includes on-chip 48 mA drivers for single-ended transmission. The SCSI controller will operate at sustained data transfer rates of up to 5 MegaBytes per second in synchronous mode and 5 MegaBytes per second in asynchronous mode.

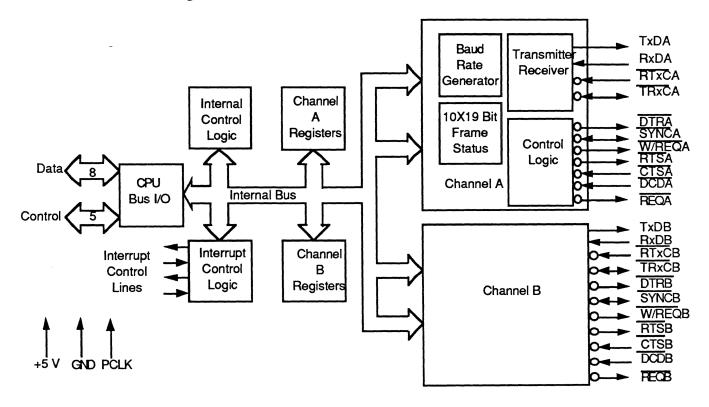

The Enhanced Serial Communications Controller (ESCC) section consists of a high-speed, multi-protocol communications peripheral. It has a total of two independent, full duplex channels and functions as a serial-to-parallel and parallel-to-serial converter/controller. AMD's proprietary enhancements make the ESCC easier to interface to, with higher effectiveness in high-speed applications, by reducing software overhead and eliminating significant external glue logic. A special hardware circuit has been included for improving system performance when executing the LocalTalk protocol. In addition, the transmit and receive data FIFO depth has been extended to 8 bytes each.

The Serial Bus Port Interface (SBP) provides a direct connection path to an external Am79C30A ISDN terminal controller. It allows the three independent 64Kbps 79C30A TDM data channels to be multiplexed and demultiplexed to and from two SCC channels and the 8-bit system bus. Pipelined byte packing/unpacking registers are also provided. The two SCC channels can be selected either from the two internal ESCC channels, or from two external SCC channels.

The IEEE P1149.1 test access port eases the continuity test between the CURIO and other components in the system by providing boundary-scan test capability.

The dual bus system interface provides a 16-bit data conduit to and from an 802.3 network and a SCSI bus, as well as an 8-bit data conduit to and from the two on chip ESCC channels and the external ISDN controller via the SBP interface.

#### 2 DISTINCTIVE CHARACTERISTICS

#### 2.1 MACE SECTION

Supports ISO 8802-3 (IEEE/ANSI 802.3) and Ethernet standards.

Implements both 802.3 MAC and PLS sub-layer functions.

Synchronous host system interface.

Fully independent system and network clocks.

High speed 16-bit data path to/from host system.

Slave based Register Address access to all on board configuration/status registers and transmit/receive FIFOs. Alternative Direct FIFO read/write access for interface to simple DMA controllers.

Arbitrary byte alignment for host memory interface.

Little endian or big endian memory interface support.

Allows for the provision of both an Attachment Unit Interface (AUI) and a Digital Attachment Interface  $^{\text{IM}}$  (DAI $^{\text{IM}}$ ).

Individual 128 byte transmit and receive FIFOs.

Runt packets (less than 64 bytes) are automatically flushed from the receive FIFO during normal operation.

The transmit FIFO retains data and does not require refilling for collision retries within the slot time (512 bit times).

Automatic padding and stripping of illegally short message frames.

External address matching and rejection support for bridge/router functions.

Dynamic transmit FCS generation programmable on a packet-by-packet basis.

Low power (sleep) mode for power critical applications.

Two internal and one external loopback capabilities.

#### 2.2 SCSI SECTION

ANSI X3.131-1986 Compatible

On-chip 48 mA drivers

Software compatible with the 53C90 (53C94-Mode 1)

SCSI-2 Tagged Queuing

High speed 16-bit data path to/from the host system

**Burst Mode**

Up to 5 MegaBytes/second Asynchronous SCSI

Up to 5 MegaBytes/second Synchronous SCSI

Single-ended SCSI mode only

#### 2.3 ESCC SECTION

Fast Data rates of up to 4 Mb/s

Two Independent Full-duplex Serial Channels

Asynchronous Mode Features include:

Programmable stop bits, clock divider, character length and parity

Break detection/divider

Error detection for framing, overrun and parity

Synchronous Mode Features include:

Supports IBM BISYNC, SDLC, SDLC Loop, HDLC and ADCCP Protocols

Programmable CRC generators and checkers

SDLC/HDLC support includes frame control, zero insertion and deletion, abort, and residue handling

Enhanced ESCC functions support high-speed frame reception using DMA

14-bit byte counter

10 X 19 SDLC/HDLC Frame Status FIFO

Independent Control on all channels

Enhanced operation does not allow special receive conditions to lock the three-byte DATA

FIFO when the 10 X 19 FIFO is enabled

Local Loopback and Auto Echo Modes

Internal or External Character Synchronization

1 Mb/s FM Encoding Transmit and Receive capability using internal DPLL at 16 Mhz Internal Synchronization between RxC to PCLK and TxC to PCLK

This allows the user to eliminate external synchronization hardware required by the older NMOS devices when transmitting or receiving data at the maximum rate of 1/4 PCLK frequency

Dedicated LocalTalk protocol state machine improves system software efficiency

8-byte deep enhanced transmit and receive data FIFOs

Separate INTerrupts for each channel

Separate DTR/REQ#, REQ# pins for each channel

#### 2.4 SBP INTERFACE SECTION

Direct Connections to an external Am79C30A ISDN Subscriber Controller and a 2-channel Serial Communication Controller (Am8530 / Am85C30)

Software programmable routing between external ISDN data with:

- 1. the 8-bit System Bus Port,

- 2. the 2-channel internal ESCC, and

- 3. the 2-channel external SCC.

Automatic framing of the three ISDN oriented data channels to and from the Am79C30A Automatic Serial and Parallel Format Conversions

Built in pipeline registers for easy synchronization

#### 3 FUNCTIONAL DESCRIPTION

#### 3.1 CURIO BLOCK DIAGRAM

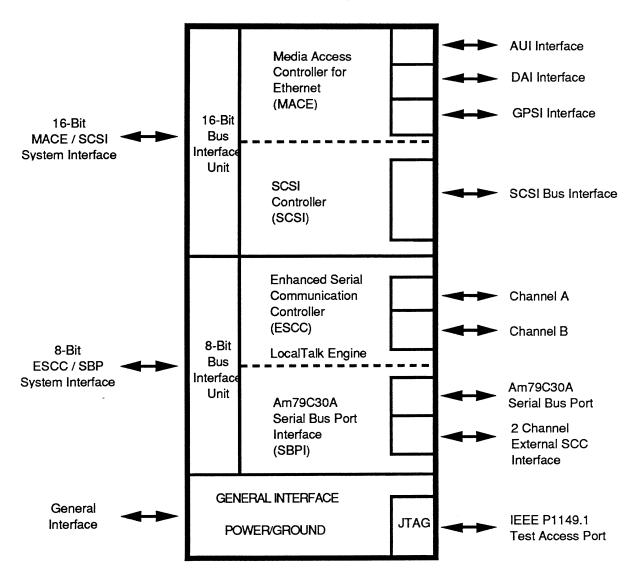

#### 3.1.1 Basic Block Diagram

### Am79C950 CURIO

### **Basic Block Diagram**

Figure 1.

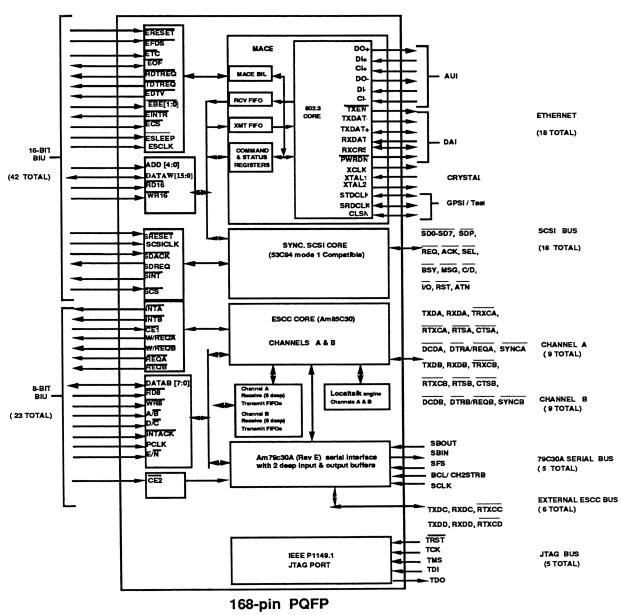

#### 3.1.2 Detailed Overview

# Am79C950 CURIO BASIC BLOCK OVERVIEW

AMD CONFIDENTIAL DATE: 5/8/91 CURIO REV: 5.2 Author: Vinod Menon

135 SIGNAL PINS

8 VCC, 2 AVCC 14 VSS, 2 AVSS

Figure 2.

### 3.2 PINOUT SUMMARY

# **CURIO PIN SUMMARY**

| PIN NAME                                                                                                                               | PIN FUNCTION                                                                                                                                                                            | TYPE                                                 | POLARITY                                | PIN ASSIGNMENT |

|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------|----------------|

| MACE Attachment<br>DO+/DO-<br>DI+/DI-                                                                                                  | Unit Interface (AUI) Data Out Data In                                                                                                                                                   | 0                                                    |                                         |                |

| CI+/CI-                                                                                                                                | Control In                                                                                                                                                                              | i                                                    |                                         |                |

| MACE Digital Atta TXEN# TXDAT+ TXDAT- RXDAT RXCRS STDCLK SRDCLK                                                                        | achment Interface <sup>TM</sup> (DAI) Transmit Enable Transmit Data + Transmit Data - Receive Data Receive Carrier Sense Serial Transmit Data Clock Serial Receive Data Clock Collision | 0<br>0<br>0<br>1<br>1/0<br>1/0<br>1/0                | Low<br>High<br>Low<br>High<br>High      |                |

| CLSN<br>PWRDN#                                                                                                                         | Power Down                                                                                                                                                                              | 0                                                    | High<br>Low                             |                |

| MACE System Inte<br>ERESET#<br>EFDS#<br>ETC#<br>EOF#<br>RDTREQ#<br>TDTREQ#<br>EDTV#<br>EBE<1-0>#<br>EINTR#<br>ECS#<br>ESLEEP#<br>ESCLK |                                                                                                                                                                                         | <br> <br> <br> <br> <br> <br>                        | Low |                |

| SCSI BUS SDI0<7-0>#, SDP# BSY# SEL# RST# REQ# ACK# ATN# MSG# C/D# I/O#                                                                 | SCSI I/O Data/Parity Bus<br>SCSI BUSY<br>SCSI SELECT<br>SCSI RESET<br>SCSI REQUEST<br>SCSI ACKNOWLEDGE<br>SCSI ATTENTION<br>SCSI MESSAGE<br>COMMAND/DATA<br>INPUT/OUTPUT                | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Low Low Low Low Low Low Low Low Low     |                |

| <u>OB</u>                                                                | SJECTIVE SPECIFICATION - ADVI                                                                                                                                                           | ANCED                            | COMBO                                    |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------------|

| SCSI System II<br>SRESET#<br>SCSICLK<br>SDACK#<br>SDREQ<br>SINT#<br>SCS# | nterface SCSI Subsection Reset SCSI System Clock SCSI Data Transfer Acknowledge SCSI Data Transfer Request SCSI Interrupt SCSI Chip Select                                              | <br> <br> <br> <br> <br>         | Low<br>High<br>Low<br>High<br>Low<br>Low |

| 16-Bit System<br>ADD<4-0><br>DATAW<15-0><br>RD16#                        | Address Bus<br>16-bit Data Bus<br>16-bit Read Signal                                                                                                                                    | <br> /0<br>                      | High<br>High<br>Low                      |

| RTxCA#                                                                   | 16-bit Write Signal  Interface Receive/Transmit Clock -Ch A                                                                                                                             | !                                | Low                                      |

| RTxCB#<br>TRxCA#<br>TRxCB#<br>DCDA#<br>DCDB#<br>DTRA#/REQA#              | Receive/Transmit Clock - Ch B Transmit/Receive Clock - Ch A Transmit/Receive Clock - Ch B Data Carrier Detect- Ch A Data Carrier Detect- Ch B Data Terminal Ready/ Req - Ch             | I<br>I/O<br>I/O<br>I<br>I<br>A O | Low<br>Low<br>Low<br>Low<br>Low          |

| DTRB#/REQB#<br>SYNCA#<br>SYNCB#<br>RxDA<br>RxDB                          | Data Terminal Ready/ Req - Ch<br>Synchronization- Ch A<br>Synchronization- Ch B<br>Receive Data-Ch A<br>Receive Data-Ch B                                                               | B O<br>I/O<br>I/O<br>I           | Low<br>Low<br>Low<br>High<br>High        |

| TxDA TxDB CTSA# CTSB# RTSA# RTSB#                                        | Transmit Data-Ch A Transmit Data-Ch B Clear to Send - Ch A Clear to Send - Ch B Request to Send - Ch A Request to Send - Ch B                                                           | 001100                           | High<br>High<br>Low<br>Low<br>Low<br>Low |

|                                                                          | System Interface ESCC Channel A Interrupt Requestance ESCC Channel B Interrupt Requestance ESCC Core Circuit Enable Wait/Request- Ch A Wait/Request- Ch B Request - Ch A Request - Ch B | est O                            | Low<br>Low<br>Low<br>Low<br>Low<br>Low   |

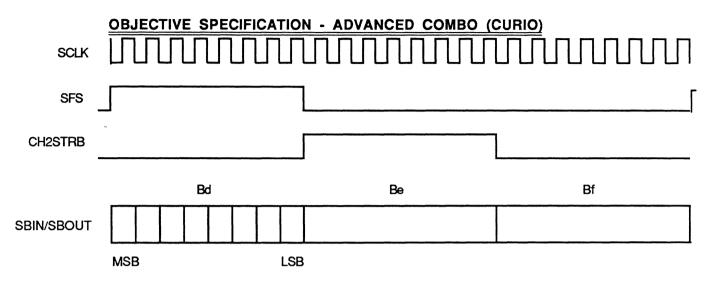

| SBP Interface<br>SFS<br>CH2STRB<br>SCLK<br>SBIN<br>SBOUT                 | Serial Frame Sync<br>SBP Channel 2 Strobe<br>Serial Data Clock<br>Serial Data In to 79C30A<br>Serial Data Out from 79C30A                                                               | <br> <br> <br> <br>              | High<br>High<br>High<br>High<br>High     |

| <u> </u>          | VIII VI EVII IVIII /IVI        | 1111000 | 3030 10 |

|-------------------|--------------------------------|---------|---------|

| External ESCC In  | terface                        |         |         |

| TxDC              | Transmit Data-Ch C             | 1       | High    |

| TxDD              | Transmit Data-Ch D             | I       | High    |

| RxDC              | Receive Data-Ch C              | 0       | High    |

| RxDD              | Receive Data-Ch D              | Ŏ       | High    |

| RTxCC#            | Receive/Transmit Clock-Ch C    | ŏ       | Low     |

| RTxCD#            | Receive/Transmit Clock-Ch D    | Ö       | Low     |

| 111200#           | Heceive/ Hansiiii Olock-Oli B  | O       | LOW     |

| SBP System Inter  | face                           |         |         |

| CE2#              | SBP Interface Circuit Enable   | 1       | Low     |

| OL2#              | ODI IIITETIACE OIICUIL ETIADIE | •       | LOW     |

| 8-Bit System Int  | erface                         |         |         |

| DATAB<7-0>        | 8-bit Data Bus                 | 1/0     | High    |

| RD8#              | 8-bit Read Signal              | 1       | Low     |

| WR8#              | 8-bit Write Signal             | Ī       | Low     |

| A/B#              | Channel A/Channel B Select     | i       | Low     |

| D/C#              | Data/Control S elect           | Ī       | Low     |

| INTACK#           | Interrupt Acknowledge          | i       | Low     |

| PCLK              | Clock                          | ŀ       | LOW     |

| E/N#              | ESCC Extended Address line     | i       | High    |

| L/14#             | LOOO Exterided Address line    | '       | ingn    |

| IEEE P1149.1 TA   | P Interface                    |         |         |

| TCK               | Test Clock                     | 1       | High    |

| TMS               | Test Mode Select               | İ       | High    |

| TDI               | Test Data In                   | i       | High    |

| TDO               | Test Data Out                  | Ö       | High    |

| TRST#             | Test Reset                     | ĭ       | Low     |

| 11101#            | 165(11656)                     | '       | LOW     |

| General Interface |                                |         |         |

| XTAL1/XTAL2       | Crystal Input                  | 1       |         |

| XCLK              | Oscillator Output              | Ö       | High    |

| <b>XCLX</b>       | Oscillator Output              | O       | riigii  |

| Power, Ground In  | nterface                       |         |         |

| DVDD              | Digital Power (8 pins)         | Р       |         |

| DVSS -            | Digital Ground (14 pins)       | P       |         |

| AVDD              | Analog Power (2 pins)          | P       |         |

| AVSS              | Analog Ground (2 pins)         | P       |         |

| AVW               | Analog Giouna (2 pins)         | 1       |         |

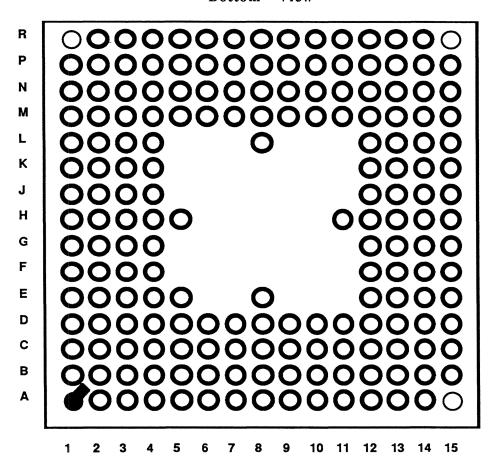

## 3.2.1 Numerical Pin Assignment Table, 181 pin PGA. (6/29/91)

| PIN | SIGNALS | PIN | SIGNALS | PIN | SIGNALS | PIN   | SIGNALS |

|-----|---------|-----|---------|-----|---------|-------|---------|

| B 1 |         | M 5 |         | P15 |         | D11   |         |

| C1  |         | M 6 |         | N15 |         | D10   |         |

| D1  | W/REQA# | M 7 | AVss    | M15 | DATAW8  | D9    |         |

| E1  | SYNCA#  | R 2 | DO-     | L15 | DATAW9  | A14   | DVcc    |

| F1  | RTxCA#  | R 3 | DO+     | K15 | DATAW10 | A13   | DVss    |

| G1  | RxDA    | R 4 | AVcc    | J15 | DATAW11 | A 1 2 | REQA#   |

| H1  | TRxCA#  | R 5 | DI-     | H15 | DATAW12 | A11   | DTRA#   |

| C2  | TxDA    | R 6 | DI+     | N14 | DATAW13 | A 1 0 | RTSA#   |

| D 2 | SBOUT   | R 7 | CI-     | M14 | DATAW14 | A 9   | CTSA#   |

| E2  | SBIN    | P 3 | CI+     | L14 | DATAW15 | B13   | DCDA#   |

| F 2 | SFS     | P 4 | AVcc    | K14 | EOF#    | B12   | PCLK    |

| G2  | CH2STRB | P 5 | DVcc    | J14 | DVss    | B11   | DCDB#   |

| H 2 | SCLK    | P 6 | EFDS#   | H14 | DVcc    | B10   | CTSB#   |

| D3  | DVcc    | P 7 | EBE0#   | M13 | SCSICLK | B 9   | RTSB#   |

| E3  | TxDC    | N 4 | EBE1#   | L13 | SRESET# | C12   | REQB#   |

| F 3 | RxDC    | N 5 | DVcc    | K13 | SDACK#  | C11   | DTRB#   |

| G3  | DVcc    | N 6 | ESCLK   | J13 | SDREQ   | C10   | DVss    |

| H3  | RTxCC#  | N 7 | TDTREQ# | H13 | SINT#   | C9    | TxDB    |

| E4  | TxDD    | M 8 | RDTREQ# | L12 | SCS#    | D8    | TRxCB#  |

| F4  | RxDD    | M 9 | ADD0    | K12 | MSG#    | D 7   | RxDB    |

| G4  | RTxCD#  | M10 | ADD1    | J12 | C/D#    | D6    | RTxCB#  |

| H4  | DVss    | M11 | ADD2    | H12 | DVss    | D5    | SYNCB#  |

| H 5 | DVss    | L8  | ADD3    | H11 | I/O#    | E8    | DVss    |

| J4  | TDO     | M12 | ADD4    | G12 | ACK#    | D4    | W/REQB# |

| K 4 | TRST#   | N 8 | RD16#   | F12 | REQ#    | C8    | D/C#    |

| L4  | TMS     | N 9 | WR16#   | E12 | SDP#    | C7    | CE1#    |

| M 4 | TCK -   | N10 | DVss    | D12 | DVss    | C6    | A/B#    |

| J3  | TDI     | N11 | ECS#    | G13 | SD0#    | C5    | E/N#    |

| K3  | DVcc    | N12 | ERESET# | F13 | SD1#    | C4    | WR8#    |

| L3  | PWRDN#  | N13 | ESLEEP# | E13 | DVcc    | C3    | RD8#    |

| M3  | XCLK    | P 8 | EINTR#  | D13 | SD2#    | B 8   | DVcc    |

| N 3 | TxDAT+  | P 9 | EDTV#   | C13 | SD3#    | B 7   | DATAB7  |

| J 2 | TxDAT-  | P10 | ETC#    | G14 | DVss    | B 6   | DATAB6  |

| K 2 | TxEN#   | P11 | DATAW0  | F14 | SD4#    | B 5   | DATAB5  |

| L 2 | RxDAT   | P12 | DVss    | E14 | SD5#    | B 4   | DATAB4  |

| M 2 | RxCRS   | P13 | DATAW1  | D14 | SD6#    | B 3   | DATAB3  |

| N 2 | CLSN    | P14 | DATAW2  | C14 | SD7#    | B 2   | DATAB2  |

| P 2 | STDCLK  | R 8 | DATAW3  | B14 | DVss    | A 8   | DVss    |

| J1  | SRDCLK  | R 9 | DVcc    | G15 | RST#    | A 7   | DATAB1  |

| K 1 |         | R10 | DATAW4  | F15 | BSY#    | A 6   | DATAB0  |

| L1  |         | R11 | DATAW5  | E15 | SEL#    | A 5   | INTB#   |

| M 1 | XTAL1 | R12 | DATAW6 | D15 | ATN# | A 4 | INTA#   |

|-----|-------|-----|--------|-----|------|-----|---------|

| N 1 | AVss  | R13 | DATAW7 | C15 | DVss | A 3 | INTACK# |

| P 1 | XTAL2 | R14 | DVss   | B15 |      | A 2 | CE2#    |

| R 1 |       | R15 |        | A15 |      | A 1 |         |

<sup>\*</sup> reference pin: E5.

Table 3.

Bottom View

181-Pin Pin Grid Array

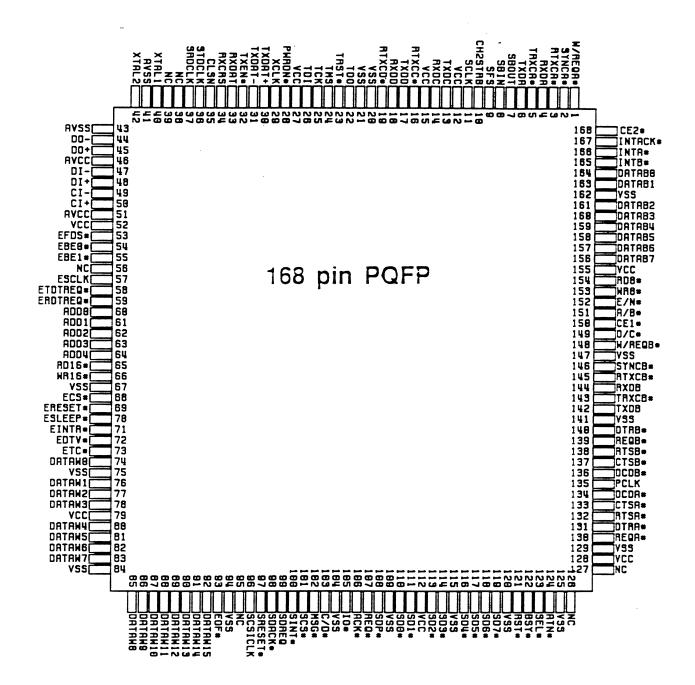

3.2.2 Pin Assignment, 168 pin PQFP. (6/29/91)

#### 3.3 PIN DESCRIPTION

#### 3.3.1 Ethernet Subsection

3.3.1.1 Attachment Unit Interface (AUI)

DO+/DO- Data Out Output

A differential output pair from the MACE for transmitting Manchester encoded data to the network. Operates at pseudo ECL levels.

DI+/DI- Data In Input

A differential input pair to the MACE for receiving Manchester encoded data from the network. Operates at pseudo ECL levels.

CI+/CI- Control In Input

A differential input pair, indicating to the MACE that a collision has been detected on the network media, indicated by the Cl± inputs being exercised with 10MHz pattern of sufficient amplitude and duration. Operates at pseudo ECL levels.

# 3.3.1.2 Digital Attachment Interface<sup>™</sup> (DAI™)

TXEN#/TXEN Transmit Enable Output

When the AUI port is selected (PORTSEL [1-0] = 00), an output indicating that valid Manchester encoded data is being output on the AUI DO± differential output. When the DAI<sup>TM</sup> port is selected (PORTSEL [1-0] = 10), indicates that Manchester data is being output on the DAI<sup>TM</sup> TXDAT± complementary outputs. Active low when the DAI<sup>TM</sup> is selected, active high when the AUI is selected. Operates at TTL levels.

| ESLEEP# | PORTSEL<br>10 | ENSTS | SIATST | INTERFACE<br>DESCRIPTION | PIN FUNCTION   |

|---------|---------------|-------|--------|--------------------------|----------------|

| 0       | XX            | Χ     | Χ      | Sleep Mode               | High Impedance |

| 1       | 00            | 1     | 0      | AUI                      | TXEN Output    |

| 1       | 0 1           | 1     | 0      | Reserved Mode            | TXEN Output    |

| 1       | 10            | 1     | 0      | DAI                      | TXEN# Output   |

| 1       | 11            | 1     | 0      | GPSI                     | TXEN Output    |

| 1       | ×             | 0     | 0      | Status Disabled          | High Impedance |

| 1       | ×             | Χ     | 1      | SIA Test Mode            | TXEN Input     |

TXDAT+/ TXDAT- Transmit Data Output

A complementary pair providing Manchester encoded data output from the MACE, for transmitting data to a local external network transceiver. During valid transmission (indicated by TXEN# low), a logical "1" is indicated by the TXDAT+ pin being in the high state, and TXDAT-in the low state; and logical "0" is indicated by the TXDAT+ pin being in the low state, and TXDAT- in the high state. During idle (TXEN# high), TXDAT+ will be in the high state, and TXDAT- in the low state. Operates at TTL levels. The operational of TXDAT+ is defined in the table below.

| ESLEEP# | PORTSEL<br>1 0 | ENSTS | SIATST | INTERFACE<br>DESCRIPTION | PIN FUNCTION   |

|---------|----------------|-------|--------|--------------------------|----------------|

| 0       | ×              | Χ     | Χ      | Sleep Mode               | High Impedance |

| 1       | 0 0            | 1     | 0      | AUI                      | High Impedance |

| 1       | 0 1            | 1     | 0      | Reserved Mode            | High Impedance |

| 1       | 10             | 1     | 0      | DAI                      | TXDAT+ Output  |

| 1       | 11             | 1     | 0      | GPSI                     | TXDAT+ Output  |

| 1       | ×              | 0     | 0      | Status Disabled          | High Impedance |

| 1       | ×              | X     | 1      | SIA Test Mode            | TXDAT Input    |

TXDAT+ Configuration

The operation of TXDAT- is defined in the table below.

| ESLEEP# | PORTSEL<br>10 | ENSTS | SIATST | INTERFACE<br>DESCRIPTION | PIN FUNCTION   |

|---------|---------------|-------|--------|--------------------------|----------------|

| 0       | ×             | Χ     | Χ      | Sleep Mode               | High Impedance |

| 1       | 0 0           | 1     | 0      | AUI                      | High Impedance |

| 1       | 0 1           | 1     | 0      | Reserved Mode            | High Impedance |

| 1       | 1 0           | 1     | 0      | DAI                      | TXDAT- Output  |

| 1       | 11            | 1     | 0      | GPSI                     | TXDAT- Output  |

| 1       | ×             | 0     | 0      | Status Disabled          | High Impedance |

| 1       | XX            | Χ     | 1      | SIA Test Mode            | High Impedance |

**TXDAT- Configuration**

Note: PORTSEL and ENSTS are located in the PLS Configuration Control register. SIATST is located in Reserved Test Register 1.

RXDAT Receive Data Input

When the DAI™ port is selected (PORTSEL [1-0] = 10), the Manchester encoded data input to the integrated clock recovery and Manchester decoder of the MACE, from an external network transceiver. When the GPSI port is selected (PORTSEL [1-0] =11), the NRZ decoded data input to the MAC core of the MACE, from an external Manchester encoder/decoder. Operates at TTL levels.

| ESLEEP# | PORTSEL<br>1 0 | ENSTS | SIATST | INTERFACE<br>DESCRIPTION | PIN FUNCTION   |

|---------|----------------|-------|--------|--------------------------|----------------|

| 0       | ×              | Χ     | Χ      | Sleep Mode               | High Impedance |

| 1       | 0 0            | 1     | 0      | AUI                      | High Impedance |

| 1       | 0 1            | 1     | 0      | Reserved Mode            | High Impedance |

| 1       | 10             | 1     | 0      | DAI                      | RXDAT Input    |

| 1       | 11             | 1     | 0      | GPSI                     | RXDAT Input    |

| 1       | ×              | 0     | 0      | Status Disabled          | High Impedance |

| 1.      | ×              | X     | 1      | SIA Test Mode            | RXDAT Output   |

#### RXDAT Configuration

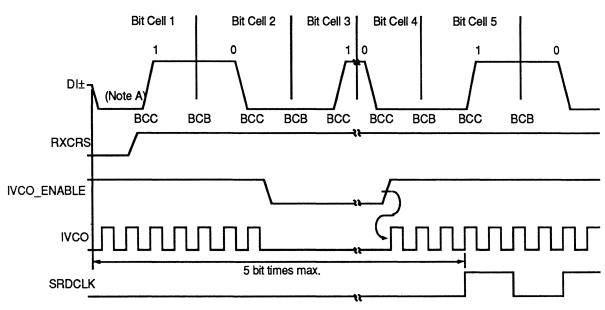

RXCRS Receive Carrier Sense

Input/Output

When the AUI port is selected (PORTSEL [1-0] = 00), an output indicating that the DI $\pm$  input pair is receiving valid Manchester encoded data from the external transceiver which meets the signal amplitude and pulse width requirements. RXCRS will be asserted high for the entire duration of the receive message. When the DAI<sup>TM</sup> port is selected (PORTSEL [1-0] = 10), an input signaling the MACE that a receive carrier condition has been detected on the network, and valid Manchester encoded data is being presented to the MACE on the RXDAT line. When the GPSI port is selected (PORTSEL [1-0] = 11), an input signalling the internal MAC core that valid NRZ data is being presented on the RXDAT input. Operates at TTL levels.

| ESLEEP# | PORTSEL<br>10 | ENSTS | SIATST | INTERFACE<br>DESCRIPTION | PIN FUNCTION   |

|---------|---------------|-------|--------|--------------------------|----------------|

| 0       | ×             | Χ     | Χ      | Sleep Mode               | High Impedance |

| 1       | 00            | 1     | 0      | AUI                      | RXCRS Output   |

| 1       | 01            | 1     | 0      | Reserved Mode            | RXCRS Output   |

| 1       | 10            | 1     | 0      | DAI                      | RXCRS Input    |

| 1       | 11            | 1     | 0      | GPSI                     | RXCRS Input    |

| 1       | XX            | 0     | 0      | Status Disabled          | High Impedance |

| 1       | ×             | X     | 1      | SIA Test Mode            | RXCRS Output   |

**RXCRS** Configuration

Note: PORTSEL and ENSTS are located in the PLS Configuration Control register. SIATST is located in Reserved Test Register 1.

STDCLK Serial Transmit Data Clock Input/Output

When using the AUI or DAI™ port, STDCLK is an output operating at one half the crystal or XCLK frequency. STDCLK is the encoding clock for Manchester data transferred to the output of either the AUI DO± pair or the DAI™ TXDAT± pair. When using the GPSI port, STDCLK is an input at the network data rate, provided by the external Manchester encode/decoder, to strobe out the NRZ data presented on the TXDAT+ output.

| SLEEP# | PORTSEL<br>10 | ENSTS | SIATST | INTERFACE<br>DESCRIPTION | PIN FUNCTION   |

|--------|---------------|-------|--------|--------------------------|----------------|

| 0 -    | ×             | Χ     | Х      | Sleep Mode               | High Impedance |

| 1      | 0.0           | 1     | 0      | AUI                      | STDCLK Output  |

| 1      | 01            | 1     | 0      | Reserved Mode            | STDCLK Output  |

| 1      | 10            | 1     | 0      | DAI                      | STDCLK Output  |

| 1      | 11            | 1     | 0      | GPSI                     | STDCLK Input   |

| 1      | ×             | 0     | 0      | Status Disabled          | High Impedance |

| 1      | ×             | Χ     | 1      | SIA Test Mode            | STDCLK Output  |

#### STDCLK Configuration

Note: PORTSEL and ENSTS are located in the PLS Configuration Control register. SIATST is located in Reserved Test Register 1.

**SRDCLK**

Serial Receive Data Clock

Input/Output

The Serial Receive Data output is synchronous to this clock, which runs at the 10MHz receive data clock frequency. The pin is only configured as an input when the SIATST is asserted.

| SLEEP# | PORTSEL<br>10 | ENSTS | SIATST | INTERFACE<br>DESCRIPTION | PIN FUNCTION   |

|--------|---------------|-------|--------|--------------------------|----------------|

| 0      | XX            | Χ     | Χ      | Sleep Mode               | High Impedance |

| 1      | 0 0           | 1     | 0      | AUI                      | SRDCLK Output  |

| 1      | 0 1           | 1     | 0      | Reserved Mode            | SRDCLK Output  |

| 1      | 10            | 1     | 0      | DAI                      | SRDCLK Output  |

| 1      | 11            | 1     | 0      | GPSI                     | SRDCLK Input   |

| 1      | XX            | 0     | 0      | Status Disabled          | High Impedance |

| 1      | XX            | X     | 1      | SIA Test Mode            | SRDCLK Output  |

#### **SRDCLK Configuration**

Note: PORTSEL and ENSTS are located in the PLS Configuration Control register. SIATST is located in Reserved Test Register 1.

CLSN

Collision

Input/Output

An external indication that a collision condition has been detected by the Medium Attachment Unit (MAU), and that signals from two or more nodes are present on the network. When the AUI port is selected (PORTSEL [1-0] = 00), CLSN will be activated when the Cl± input pair is receiving a collision indication from the external transceiver which meets the signal amplitude and pulse width requirements. CLSN will be asserted high for the entire duration of the collision detection, but will not be asserted during the SQE Test message following a transmit message on the AUI. When the DAI™ port is selected (PORTSEL [1-0] = 10), CLSN will be asserted high when simultaneous transmit and receive activity is detected (logically detected when RXCRS and TXEN# are both active). When the GPSI port is selected (PORTSEL [1-0] = 11), an input from the external Manchester encoder/decoder signaling the MACE that a collision condition has been detected on the network, and any receive frame in progress should be aborted. Operates at TTL levels.

| SLEEP# | PORTSEL<br>10 | ENSTS | SIATST | INTERFACE<br>DESCRIPTION | PIN FUNCTION   |

|--------|---------------|-------|--------|--------------------------|----------------|

| 0      | ×             | Χ     | Χ      | Sleep Mode               | High Impedance |

| 1      | 0.0           | 1     | 0      | AUI                      | CLSN Output    |

| 1      | 0 1           | 1     | 0      | Reserved Mode            | CLSN Output    |

| 1      | 10            | 1     | 0      | DAI                      | CLSN Output    |

| 1      | 11            | 1     | 0      | GPSI                     | CLSN Input     |

| 1      | ×             | 0     | 0      | Status Disabled          | High Impedance |

| 1      | ×             | X     | 1      | SIA Test Mode            | CLSN Output    |

#### **CLSN Configuration**

Note: PORTSEL and ENSTS are located in the PLS Configuration Control register. SIATST is located in Reserved Test Register 1.

PWRDN#

Power Down

Output

An output from the MACE to indicate the network port in use, as programmed by the PORTSEL[1-0] bits. Active (low) when the AUI port is selected. Inactive (high) when the DAI<sup>TM</sup> is selected.

| ESLEEP# | PORTSEL<br>10 | ENSTS | SIATST | INTERFACE<br>DESCRIPTION | PIN FUNCTION   |

|---------|---------------|-------|--------|--------------------------|----------------|

| 0       | ×             | X     | Χ      | Sleep Mode               | High Impedance |

| 1       | 00            | X     | 0      | AUI                      | Low            |

| 1       | 01            | X     | 0      | Reserved Mode            | High           |

| 1       | 10            | X     | 0      | DAI                      | High           |

| 1       | 11            | Х     | 0      | Reserved                 |                |

| 1       | XX            | X     | 1      | SIA Test Mode            | High Impedance |

PWRDN# Configuration

3.3.1.3 MACE System Interface

ERESET# Ethernet Reset

Input

This signal clears the MACE subsection logic. ERESET# can be asynchronous to ESCLK, but must be asserted for a minimum of 15 ESCLK cycles.

EFDS#

Ethernet FIFO Data Select

Input

Ethernet FIFO Data Select allows direct access to the transmit or receive FIFO without use of the address bus. EFDS# must be activated in conjunction with RD16#. When the MACE samples RD16# as low and EFDS# low, a read cycle from the receive FIFO will be initiated. When the MACE samples WR16# and EFDS# low, a write cycle to the transmit FIFO will be initiated. The ECS# line should be inactive (high) when FIFO access is requested using the EFDS# pin. If the MACE samples both ECS# and EFDS# as active simultaneously, no cycle will be executed, and EDTV# will remain inactive.

ETC#

Timing Control

Input

The Timing Control input conditions the minimum number of System Clocks (ESCLK) cycles taken to read or write the internal registers and FIFOs. ETC# can be used as a wait state generator, to allow additional time for data to be presented by the host during a write cycle, or allow additional time for the data to be latched in a read cycle. ETC# has an internal (ESLEEP# disabled) pull up.

| ETC# | Number of Clocks |

|------|------------------|

| 1    | 2                |

| 0    | 3                |

EOF#

End Of Frame

Input/Output/3-state

End Of Frame will be asserted by the MACE as the last byte/word of information is read from the receive FIFO. This will indicate the completion of the frame status field for the receive message. End Of Frame must be asserted low to the MACE, as the last byte/word of the frame is written into the transmit FIFO.

RDTREQ# Receive Data Transfer Request Output

Receive Data Transfer Request indicates there is data in the receive FIFO to be read. When

RDTREQ# is asserted there will be a minimum of 16 bytes to be read except at the end of the

frame, in which case EOF# will be asserted. RDTREQ# can be programmed to request receive

data transfer when 16, 32 or 64 bytes are available in the receive FIFO, by programming the

Receive FIFO Watermark (RCVFW bits) in the FIFO Configuration Control register. Note that

unless Runt Packet Accept is enabled (RPA bit) in the User Test Register, at least 64 bytes of

packet information must be received prior to the initial assertion of RDTREQ# for the received

packet. RDTREQ# will be asserted only when Enable Receive (ENRCV) is set in the MAC

Configuration Control register.

TDTREQ# Transmit Data Transfer Request Output

Transmit Data Transfer Request indicates there is room in the transmit FIFO for more data.

TDTREQ# is asserted when there are a minimum of 16 bytes empty in the transmit FIFO.

TDTREQ# can be programmed to request transmit data transfer when 16, 32 or 64 bytes are available in the transmit FIFO, by programming the Transmit FIFO Watermark (XMTFW bits) in the FIFO Configuration Control register. TDTREQ# will be asserted only when Enable Transmit (ENXMT) is set in the MAC Configuration Control register.

EDTV# Data Transfer Valid Output

When asserted, indicates that the read or write operation has completed successfully. The

absence of EDTV# at the termination of a host access cycle on the MACE indicates that the data

transfer was unsuccessful. The latching or strobing of read or write data can be synchronized to

the ESCLK input rather then using this signal.

Used to indicate the active portion of the data transfer to or from the internal FIFOs. For word (16-bit) transfers, both EBE<sub>0</sub> and EBE<sub>1</sub> should be activated by the external host/controller. Single byte transfers are performed by identifying the active data bus byte and activating only one of the two signals. The function of the EBE<sub>0-1</sub> pins is programmed using the BSWP bit (BIU Configuration Control register, bit 6). EBE<sub>0-1</sub># are not required for accesses to internal MACE registers.

EINTR# Output / 3-state

An attention signal that indicates that one or more of the following status flags are set: XMTINT, RCVINT, MPCO, CERR or BABL. Each of the interrupts can be individually masked. No interrupt conditions can take place in the MACE after a hardware ERESET#.

ECS# MACE Chip Select Input

Used to access the MACE FIFOs and internal registers locations using the address bus. The FIFOs may alternatively be directly accessed without supplying the FIFO address, by using the EFDS# and RD16#, WR16# pins.

ESLEEP# Sleep Mode Input

The Sleep Mode input allows the MACE to be placed in a power saving mode. All outputs will be

placed in an inactive or high impedance state. Clock inputs to the MACE can be suspended. On

removal of ESLEEP#, the MACE will go through an internally generated hardware ERESET#

sequence. The MACE internal registers must be re-initialized on removal of the Sleep Mode.

**ESCLK**

MACE Clock

Output

The system clock input controls the operational frequency of the slave interface to the MACE and the internal processing of frames. ESCLK is unrelated to the 20MHz clock frequency required for the 802.3/Ethernet interface. The frequency range is currently 5 MHz - 25 MHz.

#### 3.3.2 SCSI Subsection

3.3.2.1 **SCSI BUS**

SDIO<7-0>#,SDP# SCSI I/O Data/Parity Bus

Input/Output

48 mA, open drain SCSI single-ended Data/Parity Input/Output bus. These pins are active low SCSI Data signals.

BSY#

SCSI BUSY

Input/Output

48mA open drain SCSI I/Os.

SEL#

SCSI SELECT

Input/Output

48mA open drain SCSI I/O.

RST#

SCSI RESET

Input/Output

48mA open drain SCSI I/O. This command will cause the SCSI Controller to driver RST# true for 25-40uS, depending on SCSICLK frequency and SCSICLK Conversion Factor. See Miscellaneous Commands.

REQ#

SCSI REQUEST

Input/Output

48mA open drain SCSI I/O. Asserted only in Target mode.

ACK#

SCSI ACKNOWLEDGE

Input/Output

48mA open drain SCSI I/O. Driven in Initiator mode only.

ATN#

SCSI ATTENTION

Input/Output

48mA output Schmitt trigger input. In Initiator mode, is asserted when the controller detects an incoming parity error, or may be asserted by certain SCSI CORE commands. In Target mode, this signal is an input. Hysterisis is nominally 400mV centered at 1.4 Volt.

MSG#

SCSI MESSAGE

Input/Output

Bi-directional SCSI phase signal. IOL is 48mA output in Target mode, and Schmitt trigger input in Initiator mode. The I/O hysterisis is nominally 400mV centered at 1.4 Volt.

C/D#

COMMAND/DATA

Input/Output

Bi-directional SCSI phase signal. IOL is 48mA output in Target mode, and Schmitt trigger input in Initiator mode. The I/O hysterisis is nominally 400mV centered at 1.4 Volt.

1/0#

INPUT/OUTPUT

Input/Output

Bi-directional SCSI phase signal. IOL is 48mA output in Target mode, and Schmitt trigger input in Initiator mode. The I/O hysterisis is nominally 400mV centered at 1.4 Volt.

3.3.2.2 SCSI System Interface

SRESET#

SCSI Subsection Reset

Input

This signal clears the internal SCSI controller logic. It can be asynchronous to SCSICLK.

SCSICLK

SCSI System Clock

Input

Square wave clock input which generates internal chip timing. The maximum frequency is 25MHz. The minimum frequency for asynchronous SCSI is 10MHz. The minimum frequency for synchronous transmission rate is equal to the SCSICLK period divided by the value in the Synchronous Transfer Period Register. The asynchronous transmission rate is indirectly affected by the SCSICLK period. See section 3.5.6 on SCSI Bus Throughput.

SDACK#

SCSI Data Transfer Acknowledge

Input

Active low SCSI DMA Acknowledge from the DMA controller. SDACK# accesses the FIFO only, while SCS# accesses any register including the FIFO. SCS# and SDACK# must never be true simultaneously. Furthermore, since MACE and SCSI sections cannot be enabled at the same time, it follows that only one out of the 4 signals, EFDS#, ECS#, SDACK# and SCS# can be active at any moment.

**SDREQ**

SCSI Data Transfer Request

Output

Active high SCSI DMA Request signal to the DMA controller. SDREQ will remain true as long as either the FIFO contains at least one word to send to memory during DMA read, or has room for one more word in the FIFO during DMA write.

SINT#

SCSI Interrupt

Output

Open drain SCSI Interrupt signal to the microprocessor. It is latched on the rising edge of SCSICLK. It may be cleared by reading the Interrupt Register or SRESET# or a SCSI software Reset (but not by a SCSI Reset). This output cannot be masked by the user.

SCS#

SCSI Chip Select

Input

This input enables 8-bit access to SCSI core registers during read or write. SCS# uses the address inputs to access any register and including the FIFO, while SDACK# accesses only the FIFO. SCS# and SDACK# must never be active simultaneously. Furthermore, since MACE and SCSI sections cannot be enabled at the same time, it follows that only one out of the 4 signals, EFDS#, ECS#, SDACK# and SCS# can be active at any moment.

### 3.3.3 16-Bit System Interface

ADD<4-0>

Address Bus

Input

Ethernet:

ADD is used to access the internal registers and FIFOs for read or write

operations.

SCSI:

These pins are address bits used to access the internal registers. Although

shared with the Ethernet subsection, access timing involved is

independent.

DATAW<15-0>

Data Bus

Input /Output/3-state

Ethernet:

DATAW Bus contains read and write data to and from internal registers

and the transmit and receive FIFOs.

SCSI:

Bidirectional active high bus with internal pull-ups. The processor accesses internal registers on the lower 8 bits, while the DMA accesses the FIFO using all 16 bits. Although shared with the Ethernet subsection,

access timing involved is independent.

RD16#

Read Control Signal

Input

Ethernet: SCSI:

Indicates a READ operation during a MACE register or FIFO access. Active low register Read signal. This input allows internal registers to drive the data bus when either SCS# or SDACK# are true. Although shared with the Ethernet subsection, access timing involved is independent. However, RD16# and WR16# should not be asserted

simultaneously.

WR16#

Write Control Signal

Input

Ethernet: SCSI:

Indicates a WRITE operation during a MACE register or FIFO access.

Active low register Write signal. This input causes data to be written into

the SCSI controller's internal registers when SCS# is true. When SDACK# is true, data is written into the internal FIFO. Although shared with the Ethernet subsection, access timing involved is independent. However, RD16# and WR16# should not be asserted simultaneously.

#### 3.3.4 Internal ESCC Subsection

#### 3.3.4.1 Internal ESCC Interface

RTxCA#, RTxCB# Receive/Transmit Clocks

Inputs

These pins can be programmed in several different modes of operation. In each channel, RTxC# may supply the receive clock, the transmit clock, the clock for the baud rate generator, or the clock for the Digital Phase-Locked Loop. These pins can also be programmed for use with the respective SYNC# pins as a crystal oscillator. The receive clock may be 1, 16, 32 or 64 times the data rate in asynchronous modes.

TRxCA#, TRxCB# Transmit/Receive Clocks Input/Output

These pins can be programmed in several different modes of operation. TRxC# may supply the

receive clock or the transmit clock in the input mode or supply the output of the Digital PhaseLocked Loop, the crystal oscillator, the baud rate generator, or the transmit clock in the output

mode.

DCDA#, DCDB#

Data Carrier Detect

Inputs

These pins function as receiver enables if they are programmed for Auto Enables; otherwise, they may be used as general purpose input pins. Both pins are Schmitt-triggered buffered to accommodate slow rise-time signals. The SCC detects pulses on these pins and can interrupt the CPU on both logic level transitions.

DTRA#/REQA#, DTRB#/REQB# Data Terminal Ready Outputs

These outputs follow the inverted state programmed into the DTR bit in WR5. They can also be used as general purpose outputs or as Request Lines for a DMA controller.

SYNCA#, SYNCB# Synchronization Input/Output

These pins can act either as inputs, outputs, or part of the crystal oscillator circuit. In the

Asynchronous Receive mode (crystal oscillator option not selected), these pins are inputs

similar to CTS# and DCD#. In this mode, transitions on these lines affect the state of the

Synchronous/Hunt status bits in Read Register 0 but have no other function.

In External Synchronization mode with the crystal oscillator not selected, these lines also act as inputs. In this mode, SYNC# must be driven LOW two receive clock cycles after the last bit in the synchronbous character is received. Character assembly begins on the rising edge of the receive clock immediately preceding the activation of SYNC#.

In the Internal Synchronization mode (Monosync and Bisync) with the crystal oscillator not selected, these pins act as outputs and are active only during the part of the receive clock cycle in which synchronous characters are recognized. The synchronous condition is not latched, so these outputs are active each time a synchronization pattern is recognized (dregardless of character boundaries). In SDLC mode, these pins act as outputs and are valid on receipt of a flag.

RxDA, RxDB Receive Data Inputs These input signals receive serial data at standard TTL levels.

TxDA, TxDB Transmit Data Outputs These output signals transmit serial data at standard TTL levels.

RTSA#, RTSB# Request to Send Outputs

When the Request to Send (RTS) bit in Write Register 5 is set, the RTS# signal goes LOW. When the RTS bit is reset in the asynchronous mode and Auto Enable is on, the signal goes HIGH after the transmitter is empty. In synchronous mode or in asynchronous mode with Auto Enable off, the RTS# pin strictly follows the state of the RTS bit. Both pins can be used as general-purpose outputs.

REQA#, REQB# Transmit Request for Channel A/B Outputs Request lines for a DMA controller.

#### 3.3.4.2 Internal ESCC System Interface

INTA#, INTB# Interrupt Request Output Interrupt Request (open drain, active low). This signal is activated when the ESCC activates an interrupt.

CE1# Circuit Enable Input

Circuit Enable for the ESCC Subsection. This signal selects the ESCC for a read or write operation.

W/REQA#, W/REQB#

Wait/Request

Outputs

Wait/Request (open-drain when programmed for a Wait function, driven HIGH or LOW when programmed for a Request function). These dual-purpose outputs may be programmed as Request lines for a DMA controller or as Wait lines to synchronize the CPU to the ESCC data rate. The reset state is Wait.

#### 3.3.5 SBP Subsection

3.3.5.1 SBP Interface

SFS

Serial Frame Synchronization

Input

SFS is an 8 kHz signal which identifies the beginning of each frame by a low to high transition. The 192kbps data stream on SBIN and SBOUT is referenced to SFS.

CH2STRB

SBP Channel 2 Strobe

Input

This signal is active during the 8-bit times of the second 64kbps data channel.

SCLK

Serial Data Clock

Input

This signal carries the 192kHz data clock. Input and Output data will assumed to be valid at the rising edge of this signal.

SBIN

Serial Data In

Output

This pin outputs data to the SBIN input of the external 79C30A device.

SBOUT

Serial Data Out

Input

This pin receives data from the SBOUT output of the external 79C30A device.

3.3.5.2 External SCC Interface

TxDC, TxDD

Transmit Data

Inputs

Transmit Data inputs from External SCC channels C and D.

RxDC, RxDD

Receive Data

Outputs

Receive Data inputs to External SCC channels C and D.

RTxCC#, RTxCD#

Receive/Transmit Clocks

Outputs

Receive / Transmit Clocks for External SCC channels C and D.

3.3.5.3 SBP System Interface

CE2#

Circuit Enable

Input

Circuit Enable for the SBP Interface subsection (active low). This signal selects the SBP Interface for a read or write operation.

3.3.6 8-Bit Host System Interface

DATAB<7-0> Data Bus Input/Output/3-state ESCC: These lines carry data and commands to and from the ESCC.

SBP: This bus is used to transfer parallel data between the SBP Interface

internal data buffers, as well as the command/status register.

RD8# Read Control Signal Input

ESCC: This signal indicates a read operation. During the Interrupt Acknowledge

cycle, this signal gates the interrupt vector onto the bus if the ESCC is the

highest priority device requesting an interrupt.

SBP: This signal enables the data inside the SBP Interface internal registers to

be read through the DATAB bus.

WR8# Write Control Signal Input

ESCC: When the ESCC is selected, this signal indicates a write operation. The

coincidence of RD8# and WR8# is interpreted as a reset.

SBP: This signal enables data on the DATAB bus to be written into the SBP

Interface internal data registers, as well as the command/status register.

A/B# Input

ESCC: Channel A/ Channel B Select. This signal selects the channel in which the

read or write operation occurs.

SBP: This signal, in conjunction with D/C#, RD8# and WR8#, selectively

access the internal registers inside the SBP Interface subsection.

D/C# Input

ESCC: Data/Control Select. This signal defines the type of information

transferred to or from the ESCC. A HIGH means data is transferred; a LOW

indicates a command.

SBP: This signal, in conjunction with A/B#, RD8# and WR8#, selectively

access the internal registers inside the SBP Interface subsection.

INTACK# Input

ESCC: Interrupt Acknowledge (active low). This signal indicates an active

Interrupt Acknowledge cycle. When RD8# becomes active, the ESCC places an interrupt vector on the data bus. INTACK# is latched by the

rising edge of PCLK.

SBP: Not Applicable

PCLK 8-bit Subsection System Clock Input

E/N# Extended Address Line Input

ESCC: When this pin is LOW, all internal ESCC registers are accessible. When

this pin is HIGH, only the VERSION register and the LocalTalk/Extended FIFO enhancement register are accessible to the user. The address and

definition of these registers are as follows:

VERSION register: It is located at address 3 of the enhanced address space. i.e., in order to access the VERSION register WR0 should contain the

following 8 bit [7:0] code: "xxxx0011" and the E/N# line should be driven HIGH. (D/C# pin should be driven LOW.)

The content of the CURIO VERSION register follows the format: VERSION [7:0] = [11 x x x x x x x]; the lower 6 bits are used to indicate the rev ID of this CURIO circuit.

Write accesses to this register are IGNORED.

The LocalTalk/Extended FIFO enhancement register is located at address 2 of the enhanced address space. i.e., in order to access this register WR0 should contain the following 8 bit [7:0] code: "xxxx0010" and the E/N# pin should be driven HIGH. ( D/C# pin should be driven LOW). Both write and read accesses are recognized.

If the E/N# pin is driven HIGH, accesses to locations 0,1,4-15 are NOT permitted and will be read as zeros. (These locations are reserved for future extensions).

#### 3.3.7 IEEE P1149.1 TAP Interface

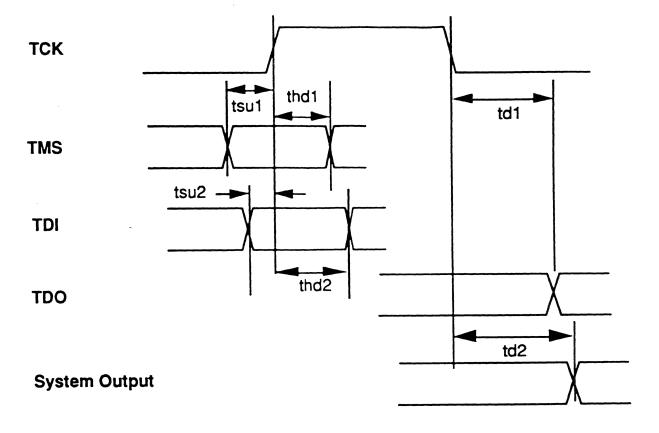

TCK

Test Clock

Input

The clock input for the boundary scan test mode operation. TCK can operate from 1MHz to 10MHz.

**TMS**

Test Mode Select

Input

A serial input bit stream used to define the specific boundary scan test to be executed. The TMS input is sampled at the rising edge of TCK. This signal is internally pull-up through a 100Kohm resistor to Vcc.

TDI

Test Data Input

Input

The test data input path to the CURIO. Data is sampled at the rising edge of TCK.

M

Test Data Out

Output

The test data output path from the CURIO. The TDO data output changes at the falling edge of TCK.

TRST#

Test Reset

Input

Assertion of TRST# causes the IEEE P1149.1 TAP to be reset. This signal is internally pulled-up through a 100Kohm resistor to Vcc.

3.3.8 General Interface

XTAL1/XTAL2 Crystal Input Input

The crystal frequency determines the network data rate. The network data rate is one-half of the crystal frequency. XTAL1 may alternatively be driven using an external TTL level source, in which case XTAL2 must be left unconnected.

XCLK Crystal Clock Output

XCLK is derived from the crystal oscillator. The frequency of XCLK is equal to the crystal or XTAL1 frequency.

#### 3.4 MACE FUNCTIONAL DESCRIPTION

The MACE can be connected to an 802.3 network via one of three network interfaces. The Attachment Unit Interface (AUI) provides an IEEE compliant differential interface to a remote MAU or an on-board transceiver. The Digital Attachment Interface™ (DAI™) can connect to local transceiver devices for 10BASE2, 10BASE-T or 10BASE-F connections. Additionally, a General Purpose Serial Interface (GPSI) is supported, which effectively bypasses the integrated Manchester encoder/decoder, and allows direct access to/from the integral 802.3 Media Access Controller (MAC) to provide support for external encoding/decoding schemes. The interface in use is determined by the PORTSEL [1-0] bits in the PLS Configuration Control register.

Designed with a slave type interface, the MACE circuit is intended to function as a standalone peripheral device to the host CPU, a DMA controller or an intelligent I/O processor. From the software stand point, it operates as a data conduit to and from the 802.3 network through register based function programming and interrupt driven event handling. The internal MAC controller executes the CSMA/CD communication algorithm without host intervention.

#### 3.4.1 BASIC MACE FUNCTIONS

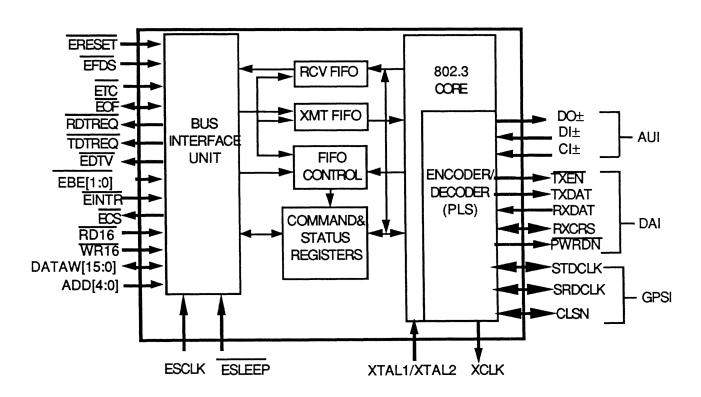

#### MACE BLOCK DIAGRAM

Figure A.1

#### 3.4.1.1 Network Interfaces

The MACE subsection can be connected to an 802.3 network via one of two network interfaces. The Attachment Unit Interface (AUI) provides an IEEE compliant differential interface to a remote MAU or an on-board transceiver. The Digital Attachment Interface™ (DAI™) can connect to local transceiver devices for 10BASE2, 10BASE-T or 10BASE-F connections. The interface in use is determined by the PORTSEL [1-0] bits in the PLS Configuration Control register.

#### 3.4.1.2 System Interface

The MACE is a register based peripheral. All transfers to and from the device, including data, are performed using a simple memory or I/O read or write commands. Access to all registers, including the transmit and receive FIFOs, is performed with identical read or write timing. All information on the system interface is synchronous to the system clock (ESCLK), which allows simple external logic to be designed to interrogate the device status and control the network data flow.

The receive and transmit FIFOs can be read or written by driving the appropriate address lines and asserting ECS# and RD16# or WR16# as appropriate. An alternative FIFO access mechanism allows use of the EFDS# and the RD16# or WR16# lines, without attention to the address lines (ADD<sub>4-0</sub>). The state of the RD16#, WR16# lines in conjunction with the EFDS# input determines whether the receive FIFO is read (RD16# low) or the transmit FIFO written (WR16# low). The MACE system interface permits interleaved transmit and receive bus transfers to take place, allowing the transmit FIFO to be filled ("primed") while a frame is being received from the network and/or read from the receive FIFO.

In receive operation, the MACE asserts Receive Data Transfer Request (RDTREQ#) when the FIFO contains adequate data. For the first indication of a new receive frame, 64 bytes must be received, assuming normal operation. Once the initial 64 byte threshold has been reached, RDTREQ# assertion and de-assertion is dependent on the programming of the Receive FIFO Watermark (RCVFW bits in the BIU Configuration Control register). The RDTREQ# can be programmed to activate when there are 16, 32 or 64 bytes of data available in the FIFO. Enable Receive (ENRCV bit in MAC Configuration Control register) must be set to assert RDTREQ#. If the Runt Packet Accept feature is invoked (RPA bit in User Test Register), RDTREQ# will be asserted for receive frames of less that 64 bytes on the basis of internal and/or external address match only. When RPA is set, RDTREQ# will be asserted when the entire frame has been received or when the initial 64 byte threshold has been exceeded.

Note that the receive FIFO may not contain 64 data bytes at the time RDTREQ# is asserted, if the automatic pad stripping feature has been enabled (ASTRP RCV bit in the Receive Frame Control register) and a minimum length packet with pad is received. The MACE will check for the minimum received length from the network, strip the pad characters, and pass only the data frame through the receive FIFO.

In transmit operation, the MACE asserts Transmit Data Transfer Request (TDTREQ#) dependent on the programming of the Transmit FIFO Watermark (XMTFW bits in the BIU Configuration Control register). TDTREQ# will be permanently asserted when the transmit FIFO is empty. The TDTREQ# can be programmed to activate when there are 16, 32 or 64 bytes of space available in the transmit FIFO. Enable Transmit (ENXMT bit in MAC Configuration Control register) must

be set to assert TDTREQ#. Write cycles to the Transmit FIFO will not return EDTV# if ENXMT is disabled, and no data will be written. The MACE will commence the preamble sequence once the Transmit Start Point (XMTSP bits in BIU Configuration Control register) threshold is reached in the transmit FIFO.

The transmit FIFO data will not be overwritten until at least 512 data bits have been transmitted onto the network. If a collision occurs within the slot time (512 bit time) window, the MACE will generate a jam sequence before ceasing the transmission, the transmit FIFO will be reset to point at the start of the transmit data field, and the message will be retried after the random back-off interval has expired.

#### 3.4.2 Detailed MACE Functions

#### 3.4.2.1 Bus Interface Unit (BIU)

The BIU performs the interface between the host or system bus and the Transmit and Receive FIFOs, as well as all on board control and status registers. The BIU can be configured to accept data presented in either little-endian or big-endian format, minimizing the external logic required to access the MACE integral FIFOs and registers. In addition, the BIU directly supports 8-bit transfers and incorporates features to simplify interfacing to 32-bit systems using external latches.

Externally, the FIFOs appear as two independent registers located at individual addresses. The remainder of the internal registers occupy 30 additional addresses consecutively, and appear as 8-bits wide.