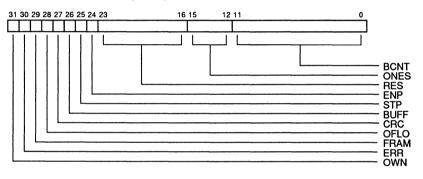

1992 World Network Data Book/Handbok

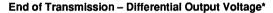

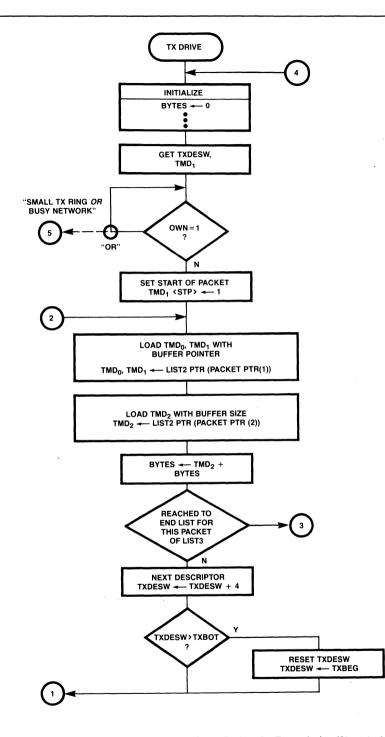

Advanced Micro Devices

# **Ethernet/IEEE 802.3 Family**

1992 World Network Data Book/Handbook

ADVANCED MICRO DEVICES 🗖

#### © 1992 Advanced Micro Devices, Inc.

#### Advanced Micro Devices reserves the right to make changes in its products without notice in order to improve design or performance characteristics.

This publication neither states nor implies any warranty of any kind, including but not limited to implied warrants of merchantability or fitness for a particular application. AMD assumes no responsibility for the use of any circuitry other than the circuitry in an AMD product.

The information in this publication is believed to be accurate in all respects at the time of publication, but is subject to change without notice. AMD assumes no responsibility for any errors or omissions, and disclaims responsibility for any consequences resulting from the use of the information included herein. Additionally, AMD assumes no responsibility for the functioning of undescribed features or parameters.

#### Trademarks

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

DAI, EADI, Integrated Local Area Communications Controller, ILACC are trademarks and PAL and SKINNYDIP are registered trademarks of Advanced Micro Devices, Inc.

Ethernet is a registered trademark of Xerox Corporation.

IBM PC/AT is a registered trademark of International Business Machines Corporation.

Macintosh II is a registered trademark of Apple Computer, Inc.

NetWare is a registered trademark of Novell, Inc.

NuBus is a trademark of Texas Instruments, Inc.

This publication provides the complete specifications for the semiconductors needed in designing 10BASE5, 10BASE2 or 10BASE-T IEEE 802.3/Ethernet network products.

It replaces the book we published less than twelve months ago. This quick cycle represents many exciting factors:

- AMD's continued introduction of new and next generation Ethernet products.

- Rapid adoption of compliant controller, physical layer and hub products.

- The accelerated pace of product introductions due to the diversity of the world market.

To those of you who have experience with our products, we are the advance guard in the increasing importance of sharing data. And, to you who are not familiar with our products, AMD's networking team welcomes the opportunity to share our newest specifications with you.

Remember our partnership helps you gain and keep the competitive edge. We are not your competition.

Robert M. Krueger Vice President, Networks Product Division

# TABLE OF CONTENTS

| Introductio | n                       | vii |

|-------------|-------------------------|-----|

| Section 1   | Product Data Sheets     | 1–1 |

| Section 2   | Am7990 Technical Manual | 2–1 |

| Section 3   | Applications            | 3–1 |

| Section 4   | Development Tools       | 4–1 |

| Section 5   | Physical Dimensions     | 5–1 |

· ·

# INTRODUCTION

Advanced Micro Devices was the first company in the industry to offer a complete 802.3/Ethernet chip set in 1985. Today, AMD is a leading supplier of integrated circuits to the local area network and the wide area network marketplace. Our total portfolio includes products for 802.3/Ethernet, Fiber Distributed Data Interface (FDDI), ESCON, Fiber Channel and ISDN applications. This rich mix of products reflects AMD's commitment to your needs and insures leadership in this exciting marketplace.

This handbook includes a complete offering of solutions for the systems architect/designer of 802.3/Ethernet local area network (LAN) applications.

#### AMD Value Proposition

AMD provides products that accelerate your products' time-to-market.

Our products are supported with software and board level solutions to accelerate the design cycle. A great emphasis is placed on standards compliance, interoperability testing and systems verification of our integrated circuits.

Many of AMD's products result from joint development programs with premier networking systems corporations. This ensures optimal product definition and system verification. Examples of joint development efforts include Digital Equipment Corporation, Hewlett-Packard Corporation, 3COM Corporation, and SynOptics Communications, Inc.

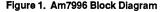

#### **Motherboards**

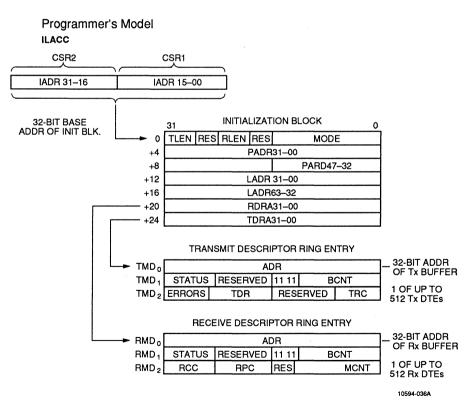

AMD is the leading supplier of 802.3/Ethernet ICs to the motherboard marketplace. This market includes engineering workstations and personal computer platforms. AMD offers solutions for both 16-bit and 32-bit microprocessor busses. The industry's most widely designed in Ethernet controller, the Am7990 LANCE, defined the industry preferred architecture for efficient software interface in high-performance applications. AMD's second generation Ethernet controller, the Am79C900 ILACC, offers an easy migration path to 32-bit applications. The ILACC has a higher level of integration and performance, while taking advantage of the existing software development investment. Software drivers written for the Am7909 LANCE can easily be converted to serve the Am79C900 ILACC.

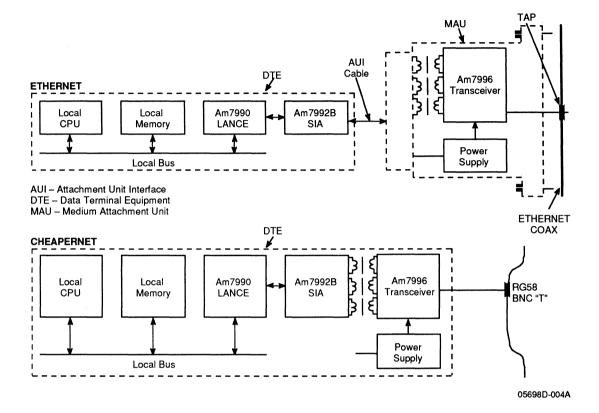

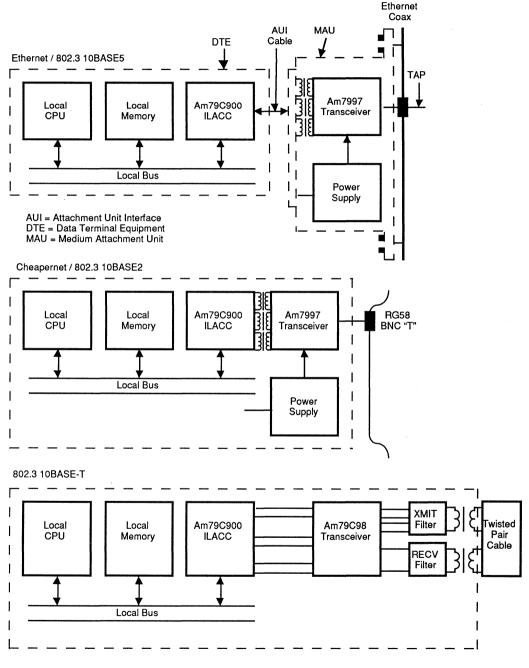

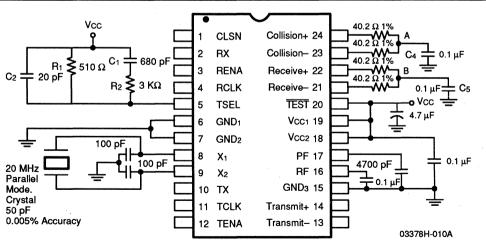

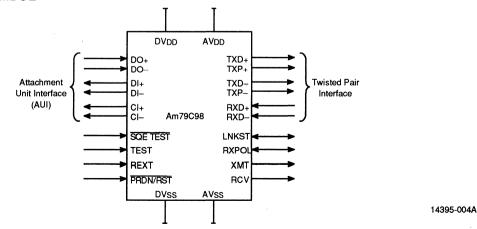

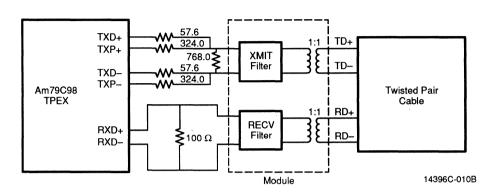

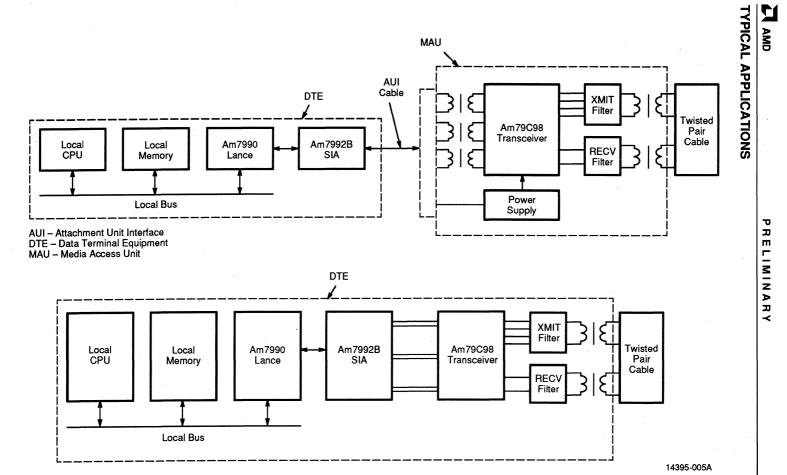

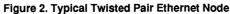

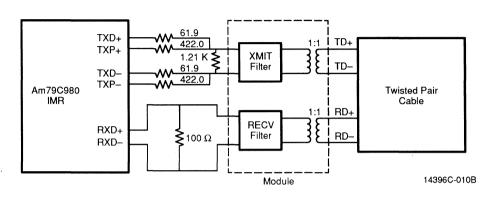

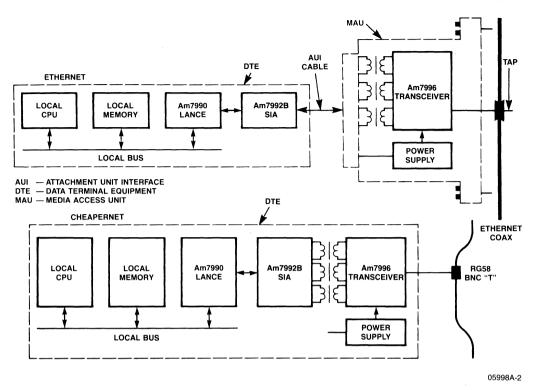

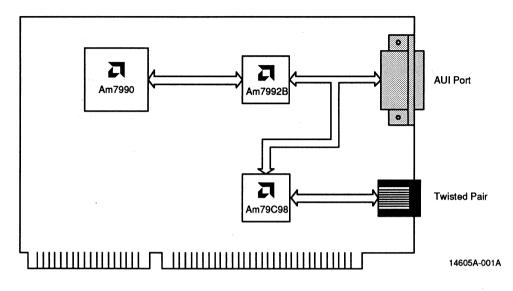

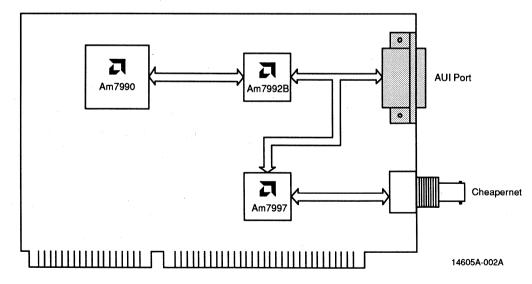

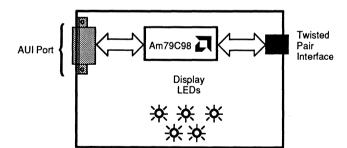

Complementing the controller offering are a Manchester encoder/decoder and several physical layer devices for either thick coax Ethernet/IEEE 802.3 (10BASE5), thin coax Cheapernet/IEEE 802.3 (10BASE2), or twisted pair Ethernet/IEEE 802.3 (10BASE-T). The Am79C98, Twisted Pair Ethernet Transceiver (TPEX), has a special power-down feature, sleep mode, optimal for PC laptop applications.

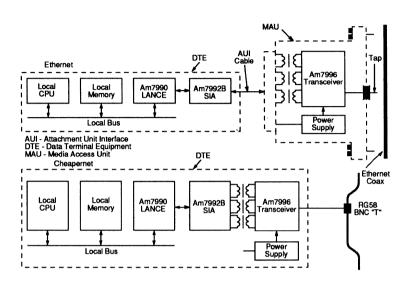

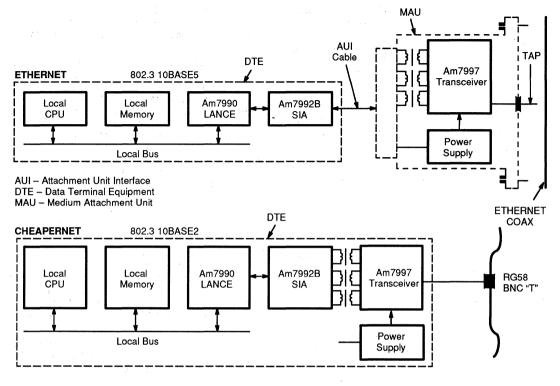

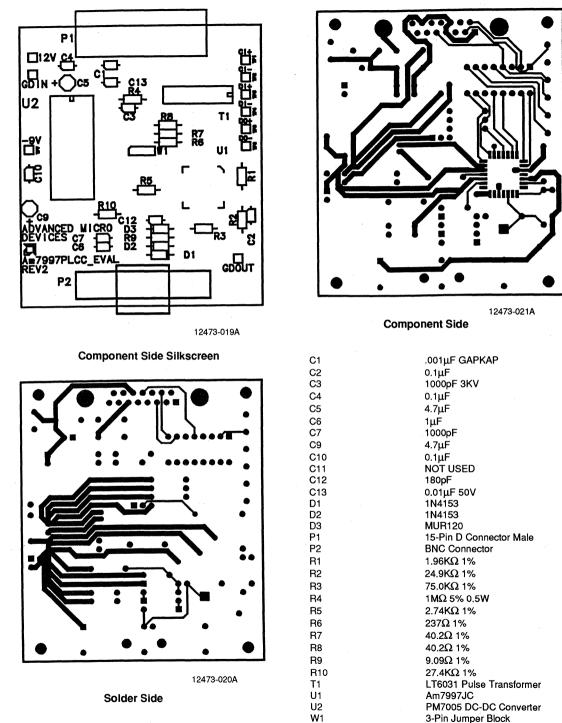

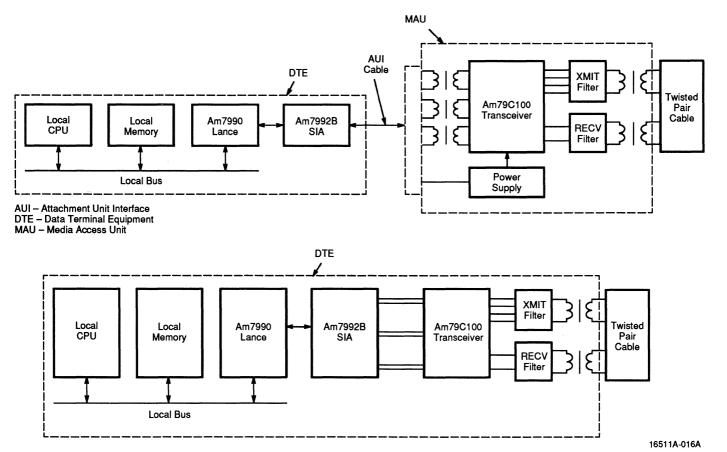

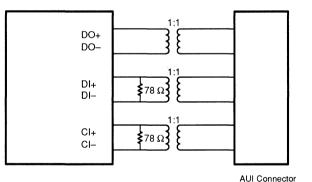

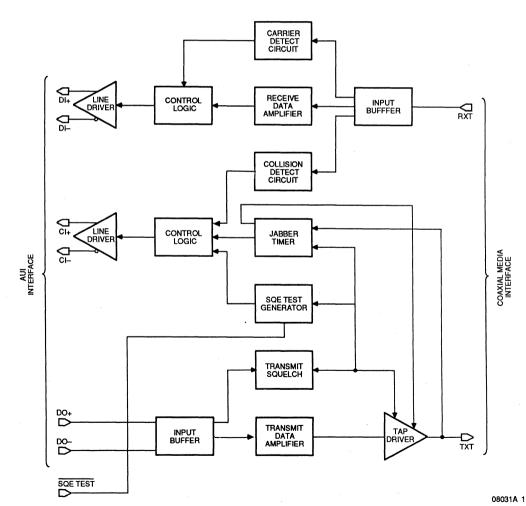

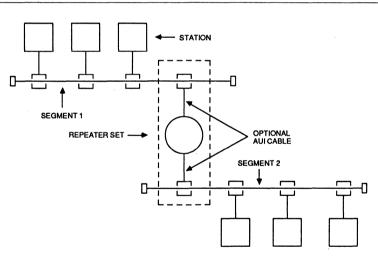

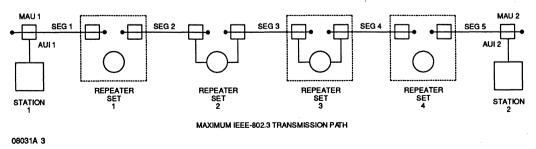

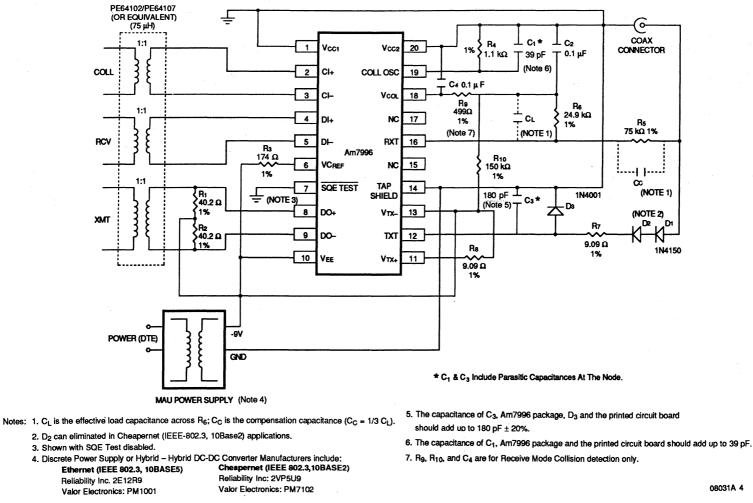

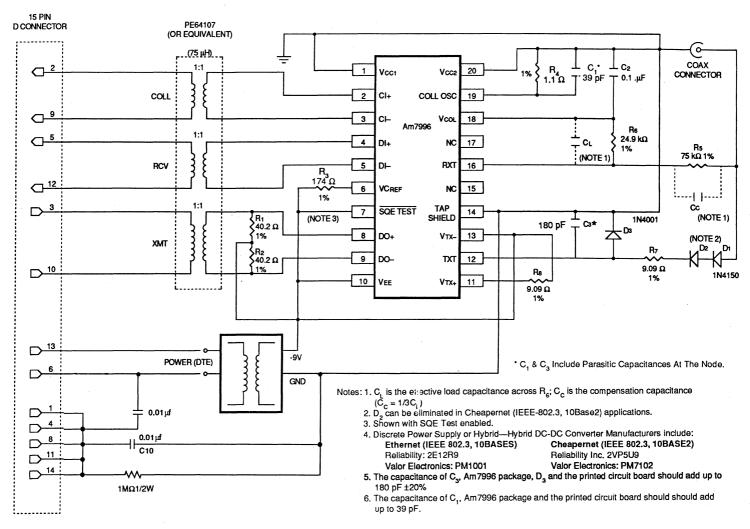

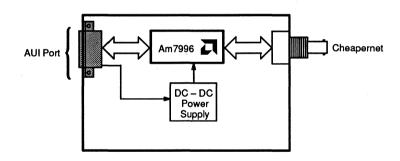

#### **Medium Attachment Units**

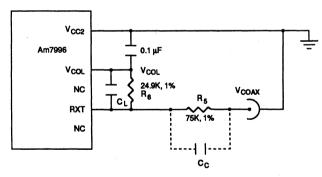

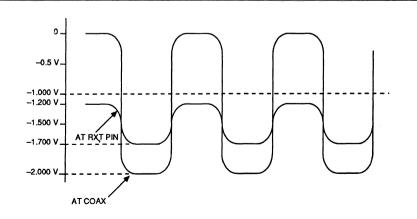

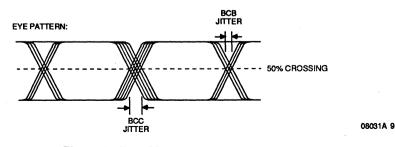

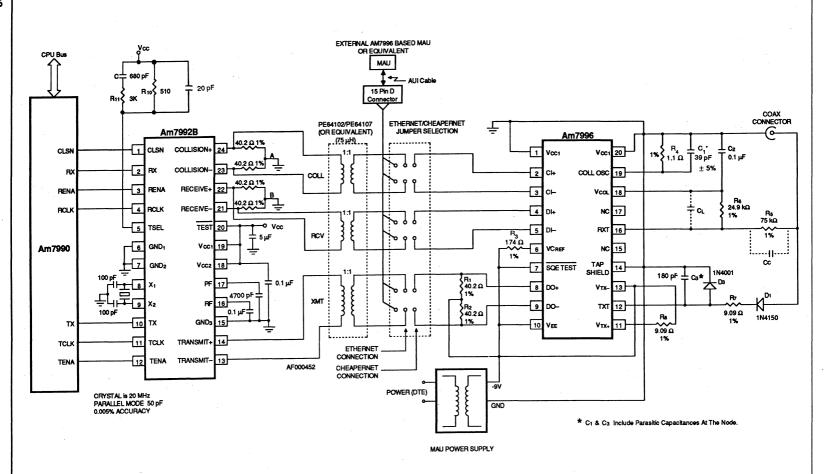

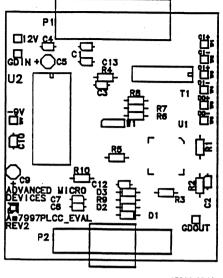

For medium attachment units (MAUs), also known as stand-alone transceivers, AMD offers two products. The original Ethernet/802.3 10BASE5 and 10BASE2 transceiver, the Am7996, is a proven industry solution used extensively in all markets. An evaluation board, the Am7996EVAL-HW, facilitates rapid design and production of Am7996 based MAUs.

The second device, the Am79C98 Twisted Pair Ethemet Transceiver (TPEX), is AMD's offering for the 802.3 10BASE-T market. The Am79C98 is a highly integrated device that allows for a very cost-effective LAN system implementation using 10BASE-T medium attachment units. The Am79C98 is also supported by a stand-alone evaluation board, the Am79C98EVAL-HW, to speed progress along the learning curve.

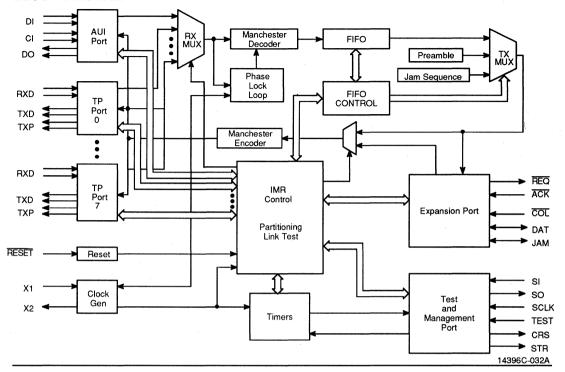

#### Multiport Repeaters

Multiport repeaters, hubs and concentrators have been used in the industry for many years in coaxial cable networks. With the emergence of 10BASE-T and its structured cabling system or physical star configuration, the multiport repeater has become an essential part of a local area network. Without a 10BASE-T multiport repeater there is no 10BASE-T network.

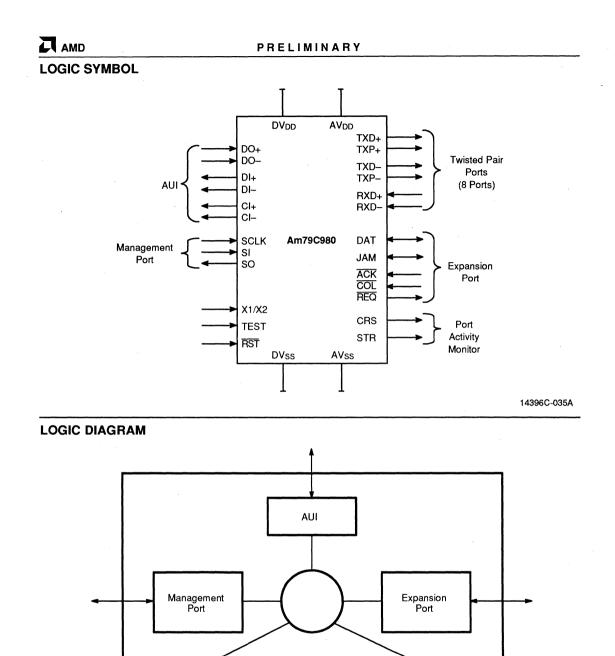

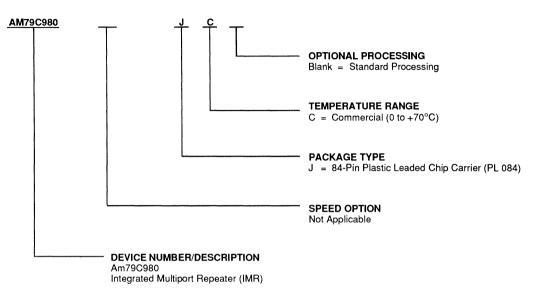

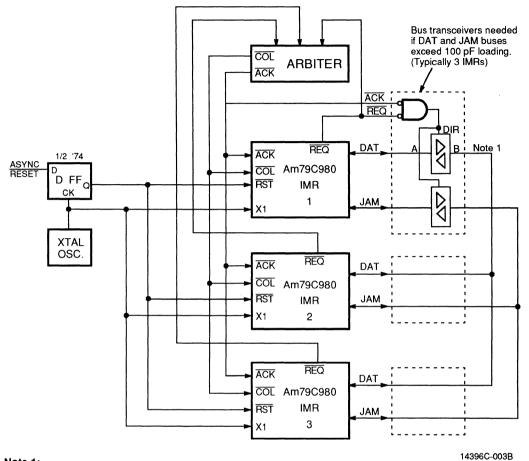

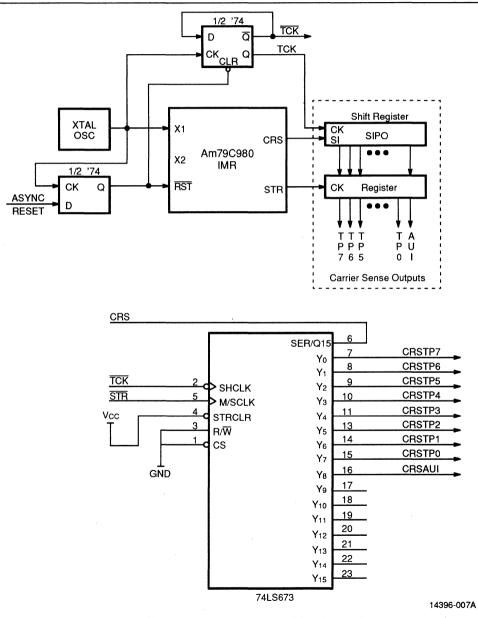

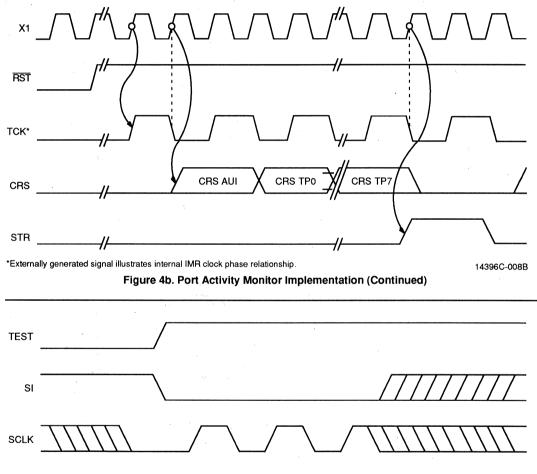

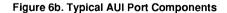

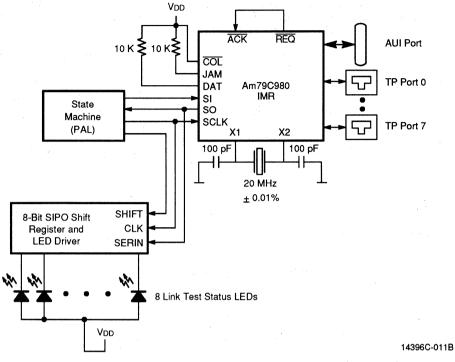

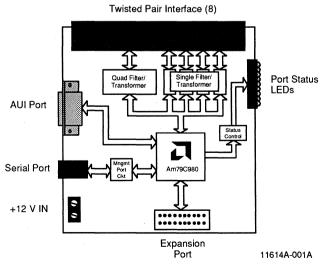

The principal value of a 10BASE-T local area network is that it allows the network manager to build, reconfigure and maintain a large and reliable network with a low-cost of ownership. To improve reliability, reduce system cost, and allow for effective LAN management in a 10BASE-T multiport repeater implementation, AMD has introduced the Am79C980 Integrated Multiport Repeater (IMR). This device allows the system designer to easily develop reliable, maintainable 10BASE-T multiport repeaters of various complexity and functionality. The Am79C980 is supported by the IMR-VELCRO-HW kit to facilitate rapid design and production of IMR based 10BASE-T hubs.

#### PC Add-on cards

AMD's family of Ethernet controllers and transceivers are well suited for high performance add-on card applications.

In 1989, AMD developed the industry's first bus master PC add-on card for the IBM PC/AT<sup>™</sup> and compatibles. The AT half card, the LANCE-AT-KT, is supported with Novell NetWare<sup>™</sup> certified driver software and a development monitor/debug program. This board allows the system designer to easily evaluate the AMD devices. It also serves as a reference platform for product development of PC add-on card products.

Similarly, the 32-bit ILACC controller is supported by a 32-bit add-on card with a NU-bus<sup>™</sup> interface, the ILACC-MAC-KT, for the Apple Macintosh II family of computers.

# Л

# SECTION 1 Product Data Sheets

| Ethernet Controllers<br>Am7990 Local Area Network Controller for Ethernet (LANCE)                   |

|-----------------------------------------------------------------------------------------------------|

| Am79C900 Integrated Local Area Communications<br>Controller <sup>™</sup> (ILACC <sup>™</sup> ) 1–55 |

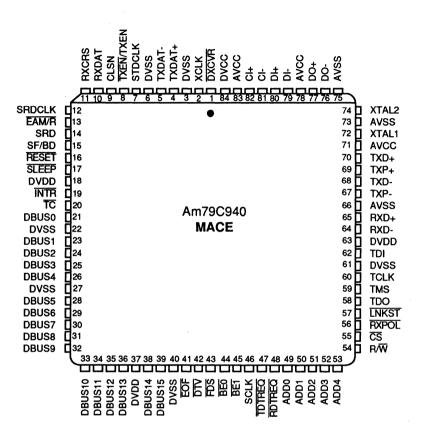

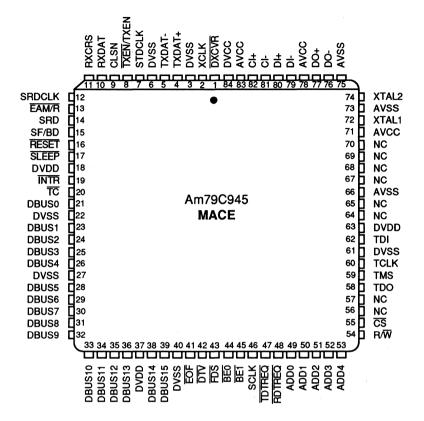

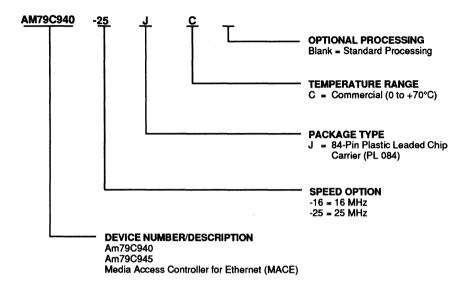

| Am79C940-16/25, Am79C945-16 Media Access Controller<br>for Ethernet (MACE)                          |

| Physical Layer<br>Am7992B Serial Interface Adapter (SIA)                                            |

| Am7996 IEEE 802.3/Ethernet/Cheapernet Transceiver                                                   |

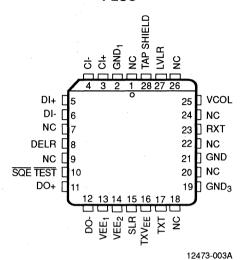

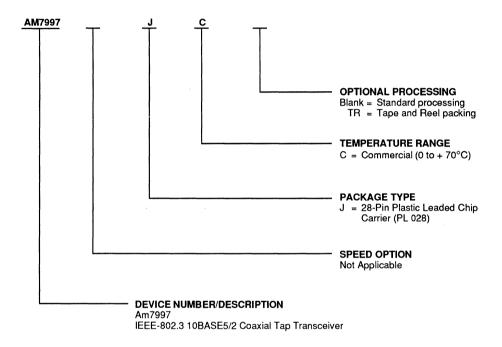

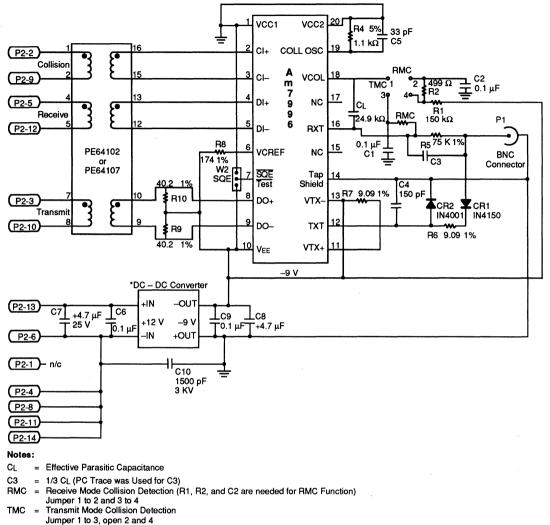

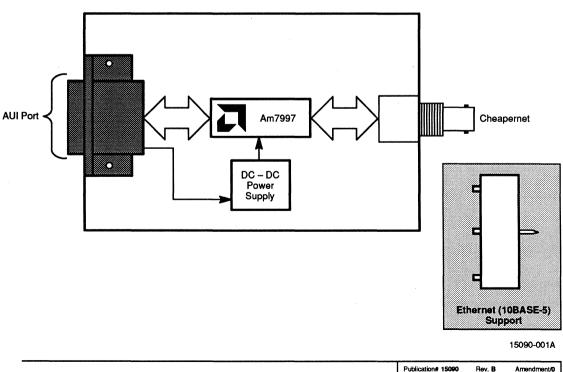

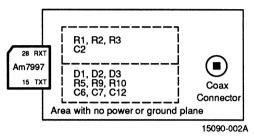

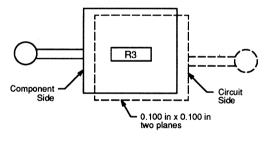

| Am7997 IEEE 802.3 10BASE5/2 Coaxial Tap Transceiver                                                 |

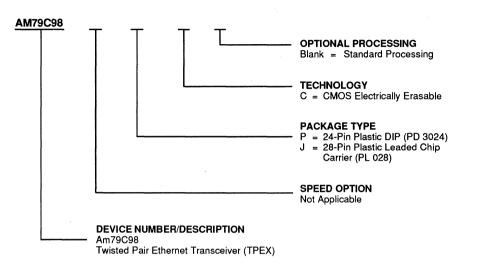

| Am79C98 Twisted Pair Ethernet Transceiver (TPEX)                                                    |

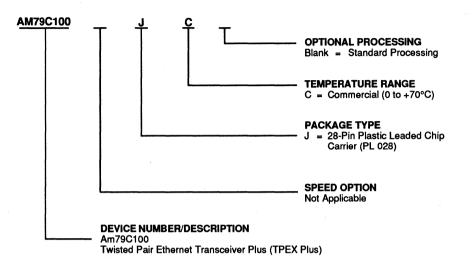

| Am79C100 Twisted Pair Ethernet Transceiver Plus (TPEX Plus) 1-207                                   |

| Hub Product<br>Am79C980 Integrated Multiport Repeater (IMR)                                         |

# Am7990

## Local Area Network Controller for Ethernet (LANCE)

## DISTINCTIVE CHARACTERISTICS

- Compatible with Ethernet and IEEE 802.3 10BASE 5 Type A, and 10BASE 2 Type B, "Cheapernet"

- Easily interfaced with 80x86, 680x0, Am29000, Z8000<sup>™</sup>, LSI-II<sup>™</sup> microprocessors

- On-board DMA and buffer management, 48 byte FIFO

- 24-bit wide linear addressing (Bus Master Mode)

## **GENERAL DESCRIPTION**

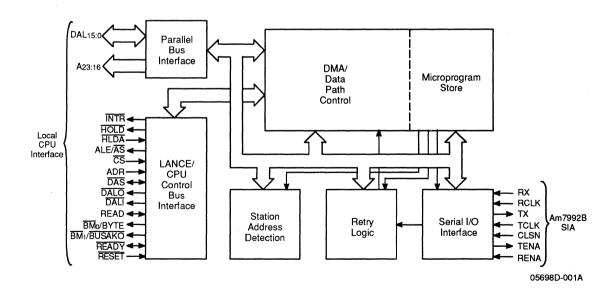

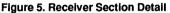

The Am7990 Local Area Network Controller for Ethernet (LANCE) is a 48-pin VLSI device designed to greatly simplify interfacing a microcomputer or minicomputer to an IEEE 802.3/Ethernet Local Area Network. The LANCE, in conjunction with the Am7992B Serial Interface Adapter (SIA), Am7996, Am7997 or Am79C98 Transceiver, and closely coupled local memory and mi-

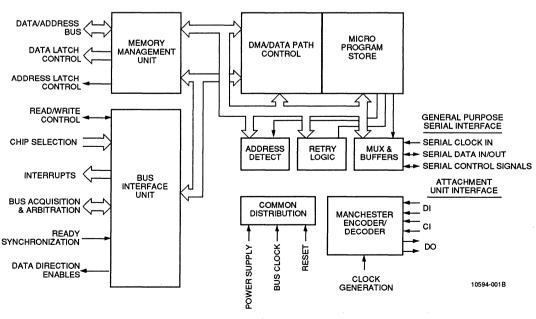

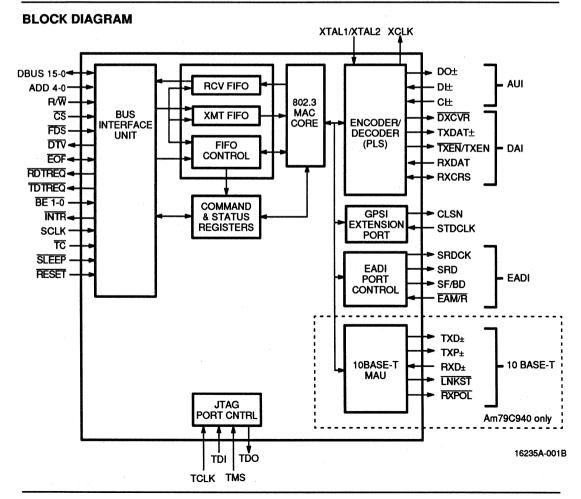

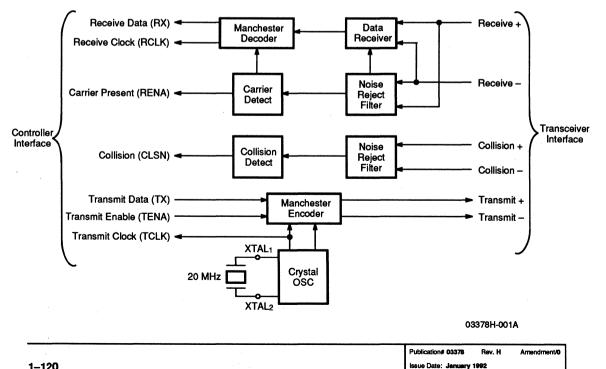

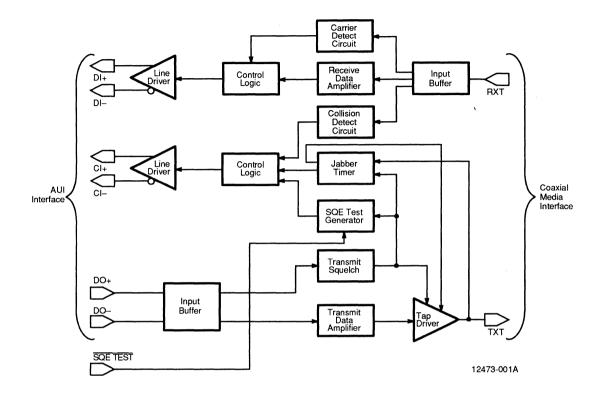

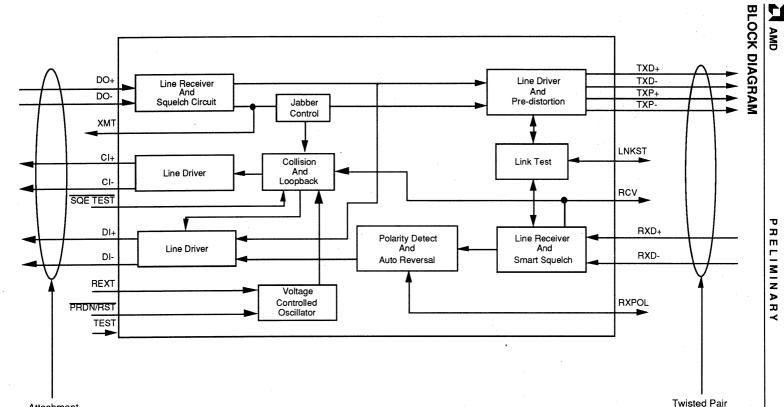

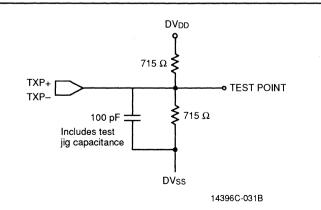

## **BLOCK DIAGRAM**

Network and packet error reporting

Back-to-back packet reception with as little as 4.1 µsec interpacket gap time

Advanced Micro

Devices

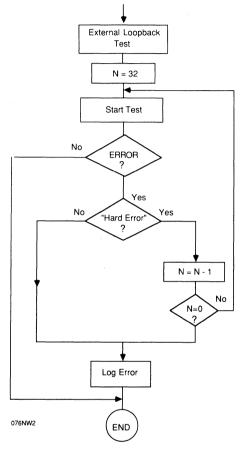

- Diagnostic Routines

- Internal/external loop back

- CRC logic check

- Time domain reflectometer

croprocessor, is intended to provide the user with a complete interface module for an Ethernet network. The Am7990 is designed using a scaled NMOS technology and is compatible with a variety of microprocessors. Onboard DMA, advanced buffer management, and extensive error reporting and diagnostics facilitate design and improve system performance.

## **RELATED AMD PRODUCTS**

| Part No. | Description                                     |

|----------|-------------------------------------------------|

| Am7992B  | Serial Interface Adaptor (SIA)                  |

| Am7996   | IEEE 802.3/Ethernet/Cheapernet Transceiver      |

| Am79C900 | Integrated Local Area Communications Controller |

| Am79C98  | Twisted Pair Ethernet Transceiver               |

| Am79C980 | Integrated Multiport Repeater                   |

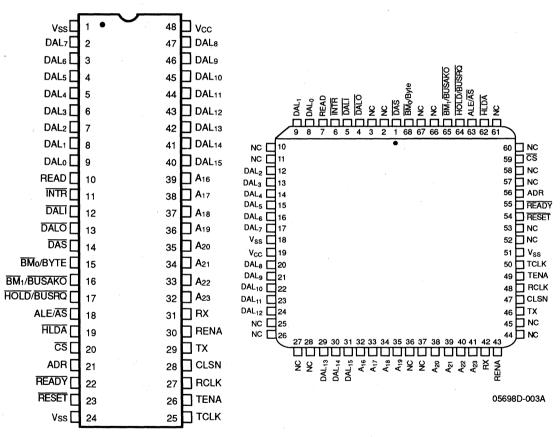

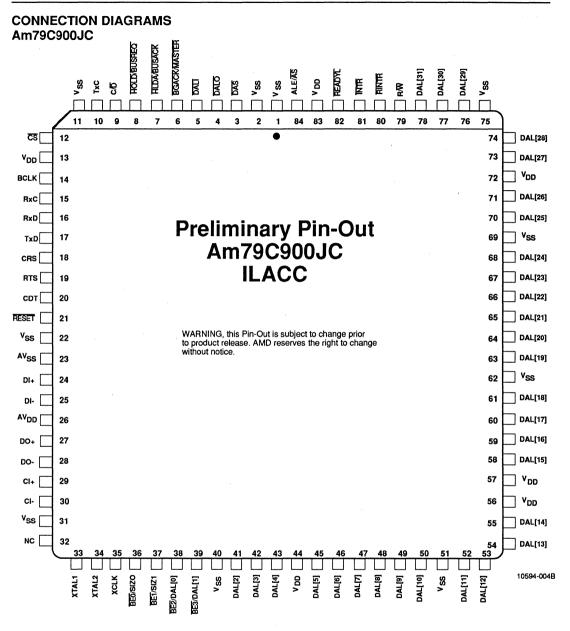

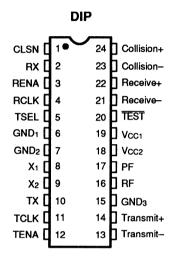

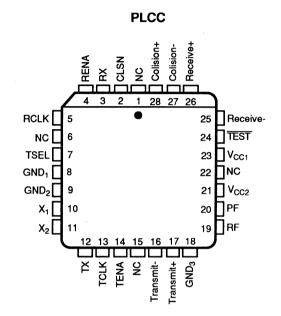

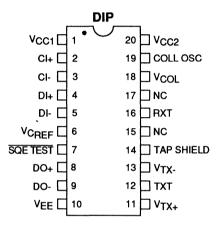

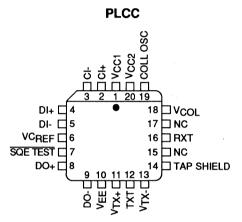

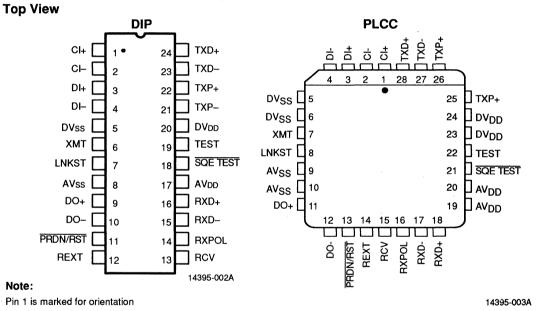

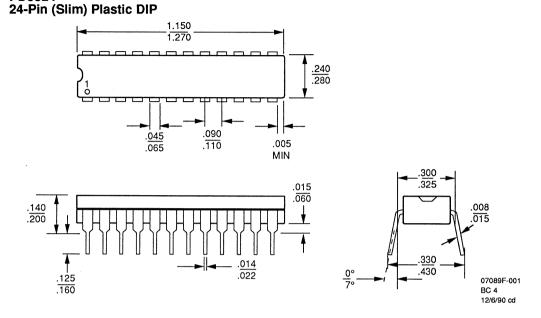

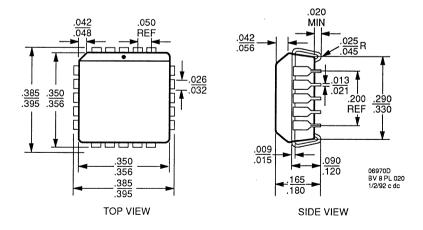

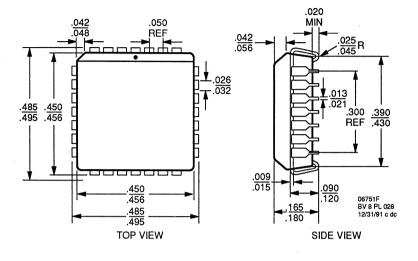

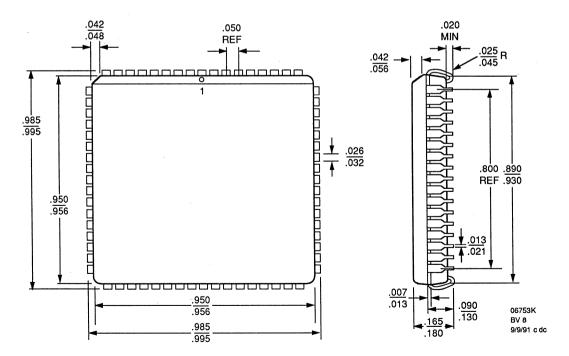

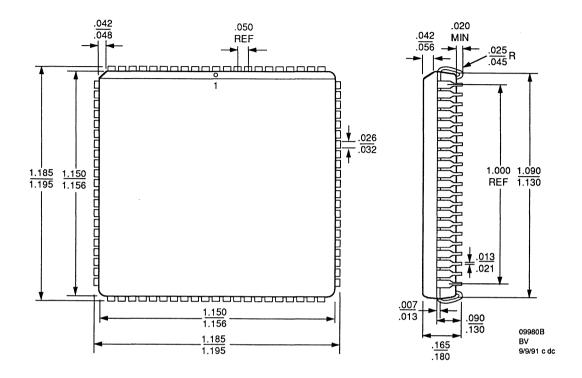

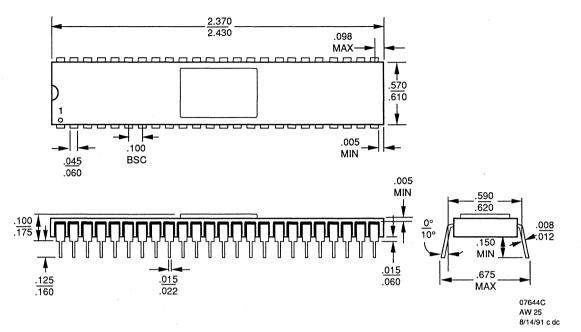

## **CONNECTION DIAGRAMS**

#### Note:

Pin 1 is marked for orientation.

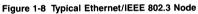

## **TYPICAL ETHERNET/CHEAPERNET NODE**

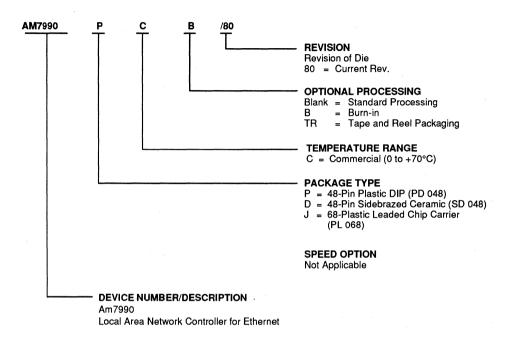

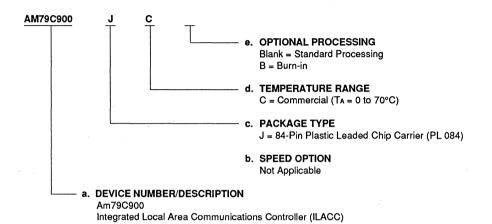

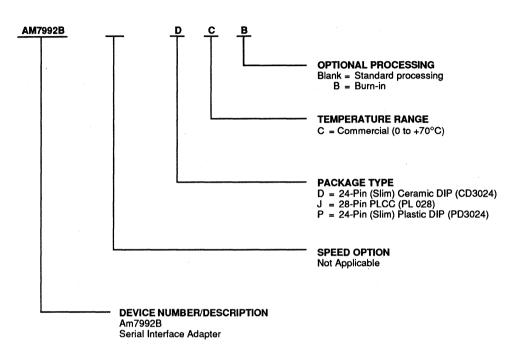

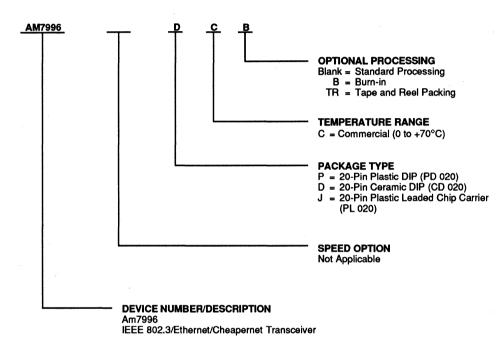

## ORDERING INFORMATION Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the following:

| Valid Combinations |                                  |     |  |  |  |

|--------------------|----------------------------------|-----|--|--|--|

| AM7990             | DC, DCB,<br>PC, PCB,<br>JC, JCTR | /80 |  |  |  |

#### Valid Combinations

The Valid Combinations table lists configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations, to check on newly released combinations, and to obtain additional data on AMD's standard military grade products.

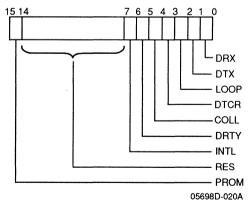

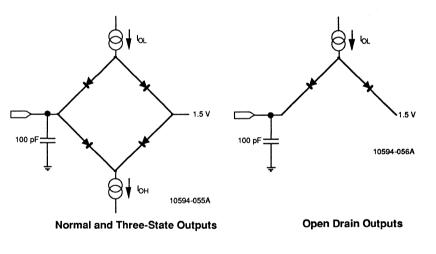

## **PIN DESCRIPTION**

#### A16 - A23

#### High Order Address Bus (Output Three State)

Additional address bits to access a 24-bit address. These lines are driven as a Bus Master only.

## ADR

#### **Register Address Port Select (Input)**

When LANCE is slave, ADR indicates which of the two register ports is selected. ADR LOW selects register data port; ADR HIGH selects register address port. ADR must be valid throughout the data portion of the bus cycle and is only used by the LANCE when CS is LOW.

## ALE/AS

#### Address Latch Enable (Output, Three-State)

Used to demultiplex the DAL lines and define the address portion of the bus cycle. This I/O pin is programmable through bit (01) of CSR<sub>3</sub>.

As ALE (CSR<sub>3</sub> (01), ACON = 0), the signal transitions from a HIGH to a LOW during the address portion of the transfer and remains LOW during the data portion. ALE can be used by a Slave device to control a latch on the bus address lines. When ALE is HIGH, the latch is open, and when ALE goes LOW, the latch Is closed.

As  $\overline{AS}$  (CSR<sub>3</sub> (01), ACON = 1), the signal pulses LOW during the address portion of the bus transaction. The LOW-to-HIGH transition of  $\overline{AS}$  can be used by a Slave device to strobe the address into a register.

The LANCE drives the ALE/ $\overline{\text{AS}}$  line only as a Bus Master.

## BM0/BYTE, BM1/BUSAKO

#### (Output, Three-state)

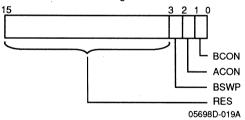

The two pins are programmable through bit (00) of CSR3

$\overline{BM}_0$ ,  $\overline{BM}_1$  — If CSR<sub>3</sub> (00) BCON = 0 PIN 15 =  $\overline{BM}_0$  (Output Three-state) (48-Pin DIPs) PIN 16 =  $\overline{BM}_1$  (Output Three-state) (48-Pin DIPs)

$\overline{BM}_0$ ,  $\overline{BM}_1$  (Byte Mask). This indicates the byte(s) on the DAL are to be read or written during this bus transaction. The LANCE drives these lines only as a Bus Master. It ignores the Byte Mask lines when it is a Bus Slave and assumes word transfers.

Byte selection using Byte Mask is done as described by the following table.

| BM <sub>1</sub> | <b>BM</b> <sub>0</sub> |            |

|-----------------|------------------------|------------|

| LOW             | LOW                    | Whole Word |

| LOW             | HIGH                   | Upper Byte |

| HIGH            | LOW                    | Lower Byte |

| HIGH            | HIGH                   | None       |

Byte selection may also be done using the BYTE line and DAL<sub>00</sub> line, latched during the address portion of the bus cycle. The LANCE drives BYTE only as a Bus Master and ignores it when a Bus Slave selection is done (similar to  $\overline{BM_0}$ ,  $\overline{BM_1}$ ).

Byte selection is done as outlined in the following table.

| BYTE | DALoo |                   |

|------|-------|-------------------|

| LOW  | LOW   | Whole Word        |

| LOW  | HIGH  | Illegal Condition |

| HIGH | LOW   | Lower Byte        |

| HIGH | HIGH  | Upper Byte        |

BUSAKO is a bus request daisy chain output. If the chip is not requesting the bus and it receives HLDA, BUSAKO will be driven LOW. If the LANCE is requesting the bus when it receives HLDA, BUSAKO will remain HIGH.

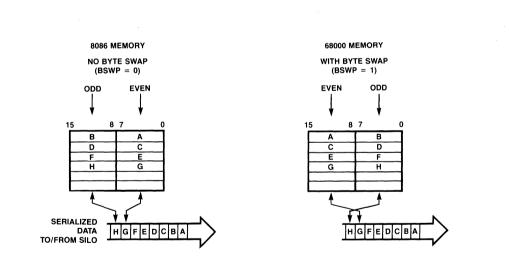

## **Byte Swapping**

In order to be compatible with the variety of 16-bit microprocessors available to the designer, the LANCE may be programmed to swap the position of the upper and lower order bytes on data involved in transfers with the internal FIFO.

Byte swapping is done when BSWP = 1. The most significant byte of the word in this case will appear on DAL lines 7-0 and the least significant byte on DAL lines 15-8.

When BYTE = H (indicating a byte transfer) the table indicates on which part of the 16-bit data bus the actual data will appear.

Whenever byte swap is activated, the only data that Is swapped is data traveling to and from the FIFO.

|                                                                 | Mode Bits                |                          |  |

|-----------------------------------------------------------------|--------------------------|--------------------------|--|

| Signal Line                                                     | BSWP = 0<br>and BCON = 1 | BSWP = 1<br>and BCON = 1 |  |

| BYTE = L and<br>DAL <sub>00</sub> = L                           | Word                     | Word                     |  |

| BYTE = L and<br>DAL <sub>00</sub> = H                           | Illegal                  | lllegal                  |  |

| $\begin{array}{l} BYTE=H \text{ and} \\ DAL_{00}=H \end{array}$ | Upper Byte               | Lower Byte               |  |

| BYTE = H and $DAL_{00} = L$                                     | Lower Byte               | Upper Byte               |  |

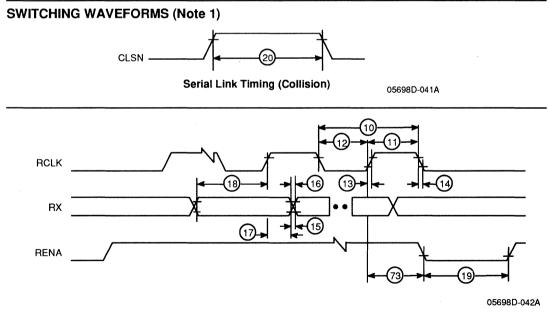

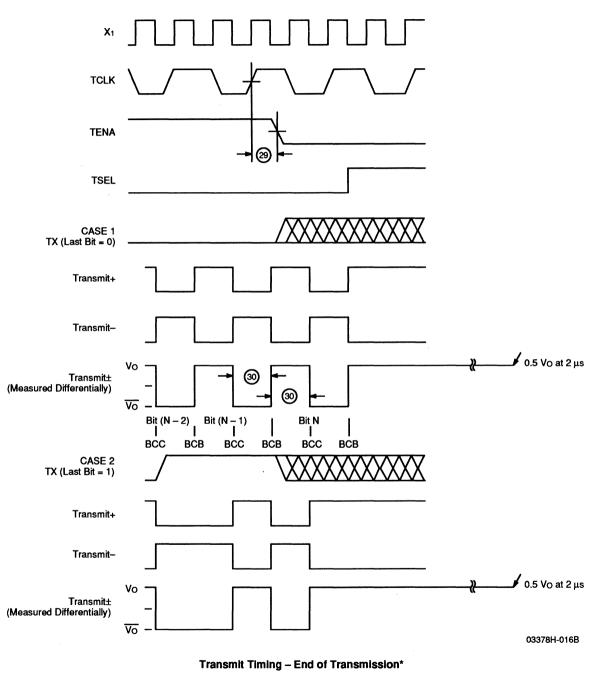

## CLSN

## Collision (Input)

A logical input that indicates that a collision is occurring on the channel.

## CS

#### Chip Select (Input)

Indicates, when asserted, that the LANCE is the slave device of the data transfer.  $\overline{CS}$  must be valid throughout the data portion of the bus cycle.  $\overline{CS}$  must not be asserted when  $\overline{HLDA}$  is LOW

## $DAL_{00} - DAL_{15}$

#### Data/Address Lines (Input/Output, Three-State)

The time multiplexed Address/Data bus. During the address portion of a memory transfer,  $DAL_{00} - DAL_{15}$  contains the lower 16 bits of the memory address. The upper 8 bits of address are contained in  $A_{16} - A_{23}$ .

During the data portion of a memory transfer,  $DAL_{00} - DAL_{15}$  contains the read or write data, depending on the type of transfer.

The LANCE drives these lines as a Bus Master and as a Bus Slave.

## DALI

## Data/Address Line In (Output, Three-State)

An external bus transceiver control line. DALI is asserted when the LANCE reads from the DAL lines. It will be LOW during the data portion of a READ transfer and remain HIGH for the entire transfer if it is a WRITE. DALI is driven only when LANCE is a Bus Master.

## DALO

## Data/Address Line Out (Output, Three-State)

An external bus transceiver control line. DALO is asserted when the LANCE drives the DAL lines. DALO will be LOW only during the address portion if the transfer is a READ. It will be LOW for the entire transfer if the transfer is a WRITE. DALO is driven only when LANCE is a Bus Master.

## DAS

#### Data Strobe (Input/Output, Three-State)

Defines the data portion of the bus transaction.  $\overline{\text{DAS}}$  is high during the address portion of a bus transaction and low during the data portion. The LOW-to-HIGH transition can be used by a Slave device to strobe bus data into a register.  $\overline{\text{DAS}}$  is driven only as a Bus Master.

## HLDA

#### **Bus Hold Acknowledge (Input)**

A response to HOLD. When HLDA is LOW in response to the chip's assertion of HOLD, the chip is the Bus Master.

During bus master operation the LANCE waits for <u>HLDA</u> to be deasserted 'HIGH' before reasserting HOLD 'LOW'. This insures proper bus handshake under all situations.

## HOLD/BUSRQ

#### Bus Hold Request (Output, Open Drain)

Asserted by the LANCE when it requires access to memory. HOLD is held LOW for the entire ensuing bus transaction. The function of this pin is programmed through bit (00) of CSR<sub>3</sub>. Bit (00) of CSR<sub>3</sub> is cleared when RESET is asserted.

When  $CSR_3$  (00) BCON = 0

PIN 17 = HOLD (Output Open Drain and input sense) (48-Pin DIPs)

When CSR<sub>3</sub> (00) BCON = 1

PIN 17 = BUSRQ (I/O Sense, Open Drain) (48-Pin DIPs)

If the LANCE wants to use the bus, it looks at HOLD/ BUSRQ; if it is HIGH the LANCE can pull it LOW and request the bus. If it is already LOW, the LANCE waits for it to go inactive-HIGH before requesting the bus.

## INTR

## Interrupt (Output, Open Drain)

An attention signal that indicates, when active, that one or more of the following  $CSR_0$  status flags is set: BABL, MERR, MISS, RINT, TINT or IDON. INTR is enabled by bit 06 of CSR0 (INEA = 1). INTR remains asserted until the source of Interrupt is removed.

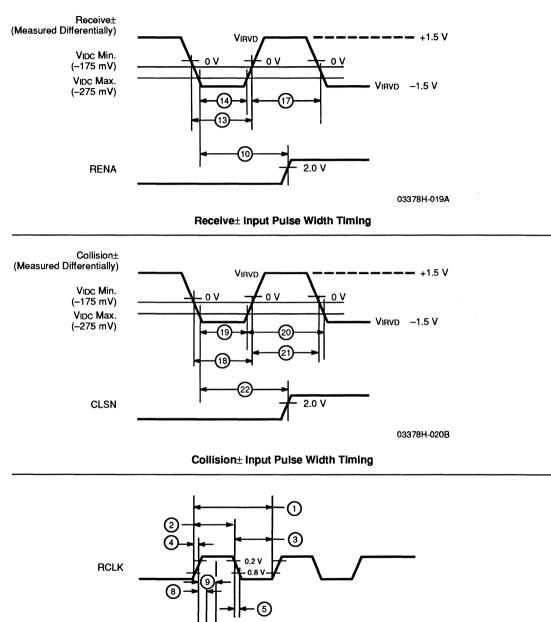

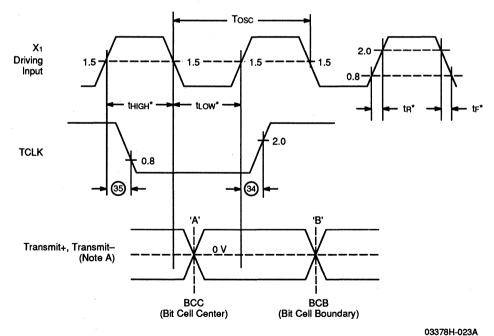

## RCLK

## Receive Clock (Input)

A 10 MHz square wave synchronized to the Receive data and only active while receiving an Input Bit Stream.

## READ

## (Input/Output, Three-State)

Indicates the type of operation to be performed in the current bus cycle. This signals an output when the LANCE is a Bus Master.

High - Data is taken off the DAL by the LANCE.

Low – Data is placed on the DAL by the LANCE.

The signal is an input when the LANCE is a Bus Slave.

- High Data is placed on the DAL by the LANCE.

- Low Data is taken off the DAL by the LANCE.

## READY

#### (Input/Output, Open Drain)

When the LANCE is a Bus Master, READY is an asynchronous acknowledgment from the bus memory that it will accept data in a WRITE cycle or that it has put data on the DAL lines in a READ cycle.

As a Bus Slave, the LANCE asserts READY when it has put data on the DAL lines during a READ cycle or is about to take data off the DAL lines during a write cycle. READY is a response to DAS and will return High after DAS has gone High. READY is an input when the LANCE is a Bus Master and an output when the LANCE is a Bus Slave.

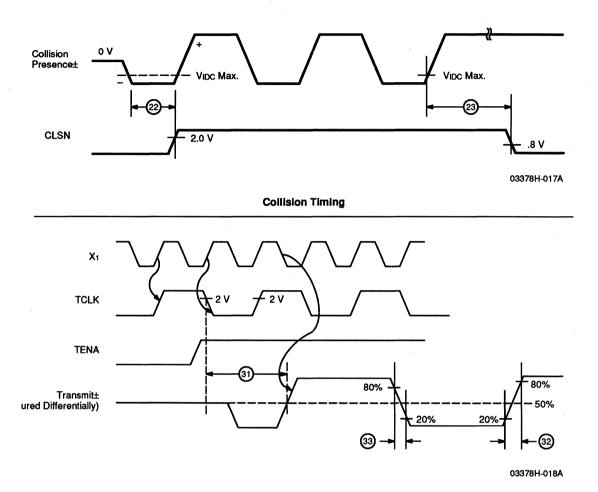

#### RENA

#### Receive Enable (Input)

A logical input that indicates the presence of carrier on the channel.

## RESET

#### Reset (Input)

Bus Request Signal. Causes the LANCE to cease operation, clear its internal logic, force all three-state buffers to the high impedance state, and enter an idle state with the stop bit of CSR<sub>0</sub> set. It is recommended that a 3.3 k $\Omega$  pullup resistor be connected to this pin.

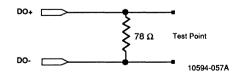

#### RX

#### Receive (Input)

Receive Input Bit Stream.

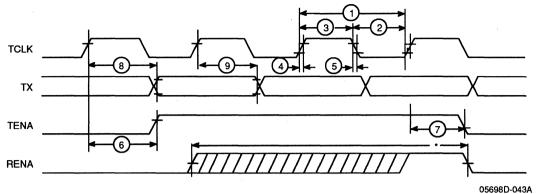

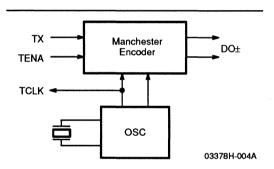

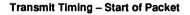

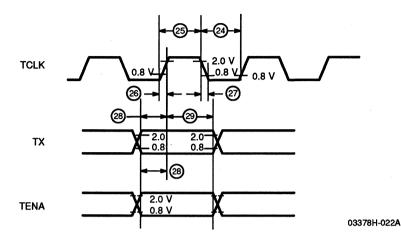

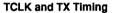

#### TCLK

#### Transmit Clock (Input)

10 MHz clock.

#### TENA

#### Transmit Enable (Output)

Transmit Output Bit Stream enable. When asserted, it enables valid transmit output (TX).

## ТΧ

## Transmit (Output)

Transmit Output Bit Stream.

#### Vcc

#### Power supply pin +5 volt ±5%

It is recommended that a 0.1  $\mu F$  and a 10  $\mu F$  decoupling capacitors be used between  $V_{CC}$  and  $V_{SS}.$

#### Vss

#### Ground

Pin 1 and 24 (48-Pin DIPs) should be connected together externally, as close to the chip as possible.

## FUNCTIONAL DESCRIPTION

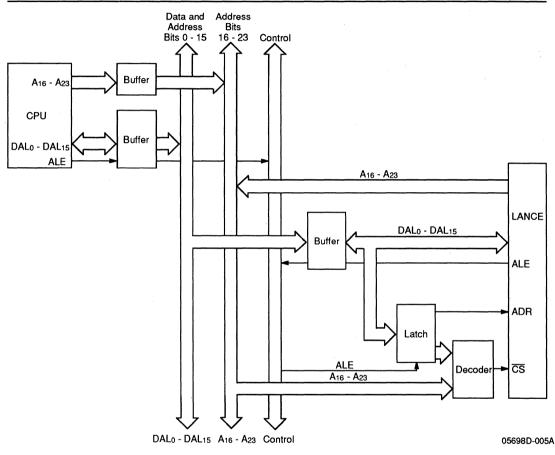

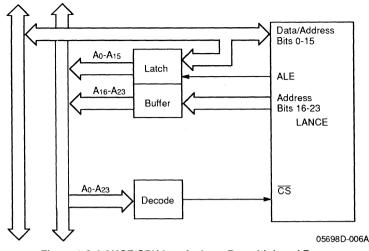

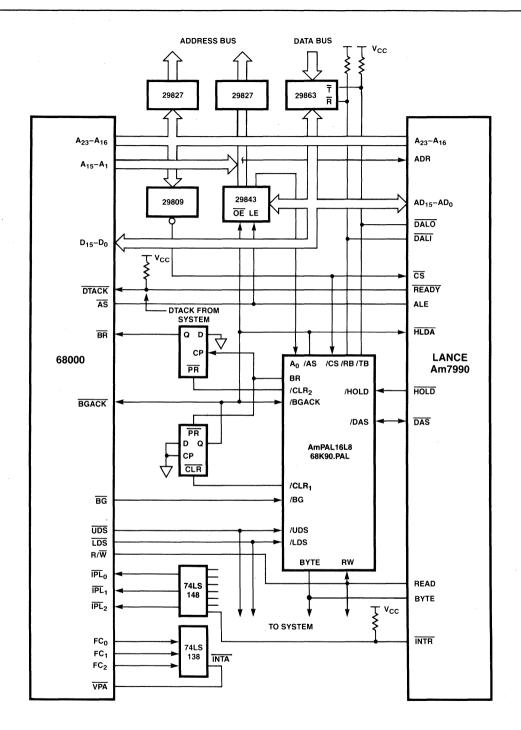

The parallel interface of the Local Area Network Controller for Ethernet (LANCE) has been designed to be "friendly" or easy to interface to a variety of popular 16-bit microprocessors. These microprocessors include the Z8000, Am29000, 80x86, 680x0 and LSI-11. The LANCE has a 24-bit wide linear address space when it is in the Bus Master Mode, allowing it to DMA directly into the entire address space of the above microprocessors. A programmable mode of operation allows byte addressing in one of two ways: a Byte/Word control signal compatible with the 8086 and Z8000 or an Upper Data Strobe and Lower Data Strobe signal compatible with microprocessors such as the 68000. A programmable polarity on the Address Strobe signal eliminates the need for external logic. The LANCE interfaces with both multiplexed and demultiplexed data busses and features control signals for address/data bus transceivers.

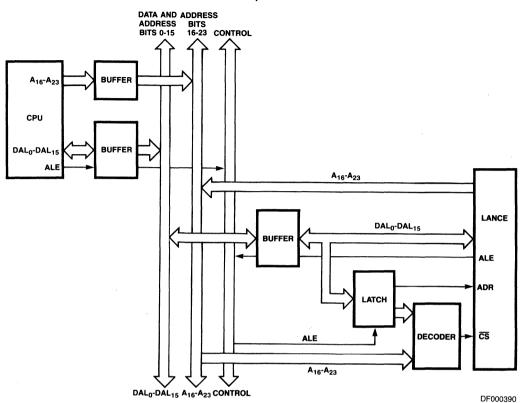

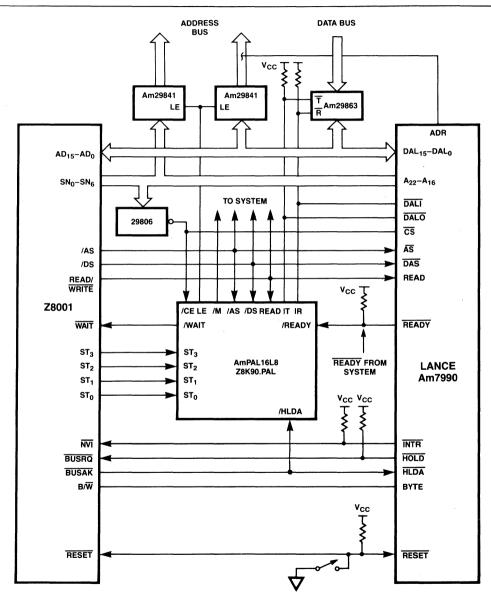

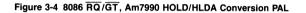

Figure 1-1. LANCE/CPU Interfacing — Multiplexed Bus

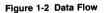

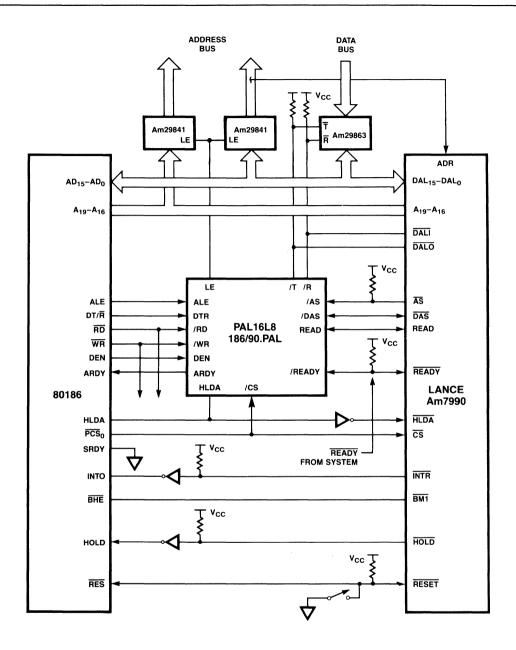

Figure 1-2. LANCE/CPU Interfacing—Demultiplexed Bus

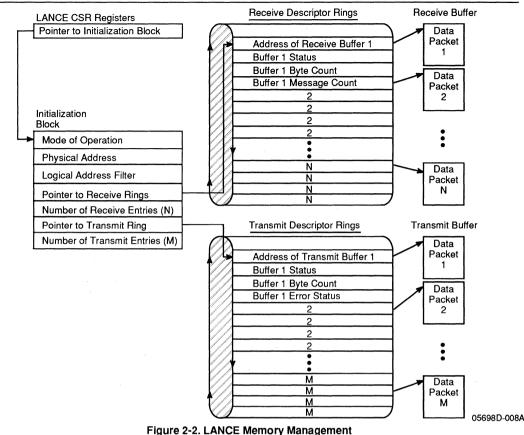

During initialization, the CPU loads the starting address of the initialization block into two internal control registers. The LANCE has four internal control and status registers (CSR<sub>0, 1, 2, 3</sub>) which are used for various functions, such as the loading of the initialization block address, different programming modes and status conditions. The host processor communicates with the LANCE during the initialization phase, for demand transmission, and periodically to read the status bits following interrupts. All other transfers to and from the memory are automatically handled as DMA.

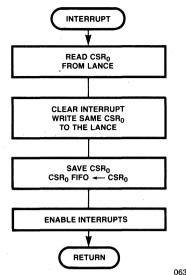

Interrupts to the microprocessor are generated by the LANCE upon: 1) completion of its initialization routine, 2) the reception of a packet, 3) the transmission of a packet, 4) transmitter timeout error, 5) a missed packet and 6) memory error.

The cause of the interrupt is ascertained by reading  $CSR_0$ . Bit (06) of  $CSR_0$ , (INEA), enables or disables interrupts to the microprocessor. In systems where polling is used in place of interrupts, bit (07) of  $CSR_0$ , (INTR), indicates an interrupt condition.

The basic operation of the LANCE consists of two distinct modes: transmit and receive. In the transmit mode, the LANCE chip directly accesses data (in a transmit buffer) in memory. It prefaces the data with a preamble, sync pattern, and calculates and appends a 32-bit CRC. On transmission, the first byte of data loads into the 48-byte FIFO. The LANCE then begins to transmit preamble while simultaneously loading the rest of the packet into FIFO for transmission.

In the receive mode, packets are sent via the Am7992B SIA to the LANCE. The packets are loaded into the 48-byte FIFO for preparation of automatic downloading into buffer memory. A CRC is calculated and compared with the CRC appended to the data packet. If the calculated CRC checksum doesn't agree with the packet CRC, an error bit is set.

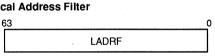

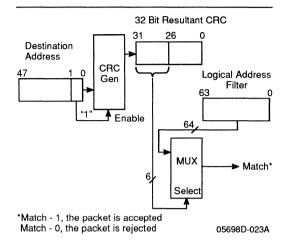

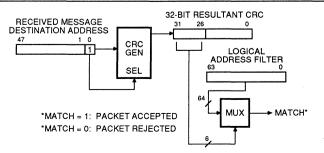

## Addressing

Packets can be received using 3 different destination addressing schemes: physical, logical and promiscuous.

The first type is a full comparison of the 48-bit destination address in the packet with the node address that was programmed into the LANCE during an initialization cycle. There are two types of logical address. One is group type mask where the 48-bit address in the packet is put through a hash filter to map the 48-bit physical addresses into 1 of 64 logical groups. If any of these 64 groups have been preselected as the logical address. then the 48-bit address is stored in main memory. At this time, a look up is performed by the host computer comparing the 48-bit incoming address with the pre-stored 48-bit logical address. This mode can be useful if sending packets to all of a particular type of device simultaneously (i.e., send a packet to all file servers or all printer servers). Additional details on logical addressing can be found in the INITIALIZATION section under "Logical Address Filter". The second logical address is a broadcast address where all nodes on the network receive the packet. The last receive mode of operation is the socalled "promiscuous mode" in which a node will accept all packets on the coax regardless of their destination address.

## **Collision Detection and Implementation**

The Ethernet CSMA/CD network access algorithm is implemented completely within the LANCE. In addition to listening for a clear coax before transmitting, Ethernet handles collisions in a predetermined way. Should two transmitters attempt to seize the coax at the same time, they will collide and the data on the coax will be garbled. The transmitting nodes listen while they transmit, detect the collision, then continue to transmit for a predetermined length of time to "jam" the network and ensure that all nodes have recognized the collision. The trans-

mitting nodes then delay a random amount of time according to the Ethernet "truncated binary backoff" algorithm in order that the colliding nodes don't try to repeatedly access the network at the same time. Up to 16 attempts to access the network are made by the LANCE before reporting back an error due to excessive collisions.

## **Error Reporting and Diagnostics**

Extensive error reporting is provided by the LANCE. Error conditions reported relate either to the network as a whole or to data packets. Network-related errors are recorded as flags in the CSRs and are examined by the CPU following interrupt. Packet-related errors are written into descriptor entries corresponding to the packet.

System errors include:

#### Babbling Transmitter

- Transmitter attempting to transmit more than 1518 data bytes.

- Collision

- Collision detection circuitry nonfunctional

- Missed Packet

- Insufficient buffer space

- Memory timeout

- Memory response failure

Packet-related errors:

- CRC

- Invalid data

- Framing

- Packet did not end on a byte boundary

- Overflow/Underflow

- Indicates abnormal latency in servicing a DMA request

- Buffer

- Insufficient buffer space available

The LANCE performs several diagnostic routines which enhance the reliability and integrity of the system. These include a CRC logic check and two loop back modes (internal/external). Errors may be introduced into the system to check error detection logic. A Time Domain Reflectometer is incorporated into the LANCE to aid system designers locate faults in the Ethernet cable. Shorts and opens manifest themselves in reflections which are sensed by the TDR.

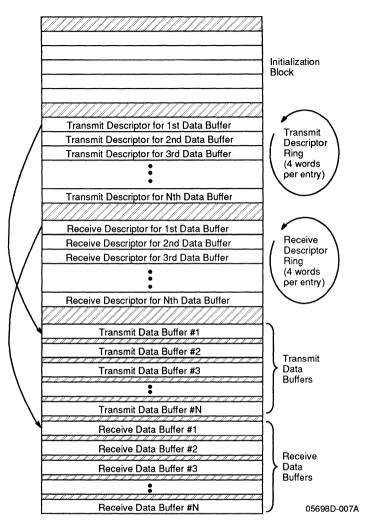

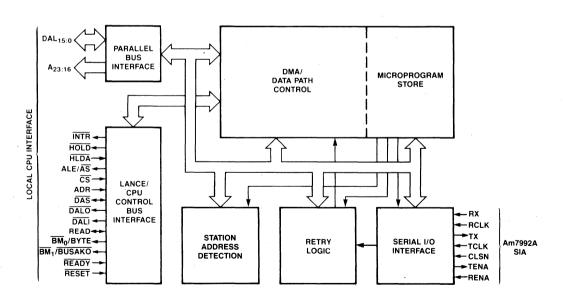

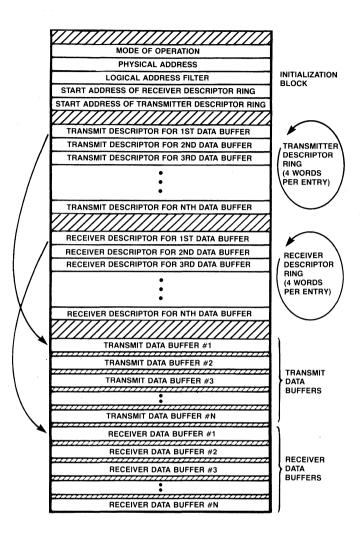

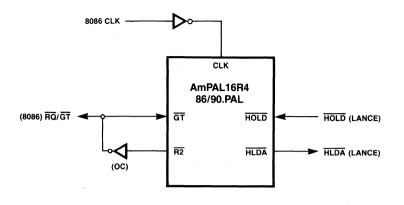

Figure 2-1. LANCE/Processor Memory Interface

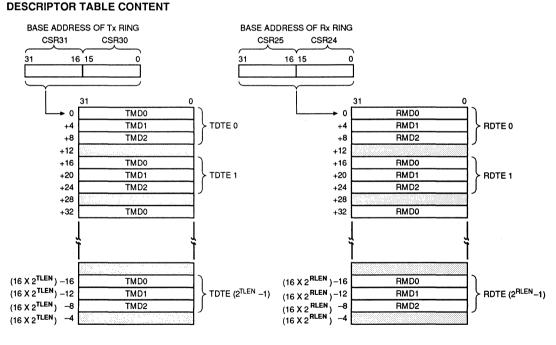

## **Buffer Management**

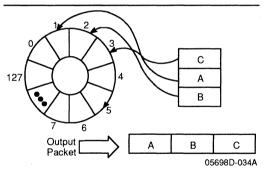

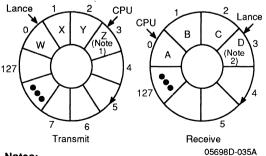

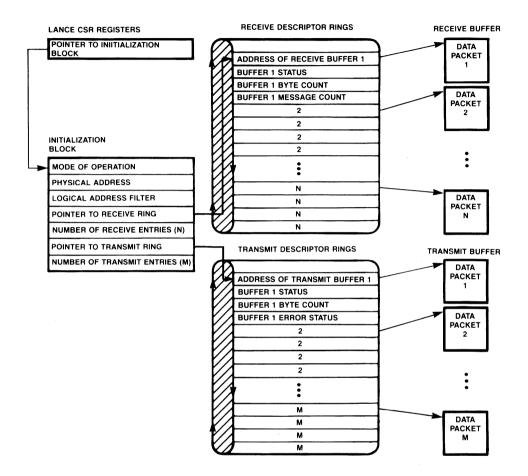

A key feature of the LANCE and its on-board DMA channel is the flexibility and speed of communication between the LANCE and the host microprocessor through common memory locations. The basic organization of the buffer management is a circular queue of tasks in memory called descriptor rings as shown in Figures 2-1 & 2-2. There are separate descriptor rings to describe transmit and receive operations. Up to 128 tasks may be queued up on a descriptor ring awaiting execution by the LANCE. Each entry in a descriptor ring holds a pointer to a data memory buffer and an entry for the length of the data buffer. Data buffers can be chained or cascaded to handle a long packet in multiple data buffer areas. The LANCE searches the descriptor rings in a "lookahead" manner to determine the next empty buffer in order to chain buffers together or to handle back-to-back packets. As each buffer is filled, the "own" bit is reset, allowing the host processor to process the data in the buffer.

## LANCE Interface

CSR bits such as ACON, BCON and BSWP are used for programming the pin functions used for different inter-

facing schemes. For example, ACON is used to program the polarity of the Address Strobe signal (ALE/AS).

BCON is used for programming the pins, for handling either the BYTE/WORD method for addressing word organized, byte addressable memories where the BYTE signal is decoded along with the least significant address bit to determine upper or lower byte, or an explicit scheme in which two signals labeled as BYTE MASK  $(\overline{BM_0} \text{ and } \overline{BM_1})$  indicate which byte is addressed. When the BYTE scheme is chosen, the  $\overline{BM_1}$  pin can be used for performing the function  $\overline{BUSAKO}$ .

BCON is also used to program pins for different DMA modes. In a daisy chain DMA scheme, 3 signals are used (BUSRQ, HLDA, BUSAKO). In systems using a DMA controller for arbitration, only HOLD and HLDA are used.

## LANCE in Bus Slave Mode

The LANCE enters the Bus Slave Mode whenever  $\overline{CS}$  becomes active. This mode must be entered whenever writing or reading the four status control registers (CSR<sub>0</sub>, CSR<sub>1</sub>, CSR<sub>2</sub>, and CSR<sub>3</sub>) and the Register

Address Pointer (RAP). RAP and  $CSR_0$  may be read or written to at anytime, but the LANCE must be stopped (by setting the stop bit in  $CSR_0$ ) for  $CSR_1$ ,  $CSR_2$ , and  $CSR_3$  access.

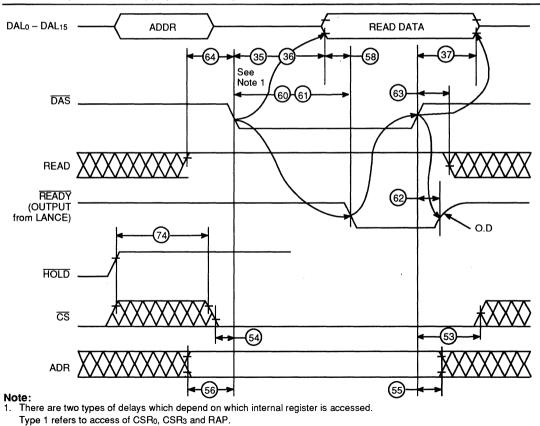

## Read Sequence (Slave Mode)

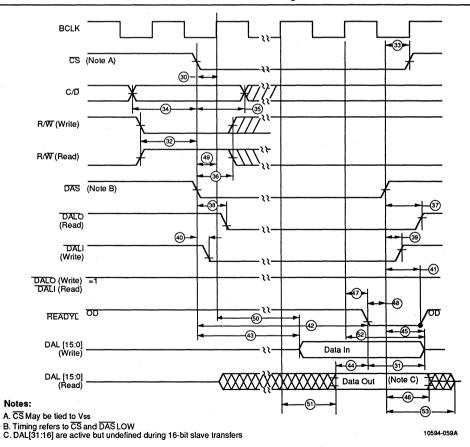

At the beginning of a read cycle,  $\overline{CS}$ , READ, and  $\overline{DAS}$  are asserted. ADR also must be valid at this time. (If ADR is a "1", the contents of RAP are placed on the DAL lines. Otherwise the contents of the CSR register addressed by RAP are placed on the DAL lines.) After the data on the DAL lines become valid, the LANCE asserts READY. CS, READ, DAS, and ADR must remain stable throughout the cycle. Refer to Figure 3.

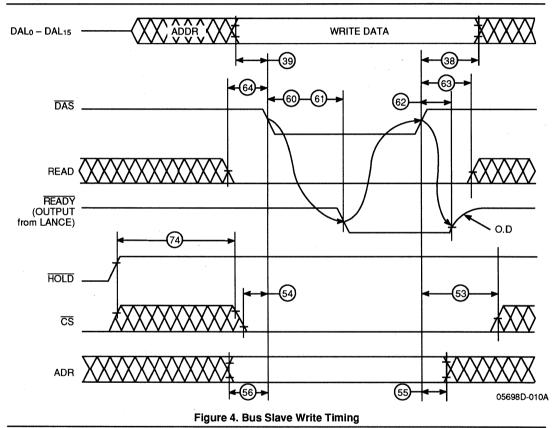

## Write Sequence (Slave Mode)

This cycle is similar to the read cycle, except that during this cycle, READ is not asserted (READ is LOW). The DAL buffers are tristated which configures these lines as inputs. The assertion of READY by LANCE indicates to the memory device that the data on the DAL lines have been stored by LANCE in its appropriate CSR register.

CS, READ, DAS, ADR and DAL <15:00> must remain stable throughout the write cycle. Refer to Figure 4.

#### Note:

Timing parameter 62 does not apply in a slave write cycle that sets the STOP bit in CSR<sub>0</sub>. Setting this bit generates a LANCE reset, which causes all bus control output signals (including READY) to start floating about 100 nsec. after READY goes active. If DAS and CS are held active for more than 400 nsec. after READY start to float, the LANCE can start a second slave cycle. DAS and CS should be deasserted within 400 nsec. after READY starts to float to prevent this second slave cycle from happening.

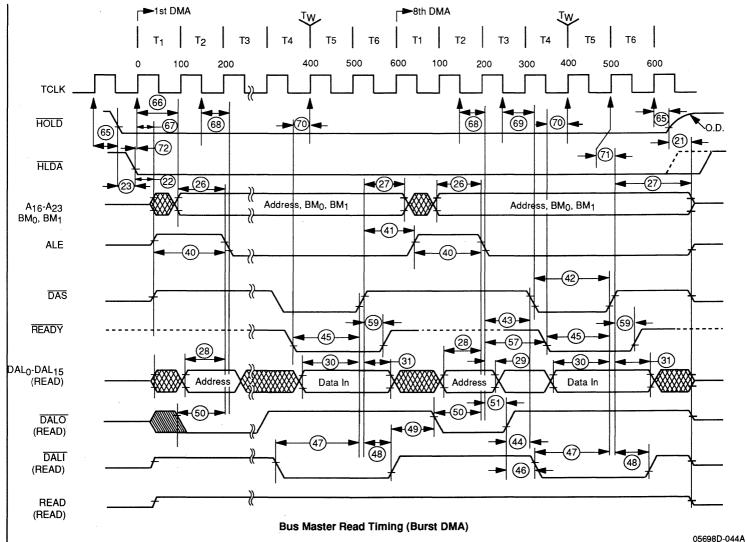

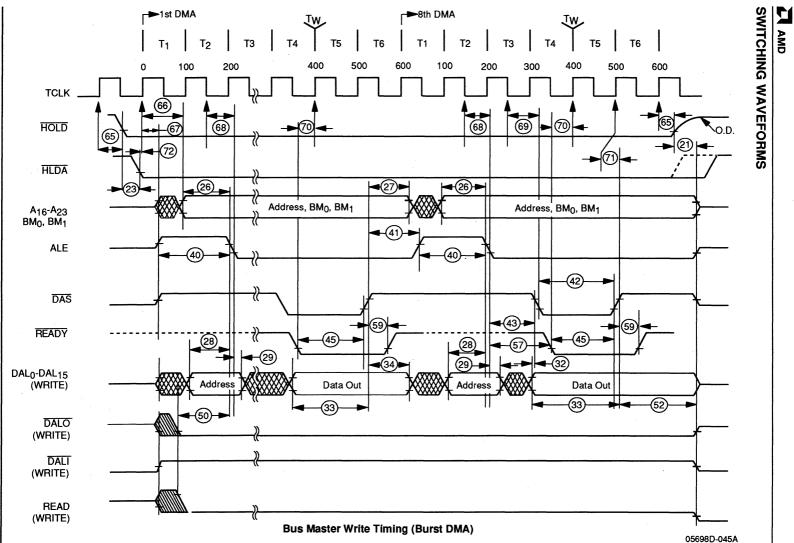

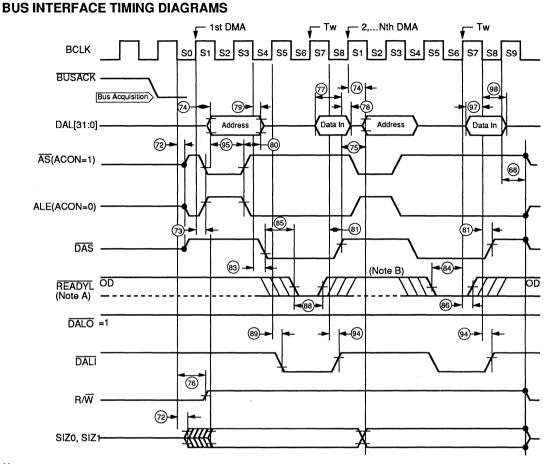

## LANCE in Bus Master Mode

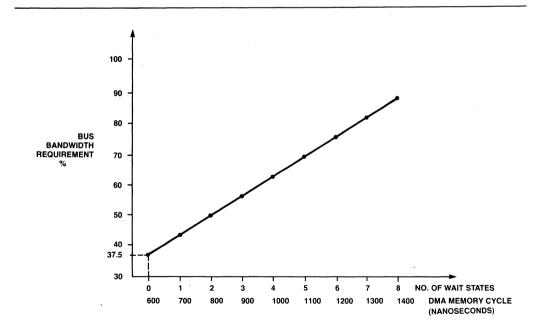

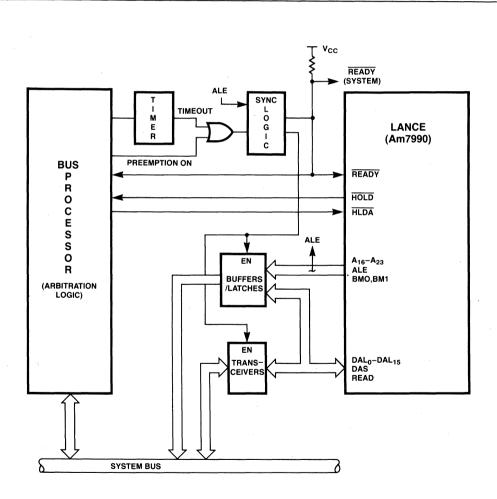

All data transfers from the LANCE in the bus Master mode are timed by ALE, DAS, and READY. The automatic adjustment of the LANCE cycle by the READY signal allows synchronization with variable cycle time memory due either to memory refresh or to dual port access. Bus cycles are a minimum of 600 ns in length and can be increased in 100 ns increments.

Type 2 refers to access of CSR1 and CSR2 which are longer than Type 1 delay.

05698D-009A

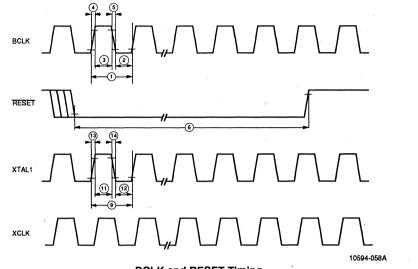

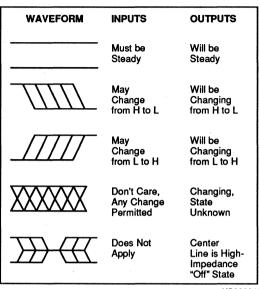

#### Figure 3. Bus Slave Read Timing

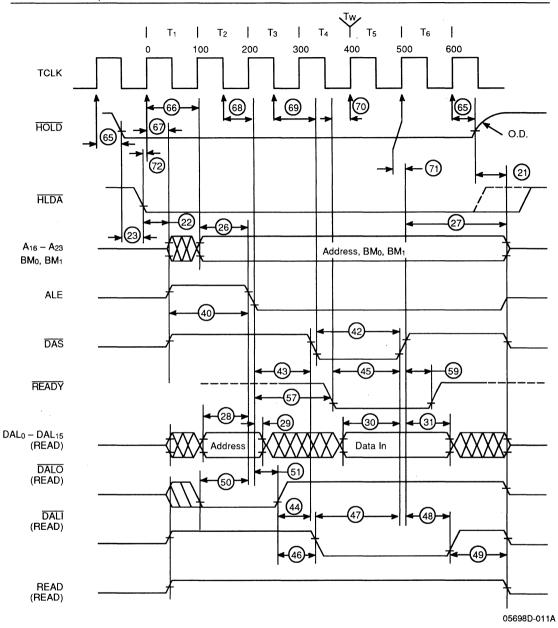

## **Read Sequence (Master Mode)**

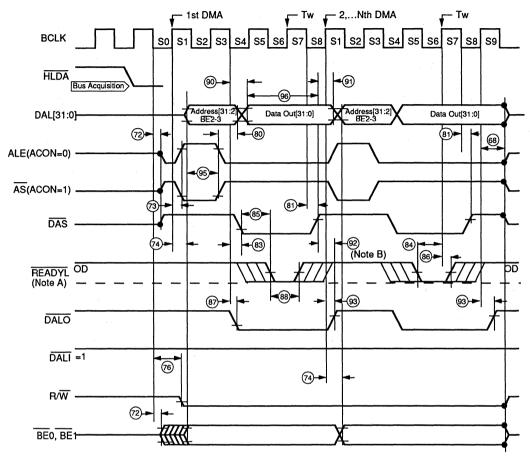

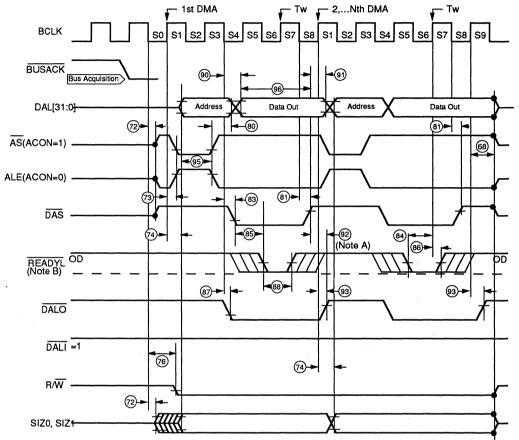

The read cycle is begun by valid addresses being placed on DAL<sub>00</sub> – DAL<sub>15</sub> and A<sub>16</sub> – A<sub>23</sub>. The BYTE MASK signals are asserted to indicate a word, upper byte or lower byte memory reference. READ indicates the type of cycle. ALE or  $\overline{AS}$  are pulsed, and the trailing edge of either can be used to latch addresses. DAL<sub>00</sub> – DAL<sub>15</sub> go into a 3-state mode, and DAS falls LOW to signal the beginning of the memory access. The memory responds by placing READY LOW to indicate that the DAL lines have valid data. The LANCE then latches memory data on the rising edge of DAS, which in turn ends the memory cycle and READY returns HIGH. Refer to Figure 5-1.

The bus transceiver controls, DALI and DALO, are used to control the bus transceivers. DALI directs data toward the LANCE, and DALO directs data or addresses away from the LANCE. During a read cycle, DALO goes inactive before DALI becomes active to avoid "spiking" of the bus transceivers.

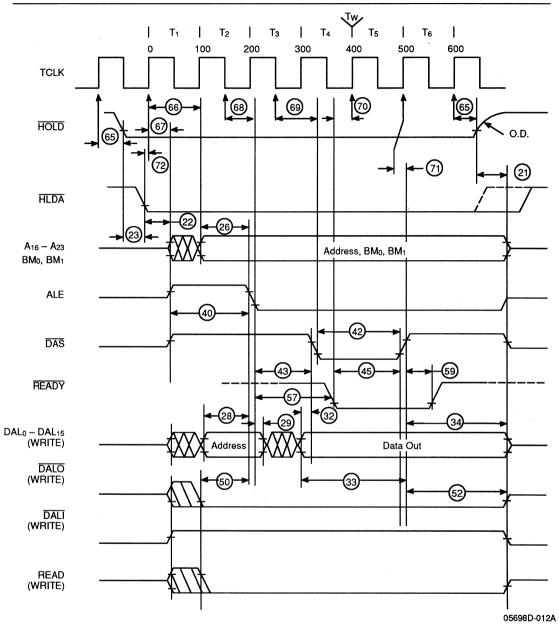

## Write Sequence (Master Mode)

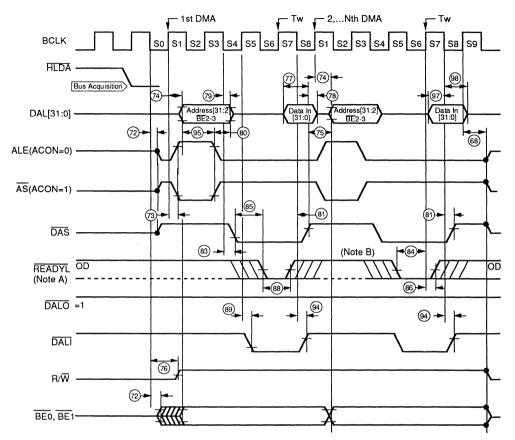

The write cycle is similar to the read cycle except that the  $DAL_{00} - DAL_{15}$  lines change from containing addresses

to data after either ALE or  $\overline{AS}$  goes inactive. After data is valid on the bus,  $\overline{DAS}$  goes active. Data to memory is held valid after  $\overline{DAS}$  goes inactive. Refer to Figure 5-2.

AMD

Figure 5-1. Bus Master Read Timing (Single DMA Cycle)

Figure 5-2. Bus Master Write Timing (Single DMA Cycle)

1-18

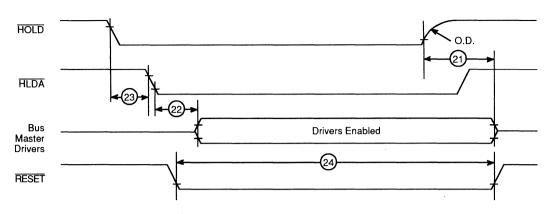

#### Note:

05698D-013A

1. RESET is an asynchronous input to the LANCE and is not part of the Bus Acquisition timing. When RESET is asserted, the LANCE becomes a Bus Slave.

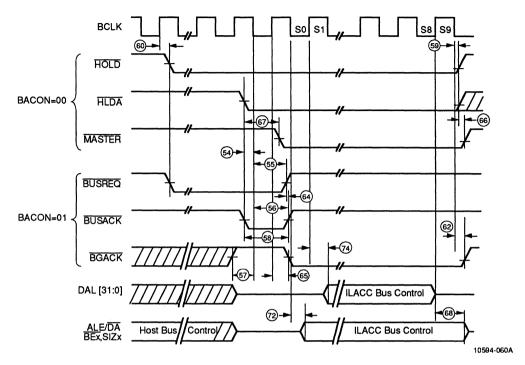

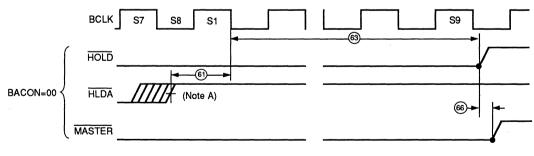

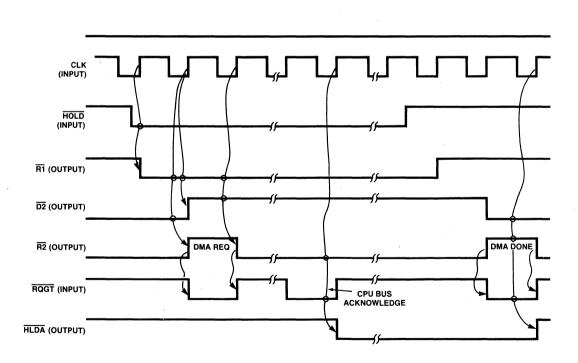

#### Figure 6. Bus Acquisition Timing

#### **Differences Between Ethernet Versions 1 and 2**

- a. Version 2 specifies that the collision detect of the transceiver must be activated during the interpacket gap time.

- b. Version 2 specifies some network management functions, such as reporting the occurrence of collisions, retries and deferrals.

- c. Version 2 specifies that when transmission is terminated, the differential transmit lines are driven to 0 volt differentially (half step).

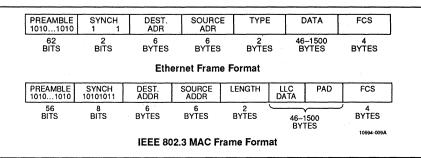

#### **Differences Between IEEE 802.3 and Ethernet**

- a. IEEE 802.3 specifies a 2-byte length field rather than a type field. The length field (802.3) describes the actual amount of data in the frame.

- b. IEEE 802.3 allows the use of a PAD field in the data section of a frame, while Ethernet specifies the minimum packet size at 64 bytes. The use of a PAD allows the user to send and receive packets which have less than 46 bytes of data.

A list of signifcant differences between Ethernet and IEEE 802.3 at the physical layer include the following:

|                           | IEEE 802.3     | Ethernet                                  |

|---------------------------|----------------|-------------------------------------------|

| End of Transmission State | Half Step      | Full Step (Rev 1) or<br>Half Step (Rev 2) |

| Common Mode Voltage       | ±5.5 V         | 0 – +5 V                                  |

| Common Mode Current       | Less than 1 mA | 1.6 mA ±40%                               |

| Receive±, Collision±      |                | <i>2</i>                                  |

| Input Threshold           | ±160 mV        | ±175 mV                                   |

| Fault Protection          | 16 V           | 0 V                                       |

## PROGRAMMING

This section defines the Control and Status Registers and the memory data structures required to program the Am7990 (LANCE).

## Programming the Am7990 (LANCE)

The Am7990 (LANCE) is designed to operate in an environment that includes close coupling with local memory and microprocessor (HOST). The Am7990 LANCE is programmed by a combination of registers and data structures resident within the LANCE and memory registers. There are four Control and Status Registers (CSRs) within the LANCE which are programmed by the HOST device. Once enabled, the LANCE has the ability to access memory locations to acquire additional operating parameters.

The Am7990 has the ability to do independent buffer management as well as transfer data packets to and from the Ethernet. There are three memory structures accessed by the Chip:

- Initialization Block 12 words in contiguous memory starting on a word boundary. It also contains the operating parameters necessary for device operation. The initialization block is comprised of:

- Mode of Operation

- Physical Address

- Logical Address Mask

- Location to Receive and Transmit Descriptor Rings

- Number of Entries in Receive and Transmit Descriptor Rings

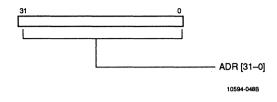

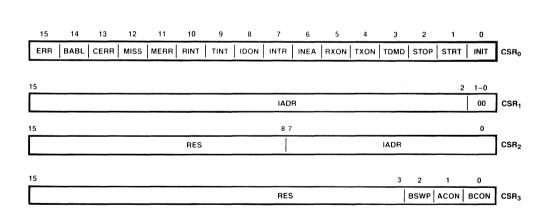

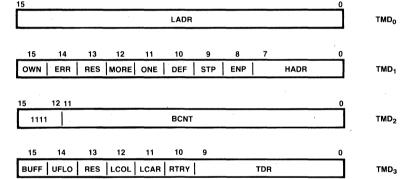

- Receive and Transmit Descriptor Rings Two ring structures, one each for incoming and outgoing packets. Each entry in the rings is 4 words long and each entry must start on a quadword boundary. The Descriptor Rings are comprised of:

- The address of a data buffer

- The length of that data buffer

- Status information associated with the buffer

- Data Buffers Contiguous portions of memory reserved for packet buffering. Data buffers may begin on arbitrary byte boundaries.

In general, the programming sequence of the LANCE may be summarized as:

Program the LANCE's CSRs by a host device to locate an initialization block in memory. The byte control, byte address, and address latch enable modes are also defined here.

- 2. The LANCE loads itself with the information contained within the initialization block.

- 3. The LANCE accesses the descriptor rings for packet handling.

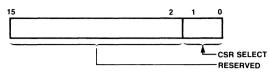

#### **Control and Status Registers**

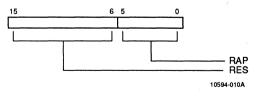

There are four Control and Status Registers (CSRs) on the chip. The CSRs are accessed through two bus addressable ports, an address port (RAP) and a data port (RDP).

#### Accessing the Control and Status Registers

The CSRs are read (or written) in a two step operation. The address of the CSR to be accessed is written into the RAP during a bus slave transaction. During a subsequent bus slave transaction, the data being read from (or written into) the RDP is read from (or written into) the CSR selected in the RAP.

Once written, the address in RAP remains unchanged until rewritten.

To distinguish the data port from the address port, a discrete I/O pin is provided.

#### ADR I/O Pin Port

| L | Register Data Port (RDP)    |

|---|-----------------------------|

| Н | Register Address Port (RAP) |

#### **Register Data Port (RDP)**

| 15 |          | 0 |

|----|----------|---|

|    | CSR DATA |   |

05698D-014A

| Bit   | Name     | Description                                                                                                                                                                                                                                                               |

|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:00 | CSR Data | Writing data into RDP writes the data into the CSR selected in RAP. Reading the data from the RDP reads the data from the CSR selected in RAP. CSR <sub>1</sub> , CSR <sub>2</sub> and CSR <sub>3</sub> are accessible only when the STOP bit of CSR <sub>0</sub> is set. |

|       |          | If the STOP bit is not set while at-<br>tempting to access CSR <sub>1</sub> , CSR <sub>2</sub><br>or CSR <sub>3</sub> , the LANCE will return<br>READY, but a READ operation<br>will return undefined data.<br>WRITE operation is ignored.                                |

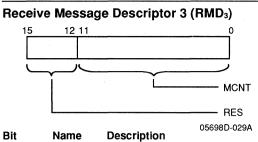

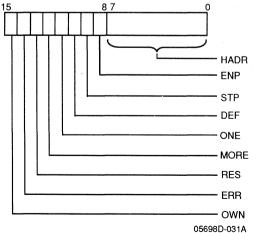

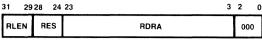

| Regist                                                                    | er Address F | Port (RAP)                                                                                                                                                                                                                                                                                  | Bit | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                           | L            | CSR 1:0<br>RES<br>05698D-015A                                                                                                                                                                                                                                                               | 14  | BABL | BABBLE is a transmitter timeout<br>error. It indicates that the trans-<br>mitter has been on the channel<br>longer than the time required to<br>send the maximum length<br>packet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Bit                                                                       | Name         | Description                                                                                                                                                                                                                                                                                 |     |      | BABL is a flag which indicates<br>excessive length in the transmit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 15:02                                                                     | RES          | Reserved. Read as zeroes. Write as zeroes.                                                                                                                                                                                                                                                  |     |      | buffer. It will be set after 1519<br>data bytes have been transmit-<br>ted; the LANCE will continue to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 01:00                                                                     | CSR(1:0)     | CSR address select. READ/<br>WRITE. Selects the CSR to be<br>accessed through the RDP. RAP<br>is cleared by Bus RESET.<br><u>CSR(1:0)</u> <u>CSR</u>                                                                                                                                        |     |      | transmit until the whole packet is<br>transmitted or until there is a fail-<br>ure before the whole packet is<br>transmitted. When BABL erron<br>occurs, an interrupt will be gener-<br>ated if INEA = 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

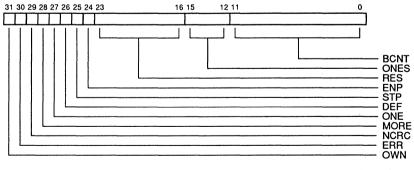

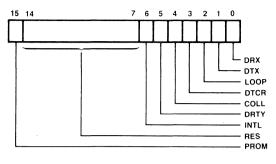

| Contr                                                                     | ol and Sta   | 00 CSR₀<br>01 CSR₁<br>1 0 CSR₂<br>1 1 CSR₃                                                                                                                                                                                                                                                  |     |      | BABL is READ/CLEAR ONLY<br>and is set by the LANCE, and<br>cleared by writing a "1" into the<br>bit. Writing a "0" has no effect. It is<br>cleared by RESET or by setting<br>the STOP bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

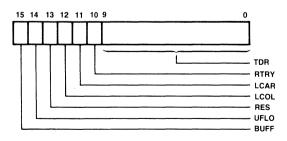

|                                                                           |              | Register Definition                                                                                                                                                                                                                                                                         | 13  | CERR | COLLISION ERROR indicates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

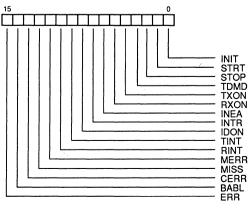

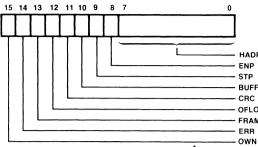

| ERR<br>BABL –<br>CERR –<br>MISS –<br>MERR –<br>RINT –<br>TINT –<br>IDON – | The LANCE    | INIT<br>INIT<br>STRT<br>STOP<br>TDMD<br>TXON<br>RXON<br>INEA<br>INTR<br>Supdates CSRo by logical<br>e previous and present                                                                                                                                                                  | 12  | MISS | that the collision input to the<br>LANCE failed to activate within<br>2 µs after a LANCE-initiated<br>transmission was completed.<br>The collision after transmission is<br>a transceiver test feature. This<br>function is also known as heart-<br>beat or SQE (Signal Quality Er-<br>ror) test.<br>CERR is READ/CLEAR ONLY<br>and is set by the LANCE and<br>cleared by writing a "1" into the<br>bit. Writing a "0" has no effect. It is<br>cleared by RESET or by setting<br>the STOP bit. CERR error will not<br>cause an interrupt to occur (INTR<br>= 0).<br>MISSED PACKET is set when<br>the receiver loses a packet be-<br>cause it does not own any re-<br>ceive buffer, indicating loss of |

| Bit                                                                       | Name         | Description                                                                                                                                                                                                                                                                                 |     |      | data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

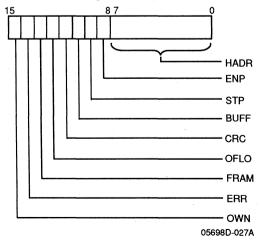

| 15                                                                        | ERR          | ERROR summary is set by the<br>"ORing" of BABL, CERR, MISS<br>and MERR. ERR remains set as<br>long as any of the error flags are<br>true.<br>ERR is read only; writing it has no<br>effect. It is cleared by Bus<br>RESET, setting the STOP bit, or<br>clearing the individual error flags. |     |      | FIFO overflow is not reported<br>because there is no receive ring<br>entry in which to write status.<br>When MISS is set, an interrupt<br>will be generated if INEA = 1.<br>MISS is READ/CLEAR ONLY,<br>and is set by the LANCE and<br>cleared by writing a "0" has no effect. It is<br>cleared by RESET or by setting<br>the STOP bit.                                                                                                                                                                                                                                                                                                                                                               |

| Bit | Name | Description                                                                                                                                                                                                                                     | Bit | Name | Description                                                                                                                                                                                                                                             |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11  | MERR | MEMORY ERROR is set when<br>the LANCE is the Bus Master and<br>has not received READY within<br>25.6 µs after asserting the ad-<br>dress on the DAL lines.<br>When a Memory Error is de-                                                        |     |      | IDON is READ/CLEAR ONLY,<br>and is set by the LANCE and<br>cleared by writing a "1" into the<br>bit. Writing a "0" has no effect. It is<br>cleared by RESET or by setting<br>the STOP bit.                                                              |

|     |      | tected, the receiver and transmit-<br>ter are turned off (CSR <sub>0</sub> , TXON =<br>0, RXON = 0) and an interrupt is<br>generated if INEA = 1.<br>MERR is READ/CLEAR ONLY,                                                                   | 07  | INTR | INTERRUPT FLAG is set by the<br>"ORing" of BABL, MISS, MERR,<br>RINT, TINT and IDO <u>N. If</u> INEA =<br>1 and INTR = 1, the INTR pin will<br>be LOW.                                                                                                  |

|     |      | and is set by the LANCE and<br>cleared by writing a "1" into the<br>bit. Writing a "0" has no effect. It is<br>cleared by RESET or by setting<br>the STOP bit.                                                                                  |     |      | INTR is READ ONLY; writing this<br>bit has no effect. INTR is cleared<br>by RESET, by setting the STOP<br>bit, or by clearing the condition<br>causing the interrupt.                                                                                   |

| 10  | RINT | RECEIVER INTERRUPT is set<br>when the LANCE updates an en-<br>try in the Receive Descriptor<br>Ring for the last buffer received<br>or reception is stopped due to a<br>failure.<br>When RINT is set, an interrupt is<br>generated if INEA = 1. | 06  | INEA | INTERRUPT ENABLE allows<br>the INTR pin to be driven LOW<br>when the Interrupt Flag is set. If<br>INEA = 1 and INTR = 1, the INTR<br>pin will be Low. If INEA = 0, the<br>INTR pin will be HIGH, regard-<br>less of the state of the Interrupt<br>Flag. |

|     |      | RINT is READ/CLEAR ONLY,<br>and is set by the LANCE and<br>cleared by writing a "1" into the<br>bit. Writing a "0" has no effect. It<br>is cleared by RESET or by setting                                                                       |     |      | INEA is READ/WRITE and<br>cleared by RESET or by setting<br>the STOP bit.<br>INEA cannot be set while STOP<br>bit is set. INEA can be set in par-                                                                                                       |

| 09  | TINT | the STOP bit.<br>TRANSMITTER INTERRUPT is<br>set when the LANCE updates an<br>entry in the transmit descriptor<br>ring for the last buffer sent or                                                                                              | 05  | RXON | allel or after INIT and/or STRT bit<br>are set.<br>RECEIVER ON indicates that the<br>receiver is enabled. RXON is set<br>when STRT is set if DRX = 0 in                                                                                                 |

|     |      | transmission is stopped due to a failure.<br>When TINT is set, an interrupt is generated if INEA = 1.                                                                                                                                           |     |      | the MODE register in the initiali-<br>zation block and the initialization<br>block has been read by the<br>LANCE by setting the INIT bit.<br>RXON is cleared when IDON is                                                                               |

|     |      | TINT is READ/CLEAR ONLY<br>and is set by the LANCE and<br>cleared by writing a "1" into the<br>bit. Writing a "0" has no effect. It is<br>cleared by RESET or by setting<br>the STOP bit.                                                       |     |      | set from setting the INIT bit and<br>DRX = 1 in the MODE register, or<br>a memory error (MERR) has oc-<br>curred. RXON is READ ONLY<br>writing this bit has no effect<br>RXON is cleared by RESET or by                                                 |

| 08  | IDON | INITIALIZATION DONE indi-<br>cates that the LANCE has com-<br>pleted the initialization procedure<br>started by setting the INIT bit.<br>When IDON is set, the LANCE                                                                            | 04  | TXON | setting the STOP bit.<br>TRANSMITTER ON indicates<br>that the transmitter is enabled<br>TXON is set when STRT is set it                                                                                                                                 |

|     |      | has read the Initialization Block<br>from memory and stored the new<br>parameters.<br>When IDON is set, an interrupt is<br>generated if INEA = 1.                                                                                               |     |      | DTX = 0 in the MODE register in<br>the initialization block and the<br>INIT bit has been set. TXON is<br>cleared when IDON is set and<br>DTX = 1 in the MODE register, or<br>an error, such as MERR, UFLC<br>or BUFF, has occurred during               |

1-22

| Bit | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                            | Bit    | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03  | TDMD | TXON is READ ONLY; writing<br>this bit has no effect. TXON is<br>cleared by RESET or by setting<br>the STOP bit.<br>TRANSMIT DEMAND, when set,                                                                                                                                                                                                                                                                         |        |           | STRT is READ/WRITE and is set<br>with one only. Writing a "0" into<br>this bit has no effect. STRT is<br>cleared by RESET or by setting<br>the STOP bit.                                                                                                                                                                                                                                                                                       |

| 55  | TUMU | causes the LANCE to access the<br>Transmit Descriptor Ring without<br>waiting for the polltime interval to<br>elapse. TDMD need not be set to<br>transmit a packet; it merely has-<br>tens the LANCE's response to a<br>Transmit Descriptor Ring entry<br>insertion by the host.<br>TDMD is WRITE WITH ONE<br>ONLY and is cleared by the<br>microcode after it is used. It may<br>read as a "1" for a short time after | 00     | INIT      | INITIALIZE, when set, causes<br>the LANCE to begin the initializa-<br>tion procedure and access the In-<br>itialization Block. The STOP bit<br>must be set prior to setting the<br>INIT bit. Setting INIT clears the<br>STOP bit.<br>INIT is READ/WRITE WITH "1"<br>ONLY. Writing a "0" into this bit<br>has no effect. INIT is cleared by<br>RESET or by setting the STOP                                                                     |

|     |      | read as a "1" for a short time after<br>it is written because the<br>microcode may have been busy<br>when TDMD was set. It is also<br>cleared by RESET or by setting<br>the STOP bit. Writing a "0" in this<br>bit has no effect.                                                                                                                                                                                      |        |           | bit.<br>Since the setting of status bits in<br>CSR <sub>0</sub> is independent of the tim-<br>ing of the slave read cycle, it is<br>possible for external events to<br>cause some of the bits to change                                                                                                                                                                                                                                        |

| 02  | STOP | STOP disables the LANCE from<br>all external activity when set and<br>clears the internal logic. Setting<br>STOP is the equivalent of assert-<br>ing RESET. The LANCE remains<br>inactive and STOP remains set<br>until the STRT or INIT bit is set. If<br>STRT, INIT and STOP are all set<br>together, STOP will override the<br>other bits and only STOP will be<br>set.<br>STOP is READ/WRITE WITH                  |        |           | in the middle of a read cycle. In<br>particular the ERR, BABL,<br>CERR, MISS, IDON, and INTR<br>bits can change during a read cy-<br>cle, while MERR, RINT and TINT<br>can not. This is not a problem if<br>CSR <sub>0</sub> is read only within the first<br>few instructions of an interrupt<br>service routine since the events<br>that cause these bits to change<br>are widely spaced in time relative<br>to the time required to execute |

|     |      | ONE ONLY and set by RESET.<br>Writing a "0" to this bit has no ef-                                                                                                                                                                                                                                                                                                                                                     | Contro | and Statu | processor instructions.                                                                                                                                                                                                                                                                                                                                                                                                                        |

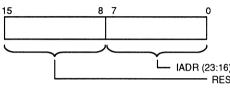

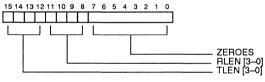

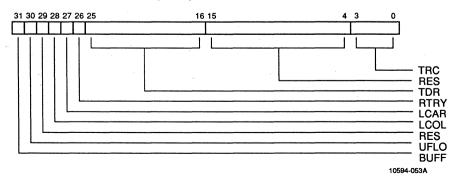

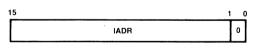

| 01  | STRT | fect. STOP is cleared by setting<br>either INIT or STRT. CSR <sub>1</sub> ,<br>CSR <sub>2</sub> , and CSR <sub>3</sub> must be re-<br>loaded when the STOP bit is set.<br>START enables the LANCE to                                                                                                                                                                                                                   |        | WRITE:    | s Register 1 (CSR <sub>1</sub> )<br>Accessible only when the STOP<br>bit of CSR <sub>0</sub> is a ONE and RAP =<br>01. Content of CSR <sub>1</sub> is not<br>preserved after CSR <sub>0</sub> s STOP bit<br>is set to one.                                                                                                                                                                                                                     |

|     |      | send and receive packets, per-<br>form direct memory access, and<br>do buffer management. The<br>STOP bit must be set prior to set-<br>ting the STRT bit. Setting STRT<br>clears the STOP bit.                                                                                                                                                                                                                         |        | <u>.</u>  | IADR<br>(15:01)<br>05698D-017A                                                                                                                                                                                                                                                                                                                                                                                                                 |

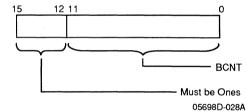

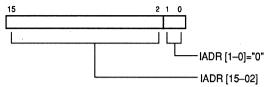

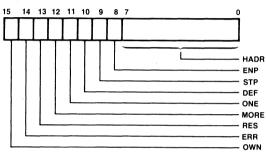

| Bit   | Name | Description                                                                                          |

|-------|------|------------------------------------------------------------------------------------------------------|

| 15:01 | IADR | The low order 15 bits of the address of the first word (lowest address) in the Initialization Block. |

| 00    |      | Must be zero.                                                                                        |

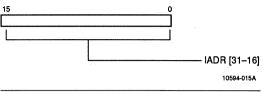

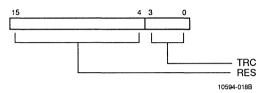

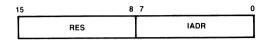

Control and Status Register 2 (CSR<sub>2</sub>)

**READ/WRITE:**

RITE: Accessible only when the STOP bit of CSR<sub>0</sub> is a ONE and RAP = 10. Content of CSR<sub>2</sub> is not preserved after CSR's STOP bit is set to one.

05698D-018A

| Bit   | Name | Description                                                                                                    |

|-------|------|----------------------------------------------------------------------------------------------------------------|

| 15:08 | RES  | Reserved. Read as zeroes. Write as zeroes.                                                                     |

| 07:00 | IADR | The high order 8 bits of the ad-<br>dress of the first word (lowest ad-<br>dress) in the initialization Block. |

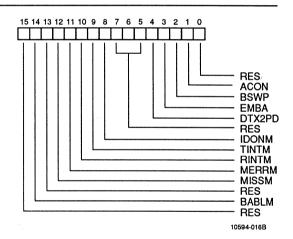

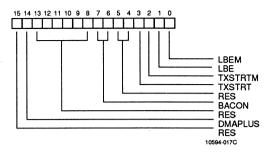

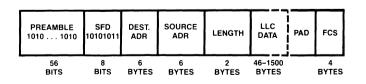

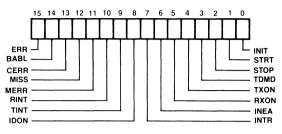

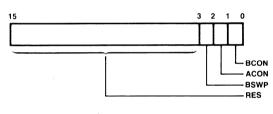

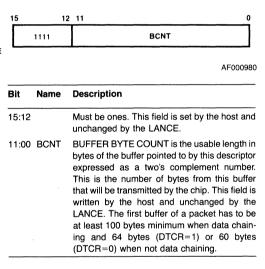

## Control and Status Register 3 (CSR<sub>3</sub>)

CSR<sub>3</sub> allows redefinition of the Bus Master interface.

READ/WRITE: Accessible only when the STOP bit of CSR<sub>0</sub> is ONE and RAP = 11. CSR<sub>3</sub> is cleared by RESET or by setting the STOP bit in CSR<sub>0</sub>.

|               | Bit       | Name           | Description                                                                                                                                                                                                                                                    |

|---------------|-----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ne<br>st      | 15:03     | RES            | Reserved. Read as zeroes. Write as zeroes.                                                                                                                                                                                                                     |

| on<br>P       | 02        | BSWP           | BYTE SWAP allows the chip to<br>operate in systems that consider<br>bits (15:08) of data to be pointed<br>at an even address and bits<br>(07:00) to be pointed at an odd<br>address.                                                                           |

| =<br>e-<br>is |           |                | When BSWP = 1, the LANCE will<br>swap the high and low bytes on<br>DMA data transfers between the<br>FIFO and bus memory. Only data<br>from FIFO transfers is swapped;<br>the Initialization Block data and<br>the Descriptor Ring entries are<br>NOT swapped. |

| 6)<br>S       |           |                | BSWP is <u>READ</u> /WRITE and cleared by <u>RESET</u> or by setting the STOP bit in CSR <sub>0</sub> .                                                                                                                                                        |

| 18A<br><br>te | 01        | ACON           | ALE CONTROL defines the as-<br>sertive state of ALE when the<br>LANCE is a Bus Master. ACON is<br><u>READ/WRITE</u> and cleared by<br><u>RESET</u> and by setting the STOP<br>bit in CSR <sub>0</sub> .                                                        |

| d-<br>d-      |           |                | ACON ALE                                                                                                                                                                                                                                                       |

| κ.            |           |                | <ol> <li>Asserted HIGH</li> <li>Asserted LOW</li> </ol>                                                                                                                                                                                                        |

| )P<br>1.      | tive goir | ig pulse of le | mmed to be asserted LOW, a nega-<br>ess than 10 ns. duration can occur at<br>master cycle just after HOLD is                                                                                                                                                   |

00 BCON

| BYTE CONTROL redefines the         |

|------------------------------------|

| Byte Mask and Hold I/O pins.       |

| BCON is READ/WRITE and             |

| cleared by RESET or by setting     |

| the STOP bit in CSR <sub>0</sub> . |

| <u>BCON</u> | <u>Pin 16</u>   | <u>Pin 15</u> | <u>Pin 17</u> |

|-------------|-----------------|---------------|---------------|

| 0           | BM <sub>1</sub> | BM₀           | HOLD          |

| 1           | BUSAKO          | BYTE          | BUSRO         |

All data transfers from the LANCE in the Bus Master mode are in words. However, the LANCE can handle odd address boundaries and/or packets with an odd number of bytes.

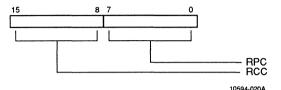

## Initialization

#### **Initialization Block**

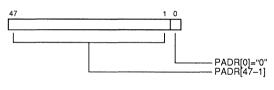

Chip initialization includes the reading of the initialization block in memory to obtain the operating parameters. The following is a definition of the Initialization Block.

The Initialization Block is read by the LANCE when the INIT bit in  $CSR_0$  is set. The INIT bit should be set before or concurrent with the STRT bit to insure proper parameter initialization and chip operation. After the LANCE has read the Initialization Block, IDON is set in  $CSR_0$  and an interrupt is generated if INEA = 1.

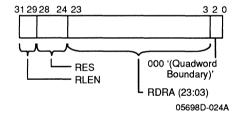

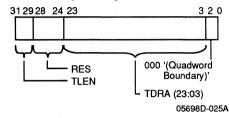

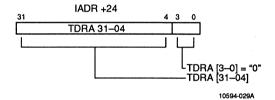

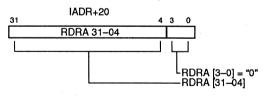

| Higher Address       | TLEN-TDR (23:16)  | IADR +22 |

|----------------------|-------------------|----------|

|                      | TDRA (15:00)      | IADR +20 |

|                      | RLEN-RDRA (23:16) | IADR +18 |

|                      | RDRA (15:00)      | IADR +16 |

|                      | LADRF (63:48)     | IADR +14 |

|                      | LADRF (47:32)     | IADR +12 |

|                      | LADRF (31:16)     | IADR +10 |

|                      | LADRF (15:00)     | IADR +08 |

|                      | PADR (47:32)      | IADR +06 |

|                      | PADR (31:16)      | IADR +04 |

|                      | PADR (15:00)      | IADR +02 |

| Base Address of Bloc | k MODE            | IADR +00 |

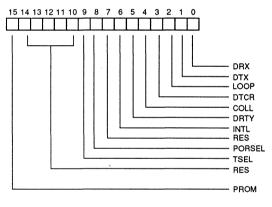

#### Mode

The Mode Register allows alteration of the LANCE's operating parameters. Normal operation is with the Mode Register clear.

| Bit   | Name | Description                                                               |

|-------|------|---------------------------------------------------------------------------|

| 15    | PROM | PROMISCUOUS mode. When<br>PROM = 1, all incoming packets<br>are accepted. |

| 14:07 | RES  | RESERVED. Read as zeroes.<br>Write as zeroes.                             |

| ACK is used<br>o determine<br>s to be done.                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| o determine                                                                                                                                                            |

| ows the chip<br>transmitted<br>presents full<br>packet size<br>tes. Internal<br>CE is opera-<br>kets are ad-<br>itself.                                                |

| receive any<br>hen it is in in-<br>le.                                                                                                                                 |

| BACK allows<br>mit a packet<br>nsceiver ca-<br>et coax. It is<br>e operability<br>connections<br>and the co-<br>t addressing<br>is valid only<br>ser needs to<br>CRC). |

| , the LANCE<br>is from other<br>EAD/WRITE<br>llign in the<br>/ traffic. The<br>corrupted or<br>fore, the ex-<br>socution may<br>See specific<br>oopback" in            |

| LOOP = 1;<br>ed.                                                                                                                                                       |

| OOPBACK<br>o loopback,                                                                                                                                                 |

| ormal<br>xternal                                                                                                                                                       |

| tternal<br>Y. When<br>JCE will at-<br>mission of a<br>collision on<br>n attempt, a<br>will be re-<br>t Message                                                         |

|                                                                                                                                                                        |

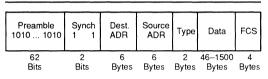

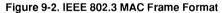

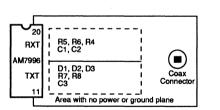

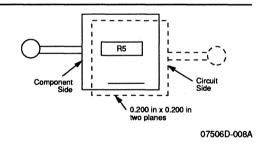

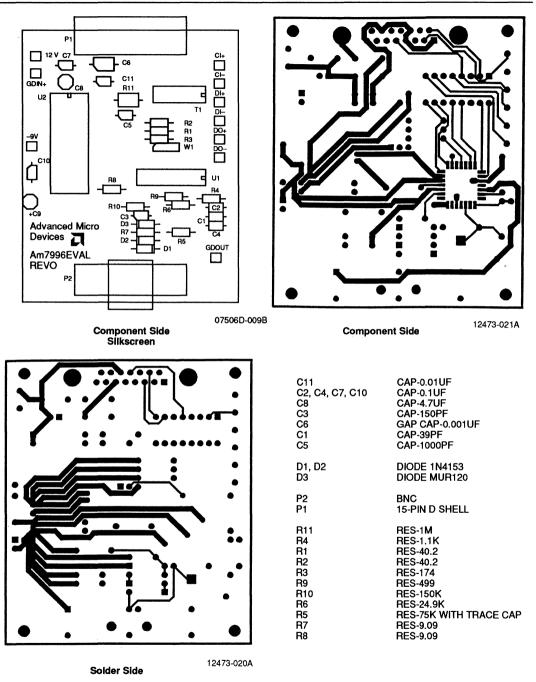

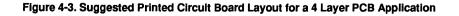

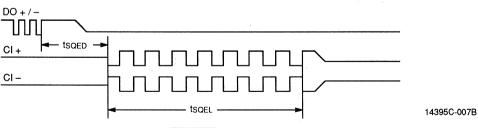

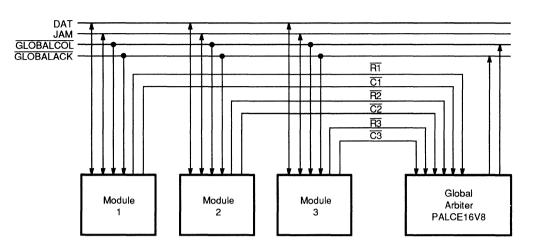

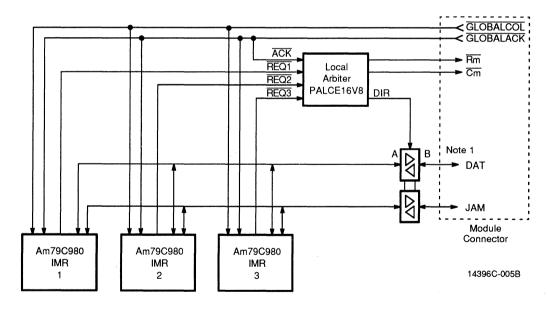

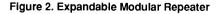

| Bit | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit                                                                                                                          | Name                                                                                                                                                                                                                                      |